# Bounded Model Checking for Asynchronous Concurrent Systems

#### Manitra Johanesa Rakotoarisoa

Department of Computer Architecture Technical University of Catalonia

Advisor: Enric Pastor Llorens

Thesis submitted to obtain the qualification of Doctor from the Technical University of Catalonia

## Contents

| A | bstra | ct      |                                    | xvii |

|---|-------|---------|------------------------------------|------|

| A | ckno  | wledgn  | nents                              | xix  |

| 1 | Intr  | oducti  | ion                                | 1    |

|   | 1.1   | Symbo   | olic Model Checking                | 3    |

|   |       | 1.1.1   | BDD-based approach                 | 3    |

|   |       | 1.1.2   | SAT-based Approach                 | 6    |

|   | 1.2   | Synch   | ronous Versus Asynchronous Systems | 8    |

|   |       | 1.2.1   | Synchronous systems                | 8    |

|   |       | 1.2.2   | Asynchronous systems               | 10   |

|   | 1.3   | Scope   | of This Work                       | 11   |

|   | 1.4   | Struct  | ture of the Thesis                 | 12   |

| 2 | Bac   | kgroui  | $\mathbf{nd}$                      | 13   |

|   | 2.1   | Transi  | ition Systems                      | 13   |

|   |       | 2.1.1   | Definitions                        | 13   |

|   |       | 2.1.2   | Symbolic Representation            | 15   |

|   | 2.2   | Other   | Models for Concurrent Systems      | 17   |

|   |       | 2.2.1   | Kripke Structure                   | 17   |

|   |       | 2.2.2   | Petri Nets                         | 21   |

|   |       | 2.2.3   | Automata                           | 22   |

|   | 2.3   | Linear  | : Temporal Logic                   | 24   |

|   | 2.4   | Satisfi | ability Problem                    | 26   |

|   |       | 2.4.1   | DPLL Algorithm                     | 27   |

|   |       | 2.4.2   | Stålmarck's Algorithm              | 28   |

|   |       | 2.4.3   | Other Methods for Solving SAT      | 32   |

|   | 2.5   | Bound   | led Model Checking                 | 34   |

|   |       | 2.5.1   | BMC Idea                           | 34   |

|   |       | 2.5.2   | Safety Check Example               | 34   |

|   |       | 2.5.3   | BMC and Liveness Properties        | 35   |

vi CONTENTS

| 3 | Exi | xting 7 | Techniques                                   | <b>37</b> |

|---|-----|---------|----------------------------------------------|-----------|

|   | 3.1 | Standa  | ard Methods                                  | 37        |

|   | 3.2 | Comp    | leteness                                     | 39        |

|   | 3.3 | SAT w   | vith Unbounded Model Checking                | 41        |

|   | 3.4 | Existin | ng BMC Tools                                 | 42        |

| 4 | Enc | oding   | Methods                                      | 43        |

|   | 4.1 | Relate  | d Work                                       | 44        |

|   | 4.2 | Symbo   | olic Representation                          | 45        |

|   | 4.3 | Encod   | ing for Independent Systems                  | 46        |

|   |     | 4.3.1   | Interleaving Execution                       | 46        |

|   |     | 4.3.2   | Breadth-First Search Execution               | 48        |

|   | 4.4 | Encod   | ing for Synchronized Systems                 | 51        |

|   |     | 4.4.1   | Interleaving Execution                       | 51        |

|   |     | 4.4.2   | Breadth-First Search Execution               | 54        |

|   | 4.5 | Expres  | ssing Reachability Properties                | 56        |

|   | 4.6 | Reduc   | ing the Bound Using Chaining                 | 58        |

|   |     | 4.6.1   | Introduction                                 | 58        |

|   |     | 4.6.2   | Application to BMC                           | 59        |

|   |     | 4.6.3   | Ordering the Events                          | 61        |

|   |     | 4.6.4   | Chaining Algorithm                           | 63        |

| 5 | Lea | n-Base  | ed Approach                                  | 65        |

|   | 5.1 | _       | d Work                                       | 66        |

|   | 5.2 |         | ing Method for Deadlock Property             | 67        |

|   | 0.2 | 5.2.1   | Introduction                                 | 67        |

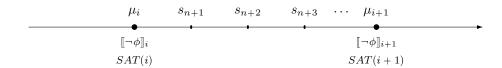

|   |     | 5.2.2   | BMC Equations                                | 68        |

|   | 5.3 |         | ing Method for Other Reachability Properties | 70        |

|   | 0.0 | 5.3.1   | Introduction                                 | 70        |

|   |     | 5.3.2   | BMC Equations                                | 71        |

|   | 5.4 |         | ng Methods                                   | 73        |

|   | 0.1 | 5.4.1   | Using Logarithmic Functions                  | 73        |

|   |     | 5.4.2   | Using Interpolation                          | 76        |

|   | 5.5 |         | g the Shortest Counterexample                | 77        |

|   | 5.6 |         | Performance                                  | 77        |

|   |     |         |                                              |           |

| 6 |     |         | nata-Theoretic Approach                      | 81        |

|   | 6.1 |         | d Work                                       | 83        |

|   | 6.2 | _       | sentation of Büchi Automata                  | 84        |

|   |     | 6.2.1   | Different Types of Büchi Automata            | 84        |

|   |     | 6.2.2   | Translating an LTL Formula Into a TGBA       | 86        |

|   |     | 6.2.3   | TGBA Encoding                                | 90        |

| CONTENTS | vii |

|----------|-----|

|          |     |

|    | 6.3   | Buildi         | ng the BMC Formulas            | 92         |

|----|-------|----------------|--------------------------------|------------|

|    |       | 6.3.1          | Interleaving Execution         | 92         |

|    |       | 6.3.2          | Breadth First Search Execution | 94         |

|    |       | 6.3.3          | Chaining                       | 96         |

|    | 6.4   | Discus         | s <mark>ion</mark>             | 97         |

| 7  | Imp   | lemen          | tation                         | 99         |

|    | 7.1   |                | ent Modules                    | 99         |

|    |       | 7.1.1          | LTL2BA                         | 99         |

|    |       | 7.1.2          | BMC Module                     | 101        |

|    |       | 7.1.3          | CNF translator                 | 103        |

|    |       | 7.1.4          | Solver                         | 103        |

|    | 7.2   | Input          | Formats                        | 104        |

|    |       | 7.2.1          | TS File format                 | 104        |

|    |       | 7.2.2          | PEP File format                | 105        |

|    | 7.3   | Impor          | tant commands                  | 107        |

| 8  | Coo   | e Stud         | too.                           | 111        |

| 0  |       |                |                                | 111        |

|    | 8.1   | 8.1.1          | iments Related to Reachability | 111        |

|    |       | _              | •                              | 112        |

|    | 8.2   | 8.1.2          | Comparison with the Tool NuSMV | 113        |

|    | 0.2   | -              | imental Results Related to LTL |            |

|    |       | 8.2.1          | Gas Station                    | 114        |

|    |       | 8.2.2<br>8.2.3 | Bakery Algorithm               | 114<br>114 |

|    |       | 8.2.4          |                                | 114        |

|    |       | _              | Sleeping Barber                |            |

|    |       | 8.2.5          | Leader Election Protocol       | 115        |

|    | 0.9   | 8.2.6          | Properties and Instances       | 115        |

|    | 8.3   | _              | iments Related to Leap         | 117        |

|    | 8.4   | Exam           | ple of a Leap Execution        | 118        |

| 9  | Con   | clusio         | ns and Future Work             | 121        |

|    | 9.1   | Conclu         | asions                         | 121        |

|    | 9.2   | Future         | e Work                         | 122        |

| Bi | bliog | graphy         |                                | 123        |

| Ιn | dex   |                |                                | 151        |

# List of Figures

| 1.1<br>1.2 | •                                                             | 3          |

|------------|---------------------------------------------------------------|------------|

| 1.2        | Image computation.                                            | ა          |

| 2.1        | A Transition system                                           | 14         |

| 2.2        | <i>To</i> and <i>From</i> sets                                | <b>L</b> 5 |

| 2.3        | Different ways for representing the states                    | 18         |

| 2.4        | A Kripke structure model of a simple traffic light controller | 19         |

| 2.5        | Runs from the traffic light controller                        | 20         |

| 2.6        | Computation tree of the traffic light controller              | 20         |

| 2.7        | A Petri net version of the traffic light controller           | 22         |

| 2.8        | An automaton model of a digicode                              | 24         |

| 2.9        | A two bit counter                                             | 34         |

| 4.1        | A Transition system                                           | 15         |

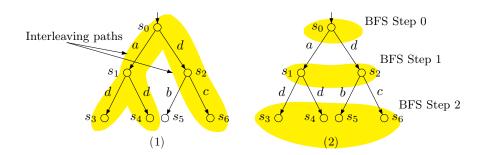

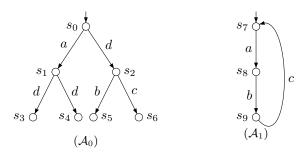

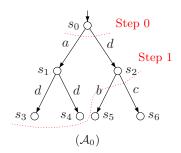

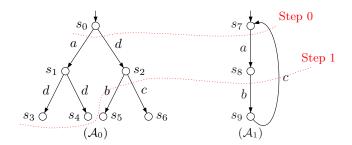

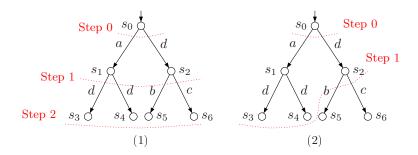

| 4.2        | Interleaving (1) vs. BFS. (2)                                 | 18         |

| 4.3        | Synchronized product of TSs                                   | 53         |

| 4.4        | Typical BFS execution for synchronized systems                | 56         |

| 4.5        | Chaining execution with event order $[a, c, b, d]$            | 59         |

| 4.6        | Chaining execution for synchronized systems                   | 60         |

| 4.7        | BFS with chaining using two different event orders            | 31         |

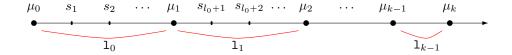

| 5.1        | Unrolling using leaps                                         | 66         |

| 5.2        | A synchronized system with idle steps                         | 37         |

| 5.3        | Leap methods for deadlock property                            | 70         |

| 5.4        | Leap methods for other reachability properties                | 72         |

| 5.5        | Different leap values                                         | 74         |

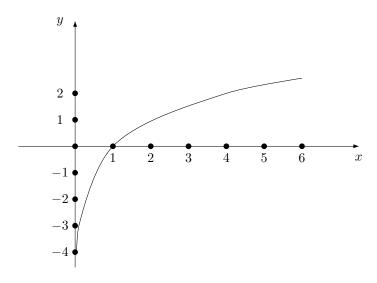

| 5.6        | Plot for the base 2 logarithmic function                      | 74         |

| 5.7        | The interpolation method with the collected points            | 77         |

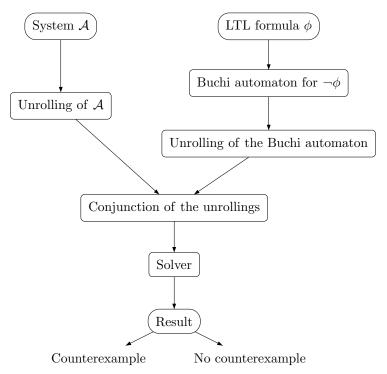

| 6.1        | Automata-theoretic approach to BMC                            | 32         |

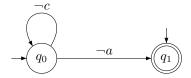

| 6.2        | A Büchi automaton                                             | 35         |

| 6.3        | A Transition-based Büchi automaton                            | 36         |

| 6.4 | TGBA for the LTL formula $(Fa \wedge F \neg a)$                 | 88  |

|-----|-----------------------------------------------------------------|-----|

| 6.5 | TGBA for the LTL formula $\phi = a \ R \ (c \lor b)$            | 91  |

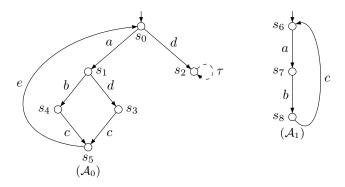

| 6.6 | A complete example: two TSs and a TGBA                          | 93  |

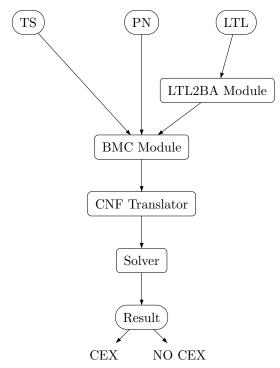

| 7.1 | BMC++ major modules                                             | 100 |

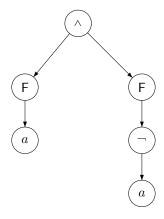

| 7.2 | The tree representation of the LTL formula $Fa \wedge F \neg a$ | 101 |

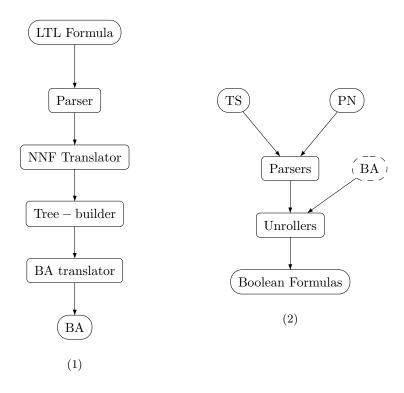

| 7.3 | Details of the LTL2BA Module (1), and the BMC Module (2)        | 102 |

| 7.4 | A transition system                                             | 103 |

| 7.5 | A Petri net.                                                    | 107 |

## List of Tables

| 2.1 | Typical CNF Translation for the gates AND, OR, and NOT | 35 |

|-----|--------------------------------------------------------|----|

| 6.1 | Tableau Rules                                          | 37 |

| 7.1 | LTL operators and their keyboard equivalents           | )( |

| 8.1 | Deadlock detection results                             | 12 |

| 8.2 | Comparison with NuSMV                                  | 13 |

| 8.3 | LTL checking results                                   | 16 |

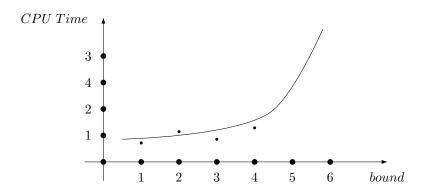

| 8.4 | Comparison of leap and standard BMC                    | 17 |

# List of Algorithms

|     | forwardReachability  |    |

|-----|----------------------|----|

| 1.2 | standardBmcAlgorithm | 7  |

| 2.1 | dpll                 | 28 |

| 2.2 | zeroSaturate         | 31 |

| 2.3 | saturate             | 32 |

| 4.1 | Bmc                  | 63 |

| 5.1 | JumpByLogarithm      | 75 |

| 5.2 | jumpByInterpolation  | 76 |

## Nomenclature

BA Büchi automata

BDD Binary decision diagrams

BMC Bounded model checking

CAD Computer-aided design

CNF Conjunctive normal form

CTL Computation tree logic

DPLL Davis-Putnam-Longeman-Loveland, name of an algorithm for solving SAT

FSM Finite state machine

LTL Linear temporal logic

NuSmv A model checking tool that has BMC capabilities

PN Petri net

SAT Boolean satisfiability problem

TGBA Transition-based generalized Büchi automata

TS Transition system

ZChaff A SAT solver

## Abstract

In this thesis we study the verification of asynchronous concurrent systems using a symbolic model checking technique called bounded model checking (BMC). BMC is a method targeted mainly at finding bugs in a system. It answers the question whether there exists an execution path, shorter than a given number, that violates a given property. Such an execution path is known as counterexample. During a BMC operation each execution path is encoded into a Boolean formula, and the problem is reduced to satisfiability checking of the formula. Therefore, the operation consists mainly in constructing a Boolean formula that is satisfiable if and only if such a counterexample exists.

We model our systems with transition systems (TSs). In particular, we are mainly interested in synchronized product of TSs. Since concurrent systems are formed by a combination of several components communicating between each other, synchronized product of TSs is well-suited to capture the behavior of such systems. The executions of concurrent systems are commonly modeled using the so-called interleaving execution, which allows only one single event to fire at each step. However, due to the complexity of such systems, performing BMC with interleaving will not only require many steps but also generate long formulas. In this work, we adopt different approaches based on breadth-first search (BFS). Our methods reduce the necessary steps, and produce smaller formulas. In a BMC operation, the translation of the model into a Boolean formula is polynomial in the size of the model, but the solving time of the Boolean formula can be exponential in the size of the formula. Therefore, our research hypothesis is that we can improve the efficiency of BMC by generating succinct formula, and by minimizing the number of necessary steps during an execution.

We introduce several BMC techniques aimed at improving the efficiency of BMC for asynchronous concurrent systems. The techniques are grouped in two main parts (i) techniques for checking reachability properties and (ii) techniques for checking other properties written in *linear temporal logic* (LTL). In addition, we also propose some methods for minimizing the number of execution steps or bounds.

We implemented all these methods in a BMC toolset. At the end of the dissertation, we will discuss the experimental results we obtained.

**Keywords:** bounded model checking, asynchronous concurrent systems, satisfiability problem, reachability properties, linear temporal logic.

## Acknowledgments

This thesis would not have been possible without the support of many people. It is a pleasure for me to thank all of them.

First, I would like to express my sincere gratitude to my supervisor Enric Pastor who offered invaluable assistance, support, and guidance throughout my work. With his great efforts to explain things clearly and simply, he helped make formal verification fun for me. He also provided encouragement and good company. I would have been lost without him.

I am indebted to all my colleagues at the Computer Architecture Department for providing a stimulating and pleasant working environment. Especially, I am grateful to Marc Solé, Josep Carmona, and Juan Lopez who spent a great deal of their time discussing with me, and gave sound advice that contributed in many ways to the accomplishment of this research project.

Special thanks to the external reviewers, Marco Peña and Robert Viladrosa who carefully read the preliminary version of this report and provided valuable suggestions and comments. Thanks also to all the members of the jury for evaluating and judging my thesis.

I would like to show my gratitude to the following institutions for funding this research: the Government of Catalonia under the scholarship FI, and the Ministry of Science and Education of Spain under the contract CICYT TIN 2007-63927.

I wish to thank all my friends, especially Nirina Rakotoarivelo, Rafael Ordonez, Manitra Raharijaona, and Fidel Pedregal Pimentel. They encouraged me and supported me from the beginning until the end, despite the long period of time I spent doing my Ph.D. thesis.

I would also like to thank my entire family for their unwavering support. Most importantly, I am very thankful to my mother, Marguerite Ravaoarivelo. She bore me, raised me, taught me, and has loved me throughout the years. To her I dedicate this thesis.

Last but not least, I would like to express my gratitude to all the people who have not been cited above but who helped me directly or indirectly with the realization of this thesis. Thank you so much everyone.

## Chapter 1

## Introduction

Complex hardware systems become more and more ubiquitous in mission critical applications such as military, satellite, and medical to name but a few. In such applications, reliability remains a primary concern because a failure that occurs during their normal operations might produce important catastrophes like loss of life or loss of money. Examples of these catastrophes include the Pentium bug [Gep95, Ade97], space launch disasters like the Mariner I [HL05] or the Ariane 5 [Har03], the Warsaw A320 crash [Lad95, CMMM95], not to mention the AT&T telephone switching failure [Ste93, Har00].

All these failures are often caused by minuscule  $bug^1$  that exists inside the software which controls the systems, or within the hardware itself. In addition, most of these systems cannot be interrupted while working, even for a few seconds a year, making it difficult to repair bugs found during their normal operations.

Therefore, manufacturers of such systems have to validate their designs, before shipping them to ward off disasters caused by undetected errors. Appropriate validation techniques are then necessary to discover bugs that would affect the use of such systems.

In general, design validation can be performed using two groups of methods: (i) simulation and testing (ii) formal verification.

In *simulation and testing*, the main purpose is to carry out some experiments before getting the product on the market. This involves introducing series of inputs into the design and checking whether the produced outputs correspond to the expected ones. Simulation and testing explore only some system behaviors and they take time to find the slightest bugs in a system. Hence, they can overlook considerable errors if the system has

<sup>&</sup>lt;sup>1</sup>Bug is a computer jargon referring to an undesirable property that makes the computer misbehave or crash. The first recorded bug was a real insect. In 1947, American mathematician and computer scientist Grace Murray Hopper (1906-1992), known also for inventing the programming language COBOL, was working on the Harvard University's Mark II computer. One day, the machine crashed. Hopper investigated and found that a moth has squeezed into one of the 17,000 relays in the machine. She removed the moth and the machine worked perfectly [Kid98, Nor05]. This is not, however the origin of the term "bug" since this term has already been used long before by other scientists, but Hopper's was the "first actual case of a bug being found" according to a note she put on her log book.

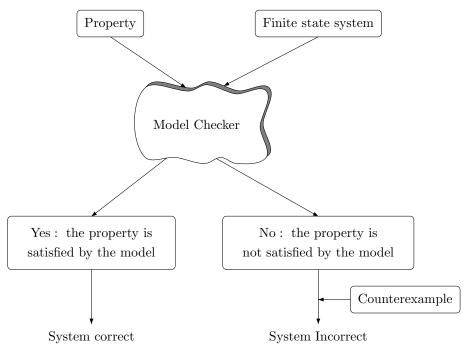

Figure 1.1: Model Checking.

huge state number. Nonetheless, many industries nowadays still use these techniques as standard ways to validate their designs.

Formal verification [Das06, Kro99], on the other hand, does not rely on direct experiments. Instead, it uses mathematical formalisms to check whether the *model* of a system satisfies a given *property*. The system is correct if this property is satisfied, otherwise it is incorrect. Formal verification offers exhaustive coverage of all system behaviors, which makes it more suitable for detecting bugs in extremely concurrent systems. There exist two main approaches to formal verification. Namely, theorem proving and model checking.

Theorem proving is a more theoretical approach. It uses mathematical axioms and proof rules to prove the correctness of a system. Hence, it can only be performed by people who have solid experience in logical reasoning. In this method, both the system and the desired property are expressed as formulas in some mathematical logic. The system is correct if a proof for the property can be constructed from the axioms of the system. The whole process is rather time-consuming, yet it is proven to be more effective for detecting software bugs in case the source code contains thousands of lines with complex logical operations [Ros05]. In addition, it has the ability to verify infinite state systems.

Model checking [CGP99, CK96, QS82] is used to verify *finite state systems*. It is fully automatic, terminates with *true* if the system is correct, or alternatively provides an execution path known as *counterexample* that shows how the system violates the given

Figure 1.2: Image computation.

property (see Figure 1.1). Counterexamples often correspond to subtle design errors and can therefore be used for debugging the system. In *symbolic model checking* [BCM<sup>+</sup>90], the system's state space is represented symbolically with Boolean encoding rather than with explicit representation.

#### 1.1 Symbolic Model Checking

#### 1.1.1 BDD-based approach

Binary decision diagram (BDD) [Bry86], which offers a compact and canonical representation of functions, is traditionally used in symbolic model checking to represent the system's state space. Numerous studies, coupled with successful practical experiments, have been done so far to exploit the performance of this technique. In particular, the model checking tool called system model verifier (SMV) [McM93], developed by McMillan in 1993, was one of the efficient tools which showed the potentiality of BDD-based approaches, and became a touchstone for other implementations. This tool has been successfully used to verify industrial designs, see e.g. [CYLR01, BLP95].

In general, BDD-based model checking relies on the approach known as *reachability* analysis which involves computing all the reachable states in the system starting from a given set and analyzing the results. Basically, there exist two fundamental variants of this approach: *forward* and *backward* methods.

#### Forward Reachability Analysis

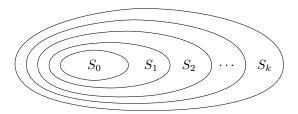

In forward reachability analysis, the goal is to determine whether a state violating an invariant property can be reached from the initial states. To achieve this goal, a reachability procedure performs repeatedly *image computation*. That is, it computes the image of the newly reached states from one iteration using a transition relation, and repeat this process until no more new states can be generated. In this case, a *least fixpoint* (lfp) is reached and the procedure stops (see Figure 1.2). The transitions and the states are represented using BDDs. The reached states are analyzed later on to determine whether any of them violates the property of interest. Formally, these images are computed as follow. Let  $S_0$  be a set of initial states and T(v, v') be a transition relation, where v and v'

denotes the current and next state variables respectively. Let us use S(v) and T(v, v') to denote the propositional formulas related to the set of states and transitions respectively. Then, the image of S(v) through T(v, v') is given as:

$$Img(S(v')) = \exists v. T(v, v') \land S(v)$$

(1.1)

Now, starting from the initial states, the least fixed point can be computed by repeatedly applying the following equation in which the final results of the set R contains all forward reached states:

$$R = lfp \ R.(S_0 \lor Img(R)) \tag{1.2}$$

For instance, assume we want to check whether a system satisfies a safety property expressing that something should be true at every state of the system. In this case, the model checker applies repeatedly image computation to determine if there is an execution path from an initial state to a state where this property fails. If such a path does not exist, then the system is correct, otherwise the system is incorrect and the path found by the model checker corresponds to a counterexample.

Algorithm 1.1 illustrates the forward reachability procedure. The set R contains all reachable states, while  $S_i$  contains the newly discovered states in each iteration. The function img() perform the image computation from  $S_i$ . The algorithm stops when  $S_i$  is empty.

```

Algorithm 1.1: forwardReachability

```

```

input : S_0 a set of initial states

output: R a set of reachable states

1 R \leftarrow \emptyset;

2 i \leftarrow 0;

3 while (S_i \neq \emptyset) do

4 R \leftarrow R \cup S_i;

5 S_{i+1} \leftarrow \operatorname{img}(S_i) \setminus R;

6 i \leftarrow i+1;

7 end

8 return R

```

Note that, for large systems, the final set R may become too big. To avoid this situation, some people perform on-the-fly check of the invariant property. That is, at each iteration the newly reached states is checked whether any of them violates the property. If the answer is positive, then the algorithm stops. This method prevents exploration through the entire state space.

#### Backward Reachability Analysis

Backward reachability is mainly used to perform diagnostic of a failure in a system. As its name suggests, it is the opposite of forward reachability. The aim in here is to know whether a specified set of target (i.e violating) states is reachable from any of the initial states. To do so, the procedure starts from the set of violating states and perform preimage computation repeatedly until a fixpoint is reached. Then, it checks if the reached set contains one of the initial states. As before, all states and transitions are encoded with BDDs. Formally a preimage computation is performed as follow. Let T(v.v') be a transition relation and  $S_t$  a set of target states. The preimage of S(v') through T(v,v') is given as:

$$PreImg(S(v)) = \exists v'. T(v, v') \land S(v')$$

(1.3)

and the least fixed point is obtained by repeatedly applying the following equation from the target set:

$$R = lfp \ R.(S_t \lor PreImg(R)) \tag{1.4}$$

The algorithm for backward reachability is similar to Algorithm 1.1. We need only to start from  $S_t$  instead of  $S_0$ . On-the-fly methods can also be applied to backward reachability in order to handle large systems.

#### State Explosion Problem

Although successful, BDD-based approaches are subject to the so-called *state explosion problem*, or the situation where the size of the state space grows exponentially beyond the available computer resources. This situation arises if the system being checked has many components that can make transitions in parallel. For that reason, certain types of designs cannot be handled efficiently with BDD-based approaches. Below, we will review briefly some interesting techniques for dealing with the state explosion problem. Namely, partial order reduction, compositional reasoning, abstraction, induction, and symmetry.

Partial Order Reduction This technique is designed for concurrent systems with communicating processes [GW94, Pel93, WW96, NG02]. With this technique, when concurrent events are independent, it suffices to consider one of them since, in this case, they all lead to the same state. Therefore, during state space exploration, only a subset of the enabled transitions is considered in each state rather than all of them. This decreases the size of the state space while preserving the properties of interest. The chosen subsets are called *ample sets* [God96, HP95], or *stubborn sets* [Val90], or *sleep sets* [God90], or *persistent sets* [God90], or also *stamper sets* [PVK01].

Compositional Reasoning This technique applies to large systems composed of parallel processes. For such systems, it is possible to divide up a given property into local

properties, each of them relates to a specific component of the system. Compositional reasoning methods [CLM89, GS90, SG90] abate the state explosion problem in the following way. Check first whether each system's component satisfies its local property, then make sure the conjunction of all local properties yields the property of interest. If all the above are verified, then the whole system satisfies the given property as well.

When the interconnections between the system's components are too complicated, a variant approach called assume-guarantee reasoning [GL94] is more appropriate. In this case, the behavior of one component hinges upon the other components' behaviors. Thus, when verifying one component, the user must make assumptions about the properties of other components. If these assumed properties are satisfied, the correctness of the entire system could be verified, in a suitable way, without generating the whole state graph.

Abstraction In this technique, the goal is to simplify the verification process by reducing the model of the system into a much simpler representation [CGL92, DGG97]. In general, the reduction consists in excluding some features of the model, by forbidding some behaviors, for example, or by merging some identical states, or by removing some data. This technique is useful especially when the original model is too large to handle by the verification tool at hand. But doing abstraction may result in a reduced model that no longer has the same behavior as the original one. Hence, the user must ensure beforehand that the chosen abstraction technique will preserve the property of interest.

Induction This method deals with parametrized systems, that is systems whose configuration depends on a certain parameter [KM95, CGJ95, WL89]. For instance, a network of n computers, or a mutual exclusion involving n processes. Here, the goal is to generalize the result, i.e. to check whether a property is satisfied by all systems in a given class. This is a hard problem. Still, in some cases, it could be resolved by generating first an invariant that represents the behavior of an arbitrary member of the class. Then, use this invariant to check the property of all class members.

**Symmetry** This technique is relevant for systems containing replicated components. It consists in replacing the system's states with different structure known as *orbit representatives* [CJEF96]. Unfortunately, finding orbit representatives also constitutes a hard problem, hence this method remains impractical in most cases.

#### 1.1.2 SAT-based Approach

Combining model checking with the Boolean satisfiability problem (SAT) is another efficient way to avoid the state explosion. Known as bounded model checking (BMC) [BCCZ99, CBRZ01, BCC $^+$ 03], this approach is mainly targeted at finding bugs in a system. More precisely, it consists in finding a counterexample of a fixed bound, say k, for a given property and constructing a Boolean formula that is satisfiable if and only if such a counterexample exists. To achieve this goal, a typical BMC algorithm works in the

following way. It first unrolls the system k times. Then, it combines the unrolled system with the negation of the given property, and encodes the whole as a Boolean formula. Finally, it calls a SAT-solver to check whether this formula is satisfiable. If the SAT-solver returns a satisfying assignment, then the system is incorrect and this assignment corresponds to a counterexample of length k. Otherwise, the SAT-solver can provide a proof of unsatisfiability. The unrolling process is polynomial in the size of the system, whereas the satisfiability check can be exponential in the size of the formula. This technique has also been successfully applied to real-world designs (see e.g. [BCRZ00, BLM01, CFF+01]).

BMC overcomes the state explosion problem because it does not use canonical representation of the state space. Furthermore, it consumes much less space than BDD-based techniques because typical SAT-solvers, used for determining the satisfiability of the constructed formula, require no more than polynomial amount of memory. Hence, it can handle huge systems with thousands of state variables, in contrast to BDD-based approaches which can only be applied to systems with, at best, hundreds of variables.

Apart from overcoming the sate explosion problem, BMC also has the following advantages: (i) The Boolean formula translation from a single unrolling can be replicated without additional analysis, thus it can be done in linear time. (ii) Due to this replication possibility, *incremental learning* is possible and is helpful in many cases. (iii) Due to the advances in SAT-solving techniques, many fast SAT-solvers are now available.

```

Algorithm 1.2: standardBmcAlgorithm

```

In practice, a standard BMC algorithm works by increasing the bound progressively to search for a deep counterexample up to a certain maximum number. At each step, the algorithm calls a SAT-solver to determine whether a counterexample exists or not for the current bound. Algorithm 1.2 illustrates this operation. It starts at bound 1 and stops when the maximum BMC length is reached or the formula becomes satisfiable. F corresponds to the formula generated at each bound by the unrolling operation. The

function solve() calls the SAT-solver to determine whether F is satisfiable.

The speed of the SAT-solver is crucial during the execution because it affects the performance of the whole BMC operation. When the bound is increased, the number of variables in the formula increases linearly, whereas the solving complexity increases exponentially. For example, when moving from a bound k to k', with k < k', the complexity increases  $2^{n.k}$  to  $2^{n.k'}$ , where n is the number of gates in the circuit. This situation implies that the deeper the exploration goes, the slower the execution.

During a BMC session, if the maximum number is reached without finding any counterexample, no conclusion can be drawn concerning the correctness of the system since the counterexample may exists at a bound beyond the maximum number. This inability to draw conclusion makes BMC somewhat incomplete compared to BDD-based approaches. Nevertheless, many techniques have been proposed so far to work around this completeness issue. We will review some of them in Chapter 3.

The standard BMC method mentioned above is well suited for synchronous systems, a kind of system in which the execution is coordinated by a clock and all variables change together at the same time. But if we apply it to asynchronous concurrent systems, a kind of system composed of many components that can communicate and work concurrently, it will fare badly. Due to the inherent interleaved nature of these systems, the number of times we have to invoke a SAT-solver will be much larger—maybe an order of magnitude. In addition, some of them tend to produce large formulas sooner. Therefore, the above-mentioned execution slowdown may appear at an early stage because not only the SAT-solver will be invoked many times, but it may also handle large formulas. Hence, these systems need more elaborate methods for handling them.

#### 1.2 Synchronous Versus Asynchronous Systems

In this section we will discuss the main differences between synchronous and asynchronous systems. We will start with the synchronous ones.

#### 1.2.1 Synchronous systems

The synchronous methodology has been used successfully for the design and implementation of safety-critical embedded systems such as flight control systems in flight-by-wire avionics and antiskidding or anticollision equipment on automobiles. They are also present in other applications such as trains, nuclear plants, and cell phones.

Basically, a synchronous circuit contains the following components:

- circuit inputs,

- gates,

- latches.

The operation in such a circuit is controlled by a global clock. All values in its storage components change simultaneously following the clock signals. During a clock cycle, each circuit input receives a random value true or false. The output of a gate is formed by a Boolean combination of its inputs. A latch corresponds to a memory unit with one input and one output. The inputs of gates and latches are connected to the inputs and outputs of other gates and latches. Consequently, the output of a latch in a given clock-cycle is a Boolean combination of inputs and outputs of latches in the previous clock-cycle. The behavior of the whole circuit is entirely predictable because each input reaches its final value before the next clock occurs. In practice, some delay may be needed for each logical operation in order to limit the speed at which the system can run. To determine the maximum safe speed, static timing analysis is often used.

#### **Advantages of Synchronous Systems**

Here are some of the most important advantages of synchronous systems.

Easier to model Synchronous systems are often modeled with *finite state machine* (FSM). To model concurrency correctly, it is sometimes necessary to use a combination of several FSMs for one system. Since synchronous models are deterministic, it is much more easier to formally reason about the models and check certain properties, especially in case of safety-critical systems.

Easier to design A synchronous circuit can be designed easily in an improvised fashion. For instance, a designer can simply define the combinational logic to compute a given function, and surround it with latches. In addition, nearly all of the most important design-related operations for synchronous systems exist in many of today's computer-aided design (CAD) tools.

#### Drawbacks of Synchronous systems

In the synchronous paradigm, time is defined as a sequence of instants between which nothing interesting happens. In each instant, some events (inputs) occur in the environment, and a reaction (output) is computed instantly by the modeled design. Therefore, despite of all the advantages we discussed above, reasoning and verification based on synchronous models are meaningful only if a completely synchronous implementation of the whole system is possible, and if we are sure that for the implemented system the reaction time (including internal communications) is negligible compared to the rate of external events. Furthermore, it is practically impossible to model a large system using synchronous models.

#### 1.2.2 Asynchronous systems

Asynchronous systems can be found in many applications, ranging from CD players to avionics systems. Their features meet the necessary requirements for assembling large-scale heterogeneous and scalable systems. Typically, they are constructed by combining several hardware components together to form a correct working system. Communication between these components is assured through *channels*, which are used both to synchronize operations and to pass data. Like their synchronous counterparts, asynchronous systems also use binary signals. However, they do not use a global clock. Instead, their components work concurrently using *handshaking* between them in order to perform the necessary synchronization, communication, and sequencing of operations. This mechanism results in a behavior similar to local clocks that are not in phase.

#### Advantages of Asynchronous Systems

Asynchronous systems have numerous advantages. We will describe some of the them.

Low power dissipation Basically, the clock in a synchronous circuit has to control all parts of the circuit including those that are not used in the current computation. For instance, even though a floating point unit on a processor may not be used in an ongoing instruction stream, the clock still has to control the unit. By contrast, for asynchronous circuits, the components are activated only when needed, so they make signal transitions only when performing some work or communicating. Because of this feature, they work fast, yet have low power dissipation.

No clock skew Clock skew refers to the difference in arrival times of the clock signal at different parts of the circuit. The absence of a global clock in synchronous circuits prevent them from having clock skew problems.

Less electromagnetic interference Electromagnetic interference (EMI) is a kind of interference caused by the high speed clock switching all over a chip at approximately the same time. Asynchronous systems generate less emission of EMI because they use local handshaking whose signals are not correlated in time.

Easing of global timing issue In systems such as synchronous microprocessors, most portions of the circuit must be carefully optimized in order to obtain the highest clock rate and to achieve better performance. On the other hand, for asynchronous systems, rarely used portions of the circuit can be left unoptimized without affecting system performance.

**Easier technology migration** Basically, integrated circuits are built using different technologies during their lifetime. For instance, early systems may be built with gate arrays, while later production may migrate to custom ICs. For asynchronous systems, there is no need to migrate all system components in order to achieve a greater performance.

Migrating only the most critical parts is sufficient. In addition, components with different delays can be substituted without altering other elements.

Automatic adaptation to physical properties The delay in a circuit can be affected by many factors including variations in fabrication, temperature, and power-supply voltage. Asynchronous systems can adapt themselves to these different factors, and will run as fast as the current physical properties allow.

#### **Drawbacks of Asynchronous Systems**

Asynchronous systems have their drawbacks, nonetheless. First of all, due to their complexity, they are more difficult to design. Next, the ordering of operations is too difficult to handle, especially for complex systems. Finally, there are not too many CAD tools devoted to asynchronous circuits. Many of the most essential operations existing in today's CAD tools such as placement, routing, partitioning, logic synthesis are either need special modifications for asynchronous systems, or are not applicable at all.

#### 1.3 Scope of This Work

The main purpose of this work is to build efficient verification techniques for asynchronous concurrent systems. Because of the pivotal roles these systems assume in a given application, designers of such systems must keep development and maintenance costs under control and meet nonfunctional constraints on the design of the system, such as cost, power, weight, or the system architecture by itself. But most importantly, they must assure their customers as well as the certification authorities that both the design and its implementation are correct. Otherwise, they may end up shipping unsafe systems to the market, and the consequences of this action would be catastrophic. To achieve this goal, designers need efficient methods and tools to assist them in verifying the correctness of the design. These methods should be built on solid mathematical foundations in order to be able to reason formally about the operation of the system.

We focus our study on BMC. We aim at developing BMC methods supported by tools for analyzing the behavior of asynchronous concurrent systems and verify their correctness, considering all the benefits and challenges in this area. BMC is traditionally used for verifying synchronous systems because the characteristics of these systems match well a BMC operation. However, in this work, we apply it to asynchronous systems. The following points explain our choice.

- There exist already numerous BDD-based methods and tools for asynchronous concurrent systems. Most of them have been successfully applied in the industry. Still, the state explosion problem limits the size of the problem they can solve. On the other hand, SAT-based methods do not have this kind of problem, thus can handle much bigger systems.

- With the success story of BMC with synchronous systems, we believe that with a little effort, it is also possible to repeat this success for asynchronous systems. For this reason, we are interesting in building verification methods and tools, based on BMC, for asynchronous systems.

- SAT-solving methods and tools continue to improve. Not only they become faster, but the size of the formulas they can handle continues to grow. Therefore, we believe that even though asynchronous systems are complex, using these state-of-the-art solvers will help to tackle the problems.

To handle asynchronous concurrent systems properly, and to tackle all the BMC problems explained in the previous section, two main related tasks should be considered. First, developing encoding techniques that provide compact Boolean formulas to be solved by a SAT-solver. Second, building efficient unrolling techniques to minimize the bound needed for finding a counterexample.

We propose in this thesis several encoding techniques for systems modeled as *transition* systems: methods for checking reachability properties as well as for checking properties expressed in *linear temporal logic* (LTL). We also propose methods for minimizing the bound during the BMC operation. We have implemented all these methods in a BMC toolset for asynchronous systems.

#### 1.4 Structure of the Thesis

The rest of this thesis is structured as follows. In Chapter 2 we give all the definitions we need throughout the report. In Chapter 3 we review most of the important BMC techniques that exist in the literature. We introduce our approaches in Chapters 4 and 6. In Chapter 7, we describe our BMC toolset. Case studies with experimentation results are shown in Chapter 8. We conclude the thesis in Chapter 9 and give some possible future directions.

## Chapter 2

## Background

In this chapter, we present the definitions and notations to be used throughout the report. We will first describe the transition system model, along with other popular formalisms for modeling concurrent systems. Next, we will explain what a property is and how to express it formally. After that, we will discuss the satisfiability problem, and review some of the most effective methods for solving it. Finally, we will show, with an example, how to use BMC to verify safety properties.

#### 2.1 Transition Systems

In order to verify the correctness of a system, it is necessary to use an appropriate formalism that can describe clearly the system's behavior. Furthermore, the model should be able to capture the properties of interest. For finite concurrent systems, the behavior is mainly determined by three elements: states, transitions, and computations. A state corresponds to a group of variables needed for describing the system at a particular instant. When an action or event occurs, the system changes from one state to another, and the values of the state before and after such an event determine a transition. A computation or also execution path is formed by an infinite sequence of states, in which two consecutive states are connected via a transition. In this section, we discuss a well-known model called transition system (TS) [Arn94], which is also the one we use in our study.

#### 2.1.1 Definitions

#### Definition 2.1.1 (Transition system)

A transition system is tuple  $A = (S, \Sigma, T, s_0)$  where

- S is a non-empty set of states;

- $\Sigma$  is a non-empty set of **events**;

- $T \subseteq S \times \Sigma \times S$  is a transition relation whose elements are called **transitions**;

14 Background

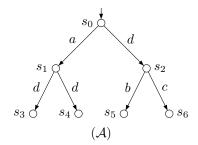

Figure 2.1: A Transition system.

-  $s_0$  is the initial state.

A transition from a state s to a state s' is written  $s \xrightarrow{e} s'$  or (s, e, s') where e denotes the event associated to the transition.

A transition system can be represented as a directed graph whose nodes correspond to the states, and the edges to the transitions. The transitions are labeled with their associated events.

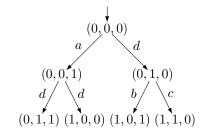

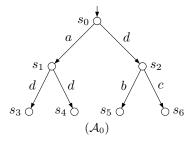

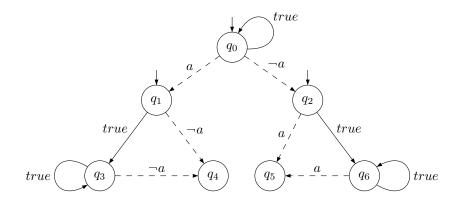

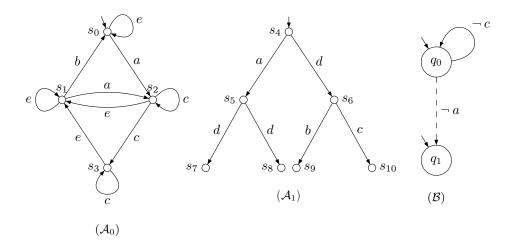

**Example 2.1.1** Figure 2.1 depicts an example of TS. We have  $\mathcal{A} = (S, \Sigma, T, so)$  where  $S = \{s_0, s_1, s_2, s_3, s_4, s_5, s_6\}$ ;  $\Sigma = \{a, b, c, d\}$ ;  $T = \{s_0 \xrightarrow{a} s_1, s_0 \xrightarrow{d} s_2, s_1 \xrightarrow{d} s_3, s_1 \xrightarrow{d} s_4, s_2 \xrightarrow{b} s_5, s_2 \xrightarrow{c} s_6\}$ .

#### Definition 2.1.2 (Enabling)

Let  $\mathcal{A} = (S, \Sigma, T, s_0)$  be a transition system, and e an event in  $\Sigma$ . e is **enabled** at state s if  $\exists s \stackrel{e}{\longrightarrow} s' \in T$ . If e is enabled, it can **fire**. The set of enabled events at state s is denoted by  $\mathcal{E}(s)$ .

#### Definition 2.1.3 (Run)

Let  $A = (S, \Sigma, T, s_0)$  be a transition system. A run or execution from a state s is a sequence of transitions

$$\sigma = s_0 \xrightarrow{e_0} s_1 \xrightarrow{e_1} \dots \xrightarrow{e_{k-1}} s_k \tag{2.1}$$

such that  $s_0 = s$  and  $\forall i \ge 0$ ,  $s_i \xrightarrow{e_i} s_{i+1} \in T$ . A state  $s_k$  is **reachable** if there exists a run from the initial state  $s_0$  to  $s_k$ .

It is, therefore, possible to construct a run from a set of states  $S_0$  to a set of states  $S_k$  denoted as  $S_0 \xrightarrow{E_0} S_1 \xrightarrow{E_1} \dots \xrightarrow{E_{k-1}} S_k$ , where  $E_i$  designs the set of events that fire from  $S_i$ .

#### Definition 2.1.4 (To Set)

Given a transition system  $\mathcal{A} = (S, \Sigma, T, s_0)$ . Let  $s \in S$  be a state. We define the set To(s) as follows:

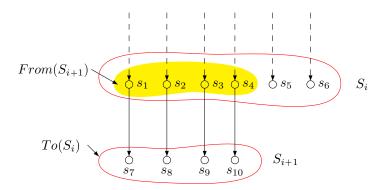

Figure 2.2: To and From sets.

$$To(s) = \{ s' \in S \mid \exists e \in \Sigma, s \xrightarrow{e} s' \in T \}$$

(2.2)

Likewise, given a set of states  $P \subset S$  the set To(P) is a set  $P' \subset S$  such that  $\forall s' \in P', \exists s \in P$  such that  $s' \in To(s)$ .

#### Definition 2.1.5 (From Set)

Given a transition system  $\mathcal{A} = (S, \Sigma, T, s_0)$ . Let  $s' \in S$  be a state. We define the set From(s') as follows:

$$From(s') = \{ s \in S \mid \exists e \in \Sigma, s \xrightarrow{e} s' \in T \}$$

(2.3)

Likewise, given a set of states  $P' \subset S$  the set From(P') is a set  $P \subset S$  such that  $\forall s' \in P', \exists s \in P, s \in From(s')$ .

Note that in a given run  $S_0 \xrightarrow{E_0} S_1 \xrightarrow{E_1} \dots \xrightarrow{E_{k-1}} S_k$ , we always have  $To(S_i) = S_{i+1}$ , but sometimes we may have  $From(S_{i+1}) \neq S_i$ . This situation happens when some of the states in  $S_i$  has no outgoing transitions (see Figure 2.2).

#### 2.1.2 Symbolic Representation

To represent transition systems symbolically, we use *Boolean algebras* [Kop89]. The representation is needed when we construct the Boolean formulas during the BMC unrolling operation. We will start this section by describing Boolean algebras, then show how to use them for representing a transition system.

#### Definition 2.1.6 (Boolean Algebra)

A Boolean algebra is a tuple (B, +, ., 0, 1), where B is a set; + an . are binary operators on B satisfying the commutative and distributive law; 0 and 1 are elements of B representing the neutral element for + and  $\cdot$  respectively. i.e.,  $\forall b \in B, b + 0 = b$  and  $b \cdot 1 = b$ .

Each element  $b \in B$  has a complement  $\overline{b} \in B$  such that  $b + \overline{b} = 1$  and  $b \cdot \overline{b} = 0$ .

16 Background

#### Definition 2.1.7 (Boolean Function)

A Boolean function is an n-variable logic function  $f : \mathbb{B}^n \to \mathbb{B}$ , where  $\mathbb{B} = \{0, 1\}$ , and f transforms each element  $(v_0, \dots, v_{n-1}) \in \mathbb{B}^n$  into an element of  $\mathbb{B}$ .

A Boolean function f is a zero function if  $f(v_0, \ldots, v_{n-1}) = 0$ ,  $\forall (v_0, \ldots, v_{n-1}) \in \mathbb{B}^n$ . Likewise, a Boolean function f is a one function if  $f(v_0, \ldots, v_{n-1}) = 1$ ,  $\forall (v_0, \ldots, v_{n-1}) \in \mathbb{B}^n$ .

Each element of  $\mathbb{B}^n$  is called vertex. A literal is either a variable  $v_i$  or its complement  $\overline{v}_i$ . A cube c is a set of literals, such that if  $v_i \in c$  then  $\overline{v}_i \notin c$  and vice versa.

#### Example 2.1.2 Below are some interesting examples of Boolean algebras.

- $(\mathbb{B}, \vee, \wedge, 0, 1)$ , where  $\mathbb{B} = \{0, 1\}$ ;  $\vee$  and  $\wedge$  correspond to the logical operators OR and AND respectively.

- $(F_n(\mathbb{B}), +, ., 0, 1)$ , where  $F_n(\mathbb{B})$  is the set of *n*-variable logic functions on  $\mathbb{B}$ ; + and . represent the addition and multiplication of *n*-variable logic functions respectively; 0 and 1 correspond to the *zero* and *one* functions respectively.

- $(2^S, \cup, \cap, \emptyset, S)$ , where S is a set;  $\cup$  and  $\cap$  correspond to the set operators union and intersection respectively.

We will now give a symbolic representation of a transition system using Boolean algebra. Given a TS  $\mathcal{A} = (S, \Sigma, T, s_0)$ . We can then build a Boolean algebra  $(2^S, \cup, \cap, \emptyset, S)$  from the set of states S. However, since in BMC, we are dealing with Boolean variables rather than sets, we need to find a way to map each state in S into Boolean variables. In this way, we will have an encoding that reasons in terms of logic operators such as  $\vee$  and  $\wedge$ , rather than set operators such as  $\cup$  and  $\cap$ .

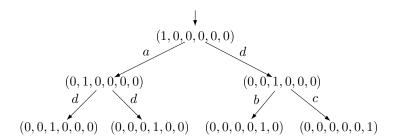

The mapping can be done as follows. We represent each state  $s \in S$  by en encoding function  $\mathcal{Q}: S \to \mathbb{B}^n$  such that  $n \geq \lceil \log_2(|S|) \rceil$  and  $\mathbb{B} = \{0,1\}$ . That is, given a set of Boolean variables  $V = \{v_0, \ldots, v_{n-1}\}$  each state  $s \in S$  is encoded into a vertex  $(v_0, \ldots, v_{n-1}) \in \mathbb{B}^n$ . We choose n = |S|, and for each state, all variables in its associated vertex equal zero except for the one which has the same index as the state. i.e. given a state  $s_i$ , we have:

$$s_i \leftrightarrow (v_0 = 0, \dots, v_i = 1, \dots, v_{n-1} = 0)$$

(2.4)

**Example 2.1.3** Assume |S| = 4. Then, we have n = 4, i.e  $V = \{v_0, v_1, v_2, v_3\}$ , and each state is mapped as follows  $s_0 \leftrightarrow (1, 0, 0, 0), s_1 \leftrightarrow (0, 1, 0, 0), s_2 \leftrightarrow (0, 0, 1, 0), s_3 \leftrightarrow (0, 0, 0, 1)$ .

Any set of states  $P \subset S$  can be represented by a *characteristic (Boolean) function*  $\mathcal{X}_P : \mathbb{B}^n \to \mathbb{B}$  that evaluates to 1 for those vertices in  $\mathbb{B}^n$  that correspond to states in P, encoded using  $\mathcal{Q}$ .

Using the state encoding above, the characteristic function of a set of states P can be expressed by the product of those variables that evaluate to 1 for each state in P.

Formally, we have:

$$\mathcal{X}_P = \bigwedge_{s_i \in P} v_i \tag{2.5}$$

This kind of characteristic function is much common in Petri net-based methods such as the one in [OTK04], but in this work, we apply it to transition systems.

**Example 2.1.4** As an example, consider the TS  $\mathcal{A}$  depicted in Figure 2.1. We have:

$$\mathcal{X}_{\{s_0,s_1,s_2\}} = v_0 \wedge v_1 \wedge v_2; \quad \mathcal{X}_{\{s_3\}} = v_3;$$

It is also possible to represent each state using the binary number equivalent to the state's index. This representation requires at least  $log_2(|S|)$  Boolean variables. For instance, assume |S|=8, then we need  $n=log_2(8)=3$  variables to represent each state, i.e.  $V=\{v_0,v_1,v_2\}$ . In binary number with three variables, we have 0=000, 1=001, 2=010, 3=011, etc. Thus, each state is mapped as follows  $s_0 \leftrightarrow (0,0,0)$ ,  $s_1 \leftrightarrow (0,0,1)$ ,  $s_2 \leftrightarrow (0,1,0)$ ,  $s_3 \leftrightarrow (0,1,1)$ , etc. For each state, the number of variables that have the value 1 varies from 0 to n. Therefore, the characteristic function  $\mathcal{X}_P$  given in equation (2.5) does not apply for this representation. Rather, it is defined as follows. Assume we have a set of states  $P=\{s_0,s_1,s_2\}$ , and n=3. Then the function  $\mathcal{X}_P$  is given as  $\mathcal{X}_P=(\overline{v}_0\wedge\overline{v}_1\wedge\overline{v}_2)\vee(\overline{v}_0\wedge v_1\wedge\overline{v}_2)\vee(\overline{v}_0\wedge v_1\wedge v_2)$ . As we can see, the derived Boolean formula is larger than the one in Example 2.1.4. Hence, this representation is not quite appropriate for SAT-based approaches because it will give extra work to the solving process. It is much more common in BDD-based methods (see e.g. [Pen03]). Figure 2.3 depicts the difference between these two representations.

# 2.2 Other Models for Concurrent Systems

In this section, we discuss other important formalisms for modeling concurrent systems. Namely, *Kripke structure*, *Petri nets*, and *automata*.

# 2.2.1 Kripke Structure

A Kripke structure [CGP99] is a formalism used for describing the behavior of reactive systems, i.e. systems that interact frequently with their environment. It is a graph-based model, whose nodes represent the system's states and whose edges represent the transitions between states. This formalism also uses a labeling function that maps each node with a set of properties that are true in the corresponding state (See Figure 2.4). Below is a formal definition of a Kripke structure.

Representation appropriate for BDD.

Representation appropriate for SAT.

Figure 2.3: Different ways for representing the states.

# Definition 2.2.1 (Kripke Structure)

A Kripke Structure is a tuple  $\mathcal{M} = (S, I, T, \ell)$  where:

- S is a finite set of states;

- $I \subseteq S$  is the set of initial states

- $T \subseteq S \times S$  is a transition relation between states;

- $\ell: S \to 2^{AP}$  is a **labeling** function that labels each state with the set of atomic propositions (AP) true in that state.

# Definition 2.2.2 (Paths, Runs)

A path from a state s is an infinite sequence of states  $\pi = s_0 s_1 s_2 \dots$  such that  $s_0 = s$  and  $(s_i, s_{i+1}) \in T$  for all  $i \ge 0$ . The set of all paths starting from a state s is denoted  $\Pi(s)$ .

A run is a path that starts from an initial state. The set of runs of  $\mathcal{M}$  is defined as  $\Pi(\mathcal{M}) = \bigcup_{s \in I} \Pi(s)$ .

A run constitutes a possible behavior of  $\mathcal{M}$  and  $\Pi(\mathcal{M})$  is called the **linear-time** behavior of  $\mathcal{M}$ .

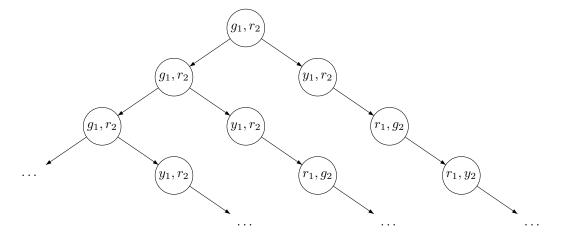

# Definition 2.2.3 (Computation Tree)

A tree rooted at a state s is the infinite tree T(s) obtained by unfolding  $\mathcal{M}$  from s.

Figure 2.4: A Kripke structure model of a simple traffic light controller.

A computation tree is a tree starting from an initial state. The set of computation trees of  $\mathcal{M}$  is defined as  $T(\mathcal{M}) = \{T(s) \mid s \in I\}$ , it shows all possible executions in  $\mathcal{M}$  starting from an initial state.  $T(\mathcal{M})$  is also called the **branching-time behavior** of  $\mathcal{M}$ .

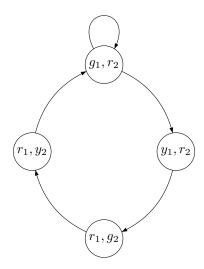

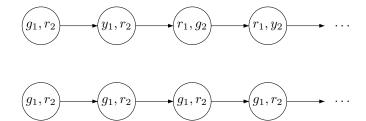

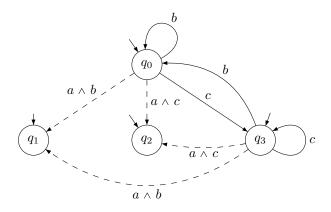

Example 2.2.1 To illustrate the Kripke structure model, let us take a simple and typical example: a controller that operates the traffic lights at an intersection between a busy highway and a farm road. The controller is designed as follows. A sensor detects the presence of a car on the farm road in either direction. By default, the highway light remains green and the farm light remains red until a car is detected by the sensor on the farm road. In this case, the light on the highway turns yellow, for a short period of time, before switching into red. Once the highway light becomes red, the light on the farm road changes into green to allow its traffic to move, and the sensor is disabled. After a time interval long enough for a few cars to pass on the farm road, its light turns yellow momentarily. Then both lights switch back to the default position, and the sensor is again enabled.

Let us associate the highway with a variable called  $road_1$  and the farm road with  $road_2$ . Assume that for each  $road_i$  we have a set of atomic propositions  $L_i = \{g_i, y_i, r_i\}$  such that:

-  $g_i$ : the light is green on  $road_i$ ,

-  $y_i$ : the light is yellow on  $road_i$ ,

-  $r_i$ : the light is red on  $road_i$ .

Figure 2.5: Runs from the traffic light controller.

Figure 2.6: Computation tree of the traffic light controller.

Since we are only concerned with the changes of lights on both roads, we will neglect the notion of time. Now, according to the design of our controller, we can build the Kripke structure  $\mathcal{M} = (S, I, T, \ell)$  where:

- $S = L_1 \times L_2$

- $I = \{(g_1, r_2)\}$

- $T = \{((g_1, r_2), (y_1, r_2)), ((y_1, r_2), (r_1, g_2)), ((r_1, g_2), (r_1, y_2)), ((r_1, y_2), (g_1, r_2)), ((g_1, r_2), (g_1, r_2))\}$

- $\ell(g_1, r_2) = \{g_1, r_2\}, \ \ell(y_1, r_2) = \{y_1, r_2\}, \ \ell(r_1, g_2) = \{r_1, g_2\},$  and  $\ell(r_1, y_2) = \{r_1, y_2\}$

- From the initial state  $(g_1, r_2)$  the model has a path  $\pi$  defined as:  $\pi = (g_1, r_2) (y_1, r_2) (r_1, g_2) (r_1, y_2) (g_1, r_2) (g_1, r_2) \dots$

The graphical representation of the model is depicted in Figure 2.4. Examples of runs and a computation tree are shown in Figure 2.5 and 2.6 respectively.

### 2.2.2 Petri Nets

A Petri net [Pet81, Rei85, Mur89] is a graphical as well as mathematical modeling tool invented in 1962 by A. Petri [Pet62, Pet66]. It has a simple, yet powerful representation comparable to flow charts, block diagrams, and networks. Moreover, through its mathematical nature, it is possible to generate state equations that represent the system's behavior. Petri nets can be used for describing numerous classes of systems, including software [BE77], computer systems [ACA78, KL82], communication networks [BT82, Dia87], process control systems [BM86, DS83], and manufacturing systems [Des89, ZDR92, BK86], just to name a few.

To model all these systems efficiently, Petri nets exist in different types including colored Petri nets [Jen97], high level Petri nets [JR91], timed Petri nets [Zub80, Wan98], and Stochastic Petri nets [MBC+98, BK02, Haa02]. In this report, we are concerned only with "classical" Petri nets. It is defined formally as follows.

# Definition 2.2.4 (Petri Net)

A Petri net is a tuple  $\mathcal{N} = (P, T, F, M_0)$  where:

- P is a set of places;

- T a set of transitions;

- F a function  $(P \times T) \cup (T \times P) \rightarrow \{0, 1\}$ ;

- $M_0$  is the initial marking.

The sets P and T are disjoint, and their elements are called **nodes**. An **arc** exists from node x to node y if F(x,y)=1. The set  ${}^{\bullet}x=\{y\in P\cup T\mid F(y,x)=1\}$  denotes the **preset** of a node x. The set  $x^{\bullet}=\{y\in P\cup T\mid F(x,y)=1\}$  denotes the **postset** of a node x.

For a Petri net  $\mathcal{N}$  we have:  $Min(\mathcal{N}) = \{x \in P \mid {}^{\bullet}x = \emptyset\} \text{ and } Max(\mathcal{N}) = \{x \in P \mid x^{\bullet} = \emptyset\}.$

# Definition 2.2.5 (Marking)

A marking M of a Petri net  $\mathcal{N} = (P, T, F, M_0)$  is a mapping of P to the natural numbers  $\mathbb{N}$ , i.e.  $M: P \to \mathbb{N}$ . M can be identified with the multiset containing M(p) copies of P for each  $p \in P$ .

Graphically, transitions and places are represented with rectangles and circles, respectively. Tokens inside places indicates that they hold a marking.

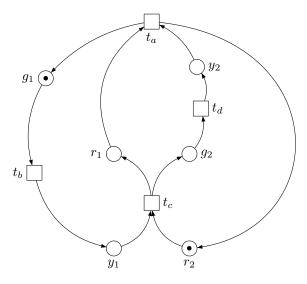

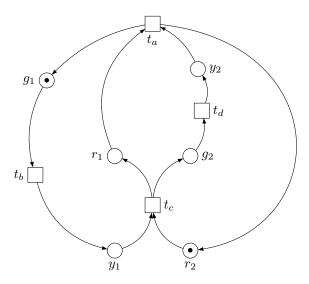

**Example 2.2.2** Figure 2.7 depicts a Petri net version of the traffic light controller described in Example 2.2.1. Formally, this Petri net can be represented as  $\mathcal{N} = (P, T, F, M_0)$ , where:

```

- P = \{q_1, y_1, r_1, q_2, y_2, r_2\},\

```

Figure 2.7: A Petri net version of the traffic light controller.

- $T = \{t_a, t_b, t_c, t_d\},\$

- $M_0 = \{g_1, r_2\}.$

# 2.2.3 Automata

Automata [Hro04, Sip97, HMU01, Koz97, Kel95] is the simplest computing model in computer science. It is used for describing finite state machines, i.e. a system that, given a set of input symbols, evolves through a series of states following a transition function. The automaton reads the input symbols one by one until there is nothing left. The next state is determined by the current symbol as well as the current state. When all the symbols are read, the automaton stops. If it stops in one of the states called accepting states, it is said to accept the input. Otherwise, it rejects the input.

As in the Kripke structure model, states are represented graphically with circles, while transitions are depicted as arrows. Each transition is labeled with the current symbol. An incoming arrow without origin identifies the initial state. Accepting states are marked with a double circle (see Figure 2.8).

Automata can be classified into different types depending on the kind of input they accept. We will only focus on *finite automata*. For the other classes, see e.g. [AD94] and the references cited above. Applications of automata to model checking can be found in [BBF<sup>+</sup>99, CGP99].

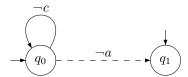

## Definition 2.2.6 (Finite Automata)

A finite automata is a tuple  $A = (Q, \Sigma, \delta, q_0, F)$  such that:

- Q is a finite set of states;

- $\Sigma$  an alphabet called, the **input alphabet**;

- $\delta: Q \times \Sigma \longrightarrow Q$  is the transition function;

- $q_0 \in Q$  is the initial state;

- $F \subseteq Q$  is the set of accepting states.

# Definition 2.2.7 (Language Accepted by an Automaton)

Let  $\mathcal{A} = (Q, \Sigma, \delta, q_0, F)$  be an automaton and  $w = e_1 e_2 ... e_n$  a word (i.e. a sequence of symbols) over  $\Sigma^*$ .

The automaton A accepts w if there exists a sequence of states  $r_0, r_1, ..., r_n$  in Q satisfying the following three conditions:

- $-r_0=q_0,$

- $\delta(r_i, e_{i+1}) = r_{i+1}$ , for  $0 \le i \le n-1$ , and

- $r_n \in F$ .

The language  $\mathcal{L}(A)$  accepted by  $\mathcal{A}$  is defined as

$$\mathcal{L}(A) = \{ w \in \Sigma^* \mid \mathcal{A} \ accepts \ w \}$$

(2.6)

which corresponds to the set of all words accepted by A.

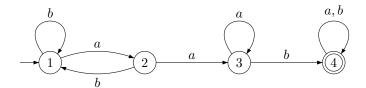

**Example 2.2.3** To illustrate the use of automata let us take a typical example: a digicode that controls the opening of building doors. This example is a simplified version of the one in  $[BBF^+99]$ . We assume that only two keys are available, a and b. The door opens upon keying in the sequence aab, regardless of any previous try. We can model the digicode using an automaton with 4 states and 8 transitions as in Figure 2.8.

The automaton can be described formally by writing  $\mathcal{A} = (Q, \Sigma, \delta, q_0, F)$ , where

- $Q = \{1, 2, 3, 4\}$

- $-q_0 = 1$

- $\delta(1,b) = 1$ ;  $\delta(1,a) = 2$ ;  $\delta(2,a) = 3$ ;  $\delta(2,b) = 1$ ;  $\delta(3,a) = 3$ ;  $\delta(3,b) = 4$ ;  $\delta(4,a) = 4$ ;  $\delta(4,b) = 4$ ;

- $-F = \{4\}.$

$\mathcal{A}$  accepts all inputs containing the string aab.

Figure 2.8: An automaton model of a digicode.

# 2.3 Linear Temporal Logic

Temporal logic [Eme90, CW96] is a form of logic used for describing the behavior of concurrent systems. It is aimed at expressing succession of events without mentioning time explicitly. It uses simple and clear notations, called temporal operators, that correspond roughly to words in a natural language such as until, next, and eventually. To express properties of states, the logic also uses atomic propositions combined with Boolean connectives such as  $\neg$ ,  $\wedge$ , and  $\vee$ .

In this section, we will focus on a temporal logic called *linear temporal logic* (LTL) [GPSS80, Lam80,  $BBF^+99$ ] which uses the following temporal operators:

- X ("next") indicates that the next state satisfies a property;

- F ("in the future or eventually") specifies that a future state on the path will satisfy a property;

- G ("globally or always") implies that a property will hold at all the future states in the path;

- U ("until") relates two properties. It states that a property holds along the path until a second property is verified.

- R ("release") is the logical dual of U. It requires that the second property holds along

the path up to the first state where the first property holds (or forever if such a state

does not exist).

Let P be a set of atomic propositions. The syntax and semantics of an LTL formula is given by the following definitions.

## Definition 2.3.1 (Syntax)

The set of LTL formulas on the set P is defined by the grammar  $\psi = p | \neg \psi | \psi_1 \wedge \psi_2 | \psi_1 \vee \psi_2 | X\psi | \psi_1 U \psi_2$ , where p ranges over P.

## Definition 2.3.2 (semantics)

Let  $\xi = u_0 u_1 u_2 \dots$  be an infinite word over the alphabet  $2^P$ . Let  $\psi$  be an LTL formula. In the semantics below,  $\xi \models \psi$  means  $\xi$  models  $\psi$ . We also define  $\xi(i) = u_i$  and  $\xi^i = u_i u_{i+1} \dots$  for  $i \in \mathbb{N}$ . The semantics of LTL is then given as follows:

- $-\xi \models p \text{ iff } p \in \xi(0), \text{ for } p \in P$

- $\xi \vDash \psi_1 \land \psi_2$  iff  $\xi \vDash \psi_1$  and  $\xi \vDash \psi_2$ ,

- $\xi \vDash \psi_1 \lor \psi_2$  iff  $\xi \vDash \psi_1$  or  $\xi \vDash \psi_2$ ,

- $\xi \models X \psi \text{ iff } \xi^1 \models \psi$ ,

$$-\xi \models \psi_1 \ U \psi_2 \text{ if } \exists i \ [\xi^i \models \psi_2 \text{ and } \forall j, \ j < i \text{ we have } \xi^j \models \psi_1],$$

We will also use the abbreviations  $true = p \vee \neg p$  and  $false = \neg true$ . The temporal operators F, G, and R are derived from the above definition as follows:

$$\mathsf{F}\psi = true\,\mathsf{U}\,\psi \tag{2.7}$$

$$\mathsf{G}\psi = false\,\mathsf{R}\,\psi \tag{2.8}$$

$$\psi_1 \mathsf{R} \psi_2 = \neg (\neg \psi_1 \mathsf{U} \neg \psi_2) \tag{2.9}$$

## **Example 2.3.1** Let us give some examples of LTL formula:

- G(barOpen U midnight) reads "it is always true that the bar opens until midnight,"

- X(ourTrain) reads "our train will come just next,"

- $\mathsf{G}\neg(critSec1 \land critSec2)$  reads "both processes will never be in their critical section at the same time,"

- $G(Req \rightarrow FSat)$  reads "any request will eventually be satisfied."

For concurrent systems, the next-time operator X does not have significant meaning because, in these types of systems, it is not really important to make a distinction between one execution step and two or more subsequent steps. These steps are considered to be observationally equivalent, especially for high level abstract specifications. For that reason, some researchers do not include this operator when they study LTL with concurrent systems (e.g. [Sor02]). The resulted logic is often known as LTL-X. In [Lam83], Lamport gives a detailed explanation as to why the next-time operator can be omitted in temporal logic.

Some people also focus their study on the logic known as PLTL which is a type of LTL combined with past operators such as Y (yesterday), O (once), and H (historically) [BC03, BHJ<sup>+</sup>06]. In theoretical point of view, there is no big difference between PLTL and future-only LTL since they both have the same degree of expressiveness. In practice, however, past operators can be more useful as they keep specifications short and simple. Hence, they can help model checker users to formulate the desired properties in a more succinct and natural way.

### **Negative Normal Form**

Many LTL-based model checking methods require the formula to be written into negative normal form (NNF)—i.e. a formula in which every negation appears only before a literal—using the operators  $\vee$ ,  $\wedge$  X, U, and R. NNF formulas can be obtained by applying the following equivalences:

$$true \equiv p \vee \neg p \tag{2.10}$$

$$false \equiv \neg true$$

(2.11)

$$\psi_1 \wedge \psi_2 \equiv \neg(\neg \psi_1 \vee \neg \psi_2) \tag{2.12}$$

$$\psi_1 \mathsf{R} \psi_2 \equiv \neg(\neg \psi_1 \mathsf{U} \neg \psi_2) \tag{2.13}$$

$$F \psi \equiv true \cup \psi \tag{2.14}$$

$$\mathsf{G}\psi \quad \equiv \quad \neg \; \mathsf{F} \; \neg \psi \tag{2.15}$$

### Logic for Nondeterministic Choices

The logic LTL can only describe events along a single computation path. Therefore, it cannot express the possibility of nondeterministic choices that may exist along an execution (run) at some instants. Because of this feature, LTL formulas are also called *path formulas*. To express nondeterministic choices, one can use the logic known as *computation tree logic* (CTL) [EH86, CES86] whose formulas may contain the following path quantifiers:

- A, known as universal path quantifier, suggests that a property is satisfied by all the computation paths starting from the current state;

- E, known as existential path quantifier, illustrates that there exists a computation path from the current state that satisfies a property.

**Example 2.3.2** To see the difference between CTL and LTL representations, let us take again one of the formulas from Example 2.3.1. In LTL, the statement "both processes will never be in their critical section at the same time," is expressed as  $AG\neg(critSec1 \land critSec2)$

More examples of properties expressed in temporal logic can be found in [BBF<sup>+</sup>99, Pnu<sup>77</sup>]. The complexity of temporal logic with model checking is discussed in [Shn<sup>02</sup>, Sa<sup>85</sup>].

# 2.4 Satisfiability Problem

The Boolean satisfiability problem (SAT) is a decision problem of finding if there exists some assignment of the values 0 and 1 to the variables in a Boolean formula that makes it evaluate to 1 (true). If this assignment exists, the formula is said to be satisfiable.

The formula to be solved is often written in *conjunctive normal form* (CNF), that is a conjunction of clauses with disjunctive literals as in the following example.

**Example 2.4.1** The CNF formula  $(x_1 \lor \neg x_2 \lor x_3) \land (x_1 \lor x_3) \land (\neg x_2 \lor \neg x_3)$  has the satisfying assignment  $x_1 = 1$ ,  $x_2 = 1$ ,  $x_3 = 0$ .

SAT has been applied to many fields in computer science including problems in electronic design automation (EDA) [FDK98, CG96, DKMW93, SSA91], microprocessor verification [VB01], field-programmable gate array (FPGA) layout [NASR04], automatic test pattern generation (ATPG) [SBSV96, TGH97], to name but a few. (See [GPFW97] for a complete list of applications that can be formulated as SAT.)

Although, SAT belongs to the class of NP-complete problems [Coo71], numerous studies have been conducted to find better algorithms and methods for it. Some of them are software-related approaches [GPD97], while others consist in customizing the hardware itself to match the requirements of SAT [AS97, SYSN01, SdBF04]. As a result, many practical SAT instances can now be solved in minutes, or even seconds on a regular computer. But since no one has ever proven that all SAT problems can be solved in polynomial time, there must be out there some SAT instance which takes huge amount of time to solve. Note that, interesting SAT benchmarks are available online at [Vel, DIM, SAT]. Benchmarks designed especially for BMC can also be found in [Zar05, Zar04].

In practice, there exist two classes of algorithms for solving SAT: *incomplete* and *complete algorithms*. Based on heuristic search algorithms, incomplete algorithms can provide results very fast. Still, they cannot prove unsatisfiability and, in some cases, terminate without giving any result at all. For that reason, most state-of-the-art SAT solvers use complete algorithms which can always lead to a result and are able to prove unsatisfiability. We will describe two well-known algorithms for solving SAT. First, a complete algorithm known as DPLL . Second, an incomplete one invented by Stålmarck.

## 2.4.1 DPLL Algorithm

Invented by Martin Davis, Hilary Putnam, Goerge Longeman, and Donald Loveland in 1962 [DLL62, DP60], DPLL accepts as input Boolean formulas written in CNF. It is a backtracking search that relies on the following rules: *unit clause rule*, *implication*, and *Boolean constraint propagation*.

**Unit Clause Rule** A Clause in which there is only one unassigned literal is called *unit clause*. If the rest of the literals in that clause have the value 0, then the unassigned literal must take the value 1 to make the clause satisfiable.