| Tesis doctoral |  |

|----------------|--|

|                |  |

Departament d'Enginyeria Electrònica

# Evaluation of die attach materials for high temperature power electronics appictions and analysis of the Ag particles sintering solution

Luis Alberto Navarro Melchor

Xavier Jorda Sanuy Xavier Perpiña Directores

Gabriel Abadal Berini Tutor

# **Contents**

| Abstract                                                        |     |  |  |

|-----------------------------------------------------------------|-----|--|--|

| Resumen                                                         | iii |  |  |

| Resum                                                           | v   |  |  |

|                                                                 |     |  |  |

| CHAPTER 1 Introduction and Motivation                           | 1   |  |  |

| 1.1. Introduction                                               | 1   |  |  |

| 1.2. Motivation                                                 | 1   |  |  |

| 1.3. Objectives                                                 | 3   |  |  |

| 1.4. Organization and Brief Description of this Thesis          | 3   |  |  |

| 1.5. Conclusions                                                | 5   |  |  |

| 1.6. References                                                 | 5   |  |  |

| CHAPTER 2 Power Electronics Packaging Review                    | 7   |  |  |

| 2.1. Introduction                                               | 7   |  |  |

| 2.2. Power Electronics                                          | 7   |  |  |

| 2.2.1. Semiconductor Devices and Power Electronics Applications | 9   |  |  |

| 2.3. Power Electronics Packaging                                | 13  |  |  |

| 2.3.1 Typical Power Electronics Package Structure               | 14  |  |  |

| 2.3.2. Advanced Power Packaging Solutions                       | 18  |  |  |

| 2.3.2.1. Pressure Contact Assembly Structure (Press-Pack)       | 18  |  |  |

| 2.3.2.2. Spring Pressure Contacts                               | 19  |  |  |

| 2.3.2.3. Deposited Metallization Technologies                   | 20  |  |  |

| 2.3.2.4. Thinpack Technology                                    | 22  |  |  |

| 2.3.2.5. Area Array or Bumping Interconnection Technologies     | 22  |  |  |

| 2.3.3 High Temperature Power Electronics Packaging              | 23  |  |  |

| 2.4 Conclusions                                                 | 25  |  |  |

| 2.5. References                                                 | 27  |  |  |

| CHAPTER 3 Ag Nano-Particles Sintering as Die-Attach Solution    | 31  |  |  |

| 3.1. Introduction                                               | 31  |  |  |

| 3.2. The Die-Attach Layer in Power Electronics Assemblies       |     |  |  |

| 3.3. Methods for the Assessment of Die-Attach Layers                      | 35   |

|---------------------------------------------------------------------------|------|

| 3.4. Ag Nano-Particles Sintering for Die-Attach Applications              | 46   |

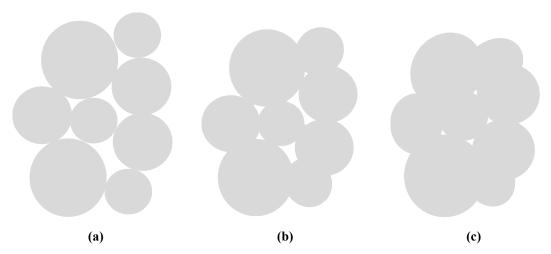

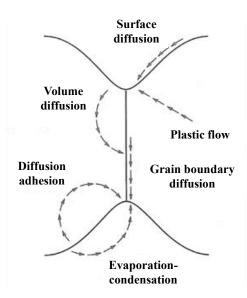

| 3.4.1. Sintering Physical Basis                                           | 47   |

| 3.4.1.1 Geometric Stages of Sintering                                     | 48   |

| 3.4.1.2. Sintering Mechanisms                                             | 50   |

| 3.4.1.3. Sintering Types                                                  | 52   |

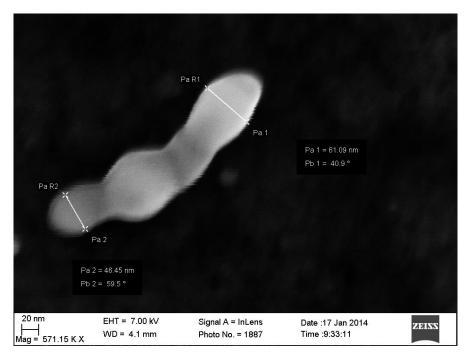

| 3.4.1.4. Particle Influence on Sintering for Die-Attach Applications      | 54   |

| 3.4.2. Ag Nano-Particles Sintering Pastes for Die-Attach Applications     | 59   |

| 3.5. Conclusions                                                          | 62   |

| 3.6. References                                                           | 62   |

| CHAPTER 4 Development of Ag Nano-Particles Sintering Process              | 69   |

| 4.1. Introduction                                                         | 69   |

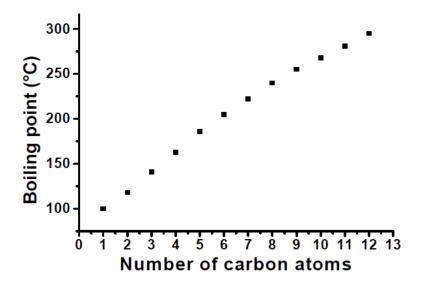

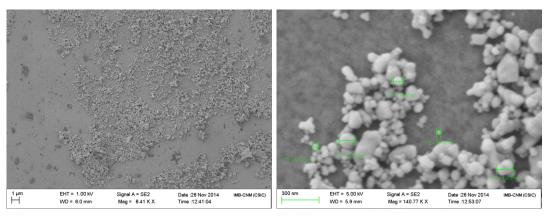

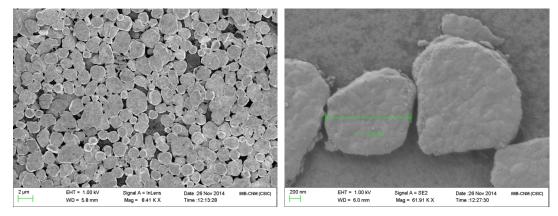

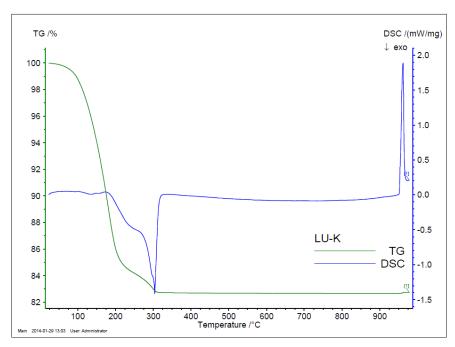

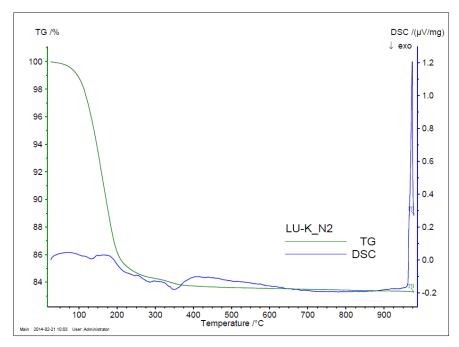

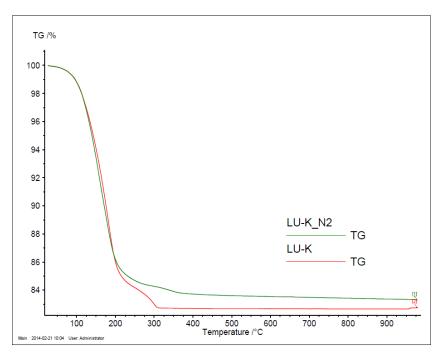

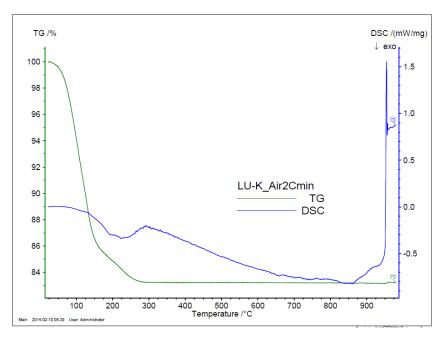

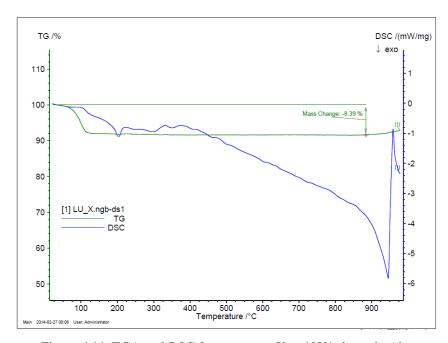

| 4.2. Ag Nano-Particles Paste Characterization                             | 69   |

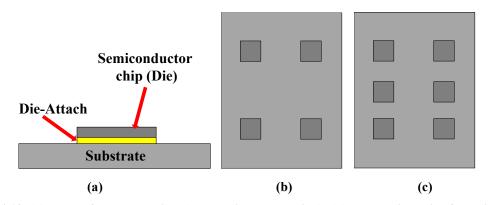

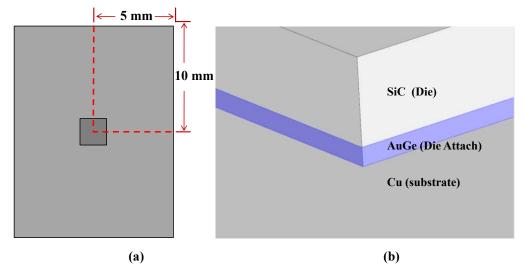

| 4.3. Test Vehicle Development for Die-Attach Assessment                   | 77   |

| 4.3.1. Devices used for Die-Attach Assessment                             | 78   |

| 4.3.2. Substrates used for Die-Attach Assessment                          | 80   |

| 4.4. Sintering Process and Experimental set-up for Manufacturing Sintered |      |

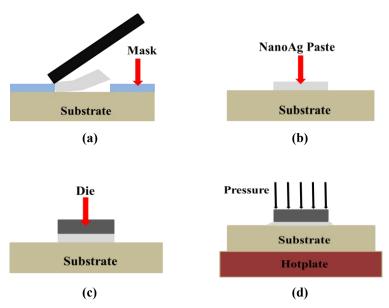

| Die-Attach Layers based on Ag Particles                                   | 83   |

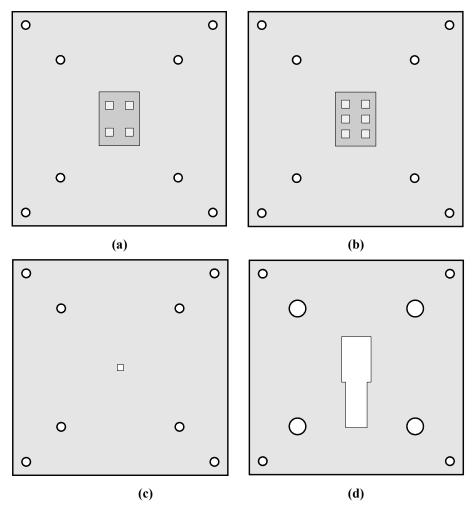

| 4.4.1. Screen Printing Methodology                                        | 85   |

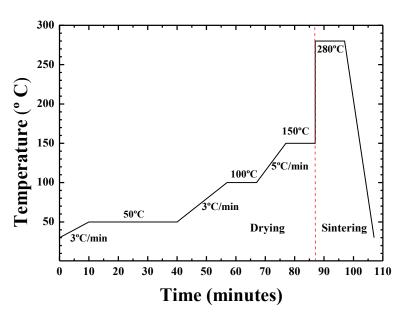

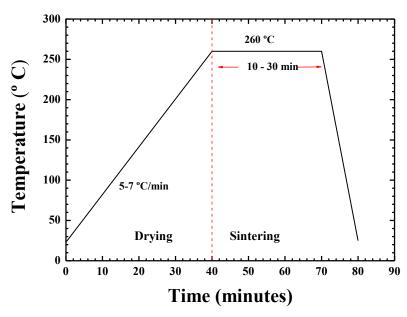

| 4.4.2. Drying Process                                                     | 86   |

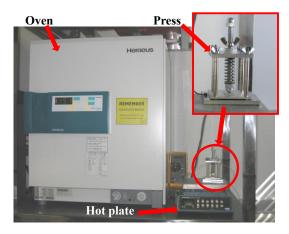

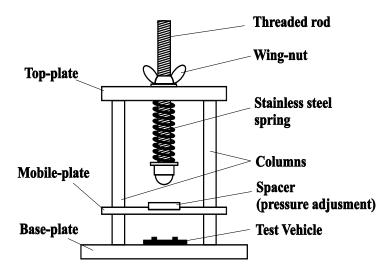

| 4.4.3. Sintering Press Development                                        | 87   |

| 4.5. Conclusions                                                          | 90   |

| 4.6. References                                                           | 90   |

| CHAPTER 5 Analysis of the Ag Sintering Process Parameters                 | 97   |

| 5.1. Introduction                                                         | 97   |

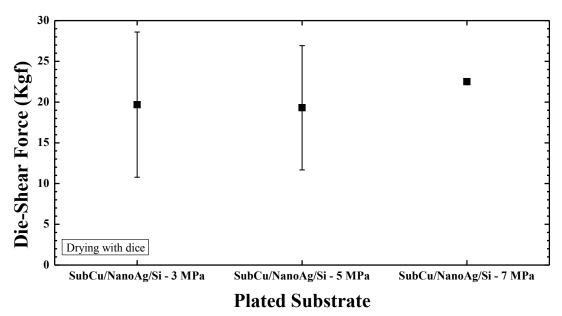

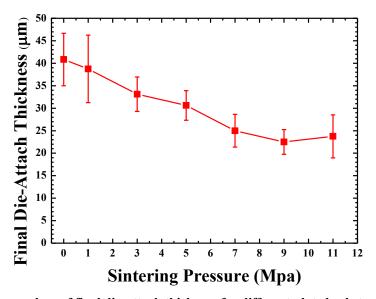

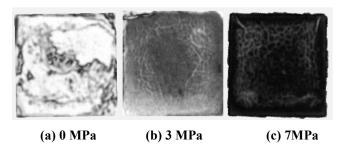

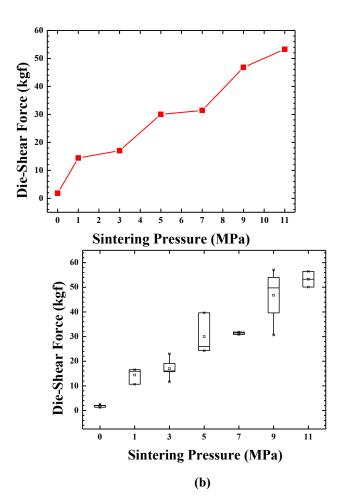

| 5.2 Influence of the Sintering Pressure                                   | 97   |

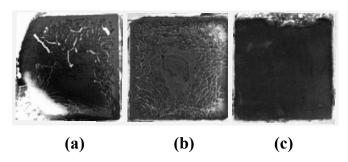

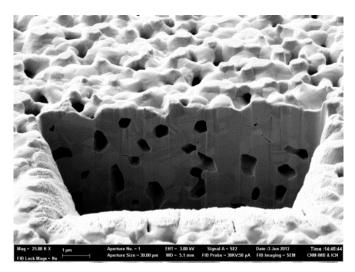

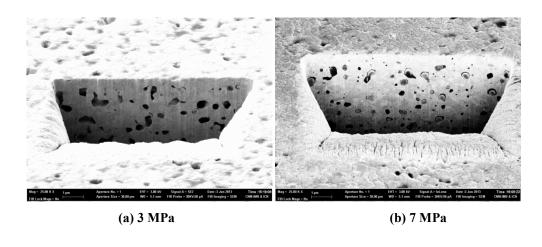

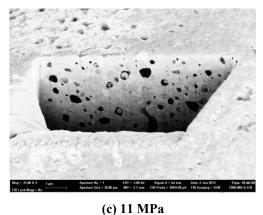

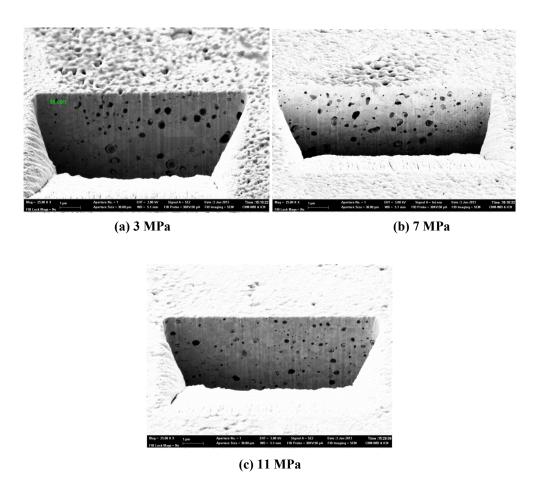

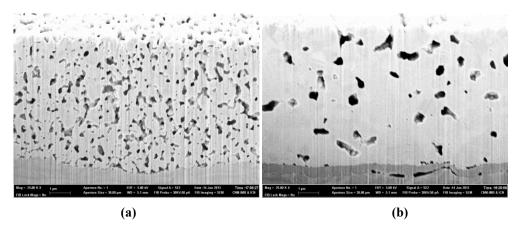

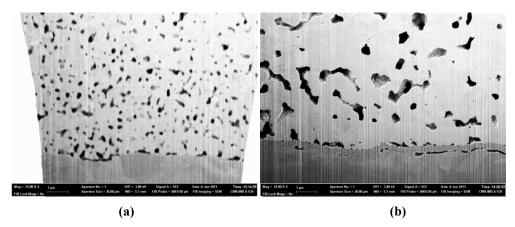

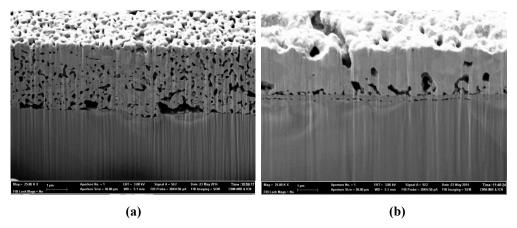

| 5.2.1. Microstructure of the Die-Attach Layer                             | 97   |

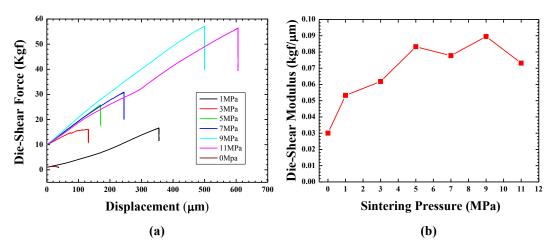

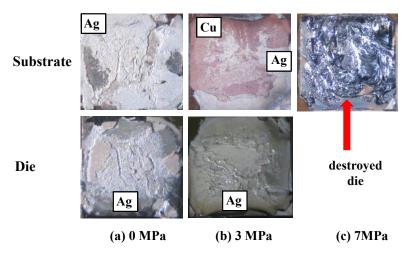

| 5.2.2. Die-Shear Results for Sintering Pressure Influence                 | 103  |

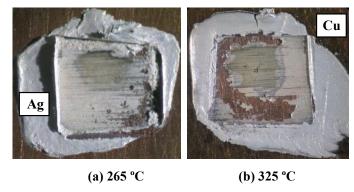

| 5.3. Influence of the Sintering Temperature                               | 106  |

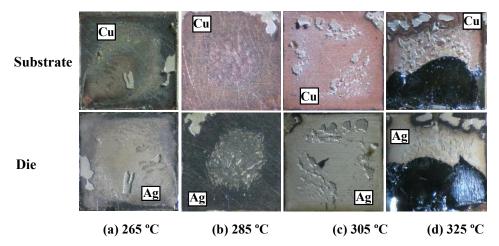

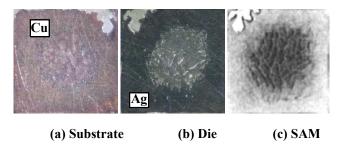

| 5.3.1. Microstructure of the Die-Attach Layer                             | 107  |

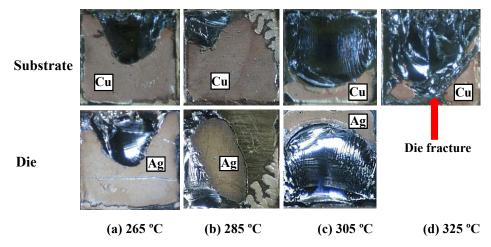

| 5.3.2. Influence of the Sintering Temperature on the Die-Shear Results    | 114  |

|                                                                           | viii |

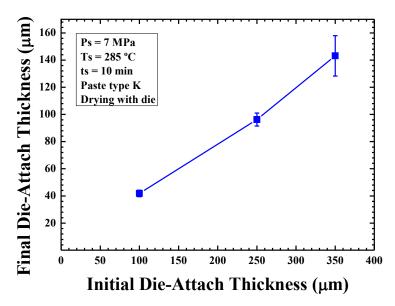

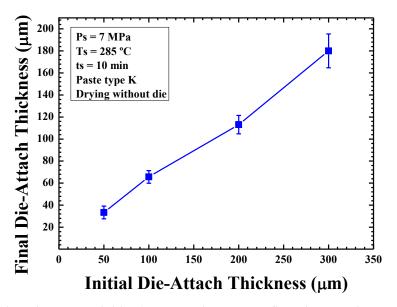

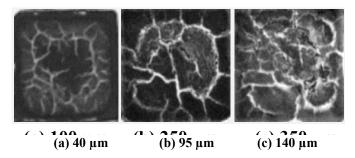

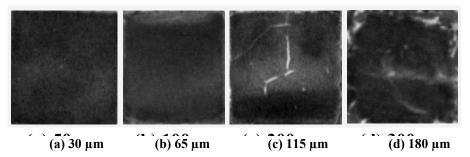

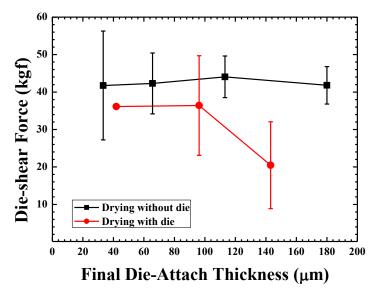

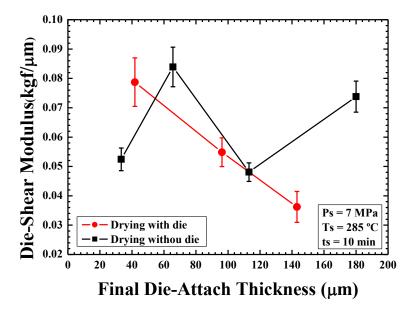

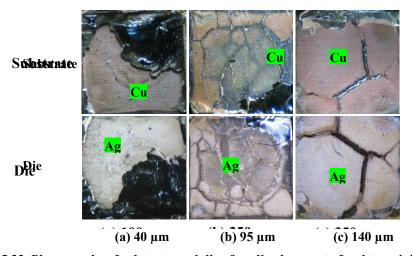

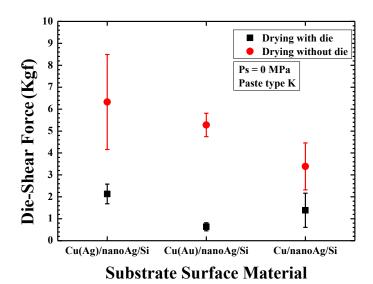

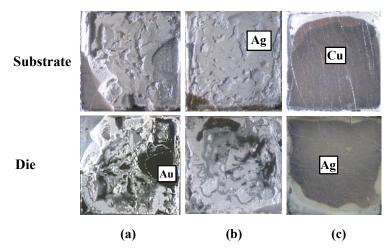

| 5.4. | Influence of the Initial Ag Paste Thickness and Drying Method            | 120 |

|------|--------------------------------------------------------------------------|-----|

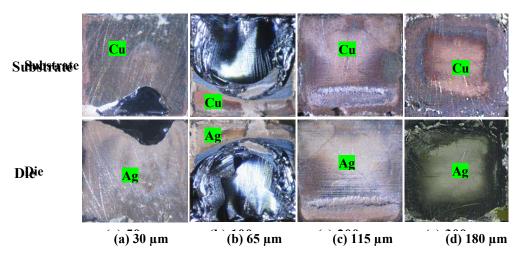

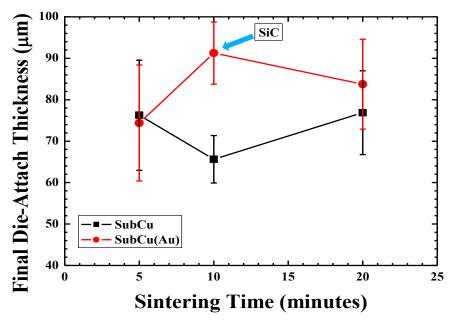

| 5.5. | Influence of the Sintering Time                                          | 127 |

| 5.6. | Influence of the Substrate Condition                                     | 131 |

|      | 5.6.1. Influence of the Substrate Surface Roughness                      | 132 |

|      | 5.6.1.1. Substrate Surface Roughness influence at 0 MPa                  |     |

|      | Sintering Pressure                                                       | 132 |

|      | 5.6.1.2. Substrate Surface Roughness influence at 7 MPa                  |     |

|      | Sintering Pressure                                                       | 133 |

|      | 5.6.2. Influence of the Substrate Surface Treatment                      | 134 |

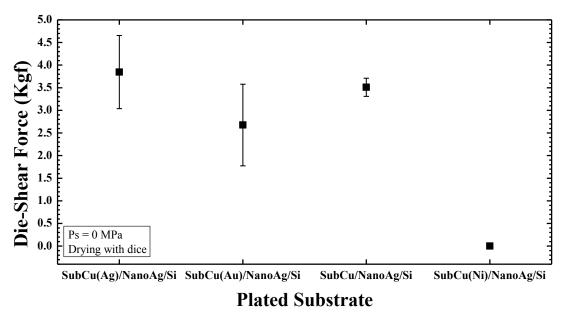

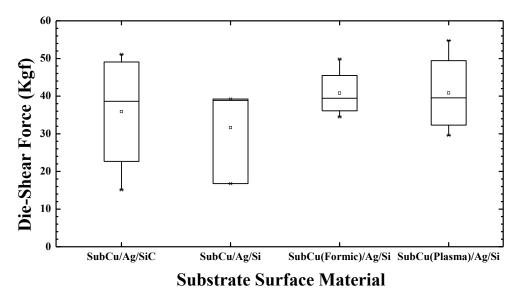

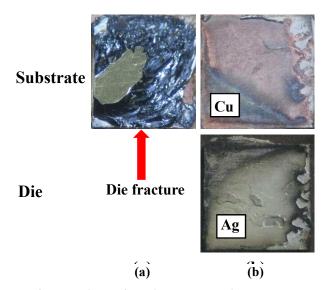

|      | 5.6.3. Influence of the Substrate Surface Material                       | 136 |

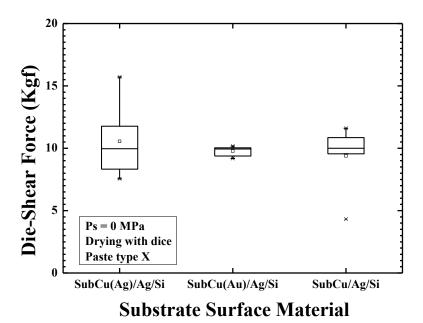

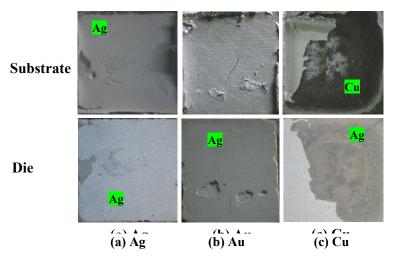

|      | 5.6.3.1. Influence of the Substrate Surface Material at 0MPa             | 136 |

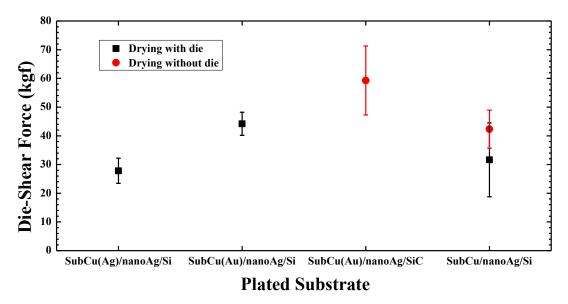

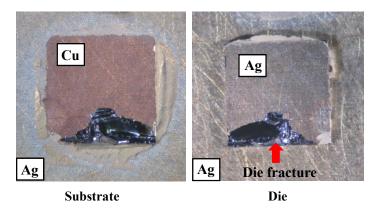

|      | 5.6.3.2. Influence of the Substrate Surface Material at 7 MPa            | 136 |

| 5.7. | Conclusions                                                              | 142 |

| 5.8. | References                                                               | 145 |

| СН   | APTER 6 Analysis of High Temperature Die Attach Materials under          |     |

|      | Thermal Cycling                                                          | 149 |

| 6.1. | Introduction                                                             | 149 |

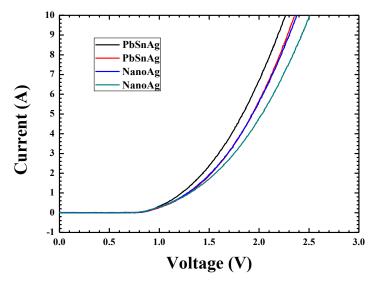

| 6.2. | Initial Evaluation of High Temperature Die-Attach Materials              | 150 |

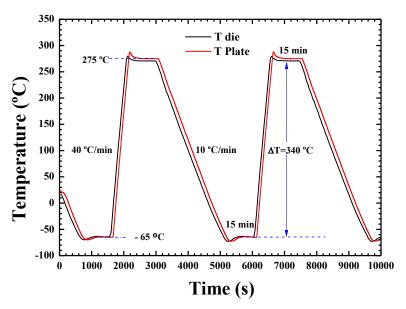

| 6.3. | Thermal Cycling Tests                                                    | 154 |

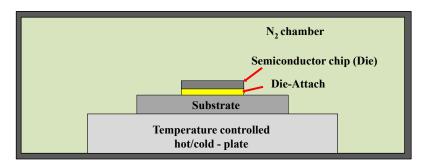

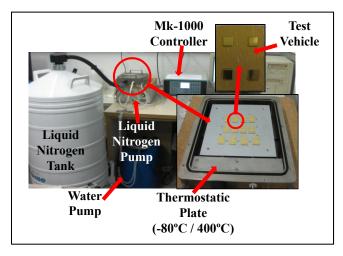

|      | 6.3.1. Experimental Set-Up                                               | 156 |

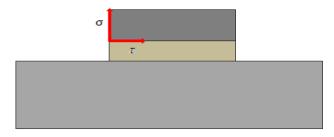

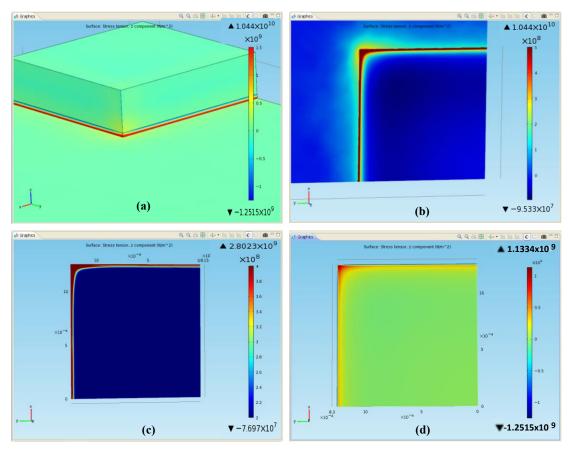

| 6.4. | Thermo-Mechanical Stress Analysis in the Test Vehicles                   | 159 |

|      | 6.4.1. Thermal Stress Module in COMSOL Multiphysics                      | 160 |

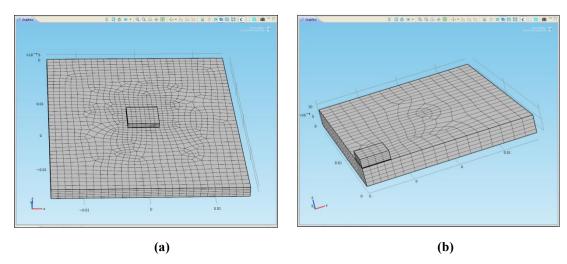

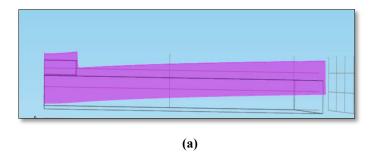

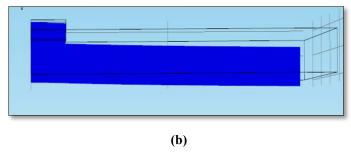

|      | 6.4.2. Boundary Conditions and Mesh Definition for the Thermo-Mechanical |     |

|      | Simulations                                                              | 163 |

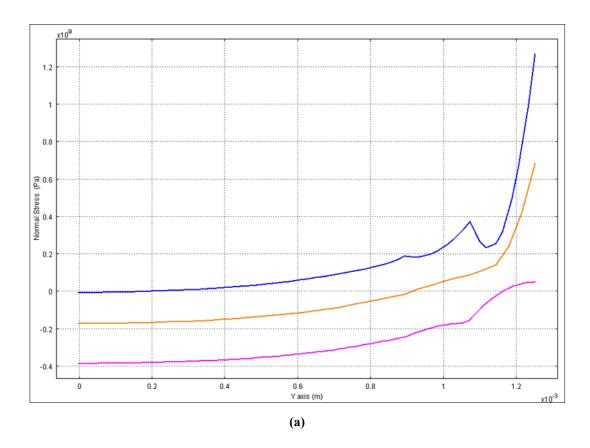

|      | 6.4.3. Analysis of Basic Thermo-Mechanical Phenomena on Single           |     |

|      | Die Structure                                                            | 167 |

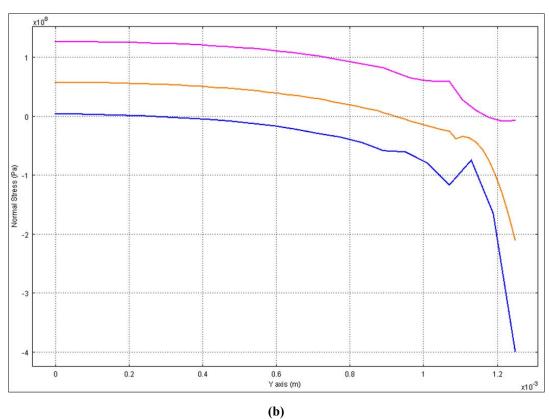

|      | 6.4.4. Simulated Stress Distributions for AuGe and PbSnAg Die-Attaches   | 174 |

|      | 6.4.5 Warping Measurements                                               | 175 |

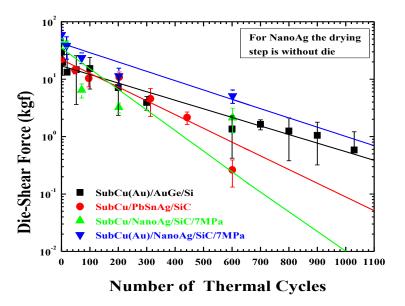

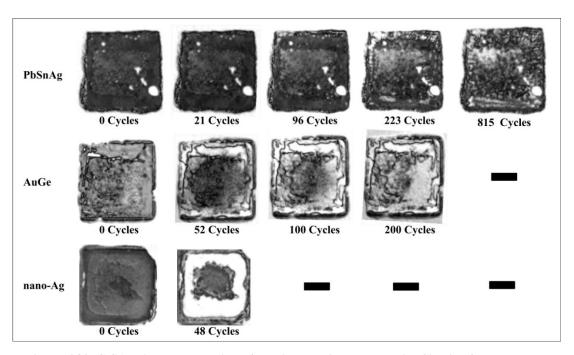

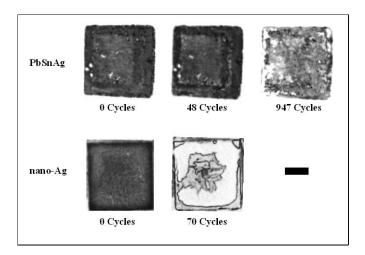

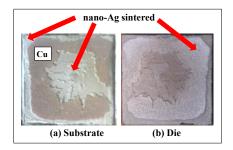

| 6.5. | Experimental Thermal-Cycling Results                                     | 179 |

| 6.6. | Conclusions                                                              | 187 |

| 6.7. | References                                                               | 189 |

# **CHAPTER 7 General Conclusions and Discussion**

193

# **CHAPTER 1 Introduction and Motivation**

#### 1.1. Introduction

This chapter will describe the motivation and the main objectives of this research work, which is related to the development of manufacturing die-attach layers based on sintered Ag particles, its comparison with solder alloys and their thermo-mechanical assessment. Besides, a brief description of the organization of this thesis is provided.

#### 1.2. Motivation

At the dawn of the second decade of 21<sup>st</sup> century, global environment and energy generation are some of the most significant issues of our society. According to the Kyoto protocol, the main countermeasures to face them are greenhouse gas emission reduction, energy saving, and rational use of energy. In this scenario, power electronics is the key technology to carry out these actions, since it efficiently manages, distributes and generates electrical energy respecting the environment.

Currently, power electronic systems are present in many market segments; such as: Domestic and office appliances, heating, ventilation and air conditioning, digital consumer, communication, factory automation and drives, traction, automotive and renewable energies. Besides, new challenges in this research field are devoted to the design of even more efficient power electronic systems (rational use of energy), as well as their expansion in the automotive arena with the electric car or in the aeronautic field with the development of more electric aircrafts (greenhouse gas emission reduction).

One bottleneck to meet these targets and challenges is related to the robust and reliable design, fabrication, packaging and integration of commercially available semiconductor power devices. In this sense, the implantation of power electronic systems can be highly improved by increasing their levels of integration and miniaturisation. One of the possible solutions consists in increasing the switching frequency of the power devices as this allows reducing the volume and weight of

magnetic passive components, although in many cases this results also in a junction temperature increase. In line with this integration strategy, there is another approach consisting in allowing the increase of the maximum operation junction temperature of the power devices. The effect of this approach is a drastic reduction of the thermal management requirements, avoiding bulky and heavy heat-sinks, fans, heat-exchangers, etc.

As it has been discussed, increasing the levels of integration (and consequently the power densities) of power converters, is practically correlated with higher operation junction temperatures. In parallel, there is also a big interest in power electronics systems suitable for operating in harsh environments and, in particular, at extreme temperatures, as these are the conditions of several critical fields: space, aeronautical, well logging, etc. This fact increases the interest in new technological solutions allowing the implementation of high temperature power converters, as their application range is extremely wide and strategic. Consequently, the framework of this thesis can be placed in the field of the "high temperature electronics" ("electronics operating at temperatures in excess of those normally encountered by conventional silicon based or their auxiliary components" [1]).

In the particular case of the design of power electronics packaging technologies, the implementation of die-attach layers is one of the most critical steps of the manufacturing process. In order to assure suitable operation and resistance to wear-out, this connection must fulfil some requirements, such as sufficient adhesion between die and substrate (so that the die does not detach from the substrate), high electrical and thermal conductivities, suitable mechanical properties to avoid and support the thermomechanical stresses and high melting point to guarantee the reliability in harsh environments. Currently, the most common die-attach material used is the family of the PbSnAg alloys [2, 3], although its melting point is not suitable for very high temperature applications (> 300 °C). Furthermore, lead-based alloys are not environmentally friend and therefore several legislations around the world are gradually limiting the use of lead in electronics [4, 5]. To address this concern several Pb-free alloys and materials have been introduced, including sintered Ag particles, although many aspects of these new technologies still require additional research. This work will

try to contribute to improve the knowhow in this field, and in particular, in using sintered Ag particles as a high temperature die-attach solution.

# 1.3. Objectives

This research work aims at the development of the process technology for manufacturing die-attach layers based on sintered Ag particles. This work will provide useful information about the influence of the most relevant sintering parameters on the quality of the die-attach and the physical understanding of the basic mechanisms explaining such influences. Another relevant objective of the work is to compare the sintered Ag solution with other solder joint materials for power electronic packaging for high temperature applications. For this purpose, experimental tests based on thermal cycling will be performed in order to identify the best solution.

### 1.4. Organization and Brief Description of this Thesis

This thesis is composed by 7 chapters, including the present one, and their content is briefly presented below:

Chapter 2 will describe the importance of power electronics in our society, its main applications, the most used semiconductor devices and the most relevant packaging structures. Main emphasis will be provided to the description of power electronics packaging technology, comparing current technologies, new trends and solutions mainly oriented to high temperature power electronics. This comparison will be performed detailing the materials, benefits and drawbacks among them. On the other hand, some comments are performed on their ageing and long-term reliability, pointing out that the thermo-mechanical stresses experienced under working conditions are among the main ageing agents.

Chapter 3 will define the die-attach technology based on sintering of Ag particles. First, it will be described the main categories of die-attach materials and their thermomechanical properties. Then a brief review of the most used methods for failure analysis (FA) will be provided, as well as the description of the methods used in this study to

analyse the quality and the degradation of the die-attach layers. Finally, the sintering theory and its adaptation to allow sintering as a die-attach technique will be described.

Chapter 4 will present the two pastes based on Ag particles used in this work and their main initial properties using different characterization tools (thermo-gravimetric analysis, SEM, etc.). Then, the test vehicle used for characterizing the die-attach layers and their process conditions will be described, providing also the most relevant physical thermo-mechanical parameters of each material involved in their development. Finally, the sintering process and the experimental set-up developed for manufacturing sintered die-attach layers, and their assessment methodology, will be explained. The discussions will address in particular the developed screen printing tools, the drying and temperature profile implementation method and the specific sintering press designed and fabricated for this research work.

Chapter 5 will describe and analyse the influence of the main Ag sintering process parameters, which determine the properties of the final sintered layer. The parameters that will be analysed are pressure, temperature and sintering time. Additionally, the drying step of the Ag paste, which is critical in the manufacturing process, will be also evaluated. Finally, the parameters and characteristics correlated to the substrate condition (surface plating material, roughness and treatment), will be also analysed. This chapter will not only explain the reasons for some of the observed parameter influences, but will also provide useful information for implementing power assemblies using sintered Ag die-attach layers.

Chapter 6 will present a comparative analysis of the thermo-mechanical performance of established high-temperature die-attach materials as a solder alloys (AuGe and PbSnAg) and sintered layers (based on sintering of Ag particles) under harsh thermal cycling tests. The study will focus on test vehicles using bare Cu substrates, due to the practical interest of this solution that avoids plating with Au or Ag, reducing the final cost of the package. Thermally cycled test vehicles will be evaluated using the methods described in chapter 3 (die-shear tests, optical and acoustic microscopy inspections), the test vehicles described in chapter 4 and the sintering processes of chapter 5. As the focus of this work is on high temperature electronics, a specific thermal cycling test set-up was required and its design details are also provided.

Besides, to support the interpretation of the thermal cycling results, auxiliary thermomechanical simulations and warpage measurements have been carried out.

Finally, chapter 7 will provide the conclusions of this technological research work.

#### 1.5. Conclusions

This chapter provided the framework and the motivation of this research work. Besides, the main objectives and general description of the chapters that constitutes this study have been summarized.

#### 1.6. References

- [1] F.P. McCluskey, R. Grzybowski, and T. Podlesak. "High Temperature Electronics". CRC press 1997.

- [2] J. Felix, "Impact of material and process parameters in soft solder die bonding," in *Proc. Semicon*, 2006, pp. 1 3.

- [3] R. Khazaka, L. Mendizabal, D. Henry, R. Hanna, "Survey of High Temperature Reliability of Power Electronics Packaging Components," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2456 2464, September 2014.

- [4] F. P. McCluskey, M. Dash, Z. Wang, and D. Huff, "Reliability of High Temperature solder Alternatives," *Microelectronics Reliability*, vol. 46, no. 9 11, pp. 1910 1914, 2006.

- [5] Y. Li and C. P. Wong, "Recent advances of conductive adhesives as a lead-free alternative in electronic packaging: Materials, processing, reliability and applications," *A Review Journal* of *Materials Science and Engineering*, vol. 51, no. 1 3, pp. 1 35, January 2006.

# **CHAPTER 2 Power Electronics Packaging Review**

#### 2.1. Introduction

This chapter aims at explaining the importance of power electronics in our society, its main applications, the used semiconductor devices and the most relevant packaging structures. Main emphasis will be provided to the description of power electronics packaging technology, comparing current technology, new trends and solutions mainly oriented to high temperature power electronics. This comparison will be performed detailing the materials, benefits and drawbacks among them. On the other hand, some comments are performed on their ageing and long-term reliability, pointing out that the thermo-mechanical stresses experienced under working conditions are among the main ageing agents.

#### 2.2. Power Electronics

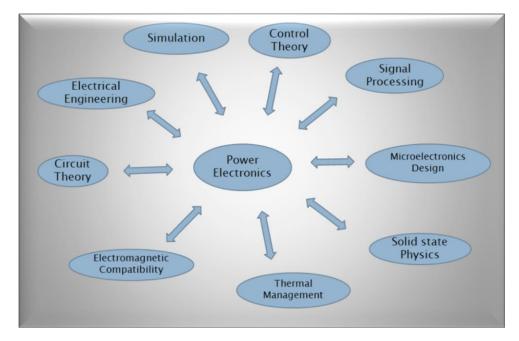

Over the last years, power electronics has acquired major relevance in our lives. It constitutes the key technology to efficiently manage, distribute and generate electrical energy respecting the environment. Currently, power electronic systems are present in many market segments such as: domestic and office appliances, heating, ventilation and air conditioning, digital consumer, communication, factory automation and drives, traction, automotive and renewable energies. The design of such systems involves the fields shown in Figure 2.1, since power electronics is a multidisciplinary and complex technology [1, 2, 3]. The most significant are:

- 1) *Microelectronic design and solid state physics*. They are important for developing the semiconductor power devices used in every power electronic system.

- 2) Component thermal management, electromagnetic compatibility and circuit theory. They are necessary for a safe and optimum system design and operation.

- 3) *Control theory and signal processing*. They ensure an efficient control chain of the power system.

- 4) *Electrical Engineering concepts*. They are essential for optimizing the interaction between power electronics and electromechanical drives, for correct design of passive elements, etc.

- 5) Simulation Tools for Virtual Prototyping. Multi-physics simulation packages are required for performing virtual prototyping and ensuring the proper operation of the power electronic system, saving cost and time.

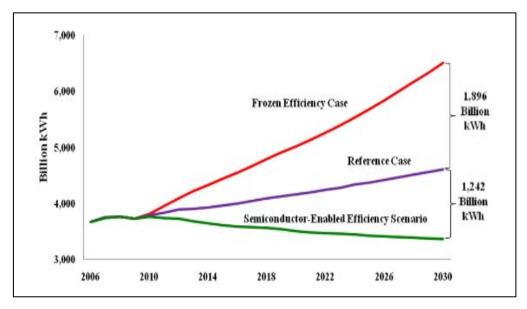

The success and fast evolution of power electronics can be mainly attributed to the development of the semiconductor power devices, which allowed in fact the development of energy efficient systems and a more rational use of energy. This is clearly observed in the case of "smart grids" for the management of electrical energy generation and distribution [4]. Their aim is to make an intelligent use of power electronics to distribute electrical energy in a more efficient and cost saving manner, which would not be possible without the current power semiconductor devices. Figure 2.2 plots predictions of US energy consumption versus year [5]. This figure compares such predictions in three different situations: a "frozen" efficiency case, where no additional efficiency improvement measures are taken beyond 2009, a "reference case" based on an analysis from the US Energy Information Association (EIA), and finally a "semiconductor enabled efficiency scenario" (SEES) where a more aggressive usage of semiconductor devices is assumed. The main conclusion that can be extracted from Figure 2.2 is that the power consumption in the frozen efficiency and reference cases does not show the same improvement in terms of consumed power than that achieved when semiconductor devices are employed. They allow also reaching such interesting results in other power electronics applications, therefore being of paramount importance in the whole energy scenario providing a solution to the energy market demands according to Kyoto's protocol. In order to provide an in-depth overview of the role of power semiconductor devices in the most important power electronics applications, their status, trends, and contributions made to the overall application scenario are detailed in the next section.

Figure 2.1. Fields related with power electronic systems [3].

Figure 2.2. Future electricity use scenarios for the US considering power electronics contribution [5].

# 2.2.1. Semiconductor Devices and Power Electronics Applications

The role of power semiconductor devices in power systems is to control the current flow within the power converter (forward state) and sustain the voltage when the current is diverted to another component (blocking state), e.g. another converter leg [3]. The most commonly used power semiconductor devices are diodes, SCRs (Switched Controlled Rectifier), GTOs (Gate Turn-off Thyristor), MCTs (Mosfet Controlled

Thyristors), BJTs (Bipolar Junction Transistor), MOSFETs (Metal Oxide Semiconductor Field Effect Transistor), and IGBTs (Insulated Gate Bipolar Transistor). They can be divided in two main families: controlled switches (or simply switches) (GTOs, MCTs, MOSFETs, and IGBTs) and rectifiers (Fast Recovery Diodes or FREDs and low-frequency rectifying diodes) [6]. The main difference between them is that the former are switched-off and -on with an external control signal (current or voltage), whereas the latter depends on circuit variables. Other classification criterion for power semiconductor devices considers the current distribution within the device (topology) [2]. According to this, devices can be categorized into lateral and vertical topologies. In the case of vertical devices, the current flows across the bulk of the chip active area, which is injected from its upper to its back side or vice versa. In high current rating applications, such devices are interconnected in parallel using multi-chip packaging technologies to ensure the required current levels, as will be explained further on. In the case of lateral devices, the current mainly flows close to the chip surface, thus being injected and collected close to the upper face of the device. To have an idea, the current conduction across the chip bulk corresponds to no more than a 5 % area of the entire chip (e.g., Laterally Diffused MOSFETs or LDMOS). Such devices are used in power integrated circuits (power ICs, also known as smart power circuits), which monolithically integrate these lateral devices with logic control circuitry [7, 8, 9].

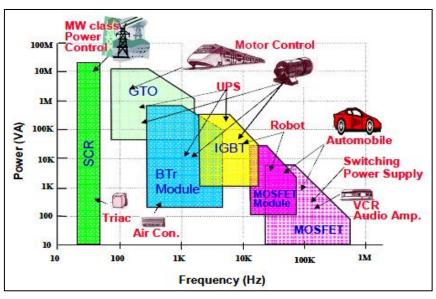

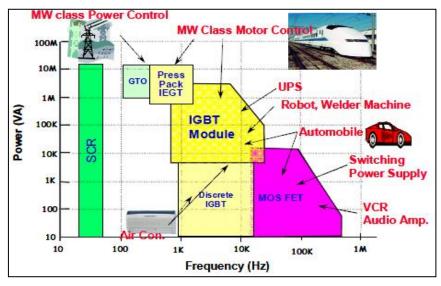

Another classification criterion for power switches is based on their voltage blocking capability: low voltage and high voltage switches. Currently, a single power switch suitable for any application does not exist, since the requirements in terms of current, breakdown voltage and switching speed cannot be satisfied simultaneously. Thus, for applications such as compact power supplies and disk drivers that require relatively low blocking voltages (< 100V) and high switching speeds (>100 kHz operation), it is common to use power MOSFETs [3]. In the cases that blocking voltages exceed 600 V (up to 6kV) and medium switching speeds are needed (1-20 kHz), IGBTs are the best choice [6, 10]. This operation range corresponds to medium-and high-power applications, the most important being railway traction, motor control and industrial drives. Probably, the IGBT is the most versatile device among the power switch families. It covers the widest application area in terms of current ratings, blocking voltage and switching speed. The IGBT versatility relies on its internal structure (hybrid structure) proposed in 1982 by Baliga [10]: it consists in a wide base

p-n-p transistor driven by an integrated short channel MOSFET. This combination produces a very high power gain (typically >10<sup>6</sup>) because of the high input impedance resulting from the MOS gate structure (voltage control, MOS-gated device), and the low on-state voltage drop resulting from the internal physics of bipolar devices [6]. Therefore, for high voltage power electronics applications, the IGBT has replaced silicon bipolar power transistor and the gate turnoff thyristors (GTO). Finally, high voltage (>5 kV), high current ratings (>5 kA), and low switching frequencies (<500 Hz) are controlled by SCRs (thyristors) and GTOs.

Figure 2.3. Power versus switching frequency and applications fields of power devices in 1997 [11].

Figure 2.4. Power versus switching frequency and applications fields of power devices in 2005 [11].

In this scenario, some power electronics applications are typically powered by certain power semiconductor devices, as it is the case for [4, 12]:

- 1) SCRs and GTOs are mainly employed in HVDC transmission lines

- 2) IGBTs have enabled AC motor drives for locomotives or hybrid cars (traction), industrial applications, and developing more efficient home air conditioners.

- 3) MOSFETs have enabled switching power supplies for industrial and consumer applications.

To have an idea about the power electronics evolution and the usage of power vertical switches in the last 15 years, some of its application fields in 1997 and 2005 are shown in Figures 2.3 and 2.4, respectively [11]. Such figures plot the power managed by the power system versus the commutation frequency of the power switch. The difference between them is that most of the applications of GTOs and BJTs have been occupied by IGBTs. MOS-gated devices are predominantly used in almost all application fields, including LDMOS in power ICs, MOSFETs for low voltage and medium voltage applications and IGBTs for high power applications.

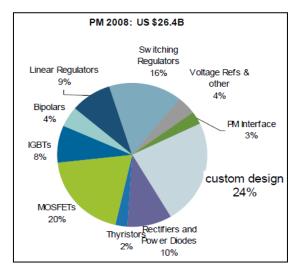

A particular case not included in Figures 2.3 and 2.4 concerns Power ICs. Although they represent a small fraction of the power device market, they cover a wide range of applications, such as switch-mode power supplies, point-of-load supplies, servo-motor drives, etc. Perhaps the most important application using Power ICs concerns switching power supplies. Power switches with low on resistance and fast switching speed are required to improve their efficiency, reliability, and cost. Over the years, power ICs have evolved from bipolar technologies to highly integrated power BCD style technologies incorporating CMOS and LDMOS transistors and many types of passives along with thick power metal levels. Today, advanced power technologies are at a 0.13µm integration level, but for many power management designs an optimum node can be around  $0.25 - 0.35 \mu m$ . This is a good compromise for cost, complexity and competitive switching efficiency. Figure 2.5 reflects the economic impact of what is depicted in Figures 2.3 and 2.4. It shows the classification of various segments within the power device market, custom design, rectifiers and power diodes, thyristors, MOSFETs, IGBTs, bipolar, linear regulators, etc. This chart includes both discrete and power ICs. However, this figure does not show the solid state lighting market, which is

mostly made up of light emitting diodes (LED). The LED industry has become increasingly important and is beginning to contribute to the overall efficiency improvement shown in Figure 2.2. Therefore, Power ICs are providing the control function for these new and highly efficient illumination sources [4].

Figure 2.5. The power semiconductor market in 2008 [4].

### 2.3. Power Electronics Packaging

Under the name "power electronics packaging" we include all the technologies and solutions providing:

- 1) Electrically interconnection for one or several power semiconductor devices.

- 2) Extraction of the dissipated heat through a thermal path separated (or not) from the electric path.

- 3) Isolation of the high voltages from other critical parts of the system

- 4) Mechanical support to the devices.

In this context, power electronics packaging plays an important technical and economical role because it constitutes the interface between the raw semiconductor device and the circuit application. One of the most critical issues related with power devices packaging concerns the reliability and robustness limits of the final component, as it is based on the combination of heterogeneous sub-assemblies and materials, including their interfaces and joints which are potential sources of defects and faults.

#### 2.3.1. Typical Power Electronics Package Structure

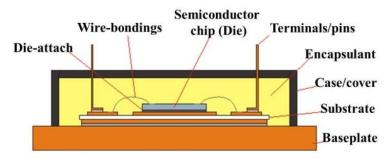

Two main packaging scenarios can be found in power electronics, concerning the packaging field: *discrete power devices* and *multi-chip power modules*. As both scenarios share similar problems and solutions, Figure 2.6 shows the generic structure of a typical power electronics package for discrete or module components. Its main parts are [13]:

- 1) *Power semiconductor chips or dice* (IGBT, FRED, MOSFET, Thyristor, Rectifier, etc.). They provide the electrical switching function.

- 2) *Die-attach*. It provides mechanical assembly of the device, as well as electrical and thermal contact on its backside.

- 3) *Top-side chip interconnections*. They provide electrical contact on the device top-side. Figure 2.6 shows as an example the wire-bonding technology. In some cases, the top-side interconnections can also provide top heat extraction.

- 4) Electrically insulating and thermally conductive substrate. It provides mechanical support for the devices, tracks and terminals, as well as electrical insulation between some of them. It also provides an efficient heat extraction path.

- 5) *Encapsulant material*. Typically it consists on a conformal coating or casting for environmental and mechanical protection.

- 6) *Base plate*. It provides mechanical support as well as heat spreading and heat conduction to the external heat dissipation system.

- 7) *Terminals and pins*. They allow the connection of the packaged device with the application circuit.

- 8) Case or cover. The housing structure that protects the overall component.

Figure 2.6. Typical power electronics package structure.

Each one of these parts involves different materials. The optimum set of materials is defined for each kind of application and environmental conditions. Depending on its functionality and its position in the package structure, each material requires particular characteristics described by the physical parameters (electrical resistivity, thermal conductivity, etc.). Typical materials used in power packaging are:

- 1) *Power semiconductor devices*. Although other semiconductors have been also introduced (SiC JFETs and rectifiers, AlGaN/GaN HEMTs, AsGa diodes, etc.), Si-based devices are the most commonly used.

- 2) *Die-attach*. The most common die-attach material used up to date is the PbSnAg alloy but now other Pb-free alloys and materials have been introduced, including sintered Ag nano-particles. This solution will be studied in depth in the next chapters.

- 3) *Top-side interconnections*. The most used technique is large Al wire-bonding. Other solutions include pressure-type contact and metal bumps.

- 4) *Electrically insulating/thermally conductive substrate*. For high power applications, the most common solution is based in ceramic substrates with Cu layers on top and backside. The typical technology is the DCB (Direct Copper Bonded) based on different ceramic materials: Al<sub>2</sub>O<sub>3</sub>, AlN, Si<sub>3</sub>N<sub>4</sub>, BeO. For low and medium power ratings, metal (typically Al) substrates with a ceramic-filled polymer (typically epoxy) insulating layer are used instead of the ceramic ones. This is the IMS technology (Insulated Metal Substrate).

- 5) *Encapsulant*. Thermoset and thermoplastic materials including silicones and epoxies are employed. The increasing voltage ranges provided by SiC devices, represent a challenge for the development of new reliable encapsulant materials.

- 6) *Base plate*. Typically, it is based on Ni plated Cu slabs. Other used materials are metal matrix composites, such as Cu matrix composites reinforced with diamond, Al matrix reinforced with SiC or carbon-reinforced composites. These composites allow matching the coefficient of thermal expansion (CTE) of the base plate with that of the substrates and semiconductors.

- 7) *Terminals and pins*. Cu leads and pins are the most common solutions, but some specific packages are based on Mo plates (press pack solutions), springloaded pins, etc.

In order of importance, the package begins at the interface of the chip itself, which is considered the first-level packaging, to higher levels of packaging such as substrate-level and system-level packaging. First-level packaging consists in the attachment of one or more bare chips to a substrate, the interconnection from these chips to the package leads and their protection with an encapsulant. The first-level interconnection has a major role, because it directly interfaces with the chips, not only electrically, but also thermally and mechanically. For reducing the temperature rises and consequently thermal stresses for the chips handling more power, it is necessary a thermal-friendly interconnection design. And lastly, reliability of the first-level interconnection is vital in ensuring that the electronic assemblies have an extended lifetime. At this point, a good thermo-mechanical matching (CTE matching) between neighbouring materials is crucial, as will be further explained in Chapter 3.

As it has been shown, power electronics packages are heterogeneous components, involving several engineering fields. Some of them are interrelated due to coupling mechanisms between different physical phenomena. We have already mentioned the thermo-mechanical effects which will be one of the focus of this work, but there are other aspects that are taken into account during the design phase such as the optimization of the electrical circuit of the package (parasitic inductance and resistance reduction), its electromagnetic compatibility (low parasitic radiation and conduction), its mechanical roughness, or thermal management guidelines. Perhaps, package thermal management concerns the most critical part, in which more engineering efforts are addressed. The goal in thermal management design is removing the heat dissipated by the power devices, constraining the maximum device temperature below specified values, and minimizing thermal gradients between components. The heat must ultimately be transferred from the package to a heat sink. In this framework, the thermal analysis techniques are used during the design phase to predict the temperatures and heat fluxes that will occur in an electronics package during its real operation. Thermal analysis involves the understanding of the fundamental heat transfer mechanisms, design tools such as thermal simulators and the thermal parameters of the materials involved in the design [14].

In order to give a more precise overview of the power packaging scenario, we will describe two examples of the most commonly used solutions for discrete and multi-chip

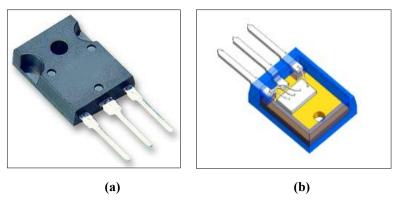

power module components. In the simple discrete TO-247 package, power semiconductor devices are soldered to a copper flange (acting as substrate, collector terminal and baseplate), and source and gate terminals are connected from the aluminium chip bonding pad to nickel-plated copper leads. The top of the chip and wire-bondings are encapsulated with a molding compound (usually based on a ceramic-filled epoxy) to provide insulation, mechanical support and protection [1, 15, 16]. Figure 2.7 (a) shows an external view of such a TO-247 package and Figure 2.7 (b) depicts its internal view.

Figure 2.7. (a) External aspect of a TO-247 discrete package. (b) Internal view of this package [16].

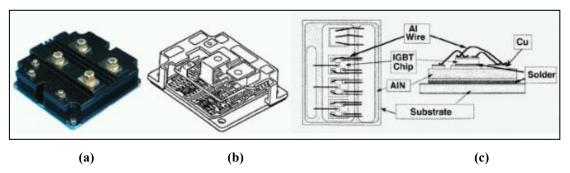

Figure 2.8. IGBT power modules and schematic of interconnect hierarchy: (a) 6.5 kV IGBT module package; (b) inside of a similar power module; and (c) power module components [17].

In the case of a multi-chip power module, chips are typically connected by wire-bonding technology. In such modules a DCB substrate is commonly used as a base for the power device (switching device and freewheeling diodes). DCB provides an excellent electrical insulation as well as good thermal conduction due to the direct bonding of copper on ceramic materials; such as alumina and aluminium nitride. Joining materials for device attachment and DCB to base plate attachment are usually solder alloys. Figure 2.8 (a) shows a 6.5kV IGBT module [17], figure 2.8 (b) shows the inside

of a similar module, and figure 2.8 (c) shows the devices interconnection within a multichip power module.

## 2.3.2. Advanced Power Packaging Solutions

In the framework of power packaging, advanced solutions have been proposed as an alternative to the classical structures presented above. For example, wire-bonding free technologies have been developed with the aim of improving the package reliability. Currently, wire-bonding is the most common chip-level top-side interconnection technology in power electronics packaging. This is due to the fact that this technology can easily adapt changes in the package design at a lower cost. This flexibility in the design and low cost, combined with continue efforts in process improvement, indicate that wire-bonding will continue to be the predominant method for chip level interconnection in the near future. Nevertheless, wire-bonding constitutes the weakest point concerning reliability in many high power or harsh environment applications. Consequently, innovative wire-bonding free interconnect techniques received a significant research effort in recent years, bringing, in addition, other benefits: lower interconnection resistance, lower noise levels and parasitic oscillations, better thermal management, higher level of system integration between power devices as well as driver circuitry, controls, sensors and communication connections, and last, reduced cost.

We present below, the most significant advanced power packaging contributions described in the recent literature, many of them characterized by different top-side interconnection approaches. Table 2.1 summarizes the advantages and disadvantages of the different advanced power packaging technologies described below [16].

#### 2.3.2.1. Pressure Contact Assembly Structure (press-pack)

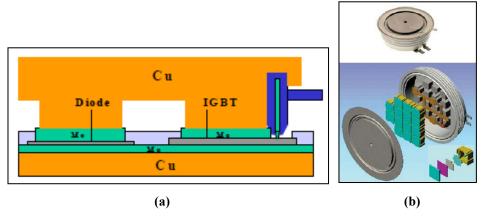

One of the proposed wire-bonding free technologies is the pressure contact technology, also known as "press-pack". The pressure contact concept, experienced through several stages, has now evolved to a sandwiched structure which includes anode-side Cu plate, anode-side Mo CTE compensating metal disc, silicon device, cathode-side CTE compensating Mo disc and cathode-side grooved Cu post, as

represented in Figure 2.9. Due to the soldering absence, this method eliminates the residual stress on each material, but also raises the concern of mechanical damage caused by pressure force. This solution is applied mainly in high power semiconductor devices (e.g., diodes, thyristors, or GTOs) for high-power applications [1, 18]. Nevertheless, research interest in the study of a pressure contact technology applied to IGBTs also raised due to the extensive use of this device and examples have been presented from several manufacturers, as for example the one shown in Figure 2.9(b) (press-pack IGBTs from ABB Semiconductors). Another noticeable example is the one presented in [19], showing a press-pack solution developed for SiC-based diodes.

Figure 2.9. Pressure contact assembly structure a) Schematic cross section [1, 18]. b) Parts of a real IGBT press-pack.

## 2.3.2.2. Spring Pressure Contacts

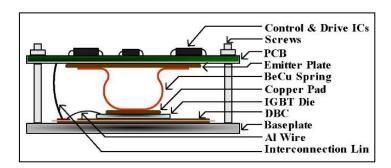

Another alternative interconnection technology for replacing wire-bondings is spring pressure contacts [20]. Figure 2.10 shows an IGBT package with spring pressure contact technology. The IGBT and diode dies are soldered on a DBC substrate using a die-attach material.

Figure 2.10. Cross section of a spring contact structure [20].

Another copper pad is placed on the emitter area of the die fixed with silicone adhesive in flank. In this case, the spring contact, made of beryllium-copper (BeCu) alloy, is soldered on the top plate electrode and pressed on the copper pad. Therefore, the emitter area is connected by a spring. In the upper face of the PCB, control and driver ICs are assembled. Furthermore, the spring made of BeCu offers properties that help reducing thermal stresses, also offering an additional thermal path. One problem of this structure is the introduced contact resistance that depends on the spring compression and affects the electrical performances.

# 2.3.2.3. Multilayer Technologies

Another wire-bonding free technology described for power packaging is based on metallization layers directly deposited on the device electrodes [16]. Metal layers and signal planes connect power devices to the rest of the circuit, and are implemented using chemical or physical deposition. Deposited metallization package technology includes General Electric's "Power Overlay" (POL) technology and embedded power technology.

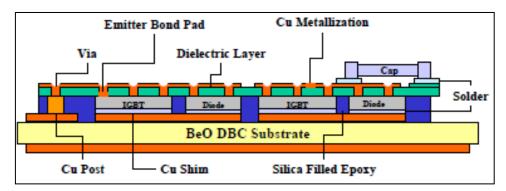

Concerning the thin-film "Power Overlay" developed at General Electric, it aims at reducing the cost of mass production and improving the reliability and efficiency of power electronics packages [21]. This technology has eliminated wire-bonding through the usage of metalized Cu vias/polyimide to achieve power and control interconnection. Figure 2.11 shows a cross-section of the POL design, where power electronics devices are soldered to a DCB substrate from the backside. Differences in device thickness are compensated by copper shims.

This technology has the following advantages [1, 16]:

- 1. Elimination of wire-bonding with metallurgical interconnections.

- 2. Lower interconnection parasitic inductance, allowing higher operation frequency.

- 3. Improved thermal performance by minimizing the number of interfaces and allowing two-sided heat removal.

- Reduced profile and more flexible packaging options allowing innovative stacking approaches for circuit packaging, including components assembled on top.

- 5. Low cost.

Besides, the inherent multilayer nature of POL technology will facilitate the integration of gate drivers and other circuits into the three-dimensional package stack of Power Electronics Building Blocks (PEBB) modules.

Figure 2.11. GE's Power Overlay Technology.

Figure 2.12. Cross section schematic of the Embedded Power technology.

Another example of a multilayer technology, is the "Embedded Power" concept developed at Virginia Tech that uses ceramic substrates, deposited metal layers, screen printable dielectric materials and solders to enclose power devices [22]. There are three major parts in the structure: the embedded power stage; electronic circuitry and base substrate, forming a monolithic power module. Figure 2.12 shows a schematic cross section of the embedded power module. Components on top of the structure are gate

drivers, control and protection circuits. The substrate provides electrical interconnection and a thermal path for the heat extraction, while the deposited metal layer provides only electrical interconnection. Another important aspect is that this is an all-low temperature (< 250 °C) hybrid processing technology.

### 2.3.2.4. Thinpack Technology

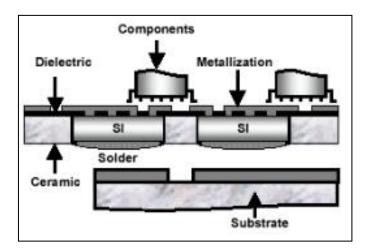

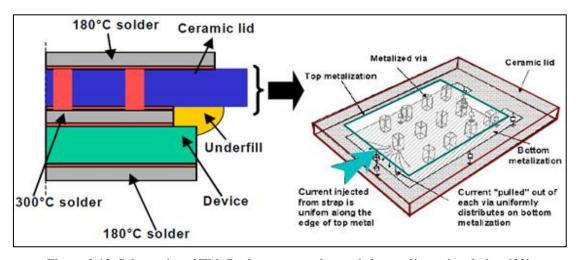

Another advanced solution is the Thinpack technology. In this technology, a ceramic lid, with holes drilled in it and filled with solder, is attached to the chip by solder reflow (Figure 2.13). Specific routing can be made in the ceramic interposer to connect electrodes on the chip to circuits. This technique was claimed to increase power module yields to nearly 100%. The thin ceramic lid shrinks package volume, decreases thermal resistance and it also serves as the base for integration of other circuit components [23].

Figure 2.13. Schematics of ThinPack cross - section and three - dimensional view [23].

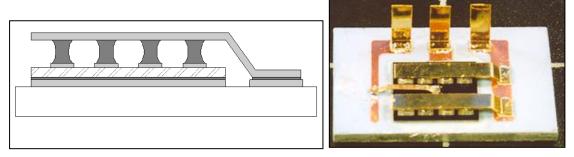

#### 2.3.2.5. Area Array or Bumping Interconnection Technologies

Area array interconnect is another wire-bonding free technology. For interconnections between device electrodes and the defined substrate metallization, solder area array bumping uses area-populated metallurgical bumps or conductive polymer bumps. Besides, bumps provide a heat dissipation path from the chip to the substrate and act as a mounting support for the chip as well as a buffer to relieve strain due to the CTE mismatch between chip and substrate. Sometimes, the silicon chips are

placed facedown when joining them to the substrate and this type of packaging is also named "flip chip". Figure 2.14 shows an example of an IGBT transistor where the top emitter connections have been performed using solder bumps, following a technology developed at IMB-CNM [24].

Figure 2.14. Schematic cross-section and picture of an IGBT with solder bumps on the top emitter pads.

#### 2.3.3 High Temperature Power Electronics Packaging

High temperature packaging is defined as the one required for "electronics operating at temperatures in excess of those normally encountered by conventional silicon based or their auxiliary components" [25]. It is essential for severe and extremely harsh environments, in which the usage of conventional packages is impractical (e.g., commercial and military aircrafts, automobiles with longer lifetimes and greater fuel economy, chemical processes with ultra-precise control and minimal waste, or spacecraft and satellites). Currently, standard packaging techniques in the market developed for Si based devices, offer maximum temperatures up to about 175 °C. This insufficient maximum working temperature severely constrains the levels of power density and environment that SiC and GaN devices can operate (350 °C and higher) [26, 27, 28].

The capability to use power electronics devices at elevated temperatures will not only make new products and applications possible (such as those mentioned above), but it will also decrease the cooling requirements of more standard applications, avoiding large, heavy, and complex cooling systems. For example, if a power transistor is dissipating 10W to the ambient air at 25 °C through a heat-sink with a thermal resistance of 10 K/W, the semiconductor temperature reaches 125 °C, a relatively safe

| Technologies                                    |                   | Advantages                                                                                                                                                                                                                                                                                             | Disadvantages/concerns                                                                                                                                                                                                                               |

|-------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wire-bonding<br>(IGBT, MOSFET)                  |                   | <ul> <li>✓ High flexibility to adapt to various devices;</li> <li>✓ No special requirement on wafer processing;</li> <li>✓ Lowest cost per connection;</li> <li>✓ Improved reliability.</li> </ul>                                                                                                     | <ul> <li>Low throughput due to sequential bonding process;</li> <li>Large parasitic noises due to long interconnect path;</li> <li>Poor thermal management;</li> <li>Inapplicable to 3D integration.</li> </ul>                                      |

| Press-pack<br>(GTO,IGCT,IGBT)                   |                   | <ul> <li>✓ Best reliability due to fatigue-free structure;</li> <li>✓ Explosion-free;</li> <li>✓ Low thermal impedance, double-sided cooling.</li> </ul>                                                                                                                                               | <ul> <li>Special cooling scheme;</li> <li>Special insulation approach;</li> <li>Hermetic sealing;</li> <li>High cost packaging.</li> </ul>                                                                                                           |

| Multilayer<br>Technologies<br>(IGBT,<br>MOSFET) | GE POL            | <ul> <li>✓ Much better electrical performance than wire-bonding due to short interconnect path;</li> <li>✓ 3D, multilayer integration applicable.</li> </ul>                                                                                                                                           | <ul> <li>High parasitic capacitance;</li> <li>Lack of stress reliever between silicon and copper interconnect (high demand for structure cohesion);</li> <li>Processing complexity;</li> <li>High cost due to laser drilling, sputtering.</li> </ul> |

|                                                 | Embedded<br>power | <ul> <li>✓ Compatible with hybrid thick-film processing;</li> <li>✓ Much better electrical performance than wire-bonding due to short interconnect path;</li> <li>✓ 3D, multilayer integration applicable.</li> </ul>                                                                                  | <ul> <li>High parasitic capacitance;</li> <li>Lack of stress reliever between silicon and copper interconnect (high demand for structure cohesion);</li> <li>Processing complexity;</li> <li>High cost due to laser drilling, sputtering.</li> </ul> |

| ThinPack<br>(MCT)                               |                   | <ul> <li>✓ Good heat dissipation due to largearea soldering on both sides and the use of ceramic lid;</li> <li>✓ Much better electrical performance than wire-bonding due to short interconnect path;</li> <li>✓ 3D, multilayer integration applicable.</li> </ul>                                     | <ul> <li>Reliability concern for large-area soldering.</li> </ul>                                                                                                                                                                                    |

| Area array solder<br>Bumping<br>(IGBT, MOSFET)  |                   | <ul> <li>High packaging density;</li> <li>Much better electrical performance than wire-bonding due to short interconnect path;</li> <li>3D, multilayer integration applicable;</li> <li>Lower cost than deposit metallization;</li> <li>ThinPack, or press-pack;</li> <li>Good reliability.</li> </ul> | <ul> <li>Requires additional wafer processing;</li> <li>High cost for low-volume package;</li> <li>Fatigue of solder alloys.</li> </ul>                                                                                                              |

Table 2.1. Pros and cons summary of various power packaging technologies [16].

value for typical Si power devices. If a similar transistor, made for example on SiC, can operate at higher temperatures, a smaller heat-sink with, let's say 20 K/W of thermal

resistance, brings the semiconductor temperature up to 225 °C. This trade-off between maximum device temperature and cooling system complexity has been considered a practical and simple way to increase the integration level in power converters.

As stated before, the implantation of this kind of solutions is slow due mainly to packaging limitations. Nowadays, some high temperature power packaging solutions are available, although they are usually expensive and are used in high added value applications such as space or military systems. Let's mention for example the metallic TO-257 package used for blocking-diodes in the solar panels of the Bepi-Colombo and Solar Orbiter ESA (European Space Agency) missions to Mercury and the Sun, respectively [29]. This package has been proved between -150 °C and 300 °C, but its fabrication involves expensive materials, such as Au, Ag, BeO ceramics, AuGe alloy, or ceramic feed-through, and relatively complex assembling processes, such as hermetic sealing. Research efforts in many R+D labs are now ongoing, aiming at low cost and reliable technologies. For example, [30, 31] describes a recent power module based on power SiC devices, able to operate with semiconductor temperatures up to 250 °C. The proposed solution follows a quite classical structure (similar to the one shown in Figure 2.8) and the main effort has been carried out on new materials and fabrication processes.

#### 2.4. Conclusions

Power electronics is a field of paramount economic and social importance, since it possibilities a high number of crucial applications. Power electronics systems are present in all the chains of generation, distribution and application of the electric energy. To provide a wide view on the framework of this work, this chapter presents the main power electronics applications and the used semiconductor devices.

The interface between the power devices and the application circuit is given by their package. Power electronics packaging must provide electrical interconnection to the device, heat extraction capability and mechanical and environmental protection. Thus, power packaging is one of the key elements in power electronics development, and it requires, at least, the same research efforts than semiconductor power devices and power converters. A detailed analysis of the main power packaging elements and materials has been also addressed in this chapter. Current available packaging

technologies and recent advanced packaging solutions have been presented for the two main scenarios of this field: discrete power devices and multi-chip power modules.

It has been discussed that power packaging involves many engineering fields due to the different physical phenomena present in such heterogeneous systems. In this sense, the thermal and thermo-mechanical issues in power electronics packages are becoming an ever more important concern. Today, the thermal and thermo-mechanical performances are being pushed from the device to the package limit by increasing heat fluxes, continued miniaturization and higher switching speeds.

Finally, it has also been explained that the performances of power electronic systems (mainly their integration level) become improved if high temperature semiconductor devices are used. Such high temperature devices also allow the development of new and crucial applications related with high environment temperatures (aerospace, automotive, etc.). Currently, the silicon technology reached its physical limits and a great effort in R+D is being done to develop devices based on wide bandgap semiconductors, such as SiC, GaN or Diamond. SiC and GaN devices with maximum operation temperatures up to 300 °C are starting to be available, and one of the limiting elements for their implantation is the package.

All technological elements required for a high temperature (300 °C) package showing high voltage and current capabilities must provide the same final reliability already reached for standard packaging solutions. Thus, the key points to reach this target not only involve an optimal thermal design of the package, but also an accurate thermo-mechanical study on die-attach, chip-to-package interconnections (wire- or bump-bonding) and encapsulants. This high temperature power packaging scenario will constitute the framework of the present research work, where the focus will be addressed to the thermo-mechanical reliability analysis of the die-attach layers, in particular for high temperature operation with special focus on Ag nano-particles sintering.

#### 2.5. References

- [1] S. Wen. "Thermal and Thermo-Mechanical Analyses of Wire Bond vs Three-dimensionally Packaged Power Electronics Modules," Thesis, Virginia Polytechnic Institute, December 1999.

- [2] X. Perpinyà. "Mesura de la Temperatura interna en Dispositius de potencia," Màster Thesis, Universitat Autònoma de Barcelona, Setembre 2002.

- [3] N. Mohan, T. Undeland, W. Robbins. "Power Electronics: converters, applications and design," New York. Wiley, 1994.

- [4] P. L. Hower, S. Pendharkar, and T. Efland, "Current Status and Future Trends in Silicon Power Devices," *in Proc. IEEE Int. Electron Devices Meeting Conference*, pp. 13.1.1–13.1.4, 2010.

- [5] J.A. Lainert, C. Knight, V. McKinney, and Ehrhardt-Martinez, K.ACEEE Report E094, May 2009.

- [6] B. J. Baliga, "The Future of Power Semiconductor Device Technology," *IEEE*, vol. 89, issue: 6, pp. 822-832, June 2001.

- [7] B. J. Baliga. "Evolution and Status of Smart Power Technology," *in Proc. Applied Power Electronics Conference and Exposition* (APEC), pp. 18-21, 1993.

- [8] A. Pérez-Tomás, X. Jordá, P. Godignon. "Optimization of a very cost-effective high voltage p-channel transistor implemented in a standard twin-tub CMOS technology," *Microelectronic Engineering*, vol. 77, issue 2, pp. 158-167, 2005.

- [9] A. Pérez-Tomás, X. Jordá, P. Godignon, J.L. Gálvez, M. Vellvehí and J. Millán. "IGBT gate driver IC with full-bridge output stage using a modified standard CMOS process," *Microelectronics Journal*, vol. 35, issue 8, pp. 659-666, 2004.

- [10] B. J. Baliga, Adler, M.S. Gray, P.V. Love, R. P. Zommer N. "The insulated gate rectifier," *in Proc. Electron Devices Meeting* (IEDM), vol. 28, pp. 264-267, 1982.

- [11] A. Nakagawa, Y. Kawaguchi, K. Nakamura, "Achieving Material Limit Characteristics in Silicon Power Devices," in Proc. International Workshop on Physics of Semiconductor Devices (IWSPD), pp. 762-767, 2007.

- [12] M. T. Rahimo. "Ultra High Voltage Semiconductor Power Devices for Grid Applications," in Proc. IEEE Electron Devices Meeting (IEDM), pp. 13.4.1-13.4.4, 6-8 December 2010.

- [13] W.W.Sheng, R.P. Colino, "Power Electronic Modules, Design and Manufacture," CRC press, 2005.

- [14] M. Pecht, "Handbook of electronic package design," Marcel Dekker, New York, 1991.

- [15] C. Wang, "High Temperature High Power SiC Devices Packaging Processes and Materials Development," Thesis. Auburn University, August 2006.

- [16] S. Wen, "Design and Analyses of a Dimple Array Interconnect Technique for Power Electronics Packaging," Thesis, Virginia Polytechnic Institute, August 2002.

- [17] Eupec, a power semiconductor producer, www.eupec.com.

- [18] H. Matsuda, ; M. Hiyoshi, and N. Kawamura, "Pressure Contact Assembly Technology of High Power Devices," *in Proc. IEEE International Symposium on Power Semiconductor Devices and IC's*, pp. 17-24, May 1997.

- [19] V. Banu, P. Godignon, X. Perpiñà, X. Jordà, J. Millán, "Enhanced power cycling capability of SiC Schottky diodes using press pack contacts," *Microelectronics Reliability*, vol. 52, no. 9-10, , pp. 2250-2255, 2012.

- [20] X. He, X. Zeng, X. Yang, and Z. Wang. "A Hybrid Integrated Power Electronic Module Based On Pressure Contact Technology," in Proc. IEEE Power Electronics Specialists Conference (PESC '06), pp. 1-5, 18-22 June 2006.

- [21] B. Ozmat, C. S. Korman, P. McConnelee, M. Kheraluwala, E. Delgado and R. Fillion. "New Power Module Packaging for Enhanced Thermal Management," in *Proc. 7th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems* (ITHERM), Las Vegas, Nevada, vol. 2, pp. 287-296, 2000.

- [22] Z. Liang, F.C. Lee. "Embedded Power Technology for IPEMs Packaging Applications," in Proc. Applied Power Electronics Conference and Exposition (APEC), vol. 2, pp. 1057-1061, 4-8 March 2001.

- [23] V. Temple, "ThinPak Technology Shrinks Power Modules, Power Hybrids and Ultra-High Speed Switching Devices," pp. 32-38, May 2000.

- [24] C.C. Meng, S. Stoeckl, H. Pape, F. M. Yee, and T.A Min. "Thermo-Mechanical Modeling of a 3D Flip Chip Fully Populated BGA Package," *in Proc. Electronics Packaging Technology Conference* (EPTC), pp. 637-640, 8-10 December 2010.

- [25] F.P. McCluskey, R. Grzybowski, and T. Podlesak. "High Temperature Electronics," CRC press 1997.

- [26] M. Östling. "Silicon Carbide Based Power Devices," in Proc. IEEE Electron Devices Meeting (IEDM), pp. 13.1.1-13.1.4, 2010.

- [27] Z. Lin, and J. Yoon. "An AlN-based High Temperature Package for SiC Devices: Materials and Processing," in Proc. International Symposium on Advanced Packaging Materials: Processes, Properties and Interfaces, pp. 156-159, 16-18, March 2005.

- [28] R. W. Johnson, C. Wang, Y. Liu, J. D. Scoffeld. "Power Device Packaging Technologies for Extreme Environments," *IEEE transactions on electronics packaging manufacturing*, vol. 30, pp. 182-193, July 2007.

- [29] P. Godignon, X. Jordà, M. Vellvehi, X. Perpinyà, V. Banu, D. López, J. Barbero, P. Brosselard, and S. Massetti. "SiC Schottky Diodes for Harsh Environment Space Applications," *IEEE Transactions on Industrial Electronics*, vol.58, issue 7, pp. 2582-2590, July 2011.

- [30] J. Hornberger, A. B. Lostetter, K. I. Olejniczak, T. McNutt, S. Magan Lal and A. Mantooth. "Silicon-Carbide (SiC) Semiconductor Power Electronics for Extreme High-Temperature Environments," in Proc. IEEE Aerospace Conference, vol. 4, pp. 2538-2555, 2004.

- [31] J. M. Hornberger, S.D. Mounce, R.M. Schupbach, A.B. Lostetter and H. A. Mantooth. "High-Temperature Silicon Carbide (SiC) Power Switches in Multichip Power Module (MCPM) Applications," in Proc. IEEE Industry Applications Conference, vol. 1, pp. 393-398, 2005.

# CHAPTER 3 Ag Nano-Particles Sintering as Die-Attach Solution

#### 3.1. Introduction

As described in the previous chapter, a typical power electronics package is made of diverse materials, each one having different mechanical properties. From the long-term reliability viewpoint, the difference in the coefficient of thermal expansion (CTE) between adjacent materials (e.g., die, die-attach and substrate) is the most limiting factor, since it induces thermo-mechanical strains during power packaging manufacturing or under operation conditions, which compromises and fixes the package wear-out. The thermo-mechanical strain may be associated with deformations and with resulting mechanical stresses during local or global temperature changes. In fact, temperature changes are commonly encountered during the device manufacturing or packaging, such as vapour depositions and soldering operations, and under actual working conditions, for instance switching operation and global environmental temperature changes.

The description and basic analysis of the die-attach technology based on sintering of Ag particles is the main objective of the present chapter. For this reason, first, the framework will be introduced by describing the main categories of die-attach materials and their thermo-mechanical properties, which determine the behaviour under working conditions. Then a brief review of most used methods for failure analysis (FA) will be provided, as well as the description of the methods used in this study to analyse the quality and the degradation of the die-attach layer. The chapter ends with the description of the sintering theory, and its adaptation to allow sintering as a die-attach technique.

#### 3.2. The Die-Attach Layer in Power Electronics Assemblies

The die-attach constitutes one of the most critical part of power devices assemblies. In order to ensure that the package is a mechanically reliable and thermally/electrically efficient system, is very important satisfy certain requirements. These requirements include sufficient adhesion between die and substrate, so that the die does not detach from the substrate, resilience to provide stress relaxation on the die (for suitable reliability), high thermal conductivity to dissipate heat, low electrical resistivity to minimize conduction losses, CTE matching between both substrate and die, ability to process at appropriate temperature (not too high) and good stability at operating temperature.

There are many categories of die-attach, including both high and low temperature use. The main categories are: solder alloys (eutectic and soft soldering), electrically conductive adhesives (ECA) based on polymers, and silver based die-attaches (such as silver glass die-attach, silver indium based and silver based on sintering of particles) [1]. The most relevant materials are summarized in Table 3.1. Among them, die-attach solder alloys are the most used and become a standard solution. Pure silver has been also included in Table 3.1 in order to compare its properties with those of the sintered nano-Ag. It is interesting to highlight that Ag has the highest electrical conductivity and the second best thermal conductivity among all materials, showing also good mechanical properties. Its high melting temperature enables it to work at higher temperatures than usual solders. For this reason, this material is used as a basis for different solder technologies.

Solder alloys are usually tin-, lead-, gold- or indium-based. Rich lead alloys (for example Pb95.5Ag2.5Sn2) have been used as the reference die-attach material for decades as they present a low cost and good ductility (which leads to lower stresses). As a result they exhibit robustness against failure [2, 3], but they have a lower melting point in comparison to hard or stiffer solders. For this reason, they are not suitable for very high temperature applications. Furthermore, lead-based alloys are not environmentally friendly and therefore several legislations around the world are gradually limiting the use of lead in electronics [4, 5]. To address this concern several Pb-free alternatives have emerged in response to these requirements. Among them, the most representative are Pb-free alloys, ECAs, and die-attach based on sintering of particles.

In the case of pb-free alloys, SnAg-based alloys are nowadays used in many applications, but are limited for standard operation temperatures. Gold-based eutectics

like AuSi, AuSn, and AuGe show higher ultimate tensile strength, and consequently offer excellent fatigue and creep resistance for high temperature applications (owing to the maximum working temperature of the device is limited by the eutectic temperature of the solder alloy). The disadvantage is primarily due to their stiffness which leads to high stresses (which arise due to thermal expansion mismatch among the die, die-attach, and the substrate) in the semiconductor. Besides, the high cost is another inconvenient.

| Material              | Melting / Processing Temperature (°C) | Density<br>(Kg/m³) | Thermal Conductivity (W/m °C) | CTE<br>(ppm/°C) | Young<br>Modulus<br>(GPa) | Poisson<br>ratio |

|-----------------------|---------------------------------------|--------------------|-------------------------------|-----------------|---------------------------|------------------|

| Ag                    | 961 [6]                               | 10500 [6]          | 430 [6]                       | 19 [6]          | 76 [6]                    | 0.37 [7]         |

| Au80 Sn20             | 280 [6]                               | 14700 [6]          | 58 [6]                        | 16 [6, 8]       | 68 [6]                    | -                |

| Au88 Ge12             | 356 [9, 10]                           | 14670 [11]         | 44 [9, 10]                    | 13 [9, 10]      | 63 [9 ]-<br>72.74 [11 ]   | 0.32 [12]        |

| Au97 Si3              | 363 [9]                               | 1568 [9]           | 293 [9]                       | 11 [9]          | 69.5 [9]                  | -                |

| Pb95.5 Ag2.5<br>Sn2   | 300 [6]                               | 11200 [6]          | 23 [6]                        | 30 [6]          | 13.8 [6]                  | -                |

| Sn60 Pb40             |                                       | 9000 [13]          | 50 [13]                       | 21 [13]         | 10 [13]                   | 0.4 [13]         |

| Sn37 Pb37             | 183 [6]                               | 8500 [6]           | 51 [6]                        | 25 [6]          | 16 [6]                    | -                |

| Sn93.6 Ag4.7<br>Cu1.7 | 218 [14]                              | 7400 [14]          | 55 [14 ]                      | 21 [14]         | 31 [14]                   | 0.4 [14]         |

| Sn96.5 Ag3.5          | 221 [9]                               | 7360 [11]          | 33[11]                        | 26.5[15]        | 38.5 [15]                 | 0.29 [15]        |

| Sintered nano Ag      | 280 [6]                               | 8600 [6]           | 240 [6]                       | 19 [6]          | 9 [6]                     | -                |

Table 3.1. Properties of die-attach materials.

ECAs involve of a polymeric resin, which provides physical and mechanical properties such as adhesion, mechanical strength, impact strength, and metal filler that conducts electricity. Usually, the polymeric resin is an epoxy, a silicone, or a polyimide and metal filler can be silver, gold, nickel or copper [5]. ECAs are widely used as attachment materials due to their low cost and easy manufacture. These adhesives are not used for ceramic or hermetic metallic packages because the temperatures required to finish the encapsulation process after the die-attach, may degrade the properties of the adhesive. The polymer-based adhesives offer many advantages such as lower stresses due to low Young's modulus and curing (processing) temperature, ease of use in a manufacturing environment, and low cost compared to conventional solder technology. Nevertheless, they show worst thermal and electrical properties than metals and their use is restricted to low- and medium-power applications. Another disadvantage is

conductivity fatigue owing to high temperatures and humidity aging decreases the conductivity [1, 5].

Among silver-based technologies, the silver glass die-attach, is an adhesive paste formed by silver (micro-flakes) and glass particles in an organic solvent medium [16]. This technology needs high temperature firing above 600 °C during processing to create an appropriate die-attach. In fact, pressure can be used in order to reduce the firing temperature [17]. In the same sense, some researchers have been reported that this technology have been showed satisfactory adhesion and have been provided high thermal and electrical conductivity. Moreover, it has been demonstrated extremely resistant to degradation during temperature cycling from -65 °C to 150 °C. Nevertheless, the main disadvantage is its lengthy processing techniques, which are unsuitable for mass manufacturing purposes [6, 17].

Another silver based technology is a silver indium based. A film with 20 wt% of Indium (Ag-In<sub>20</sub>) and therefore with a melting temperature beyond 700 °C was created via thermal evaporation [1]. Besides, a silver-indium die-attach for high temperature at low process temperature of 206 °C was obtained with practically void-free and uniform thickness around of 7.2 to 7.8µm. In fact, the process of the Ag-In die-attach requires two steps. The aim at first step is to produce the joint and the second step is for increase the melting temperature of the die-attach by an annealing process. Several Ag-In intermetallic layers are formed during process, but in particular, the intermetallic compound Ag-In<sub>2</sub> avoids the indium layer oxidation. Apparently this technology is very promising, but its disadvantage is its very long process.

Due to good physical properties of the Ag is widely used as basic material on sintering of particles. In the case of nano-scale particles is interesting because the bonding process can be performed at a temperature lower than that of the die-attach melting point. Therefore, is possible avoid the use of the high pressures, which is common in micro-scale particles [17, 18]. Moreover, they present the advantage of a low residual stress (owing to low-temperature process) and a better suitability for high-temperature operation (owing to high melting temperature). Besides, this property will avoid the remelting problem in the assembly processes of packaging. In fact, this property will be further discussed in section 3.4.

In the case of Ag nano-particle sintering, the porous microstructure of nano - scale sintered Ag can relieve the thermo-mechanical stresses generated from mismatched CTEs in the joined structure. Nano-particles Ag sintering seems to be a very promising die-attach solution also for high temperature applications, though it is still undergoing reliability studies,[3, 19, 20].

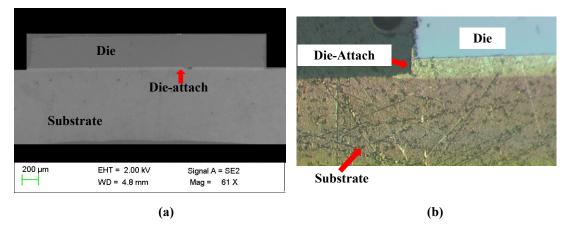

# 3.3. Methods for the Assessment of Die-Attach Layers

The die-attach layer is the joint between die and substrate in a package. In order to assess this layer, in this study we have used the following systems and methods: Optical Microscope, Optical Imaging Profiler, SAM (Scanning Acoustic Microscope), SEM-EDX, FIB-SEM and a specific tool for obtaining the adherence force between die and substrate (die-shear tester). The description of each technique, the associated equipment, its characteristics and some specifications are described below:

Optical Microscope is a non-destructive system for failure analysis. It uses the visible light and a system of lenses with the aim at magnifying the sample image to detect physical defects. In this study optical microscopy was used for obtaining optical micrographs of the tests vehicles at different phases of the experimental research. In fact it was the most used technique in this study.

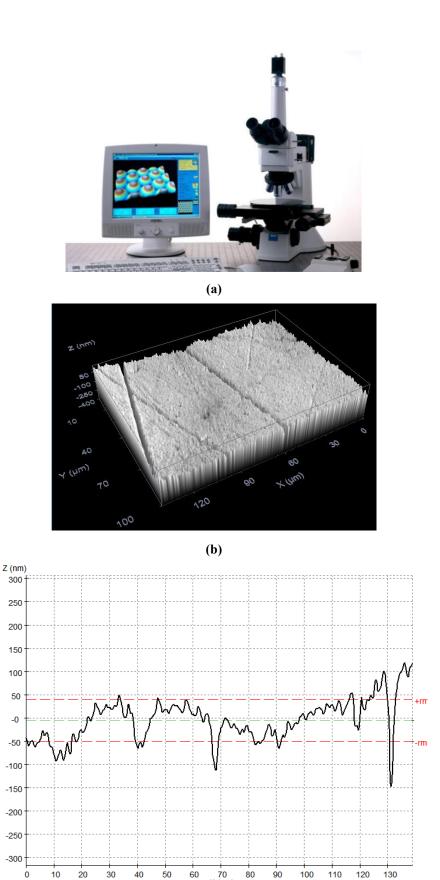

Optical Imaging Profiler (Sensofar PLu 2300) is a non-destructive system that is constituted by an independent sensor head, which combines interferometry and white light confocal imaging techniques (see Figure 3.1(a)). The system acquires three-dimensional images of surface profiles, therefore, it can obtain measures of surface roughness and thickness of samples. In this study, the imaging profiler was mainly used to obtain surface roughness and the thicknesses of Cu substrates and semiconductor dice (Si and SiC) [21]. Figure 3.1(b) shows an image of the surface roughness of the Cu polished substrate in a small area of 138 x 102μm². In this case the Ra is approximately 35 nm. Figure 3.1(c) shows the roughness profile of the same polished substrate along X axis.

-100 -150 -200 -250 -300

Figure 3.1. (a) Sensofar PLu 2300 optical imaging profiler used to obtain roughness measurements. (b) Confocal image of a polished substrate (Ra= 35 nm). (c) Surface profile of the roughness in the X axis.

(c)

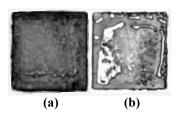

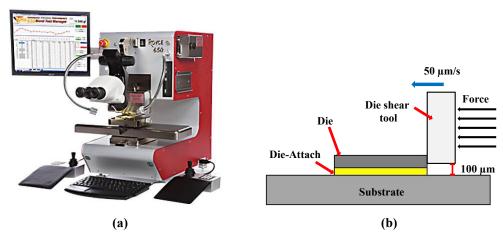

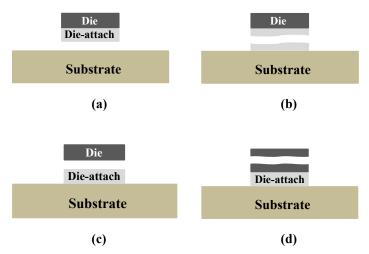

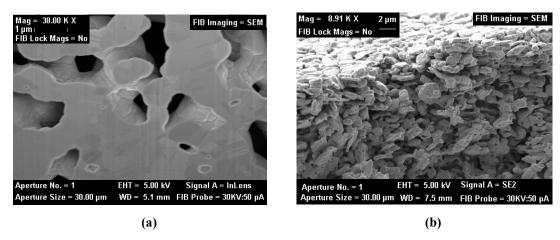

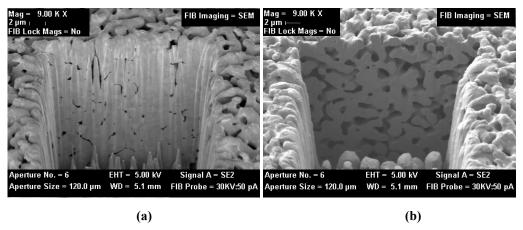

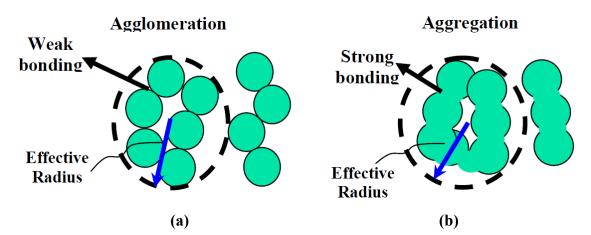

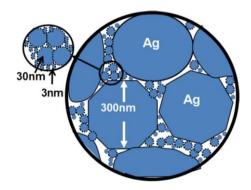

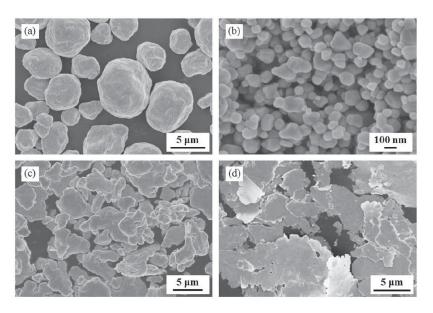

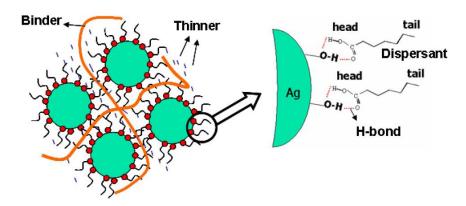

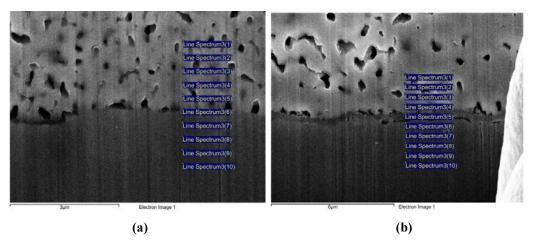

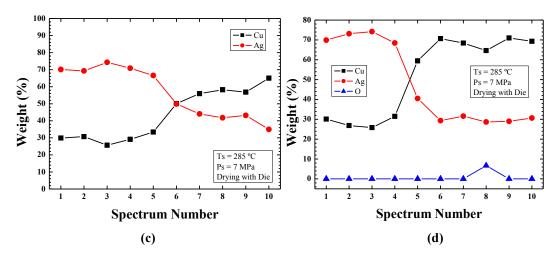

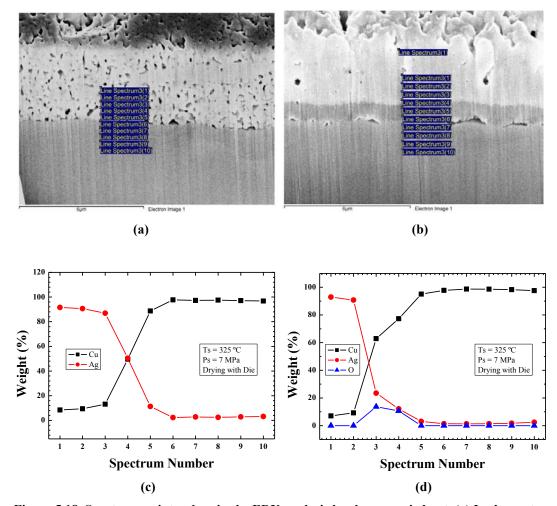

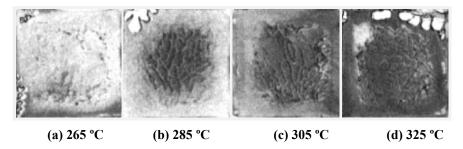

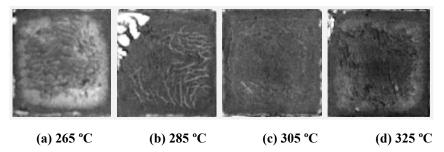

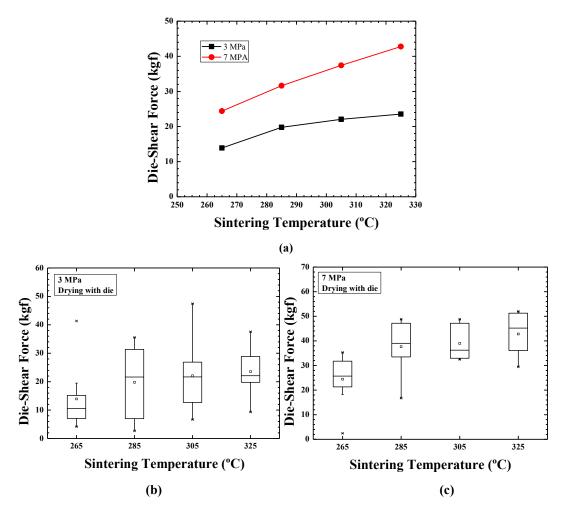

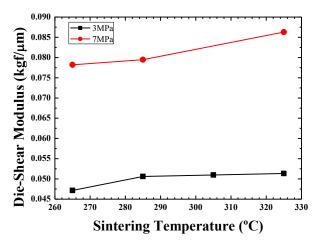

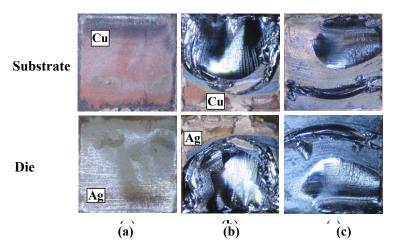

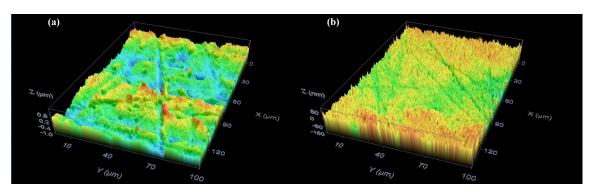

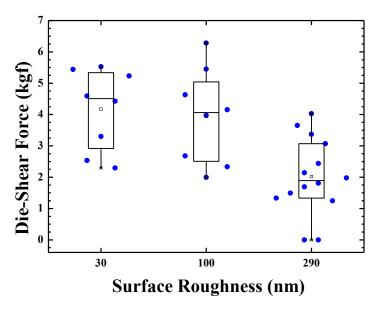

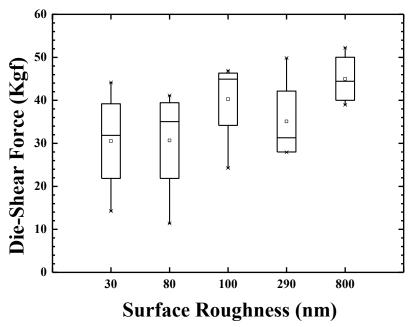

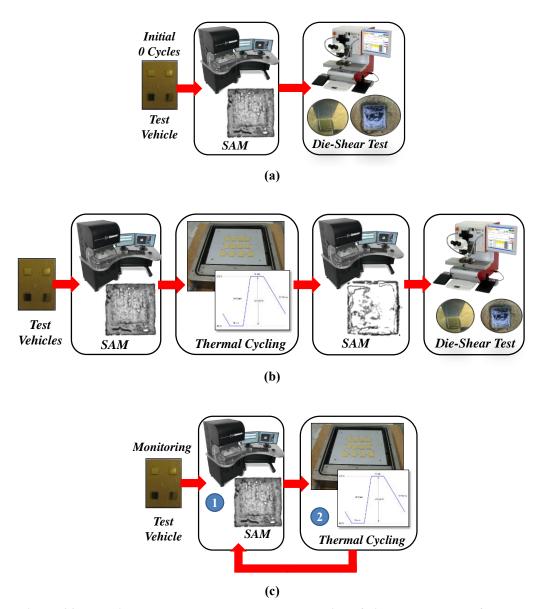

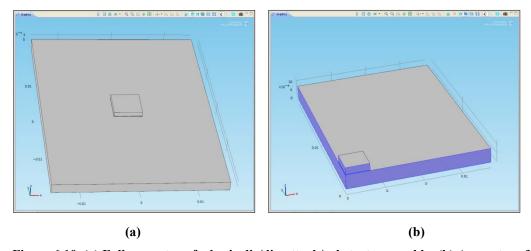

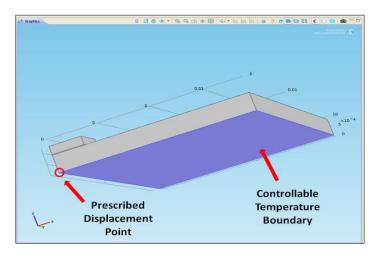

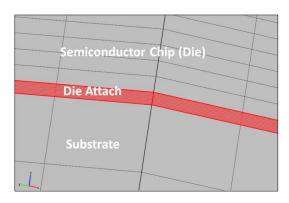

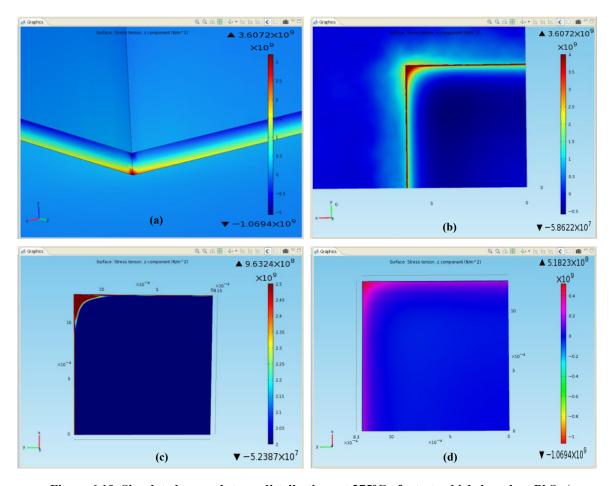

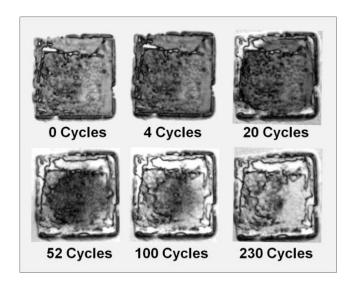

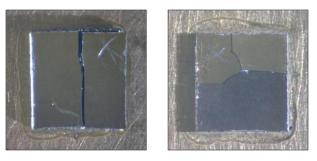

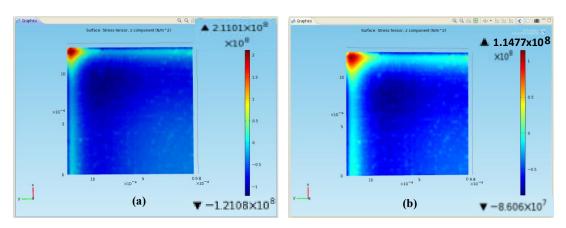

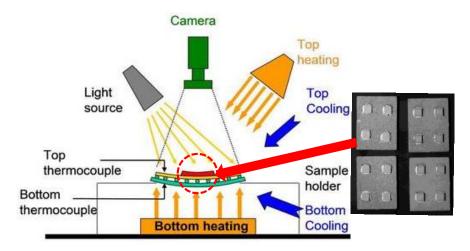

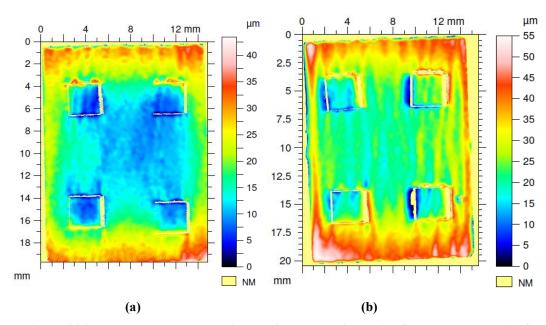

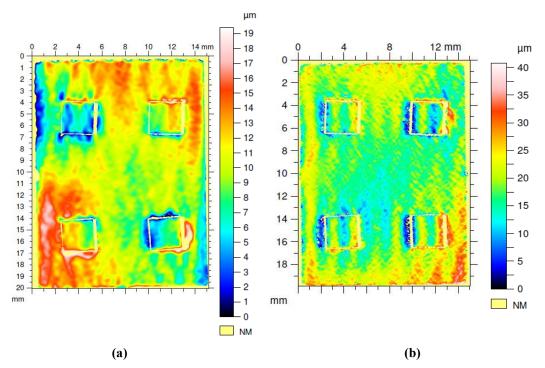

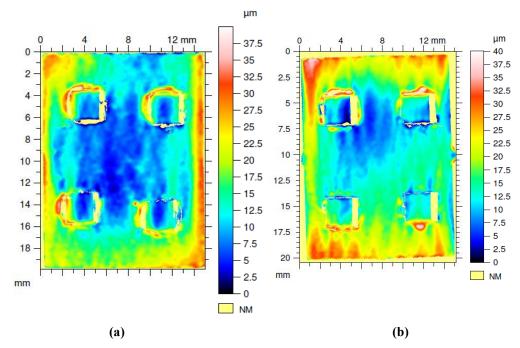

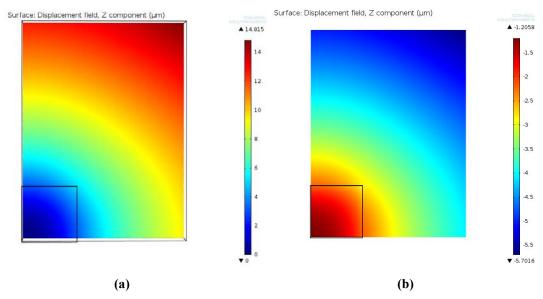

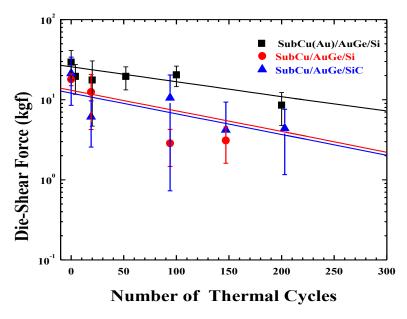

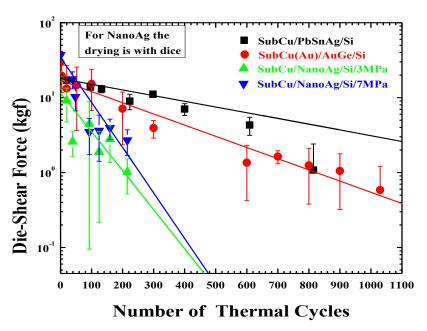

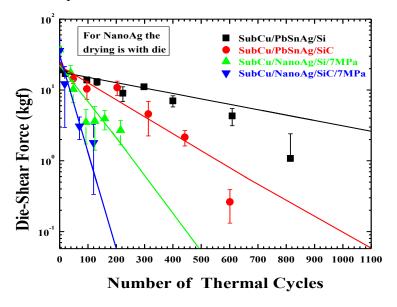

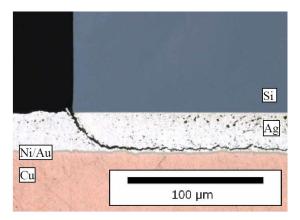

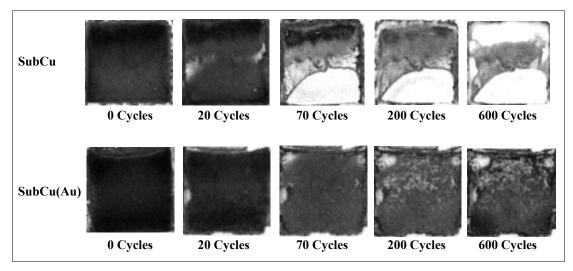

Scanning Acoustic Microscope (SAM) Sonoscan GEN-5 (see Figure 3.2) [22], is a non-destructive system that uses sound waves between 10 MHz and 240 MHz to acquire images, which can be useful to detect defects (failures) inside a package structure, originated during manufacturing or during accelerated testing. The failures (delamination, voids, cracks, etc.) appear mainly between interfaces of the package structure, i.e., failures in bonds, lead frames or die-attach materials. There are two basic SAM approaches, based on processing the echoes returned by the package (reflected echo) or processing the waveform of the sound transmitted at the opposite extreme of the package (transmission inspection). In the present study, only reflected echoes have been considered.