Nanomechanical structures are defined using EBL. The complete process consists of EBL, metal deposition, lift off, RIE and wet etching. A variety of resonating structures are fabricated on different substrates. Discrete devices serve to establish the EBL design and exposure conditions, metal deposition and etching processes parameters. Combination with UV lithography facilitates the electrical characterization of device performance. A procedure for precise alignment is established. EBL is used to define nanomechanical structures monolithically integrated into CMOS circuitry. CMOS enhances the resonator signal for high sensitivity applications. A complementary approach using FIB direct machining is also presented. Both methods are adapted to keep the integrity of the CMOS circuitry.

# 4 Fabrication of nanomechanical devices

# 4.1 Introduction to nanomechanics

Mechanics as a discipline deals with the response of structures to applied forces. The working principle is easily visualised in terms of energy. The whole process can be treated in terms of the accumulation of applied force in the form of potential energy. Ideally, this energy is converted to movement. The motion of the mechanical element is determined by the structure shape, mass, dimensions, material and external forces. For clamped elements, there are two main displacement modes, dynamic (vibration) or quasi static (deflection).

Vibration consists of oscillation about an equilibrium point. In the resonance state, the amplitude of vibration is maximized at a certain frequency. The efficiency of the energy conversion is measured in terms of the quality factor, Q, that quantifies the amount of dissipated energy. Indeed, real structures are subject to frictional forces.

Deflection is the response of the mechanical structure to loading forces. It causes structure deformation from the equilibrium point and, in the eleastic regime, it returns to the origin if no force is applied. An excess in the applied force may cause the break or permanent deformation of the movable element, since plastic range is reached.

Mechanical devices are used in combination with a transducer, to constitute the mechanical system. Transduction is the conversion of the movement measurement to another signal type, typically electrical or optical. It includes both the movement excitation (actuation) and the sensing operation (detection). Electromechanical systems are formed by mechanical elements coupled to electronics circuits using an electromechanical transducer, this is, conversion of electrical energy into mechanical energy (motion or displacement), or viceversa. The miniaturization of mechanical elements and their combination with microelectronics evolved in the

microelectromechanical systems (MEMS). MEMS comprise a great number of daily used applications (1).

The feasibility of higher resolution in lithography and fabrication methods allows to reduce the mechanical structures down to the nanoscale range (2). As an alternative method, bottom up approaches can be introduced to fabricate this kind of systems. Hence, nanoelectromechanical systems (NEMS) are feasible. The interest of NEMS is not only seen as the natural evolution of MEMS miniaturization, but also may support the research in nanoscience. For mesoscopic or nanoscale devices, surface effects begin to be significant for the device performance and models based on macroscopic mechanics may not be valid anymore. This, far from being a limitation, can be exploded for a great number of applications, ranging from higher resolution sensing to fundamental science (3).

The ideal type of NEMS would be those where monitored phenomena exhibit large and measurable changes for small displacements of the nanomechanical structure. In consequence, higher frecuencies and weak applied forces generate faster and low power devices, in addition to provide spatially localized response. The possibility to precisely tailor their geometry allows to determine the motion direction.

However, the complete control over the NEMS technology encounters three main challenges. The magnitude of the displacement signals usually is directly proportional to the structure dimensions, the mechanisms that involve can differ from the controllable or understandable processes and system fabrication is often difficult to be absolutely reproducible or controllable. In practice, dissipation and noise play a central role in the NEMS characterization and improvement and the development of valid applications.

One of the typical nanomechanical device is the doubly clamped beam. As an example, the description of the mechanical model is included and it serves to illustrate the resonating structure performance and specifications that are crucial. Also, the dissipation and noise sources are presented, specially, in relation to the transduction system. Hence, this general overview ought to support the relation of results presented in this chapter. The results discussion is focused only in the fabrication process and, specifically, based on EBL as the patterning technique.

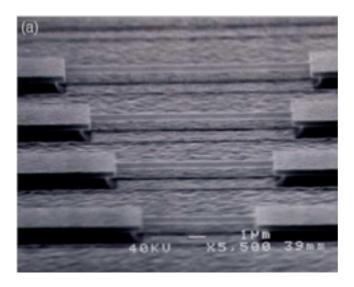

Figure 4.1 Example of doubly clamped beams. Done in the same structuring material and equivalent width (w) and thickness (t), the difference in lenght (l) implies different natural resonance frequency for each structure ( $\omega_0 \alpha 1/l^2$ ), from reference (3).

The beam motion can be described as a 1D (out of plane) harmonic oscillator, which displacement, x(t), is expressed by,

$$\frac{d^{2}x(t)}{dt^{2}} + \frac{\omega_{0}}{Q} \frac{dx(t)}{dt} + \omega_{0}^{2}x(t) = \frac{f(t)}{m_{eff}}$$

(4.1)

where, f(t) is the steering force,  $m_{eff}$  is the effective mass,  $\omega_0$  is the resonance frequency and Q the quality factor. In first approximation and in the vicinity of a mode resonance frequency, they are given as,

$$\begin{split} m_{\text{eff}} &= 0.735 \cdot l \cdot t \cdot w \cdot \rho, \\ \omega_0 &= 2\pi \cdot (1.05) \sqrt{\frac{E}{\rho}} \frac{t}{l^2} \\ k_{\text{eff}} &= 32E \cdot t^3 \frac{w}{l^3} \end{split} \tag{4.2}$$

where, l, t, w are the dimensions, E is the Young's modulus,  $\rho$  is the mass density of the beam and  $k_{eff}$  is the stiffness (4). The motion of the element is determined by the dimensions and materials that constitute it and it is restricted by the intrinsic energy dissipation and non idealities.

Applying the same development to the simplest mechanical structure, the motion characteristics for one side clamped beam (cantilever) are expressed as,

$$\omega_0 = 2\pi (0.17) \sqrt{\frac{E}{\rho}} \frac{t}{t^2}$$

$$k_{eff} = \frac{2}{3} E t^3 \frac{w}{t^3}$$

(4.3)

Scaling down the dimensions of the mechanical element leads to important consequences on their operation. In special, resonance frequency is inversely proportional to the size or mass sensitivity scales with the fourth power of length, what is interesting for high frequency applications or in terms of mass sensing resolution, respectively (Figure 4.2).

| magnitude                           | scaling factor  |

|-------------------------------------|-----------------|

| lenght, L                           | K               |

| area, A                             | K <sup>2</sup>  |

| volume, V                           | $K^3$           |

| mass, m                             | K <sup>3</sup>  |

| stiffness, k                        | K               |

| resonance frequency, f <sub>0</sub> | K <sup>-1</sup> |

| mass sensitivity, S                 | $K^4$           |

Figure 4.2 Magnitudes expressed in terms of the scaling factor.

The measurement of the motion is possible through the transducer, this is, the actuactor and the sensor. The transduction system is characterised in terms of sensitivity

or resolution: the capability to apply or to detect sufficiently small forces or displacements, respectively. The detection is characterised by the noise level and displacement responsitivity. The influence of the excitation method on the motion (backaction) is also critical, together with the coupling circuit, for the system resolution. The fabrication of the transduction and mechanical element on-chip often represents an improvement for the system performance.

There are two main techniques for the actuation, magnetomotive or electrostatic (capacitive) methods, while detection may be done by magnetomotive, optical, capacitive displacement and piezoresistive or piezoelectric detection and electron tunneling. Description of each one them is included in (1) and detailed description of each noise and dissipation sources can be consulted in (5).

# 4.2 Fabrication process

One of the key issues of NEMS is the fabrication of the nanomechanical device. In general, this is accomplished with the combination of MEMS micromachining with nanolithographic techniques. Nanopatterning provides the starting point for achievement of controlled submicronic features that are subsequently transferred to the substrate layers. Hence, the 3D movable structure is defined and ready to be connected to the transductor element, which is intended to carry out the actuation and sensing operations.

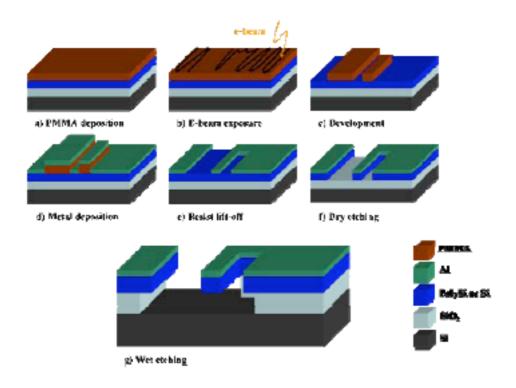

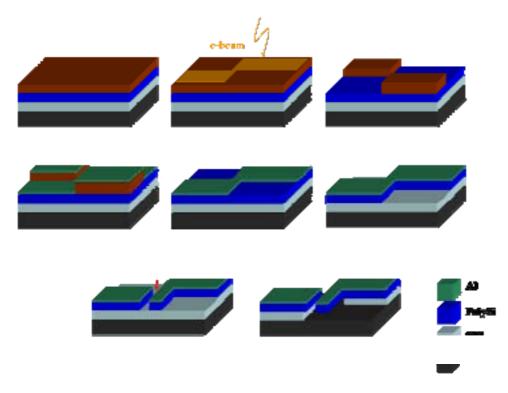

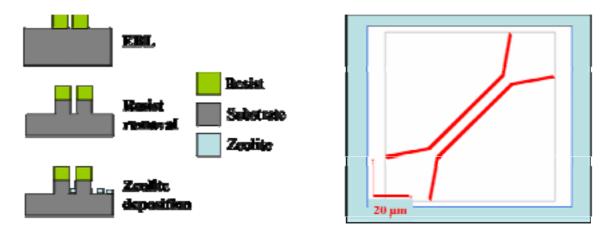

The general scheme for the fabrication of nanomechanical structures is illustrated in Figure 4.3 (6). EBL is the most commonly used technique for nanolithography in this kind of configurations. The process starts with the resist deposition by spin coating, electron beam exposure and resist development. After this, metal deposition and resist lift off defines the mask for the dry etching that transfers the pattern to the structural layer. The end of the process is the release of the structure by wet underetching of the sacrificial layer.

The use of EBL for patterning represents many advantages that provide an ideal lithographic platform for the NEMS fabrication. Its high resolution is capable of defining features down to the nanoscale if needed. More important, the pattern design flexibility may be very convenient for prototyping, since in these devices design optimization is often essential. In addition, the possibility to precisely align with other lithographic levels in a flexible and compatible way may be also very useful, as it is shown in the following sections. However, direct writing EBL may be limited for a rather low throughput, consequence of the serial addressing of the beam.

The rest of fabrication steps may be also challenging and they ought to be considered for the design of the pattern and also for the complete processing flow. Dry etching is characterised by its anisotropy. However, deep etchings require a robust mask capable of resisting the entire process and a good control over the etching profile, in terms of both directionality and scalloping. More generally, the undercut may be a problem for some configurations and limitations are encountered for etching narrow trenches, small features, etc. For the release of the structure, the main difficulties affect the design of the structure, together with the thickness of the sacrificial layer and etching time. Feature lateral size determines the configuration, but may be reasonable in terms of time and space, for example to avoid clamping structure collapse. In addition to this, drying after wet etching often causes the released structures to stick to the substrate. Some of these aspects and their experimental solution are described more in detail in the next section.

Figure 4.3 Scheme of the whole processing flow for the fabrication of free standing nanomechanical structures. It is based on EBL and metal lift-off, RIE and wet etching.

# 4.3 Fabrication of discrete nanomechanical devices

In this case, Silicon on Insulator (SOI) substrates are the base material for fabricating the nanomechanical structures. Two different SOI thicknesses are used, 0.6 and 1.5  $\mu$ m, on 1  $\mu$ m of SiO<sub>2</sub>. The SOI layer is highly n-doped by diffusion of phosphor at high temperature (surface doping:  $N_d = 10^{18}$  at·cm<sup>-3</sup>). Then doping impurities are thermally activated under O<sub>2</sub> and N<sub>2</sub> atmosphere. Therefore, it is not necessary to evaporate a metal for the contacts in the device characterization, after the release of the structures.

# Design of nanomechanical structures

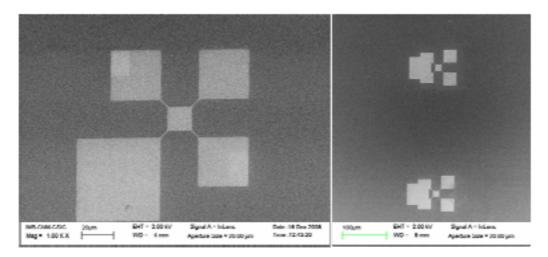

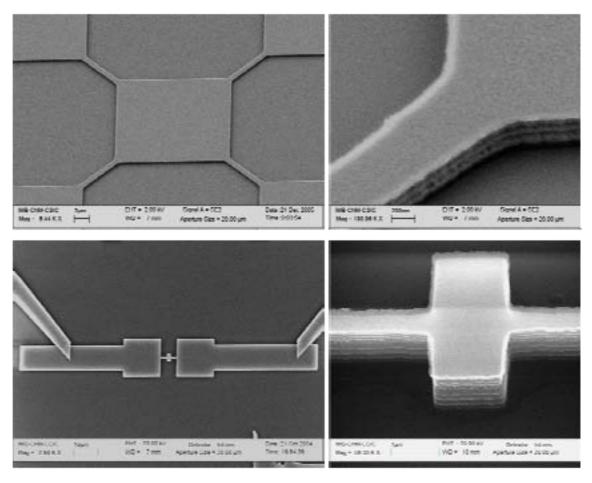

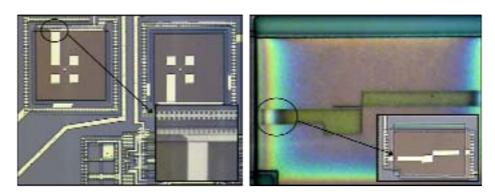

A variety of design structures are tested. Cantilevers, quad beams and paddles for lateral, vertical or torsional motion, respectively. In order to optimize their performance, also different pad configurations and device sizes are tested (Figure 4.4). The study of all these parameters and the electrical characterization of the devices has been performed by Julien Arcamone and it is compiled in his thesis (7).

Figure 4.4 Examples of different configurations for quad-beam structures. EBL pattern flexibility facilitates the optimization of the design.

Several different clampling structures are tested.

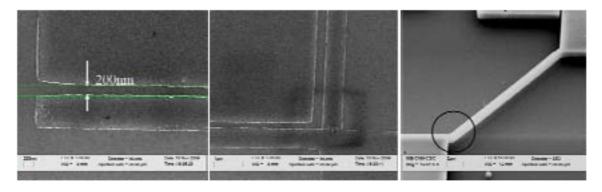

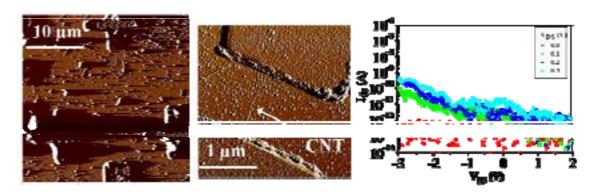

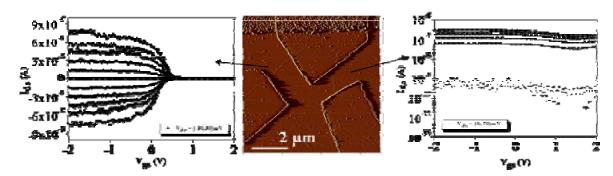

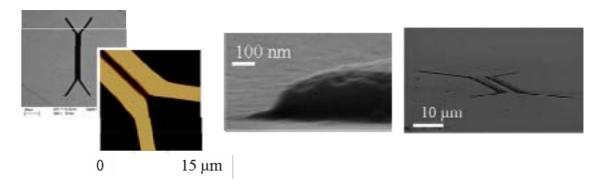

# Patterning of the structure by EBL

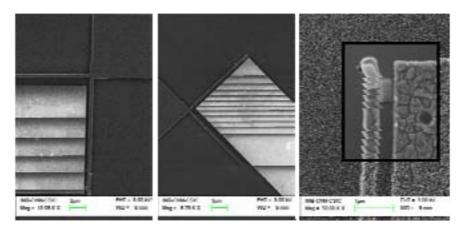

The patterning is based on EBL on a PMMA layer of ~100 nm at 10 keV beam energy and with a WF size of  $100 \times 100 \, \mu m^2$ . The design feature sizes are not difficult to obtain since they are typically of a few hundred nanometers, but precise definition of the structures in terms of symmetry, edge definition, etc is crucial. A thin layer of Al (24 nm) is deposited and lift off of the resist is performed on warm acetone with ultrasonic assistance and rinse in IPA and water. As can be seen in Figure 4.5, left, resulting structures show a good performance of the EBL in terms of resolution. However, some inaccuracies are also encountered. For example, for the double cantilever configurations, slight differences in the trench and cantilever width appear, even if the design is completely equivalent (Figure 4.5, center). In the case of quad beam structure, incorrecteness of anchor contact with the clampling areas and central plate may make worse the device performance (Figure 4.5, right). These defects are compensated by adjusting the pattern design, the cantilever widths and gap respect to the area, or exposing first the critical parts and enlarging the beams to ensure the proper contact.

Figure 4.5 Results of EBL in terms of accuracy and resolution. In the left, narrow trenches (200 nm) are obtained after metal deposition and lift off. However, uncertainties in the design reliability may cause defects when transferred to the structural layer. In the center, equivalent gap between driver and cantilever in the design is not experimentally obtained without correction (center) and anchoring placement is also ensured (right).

# Transference of the pattern to the structural layer by RIE

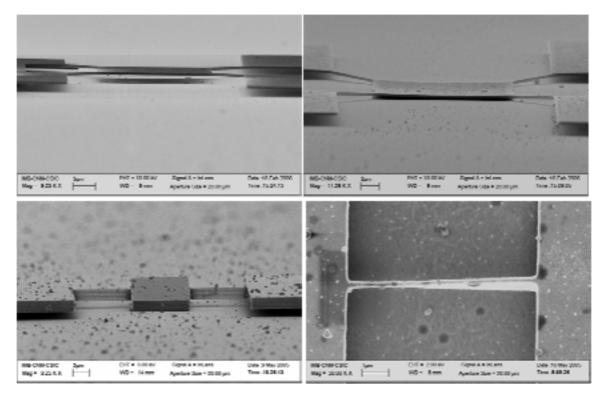

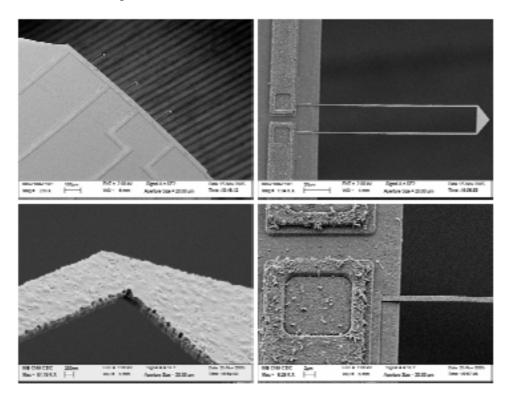

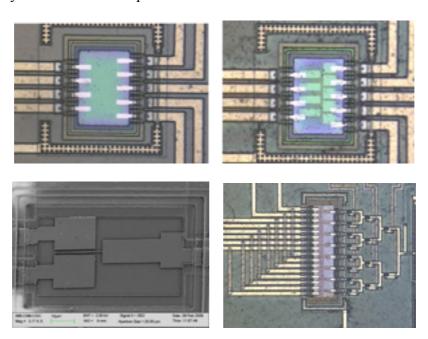

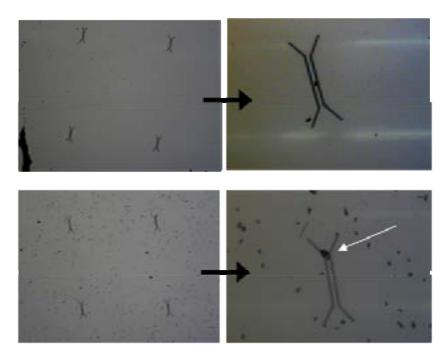

The next step of the process is the RIE for transferring the metal pattern to the Si layer. The dry etching has been optimised to precisely tune the profile and to achieve a reliable transference of Al pattern. The main difficulties are due to the Si thickness and controlling the width of the trenches. RIE is performed on Alcatel A601E and it is based on a nanoscale plasma etching recipe: alternating cycles of  $C_4F_6$  and  $SF_6$  at room temperature (8). The results in Figure 4.6 show the accuracy of the etching process and the appropriate choice of Al for suitable selectivity and the mask resistance of the thin metal layer.

Figure 4.6 Results of optimized RIE process, on quad-beam (top) and paddle (bottom) structures. Both thin  $(0.6 \ \mu m)$  and thick  $(1.5 \ \mu m)$  Si layer are controllably etched for vertical profiles and low undercut.

# Release of the structure by wet etching

The structure fabrication ends with the release of the movable part. For this, a commercial buffered HF solution, SiOetch (9) is used. The time duration of the immersion determines the etched lateral size and depth. Hence, for the releasing of large central plates long etching times are needed. In addition, certain tendency for the structures to collapse or to stick to the substrate is encountered. This is due to the

surface tension forces that are present during the solvent evaporation (Figure 4.7). The release efficiency is improved with the use of critical point drying (CPD).

Figure 4.7 SEM images of some examples of results obtained after the release of the nanomechanical structures. The central plate of the quad beam structure is suspended in the top left image. The tendency to stick (quad beam structure, top right) or to collapse (paddle structure, bottom) reduces the fabrication yield.

### Combination of EBL with photolithography

Once the fabrication processing flow is established and the optimization of structure design is done, the combination of EBL with photolithography is convenient to facilitate external electrical contacts. First, pads, contact lines and alignment marks are defined by photolithography and metal deposition and lift off. Then, the patterning of the nanomechanical structure has to be defined by, for example, EBL to achieve submicronic features. The characteristics of EBL not only contribute in terms of resolution. It also allow to adapt the positioning and dimensions calibration with the existing structure, in addition to the high flexibility in the pattern design.

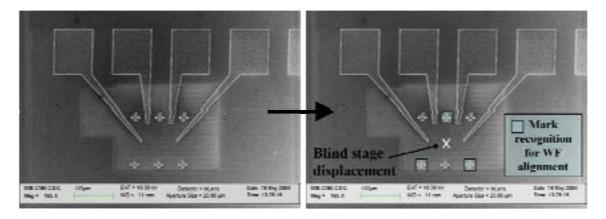

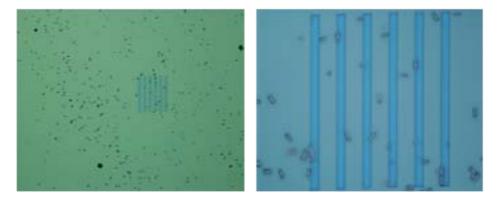

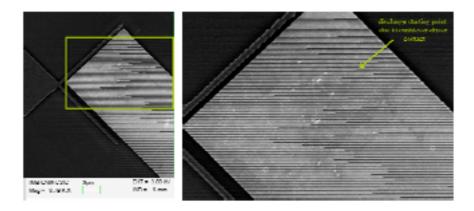

Dedicated marks are used to align the EBL with the existing structure that configures the contact pads. Due to the mask design, WF size for EBL is changed to  $200 \times 200 \ \mu m^2$ . The main difficulty relies on the materials that constitute the marks. RIE is performed in a CMOS compatible equipment, which implies that SEM high contrast materials (e.g. Au) can not be used to define the alignment marks. Due to this, the contrast for the WF alignment is very low and a high number of lines is needed during the scan for the mark recognition (Figure 4.8, left). Alignment procedure starts with the definition of a first reference system (origin and X axis). This allows to blindly move the stage to the relative positions where EBL is to be done. There, mark recognition is performed to finely match position and dimensions of photolithography and EBL (Figure 4.8, right).

Figure 4.8 In the left, SEM image of the prestructure defined by photolithography and metal lift off. Low contrast with the Al marks is observed. In the right, scheme of the procedure for the EBL alignment.

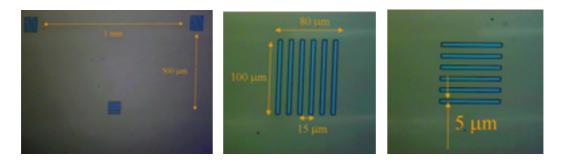

# Combination of EBL with photolithography at wafer scale level

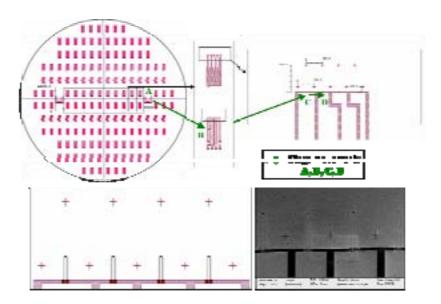

A similar approach is used for fabricating quasi-static nanomechanical structures. In the framework of BioFinger (10), polySi cantilevers are fabricated at wafer scale level with integrated piezoresistance for detection of the vertical deflection. This work has been developed by Guillermo Villanueva and the design and the fabrication details are compiled in his thesis (11). In this case, EBL is used to define cantilevers with submicronic arms width, not reachable by photolithography. The final goal of the project is the direct detection of molecular interactions, which can be obtained because of the increase of sensitivity due to the reduced dimensions.

Figure 4.9 Detailed description of the structure and the alignment procedure from the wafer scale level (top, left) to each individual position for EBL realization (bottom left). From A to D, letters represent the stage displacements (from photolithography alignment marks (A), to the reference point for each array (B), to the first array position (C) and to the rest of array positions (D)). SEM image is an example of an array of four identical cantilevers (250 nm in lenght), correctly defined and placed, after lift off step.

The same alignment strategy than in the previous case is used. Thanks to the silicon nitride marks (200 nm thick) that provide higher contrast than aluminum marks, the alignment procedure is easier. Working with wafers implies longer displacements and, hence, the definition of the stage references should be more accurate. First, the photolithography alignments marks are used to establish the origin and to correct the wafer rotation (A). An intermediate point (B) is used to approach to the EBL positions (C and D), where mark recognition is performed for the fine WF alignment (WF size is  $800 \times 800 \ \mu m^2$ ). In total, there are 20 arrays with four positions in each array to be individually addressed and aligned. The important aspect for this system is the correct definition of four identical cantilevers and their precise placement for each array. As can be seen in the SEM image in Figure 4.10, the alignment procedure and the exposure process, at 10 keV, are valid. A thin Al metal layer (32 nm) is used as the mask for the subsequent process steps.

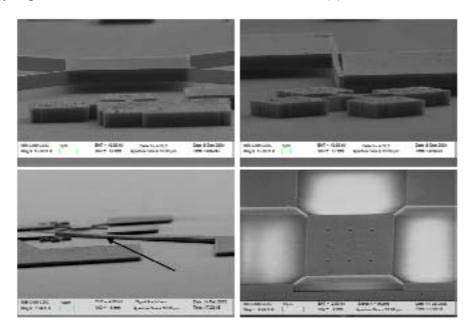

The challenge of this technology relies on the fragility of the structures during the etching and release of the structures. In particular, the transfer to the structural layers is done by RIE on a three layer system (two polysilicon layers, 400 and 200 nm, separated by a thin SiO<sub>2</sub> film, 30 nm). The simulataneous release of all the chips, which contain the cantilever arrays, is realized on the whole wafer from the back side. In Figure 4.10, some final results are shown, where the precision of the feature shape and alignment for the EBL process are observed.

Figure 4.10 SEM images of some results of fabricated nanocantilevers. The fragility of the structures may cause their break (in the top left image, a cantilever is missing after release of the structures and manipulation). Patterning accuracy and precise alignment is also observed in the left side images.

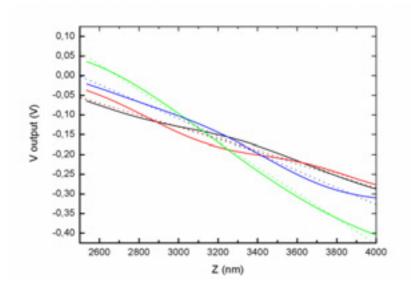

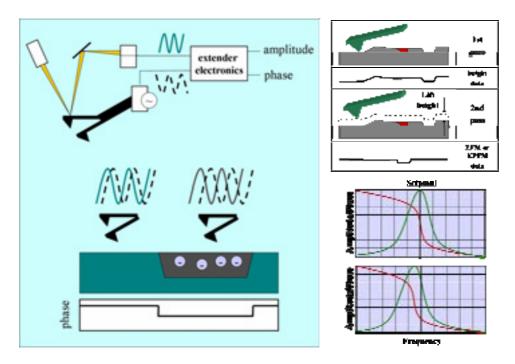

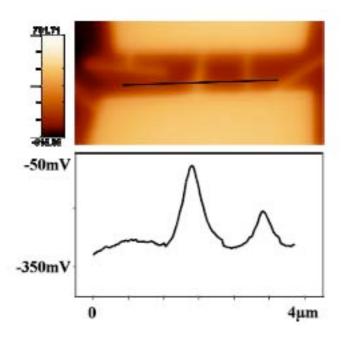

In addition, the performance of the nanomechanical structures has been tested and it proved the piezoresistance of the cantilever. The measurement system is based on the change of the electrical response when applying a bending force with the tip of an AFM. Simultaneous acquisition of the electrical signal in the deflected cantilever and an identical one allows to establish the dependence of voltage with the deflection, as can be seen in Figure 4.11.

Figure 4.11 Electrical response to the AFM-induced cantilever bending. Cantilevers are 150  $\mu$ m long and leg width is 500 nm. The force is applied at 15  $\mu$ m for the anchoring point. Dotted lines correspond to linear fits.

# More results of lithography combined fabrication

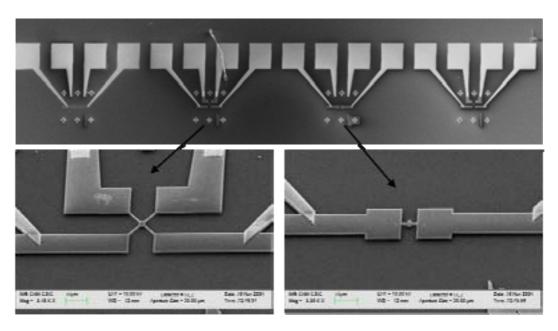

In the case of the resonating structures defined at chip level, good results are also obtained, as can be seen in Figure 4.12. Both in terms of pattern definition and alignment, the three types of structures (single and double cantilevers, paddles and quad beams) are precisely defined.

Figure 4.12 SEM images of some results obtained working at chip level. EBL alignment and pattern resolution can be again observed for the different configurations.

The RIE process is good and the release of the structure appears as the main difficulty. In addition to the CPD, AFM can often be used to gently separate the movable part from the driver if sticked (Figure 4.13). Also the long etching times make optically defined pads lines to collapse (Figure 4.13, arrow), which is solved with shorter etching times thanks to the inclusion of small apertures in the central plate (Figure 4.13, bottom right). The performance characteritzation of these devices has been tested by capacitive detection and the results are found in (8).

Figure 4.13 Detailed results of the fabrication process (SEM images). The good RIE profile is shown for quad beam and double cantilever structure (top images). The lateral bending of the cantilevers to the driver may be solved by AFM based methods. Long etching times may cause structural defects (the arrow in the bottom left image indicates the collapse of a photolithography defined line). The inclusion of small apertures in the central plate may help to solve this aspect (bottom right).

# 4.4 Fabrication of CMOS-integrated nanomechanical devices

Technologically, it is possible to fabricate resonating structures that reach natural resonance frecuencies in the GHz range and high quality factors. However, their characterization and their use as high performance sensors is often masked by the noise of the intrinsic signal and limitations in signal transduction (5).

In order to optimise the device performance, the integration of the nanomechanical resonators into a CMOS circuit is proposed. Thus, devices are both actuated and sensed electrically (capacitive read-out). The direct connection with the circuit not only makes the system more portable, but is expected to reduce the parasitic capacitances. This allows to register the oscillation of, for example, very small cantilevers.

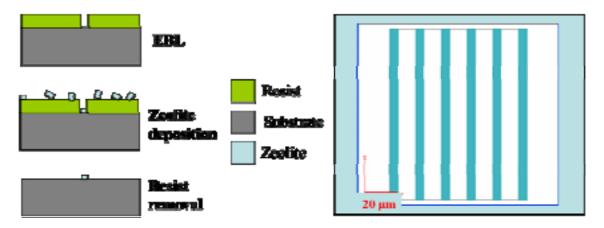

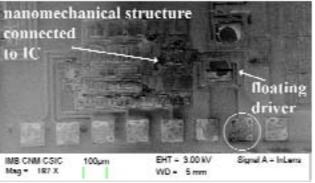

## Monolithic integration of nanomechanical structures into CMOS by EBL

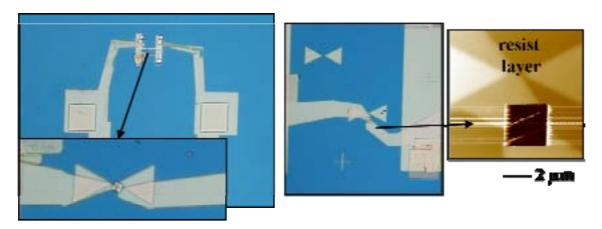

The complete fabrication process consists of the combination of CNM CMOS circuit technology with the definition of the nanomechanical structure as a post process based on EBL. Definition of the cantilever with dimensions well below 1 µm requires

the use of advanced UV lithography (like Deep UV lithography) or other nanolithography techniques. Advanced UV lithography, although it is very robust and presents a high throughput, it has the drawbacks of un-assumable cost for prototyping and difficulties when patterning non planar surfaces. The use of advanced UV lithography has sense if the cantilever is defined during the fabrication of the CMOS circuit, which is feasible (12) but it limits the flexibility in the design (as for example, the selection of suitable materials).

On the other hand, electron beam lithography presents the advantages of assumable cost, high resolution and it is adapted to pattern surface with some topography. In this case, the definition of the cantilever after being completed the fabrication of the CMOS circuits give additional flexibility to the design either for the selection of materials and processing at chip level. Details of the fabrication of integrated cantilevers on CMOS as a post-process module can be found in (13, 14). A dedicated area, the integration area, is used for the monolithical integration of the resonator. The layers that constitute the CMOS circuit are used to define the structure. Hence, one of the polySi layers acts as the structural layer, whereas the field oxide layer is used as a sacrificial layer for the release of the structure.

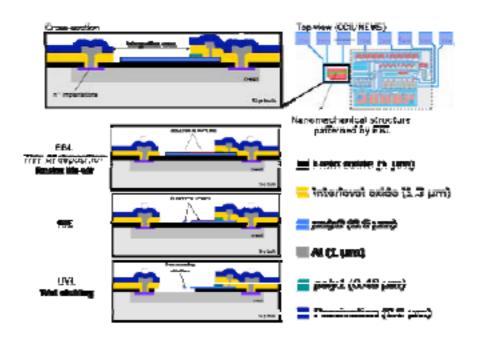

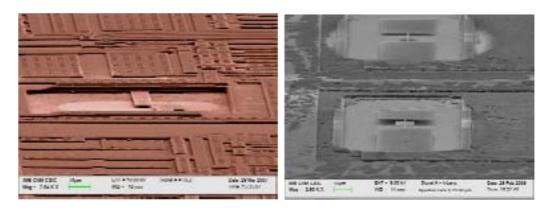

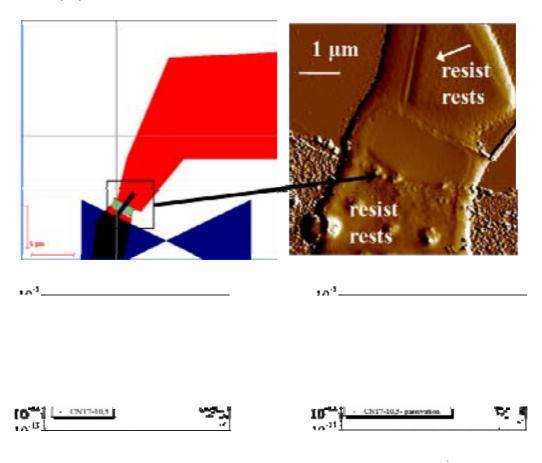

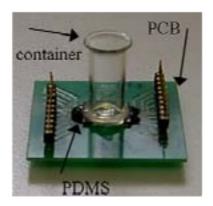

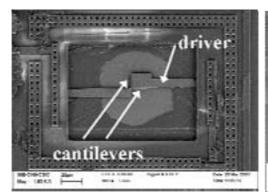

After the CMOS circuit fabrication, openings in the pasivation layer are done in the integration areas and the wafers are diced. A PMMA layer is spin coated on the chip for the EBL step. A thin layer of Al (32 nm) is deposited after development and the resist lift off is done. RIE is used to transfer the Al pattern to the polySi layer and the structures are release by wet etching. In order to protect the circuits during the SiO<sub>2</sub> etching, a negative photoresist mask, patterned by UVL is employed (Figure 4.14).

Figure 4.13 Scheme of the main steps for the fabrication of nanomechanical devices into the CMOS circuit by means of EBL.

# **Issues of EBL on CMOS circuits**

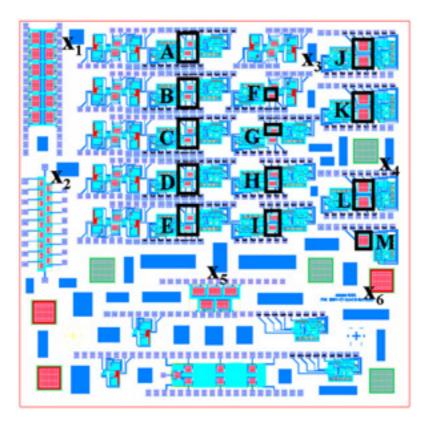

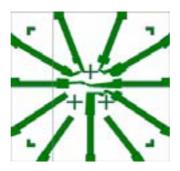

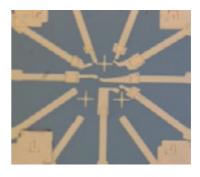

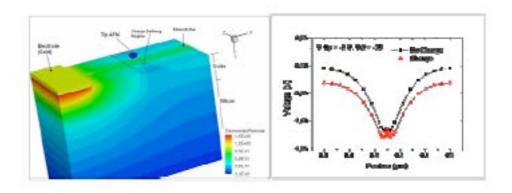

The use of EBL to define nanostructures on CMOS circuits encounters three main issues that should be considered: alignment, beam energy and topography. Originally, the design of the chip was oriented to use nanostencil lithography at wafer scale level to define the resonating structures (15). In consequence, there are not dedicated marks that can be used to blindly address the EBL exposure. The previous experience in alignment is used to establish a specific procedure that enables the correct placement of the structures. Starting from the GDS file of the CMOS design, compatible with the Raith software, the coordinates of each integration area are determined. There are 23 positions prepared to be exposed (Figure 4.15). In addition to this, several reference points separated from the circuits are established (x<sub>#</sub>, in Figure 4.15). These reference marks are chosen among the structures that are defined within the chip. In particular, selected points are not part of the circuits that connect each integration area, but they are close enough to reduce long stage displacements. Additionally, it is convenient that the integration areas to be patterned are placed within the zone delimitated by the three mark sites that have been chosen.

The alignment procedure differs from the previous cases in the importance of the definition of the reference system for the stage movement. First, the corner of the chip is used to define the origin and the rotation of the sample. Then, three reference points are used to precisely establish the UV reference system that determines the stage displacements. As an example,  $x_1$ ,  $x_2$  and  $x_3$  are used for paterning integration areas from A to I. Stage is blindly displaced to the coordinate of each integration area and exposure is directly executed (WF calibration is previously performed in the chess calibration sample, see chapter 2).

Figure 4.15 Design of the whole chip area. The integration areas are marked in black with letters (A-M), 23 EBL positions, and examples of reference points correspond to  $x_{\#}$ .

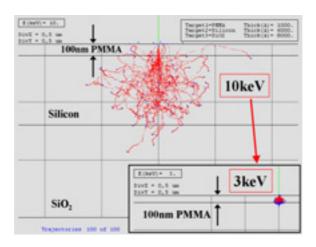

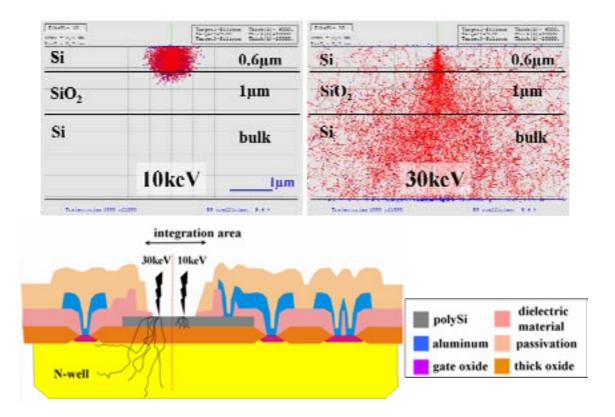

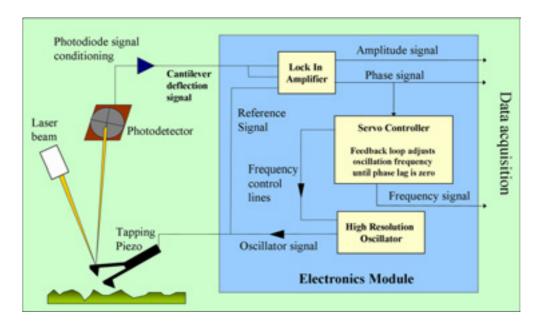

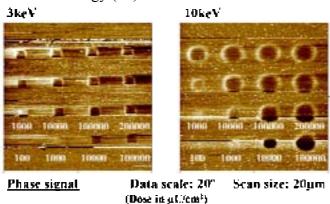

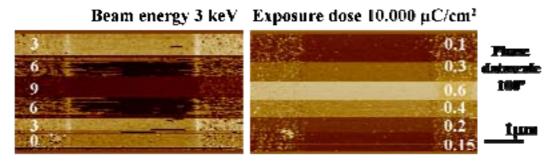

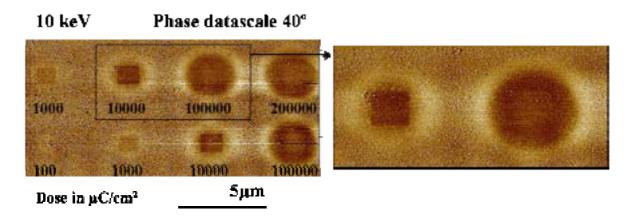

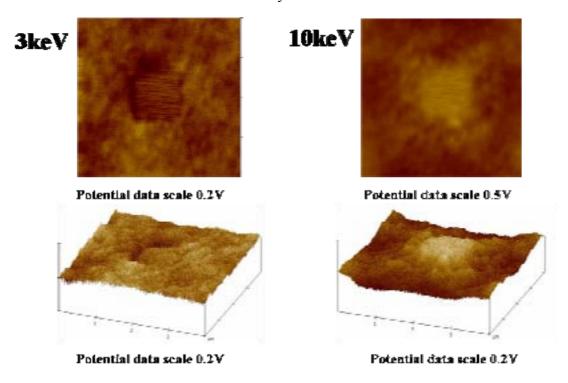

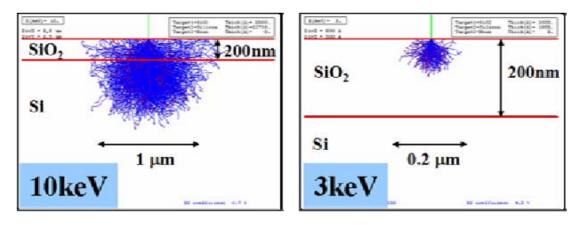

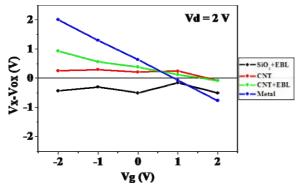

Concerning the beam energy, it is reported that energetic electron beams induce damage in the CMOS circuits (see chapter 6)). Due to this, the possibility to use lower energies to define the structures with no effect on the circuit performance is tested. For 3 keV beam energy on PMMA, the electron range is about 300 nm. As can be seen in Figure 4.16, the simulations of electron trajectories on 100 nm of PMMA on Si show a larger charge confinement in the resist layer for 3 keV beam energy, while for 10 keV a significant fraction of the incoming electrons are stopped along the Si layer.

Figure 4.16 Electron trajectories simulation at 10 and 3 keV beam energies in 100 nm of PMMA upon Si layer. The charge confinement at low energy is clearly seen.

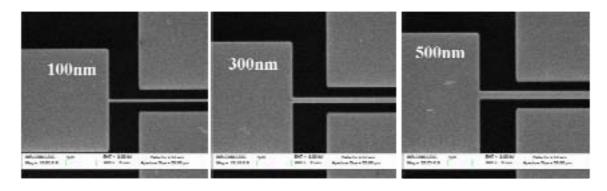

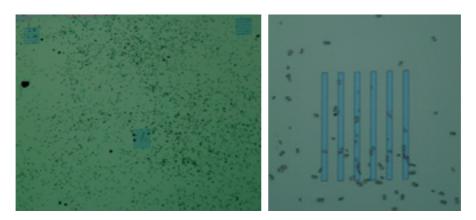

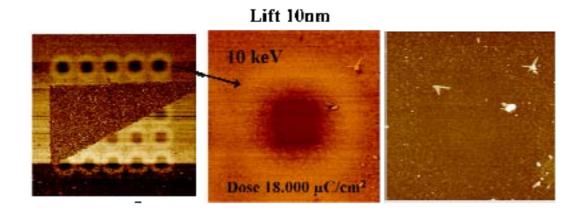

The clearing dose and designs are tested to determine the exposure parameters that may allow a good pattern definition. In Figure 4.17, examples of these trials after final optimisation are included. Control over the cantilever width and good edge definition is feasible for this kind of structures at low beam energy (3 keV).

Figure 4.17 SEM images of the set up of EBL patterning at low beam energies (3 keV), after development. Clearing doses are determined and control over the dimensions (cantilever widths are indicated in white) and good edge definition is obtained.

As mentioned, the passivation layer is removed from the surface integration areas in order to permit the post processing for the fabrication of the nanomechanical structure. Due to this, the topography of the chip represents a limitation over the resist deposition control. The standard spin speed (1500 rpm) for depositing the thin layer is used. However, it is possible that thicker or thinner layers are formed for the same spin conditions, if delivered resist is trapped or does not penetrate the hollow area. An excess of resist, added to the limited electron penetration range, may cause that resist is not

completely developed in the edges of the integration areas. As a result, lift off evidences for the disconnection of the structures to the circuit and lowers the fabrication yield (Figure 4.18, right). In addition, the use of a thin layer of Al does not ensure a complete coverage of the steeped profile, which is needed for masking the subsequent dry etching. For this reason, the use of conformal sputtering for the metal deposition is advantageous.

Figure 4.18 Optical images for some results after the development (right) and after the lift off process (left and insets). Good edge contact can be obtained (left), but no control over the resist deposition and low beam energy may limit the possibility to fully expose the resist, mainly in the contact to the circuit (inset of right side image).

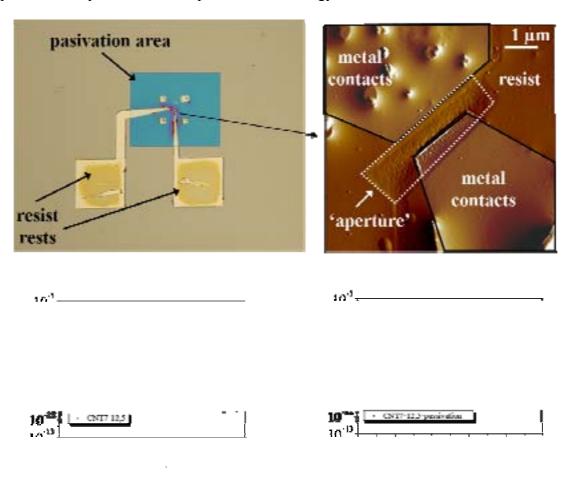

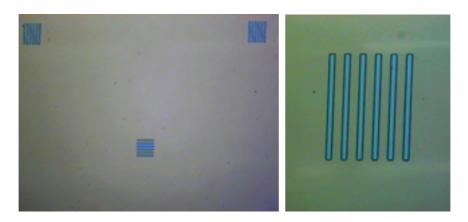

A possible solution is the addition of Al contacts by UV lithography previous to the EBL step (Figure 4.19). This strategy is been tested in the framework of project NANOMASS (16), where also nanomechanical structures are integrated into CMOS circuits (17). Even if it is possible to achieve good contact definition (Figure 4.18, left and Figure 4.20, bottom left), the predefined Al contacts ensure the correct definition of the resonator-circuit connection and increases the tolerance in the alignment, more important for small integration areas or complex configurations (Figure 4.19). Hence, the efficiency of the fabrication process is increased.

Figure 4.19 Optical images of the integration area with Al precontacts defined by photolithography (top). Even if it is possible to successfully define the contacts only by EBL (bottom left SEM image)

the Al contacts facilitate the patterning, specially for small integration areas and complex designs.

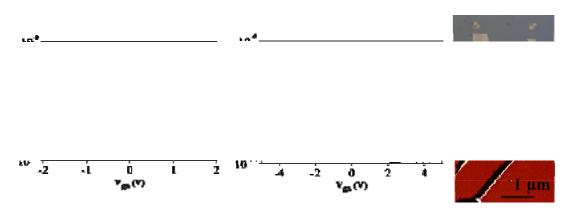

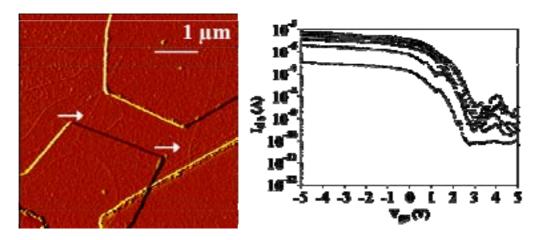

# Results of integrated nanomechanical devices

During the release of the structure in wet etching, the rest of the circuit is masked for protecting. Photolithography leaves open only a portion of the integration area, in order to remove the SiO<sub>2</sub> almost only underneath the nanomechanical structure. The alignment tolerances for EBL are larger than Nanomass chips (Figure 4.19), thanks to bigger integration areas and to the design of the circuits contacts (Figure 4.20). However, this additional photolithography, after the EBL-based nanofabrication, limits the freedom degree for the placement of the nanomechanical structure within the integration area.

Figure 4.20 SEM images of cantilever (left) and paddle structures (right) after the release of the structures. The epoxy resist mask used for the circuit protection during wet etching is also observed.

Some results of device fabrication are shown in Figure 4.20 and 4.21. Device performances are electrically characterized and used for mass sensing applications. The good functional performance of the system is demonstrated in (8) and (18).

In conclusion, a reliable technology process is established for the realisation of NEMS. Concerning to nanofabrication, EBL is capable of fullfilling the requirements of the process: good pattern definition, precise alignment and compatibility with CMOS circuitry. Also, the difficulties in pattern transfer and release of the structure are solved or adjusted.

Figure 4.21 SEM images of the final result of a cantilever based device monolithically integrated into the CMOS circuit.

# 4.5 Focused Ion Beam fabrication combined with Electron Beam Lithography

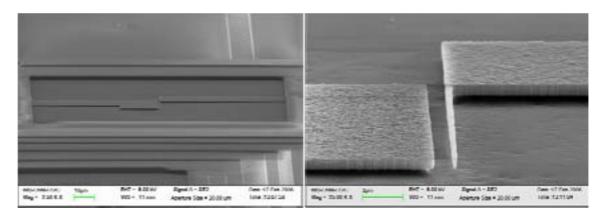

An alternative method for the fabrication of nanomechanical structures on CMOS chips is proposed. Based on the technology presented above, the fabrication of the cantilevers for lateral motion and capacitive read-out is performed with the machining capabilities of FIB. The focused beam of ions can be used to remove or to deposit material (19). In this case, instead of using RIE, the critical definition of the cantilever width and trench is undertaken by direct structuring with the Ga<sup>+</sup> ions.

# Fabrication process by direct FIB machining

This methodology allows to fabricate discrete devices with nanomechanical structure specificacions of higher resolution, this is, narrow cantilevers or small gaps. This is due to the slower etching rate, as compared to RIE, and in situ control of the results. The fabrication processing flow is outlined in Figure 4.22. EBL lithography is used to define the pre-structure that will constitute the cantilever and driver after the FIB milling (obviously, this step could be also accomplished by photolithography, but a dedicated mask would be needed and pattern flexibility for prototyping is then cancelled). Pattern transfer is done again by metal deposition and lift-off and RIE for the etching of the Si layer. Then, FIB is used to directly define the separation of cantilever and driver by cutting the whole Si thickness. Finally, wet etching is used for the nanomechanical structure release.

Figure 4.22 Scheme of the fabrication process of nanomechanical structures combining EBL and FIB machining.

# **Establishment of the FIB procedure**

Experimentally, the feasibility of the FIB based process is tested. The FIB equipment is a Crossbeam 1560 XB from Carl Zeiss. Among its most relevant characteristics, it is equiped with a Ga<sup>+</sup> ions column and a field emission SEM, that enables the on-line monitoring of ion beam process.

The fabrication is performed in the same CMOS chips that have been used in section 4.4. These CMOS circuits are designed to actuate the cantilever by electrostatic excitation and to detect the movement by capacitive detection, as described in (20).

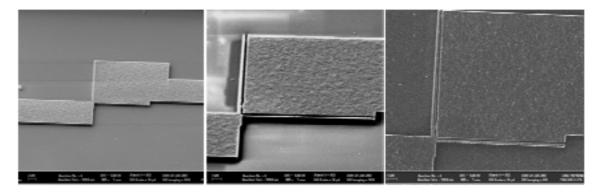

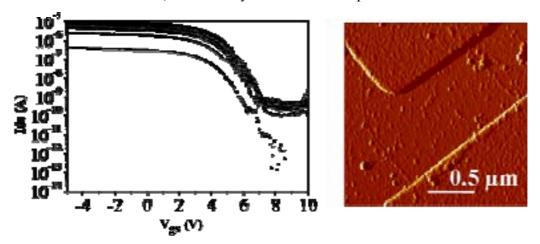

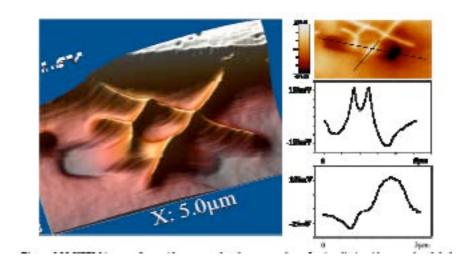

First, the beam alignment point is determined in order to make FIB and electron beam coincidental. SEM assesses the movement of the stage to the integration area that is to be machined, but it is reduced as much as possible. Fast FIB imaging at low current (10 pA) is used to define the pattern design on the pre-structure. The beam current during the milling is shifted to medium-low level (100 pA), which means that slow material removal is performed and better milling control is expected. The cutting conditions have been tested previously in analogous structures. As can be seen in Figure 4.23, the possibility to use this strategy to define the structure is confirmed. The release of the structure is analogous to the previous cases and consists of the elimination of SiO<sub>2</sub> underneath the cantilever by means of wet etching.

Figure 4.23 SEM images of the pre-structure defined by EBL, metal deposition and RIE (left) and after the cantilever definition by FIB milling (center, tilted image, and right, top view)

# Results of FIB based fabrication

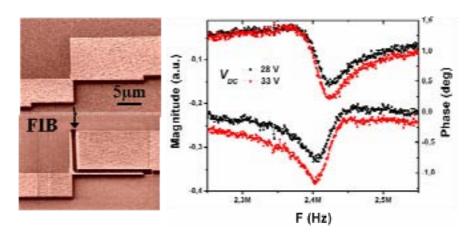

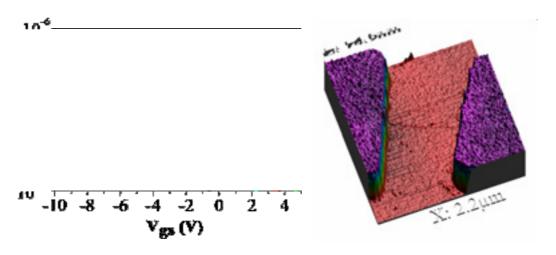

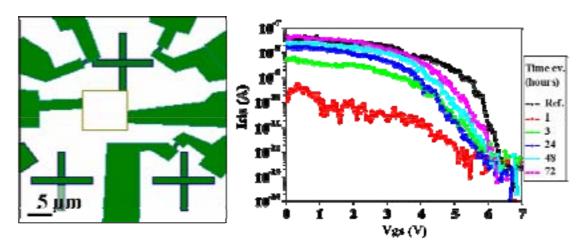

The effect of the energetic ion beam (30 keV) on the system is also studied to evaluate a possible damage in the circuits or the characteristics of the integration area (19). For this, different options are tested in different integration areas: SEM imaging, cutting with or without SEM on-line imaging and different cutting configurations. The circuits are then measured and no major modification is observed in their performance.

One of the limitations of the process is the depth determination of the cutting. Milling rate may be slightly variable and strongly dependent on beam current, material, design dimensions, etc. As a result, the achievement of complete milling of the Si layer is not univoquely defined and both over or underetching may occur. However, even with an excess of milling, the CMOS circuit is not modified. In figure 4.23, it is shown the electrical characterization of the resonance spectra of a cantilever fabricated by FIB.

Electrostatic actuation and capacitive readout by the integrated circuit (IC) are used for detecting the oscillations of polysilicon resonators in the MHz range. The resonator is electrostatically driven by a DC+AC voltage. Its readout electrode, electrically connected to the IC input, collects a capacitive current whose, one part is specifically generated by the variation of electrode-resonator capacitance due to the mechanical motion itself. With the aim of reading out this current, a dedicated interfacing CMOS circuit (21) was designed based on a second generation current conveyor (CCII). Basically, the CMOS circuit ensures a constant input voltage biasing, while it amplifies the input current and converts it to an output voltage signal according to the load resistor. We have not found any difference in their performance between before and after FIB processing, as it can be observed in figure 4.23. More details about the circuit can be consulted in (7). Another aspect that difficults the control over the FIB machining relies on the beam drift. In consequence, the patterned result may not correspond with the designed structure.

Figure 4.24 In the left, SEM images of the prestructure (top) and after FIB machining (bottom). In the right, the characterization of the released structure performance shows the compatibility and consistency of the processing flow.

In summary, the fabrication of nanomechanical devices by EBL has been described and the complete technology is established and optimized. First, discrete devices are fabricated, which allowed to determine the specific process conditions. Combination of EBL with photolithography facilitates the electrical characterization of nanomechanical device in operation. The main achievement consists of the monolithic integration of nanoresonators into CMOS circuits, which enhances the signal of the nanomechanical element response. Alternative method of fabrication based on FIB is also demonstrated.

# References

(1) K. L. Ekinci

Electromechanical transducers at the nanoscale: Actuation and sensing of motion in nanoelectromechanical systems (NEMS)

Small 1 (8-9), 786-797 (2005)

(2) A. Husain, J. Hone, H. W. C. Postma, X. M. H. Huang, T. Drake, M. Barbic, A. Scherer, and M. L. Roukes

Nanowire-based very-high-frequency electromechanical resonator Applied Physics Letters **83** (6), 1240-1242 (2003)

(3) K. L. Ekinci and M. L. Roukes

Nanoelectromechanical systems

Review of Scientific Instruments **76** (6) (2005)

(4) A.N. Cleland

**Foundations of Nanomechanics**

Springer-Verlag **ISBN 3-540-43661-8** (2003)

(5) A. N. Cleland and M. L. Roukes

Noise processes in nanomechanical resonators

Journal of Applied Physics 92 (5), 2758-2769 (2002)

(6) H. G. Craighead

Nanoelectromechanical systems

Science **290** (5496), 1532-1535 (2000)

(7) J. Arcamone

Integration of nanomechanical sensors on CMOS by nanopatterning methods

PhD Dissertation, July 2007, Universitat Autònoma de Barcelona

(8) J. Arcamone, G. Rius, G. Abadal, J. Teva, N. Barniol, and F. Perez-Murano Micro/nanomechanical resonators for distributed mass sensing with capacitive detection

Microelectronic Engineering 83 (4-9), 1216-1220 (2006)

(9) SioetchH 06/01 VLSISelectipur worldaccount.basf.com/wa/EU~en\_GB/Catalog/Chemicals/pi/BASF/PRD/30 268479

(10) BioFinger

**Diagnosis tool based on measurement of molecular interactions** IST-2001-34544

(11) G. Villanueva

Development of cantilevers for biomolecular measurements

PhD Dissertation, December 2006, Universitat Autònoma de Barcelona

J. Verd, A. Uranga, G. Abadal, J. Teva, F. Torres, F. Perez-Murano, J. Fraxedas, J. Esteve, and N. Barniol

Monolithic mass sensor fabricated using a conventional technology with attogram resolution in air conditions

Applied Physics Letters 91 (1) (2007)

(13) J. Verd, G. Abadal, J. Teva, M. V. Gaudo, A. Uranga, X. Borrise, F. Campabadal, J. Esteve, E. F. Costa, F. Perez-Murano, Z. J. Davis, E. Forsen, A. Boisen, and N. Barniol

Design, fabrication, and characterization of a submicroelectromechanical resonator with monolithically integrated CMOS readout circuit

Journal of Microelectromechanical Systems 14 (3), 508-519 (2005)

M. Villarroya, E. Figueras, J. Montserrat, J. Verd, J. Teva, G. Abadal, F. P. Murano, J. Esteve, and N. Barniol

A platform for monolithic CMOS-MEMS integration on SOI wafers

Journal of Micromechanics and Microengineering 16 (10), 2203-2210 (2006)

(15) NaPa

Emerging nanopatterning methods

NPM4-CT-2003-500120

(16) NANOMASS

Smart NEMS system for high sensitivity mass detection

IST-2001-33068

(17) S. Ghatnekar-Nilsson, E. Forsen, G. Abadal, J. Verd, F. Campabadal, F. Perez-Murano, J. Esteve, N. Barniol, A. Boisen, and L. Montelius

Resonators with integrated CMOS circuitry for mass sensing applications, fabricated by electron beam lithography

Nanotechnology 16 (1), 98-102 (2005)

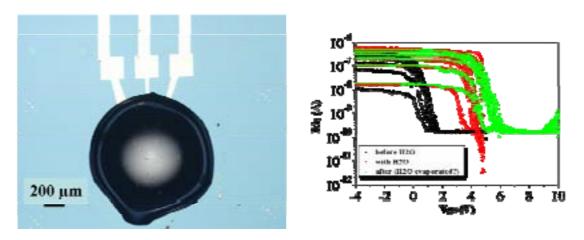

(18) J. Arcamone, E. Dujardin, G. Rius, F. Perez-Murano, and T Ondarçuhu

Evaporation of femtoliter sessile droplets monitored with nanomechanical

mass sensors

Journal of Physical Chemistry B on line (2007)

(19) C. Lehrer, L. Frey, S. Petersen, and H. Ryssel

Limitations of focused ion beam nanomachining

Journal of Vacuum Science & Technology B 19 (6), 2533-2538 (2001)

(20) J. Arcamone, G. Rius, J. Llobet, X. Borrisé, and F. Pérez-Murano

Mass measurements based on nanomechanical devices: differential

measurements

submitted to IOP Journal of Physics: Conference Series (2007)

(21) J. Arcamone, B. Misischi, F. Serra-Graells, M. A. F. van den Boogaart, J. Brugger, F. Torres, G. Abadal, N. Barniol, and F. Perez-Murano

# A compact and low-power CMOS circuit for fully integrated NEMS resonators

IEEE Transactions on Circuits and Systems Ii-Express Briefs **54** (5), 377-381 (2007)

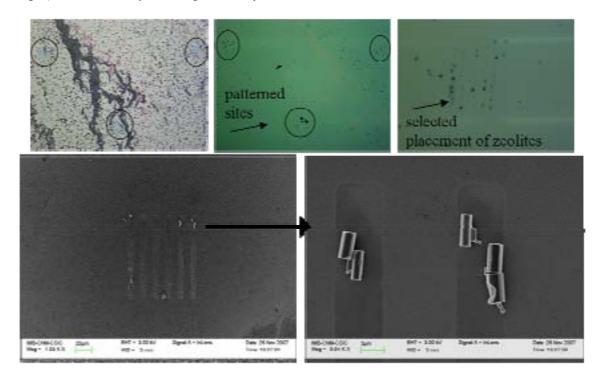

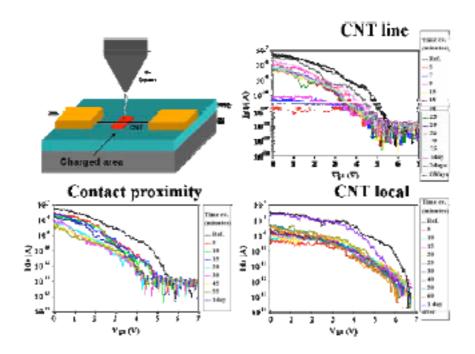

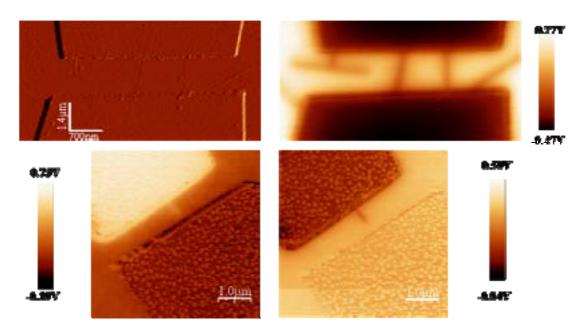

Carbon nanotubes are used as active elements of electronic devices. After a brief introduction to CNTs, fabrication of devices based on EBL is discussed. FETs are accomplished by contacting single tubes that have been either deposited or grown on oxidised substrates. For on chip-synthesized CNTs, four different approaches are tested in order to optimize device fabrication by the deposition control of the growth catalyst. Postprocessing approach to adapt CNTFETs for sensing applications is developed. A methodology to selectively control CNT placement and orientation is proposed using zeolites.

# 5 Fabrication of Carbon Nanotube based devices by EBL

# 5.1 Introduction to carbon nanotubes

The continuos development of microelectronics has been based on the miniaturization of metal oxide semiconductor field-effect transistor (MOSFET). Along last decades, the advances of integrated silicon technologies allowed device scalability, which results in improved speed and power consumption. Hence, better device performance and increased density is achieved. Obviously, industrial interest continues to pursue this progress, but this strategy will at some point reach both physical and technological limitations. Indeed, a new approach is needed and it can be undertaken by two ways: creation of a completely new concept for the devices or introduction of new materials that overcome current limitations in the existing configurations. For the moment, this second solution seems easier to implement and benefits from the discovering of unique and promising materials (1, 2).

Carbon nanotubes (CNT) are considered one of the most suitable building blocks that could lead the evolution for the next generation of devices. Accidentaly, in 1991 S. Ijima observed their synthesis by discharges in carbon electrodes (3). Their appearance was preceded of fullerene discovering, a stable large closed-cage carbon cluster that can be considered nearly 0D (4). CNTs are seen as quasi 1D structures due to their large aspect ratio. Carbon atoms are arranged in long lengths and small diameters that result in interesting physical properties. CNT structure can be described as rolled graphene sheets with half a fullerene in each final edge. This forms a cylinder of few nanometers in diameter that can reach several microns in length. Aside from the interest of studing this structure from a fundamental point of view, their additional outstanding properties make them ideal for many applications (5). As a matter of fact, CNTs exhibit unique electronic, structural and molecular behaviour in terms of electrical conductivity, mechanical strength, chemical reactivity and optical activity (6).

Their use covers a diverse range of interesting potential applications: energy storage, molecular electronics, probes and sensors, composite materials or templates. For example, in molecular electronics they can be used for fabrication of field emitting devices or transistors. As a prerequisite, their properties have to be controllable to allow engineered molecular devices. In composite materials, the high strength, flexibility and low weight make them ideal to reinforce material matrices.

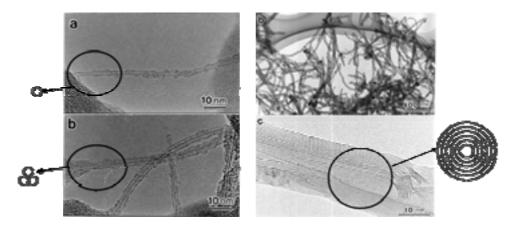

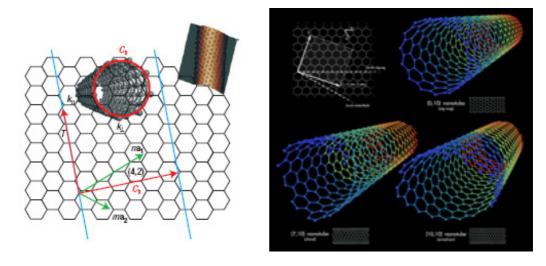

Morphologically, they can be classified in different ways. A single graphene sheet forms what is called a single-wall carbon nanotube (SWCNT), whereas multi-wall carbon nanotube (MWCNT) is a collection of concentric SWCNT of increasing diameter. Specially SWCNTs tend to form bundles, due to their intrinsic electronic configuration (Figure 5.1) that induce intertube attractive Van der Waals forces (7).

Figure 5.1 TEM images for different CNTs structures. (Left) a. Single wall CNT; b. Bundle of SWCNTs. (Right) b. Multi wall CNTs; c. Concentric structure of MWCNTs (8).

Considering in detail the structure and atomic configuration, their special properties can be modelled. Seen as a graphene sheet wrapped in a certain direction, SWCNT can be described by discrete numbers that determine a chiral vector. The excellent mechanic properties of stiffness and strength are quantified by elastic modulus and tensile strength and they can be deduced from the formation of covalent sp<sup>2</sup> bonds between individual carbon atoms (9).

Their electronic properties can be modeled directly from their morphology (10, 11, 12). Chiral vector is perpendicular to the axis of the CNT and relates equivalent atom sites in the tube by means of the unit vectors in real space of the graphene sheet, a hegaxonal lattice (Figure 5.2, left). The electronic properties strongly depend on the exact arrangement of carbon atoms. Extrapolation from the band structure of graphene in 2D to CNTs in 1D can distinguish metallic tubes from semiconducting ones in terms of chiral indices, m and n. When m = n, tubes are metallic and called armchair tubes . If n-m = 3i (where i is an integer  $\neq$  0), tubes are small gap semiconductors (semi-metallic), the zig-zag tubes. The rest of combinations are semiconducting tubes, called chiral and distinguished by the chiral angle  $(0 < \phi < 30^{\circ})$  (Figure 5.2, right). Tight binding description of the electronic structure predicts  $E_{gap}$  in terms of carbon-carbon distance and CNT diameter.

Experimentally, the exact determination of tube diameter together with their conduction could allow to deduce atomic arrangement and compare it with direct imaging results. But it is difficult to perform these three characterizations at the same time. TEM sample preparation is not compatible with device fabrication for electrical characterization of an individual CNT, so only indirect techniques such as Raman can

contribute to compare results with theoretical model. Other advanced characterization techniques are been established, such as AFM-based methods (13).

This description does not include defects in the structure that cause deviations from the ideal model. Among others, bends, torsions, formation of junctions or impurities affect their characteristics. Great efforts in simulations are done to predict their contributions (14).

Figure 5.2 (Left) CNT shown as rolled graphene sheet of determined chiral vector. (Right) Types of SWCNTs in function of the atomic configuration: zig zag (top), chiral (bottom left) and armchair (bottom right) CNTs. Chirality determines electronic transport (2).

As mentioned, one of the crucial aspects for the development of applications is based on the possibility to control CNT properties. Growth mechanism is still controversial and it seems difficult to believe that chirality could ever be tuned. Control over synthesis parameters, like pressure, temperature, gases ratios or catalyst particle diameters, seems reasonable. In the growth, carbon atoms are extracted from gases, graphite, etc, when certain external energy is supplied and they tend to form tubular structures.

The synthesis is performed mainly by means of four techniques: arch discharge (15), laser ablation (16), CVD (4) and flame synthesis. Arch discharge consists of two carbon rods placed in an enclosure filled with inert gas. The application of a direct current creates a high temperature discharge between the two electrodes and CNTs are formed. It is easy to implement and results in a large quantity of material, but often contain more impurities than with other techniques. Laser ablation is similar to arch discharge. It is realized in an oven at high temperature by ablation of the graphite target with laser beam. In this case, a smaller quantity of tubes is created, but they are cleaner. The third possibility, CVD uses gaseous carbon sources (methane, acetilene, etc) that are decomposed by the external energy and catalyst particles act as 'nucleation' centers. It will be further presented in the next section. Some authors consider that the tubes have poorer quality and larger diameter that other techniques, but the advantage is that it seems easier to scale up and the control over several parameters could allow its use for device fabrication. Flame synthesis is more unusual and relies on the application of a flame to metal catalyst islands that form an aerosol. Its interaction with the carbon atoms from hydrocarbon fuels creates CNTs. No general characteristics for these tubes are reported.

# **5.2 Fabrication of CNTFETs**

From the technological point of view, the fabrication of devices based on CNTs is challenging. Their integration to develop specific functions encounters two main limitations: the control of intrinsic properties of the tubes and the compatibilization of the different processes during device fabrication. Ideally, the control on diameter, length or quantity, the choice of semiconducting vs metallic conduction or the ability to locate them in selected places and either vertical or horizontally is desired.

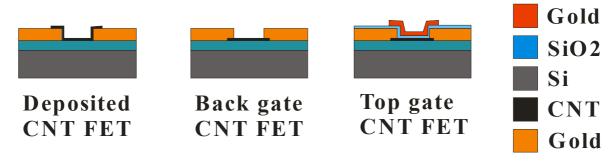

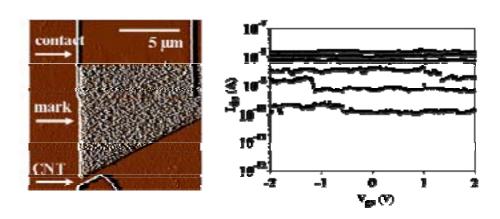

The first electrical measurements performed on individual CNTs are reported in 1998 for CNTFETs (17,18). The devices were fabricated with a simple approach based on photolithography for the definition of noble metal contacts on an oxidized substrate with highly doped silicon underneath. CNTs were placed by chance on the contacts from a solution (Figure 5.3, left).

The performance of those early devices was far from making CNTFETs competitive to MOSFETs. They behaved as p-type transistors with modulation of drain current from gate voltage. But their characteristics showed low current and transconductance, high parasitic resistance and subthreshold slope and no current saturation.

Patterning contacts on top of the CNTs improves significantly device performance, because metal-CNT contact is not due to weak van der Waals forces anymore (Figure 5.3, center). Other efforts to optimize the electrical properties are done by thermal annealing or choice of metal to adjust metal Fermi level with CNT band edge. It is also desirable to control their conduction. On air, they behave as p-type transitors (hole conduction), but doping may convert them to n-type (electron conduction) (19). Even sometimes they show ambipolar transport (20). This reinforces the necessity of a homogeneus controllable synthesis, in terms of diameter, length, chirality, etc.

Figure 5.3 Different configurations of CNTFETs. (Left) FET based on deposited tubes on the contacts. (Center) FET based on CNTs underneath the metal contacts. (Right) FET based on CNTs underneath the metal contacts and top gate modulation.

Other approaches implement devices by means of other configurations. In particular, the placement of the gate may allow many different options. The results above correspond to the back-gate configuration, but also top-gate transistors, where modulation is driven from a contact upon a gate oxide on the CNT (Figure 5.3, right), or placement of a proximity third electrode, that lead to single electron transistor devices, are possible.

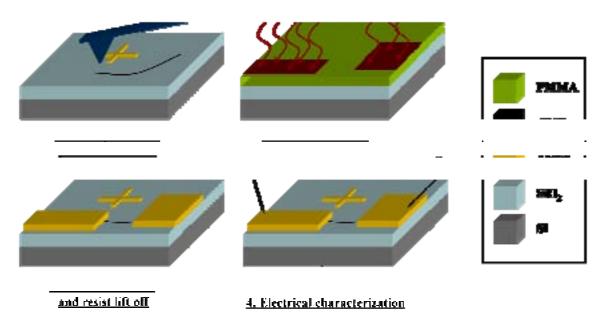

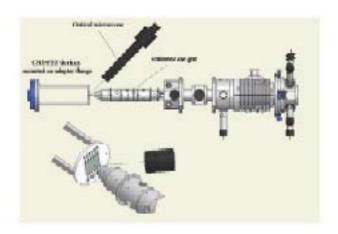

During the development of this PhD thesis, the technology to fabricate CNTFET has been established at IMB-CNM-CSIC. A general process flow is established for the fabrication of discrete devices based on EBL. A first approach is based on deposition of CNTs and contact definition. In the second part, the introduction of CVD for CNT synthesis allows a better integration and process is optimized by selective deposition of catalytic particles.

Results in this chapter are restricted to back-gate configuration. A good performance for the devices will be presented. Technological issues and different processing flows for device fabrication are discussed along the subsections 5.2.1 and 5.2.2, whereas electrical characterization of contacted CNTs will be studied in 5.3. The common part of the device fabrication process is schematized in Figure 5.4

Figure 5.4 Common processing steps for the fabrication of CNT based devices.

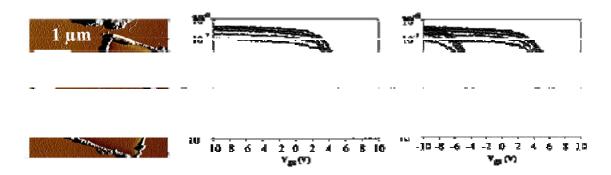

# 5.2.1 Contacting deposited CNTs

The first FET based on a CNT fabricated at the IMB-CNM was presented in the Nanospain workshop in 2006 and, probably, it was the first time that such devices were fabricated by a spanish laboratory (July 2006).

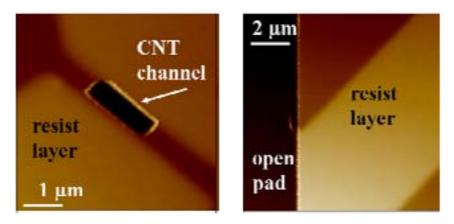

As mentioned, back gate configuration is chosen to implement CNT based devices. A commercial silicon wafer is processed in the Clean Room of the CNM. Implantation is performed to highly dope silicon substrate and thermal oxidation is used to grow a high quality  $SiO_2$  layer of controlled thickness, 200 nm. After cutting the wafer in dices of 1.5 x 1.5 cm<sup>2</sup>, the fabrication process for the devices consists of two levels of lithography and pattern transfer by metal deposition and resist lift off, to define drain and source contacts.

Figure 5.5 Fabrication process for contacting individual SWCNTs. It is based on two levels of EBL and AFM inspection for the determination of CNT coordinates.

First, reference marks are fabricated. For this, a chip is covered with 120 nm of PMMA by spining and patterned by EBL. Marks design consists of two sets of marks, one for the determination of CNT coordinates and the other for the alignment of the second level of lithography. This mark design is defined along the chip in many determined positions (typically 70-100) automatically. A thin layer ~30 nm of gold (with an thinner adhesion layer of chromium underneath) is deposited by thermal evaporation and lift off of the resist is realized in warm acetone, sonication, rinsing in IPA and drying in N<sub>2</sub> (Figure 5.5). The choice of thickness and material has to ensure that mark recognition in the second level of lithography will be possible.

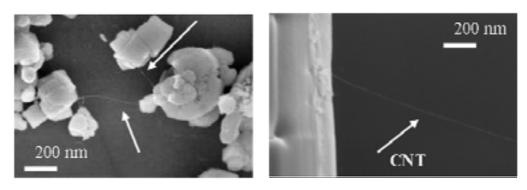

The single-walled CNTs have been synthesized by laser ablation and they are presented as powder material. For the deposition, a little amount of CNT material in powder is dissolved in 1,2 dichloroethane and sonicated for 15 minutes in order to disgregate CNTs. Some drops are deposited covering the whole area and the chip is spun at 1000 rpm during one minute to evacuate the excess of solvent. It is important to perform this manipulation with clean laboratory equipment and inside controlled facilities to avoid contamination and impurities in the surface and CNT, respectively. (Figure 5.6, left)

Figure 5.6 (Left) Deposition of CNTs on prepatterned substrate and AFM based CNT coordinates determination relative to the marks. Image scan size is 30 µm. (Center) Design of the second level of EBL for contacting CNTs. (Right) Result of metal deposition and resist lift off.

Four CNTs are contacted in this sample position.

The determination of precise coordinates of the CNTs with respect to the reference marks allows to design the pattern for contacting selected tubes. The inspection is performed with an AFM equiped with a close loop scanner, in order to

improve calibration accuracy. Again, it is important to have a clean surface and smooth edge metal marks in order to facilitate inspection: SWCNTs are 1 nm in diameter, whereas metal layer is 30 times thicker. Often, amplitude signal recording in the AFM imaging provides a more suitable contrast than topography, since it reflects rather the change in surface topography than the topography itself. Isolated, long, straight and small diameter tubes are chosen to be contacted.

The definition of drain-source contacts is again based on EBL patterning of PMMA layer. The pattern design is realized manually placing the coordinates of the two end points of each tube in the original design of the reference marks. Then, it consists of adding the contacts with the shape adapted to the tube form and contact separation length that is desired (Figure 5.6, center). The alignment procedure is similar to the one described in previous sections (Chapters 2, 4). First, a reference system is defined with a chip corner (origin) and chip side (axis) and the stage is driven blindly to the positions where EBL will be performed. Mark recognition consists of opening small windows to adjust the write field references for the beam scan control of deflection in the hardware of lithography. In this case, a double layer of 495k MW + 950k MW PMMA, in total ~250 nm, is used to facilitate the lift off process without sonication to avoid creation of structural defects in the CNT. The metal deposition again consists of evaporation of a layer of 3-5 nm Cr and 25 nm Au (Figure 5.6, right)

After contact fabrication, the edges of the selected tubes are trapped by the metal, obviously if alignment is correct. But also it is important to remark that some rests for the CNT deposition are eliminated and, more importantly, non contacted tubes still remain on the surface. This enables to iterate contacting steps in the same chip if needed.

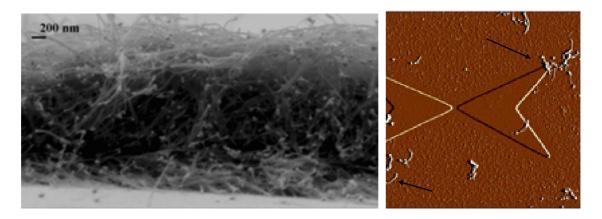

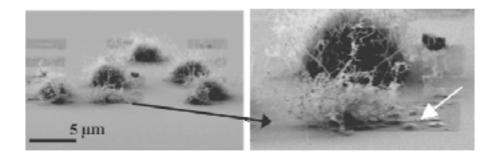

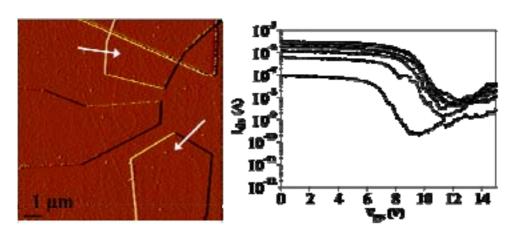

In addition to contacting deposited SWCNTs, a similar approach has been applied to perform electrical characterization of MWCNT grown at CNM by CVD. The recipe to synthesise MWCNTs provides a great number of vertically oriented tubes. From one side, it is interesting to characterise the nature of these MWCNTs individually since they will be used collectively for sensing, but also the fabrication of discrete devices may take advantage of this massive CNT production that has been established at CNM.

Figure 5.7 (Left) Massive CVD-grown MWCNTs used for individual contacting. Typical tube diameter is 20 nm. (Right) CNTs are dissolved on IPA and deposited in a prepatterned subtrate.

AFM Amplitude signal scale is 0.3 V and scan size is 20 μm.

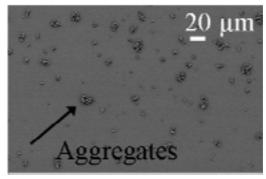

The fabrication process is analogous to the precedent case and only the set up of the solution of CNTs to be deposited differs. A great number of  $\sim 1.5 \, \mu m$  length grass-like CNTs are grown in a SiO<sub>2</sub> layer using Pt as catalyst (Figure 5.7, left). The whole chip is immersed in IPA and sonicated for 1 minute. The dark colour of the chip where CNTs were synthesized changed to a clear one indicating that CNTs were certainly detached from the substrate. Some drops are deposited in silicon oxide substrate where previously some reference and alignment marks have been defined by EBL. AFM inspection is performed to determine tube coordinates, but non uniformity and aggregation of CNTs appears. (Figure 5.7, right). For further experiments, more sonication of the solution helps to disgregate them and to increase the potential number of tubes to be contacted.

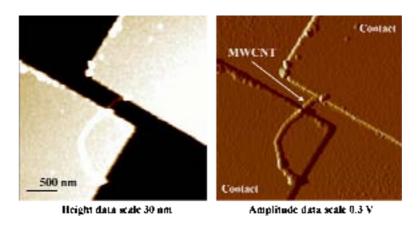

The fabrication of contacts for electrical characterization is the same that has been described above. It would be convenient to have longer CNTs in order to have more tolerance with coordinates determination of the MWCNTs and, hence, to facilitate metal contac fabrication (Figure 5.8). The electrical characteristics are included in the next section 5.3.

Figure 5.8 Example of a deposited MWCNT that has been contacted.

# 5.2.2 Contacting CVD grown CNTs

The challenge to integrate CNTs in the conventional fabrication processes for the production of great number of devices is not completely solved yet. One of the main limitations comes from the synthesis of CNTs, which is not directly compatible with most of current technologies. In particular, the temperature of synthesis for the CNTs is typically above 700°C. This fact can cause the alteration of previous processes characteristics or damage of structures defined before the synthesis. From the existing synthesis techniques, only CVD seems suitable to be combined with silicon based microfabrication.

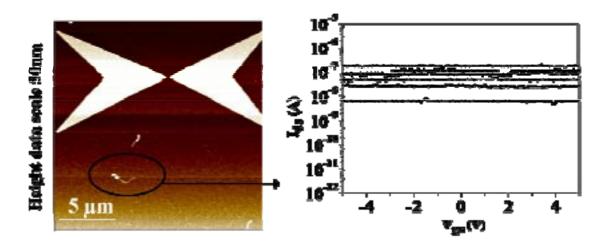

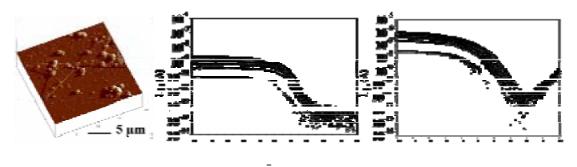

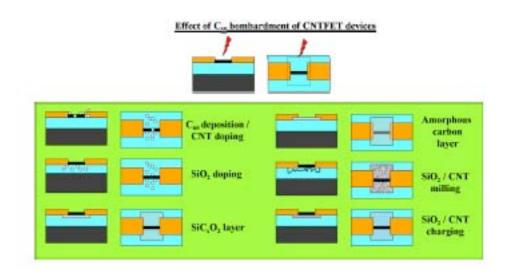

The fabrication of discrete devices follows the back-gate conguration and only four minor alternatives of process flow are presented (Figure 5.9). Even if the results will not be analized until the next section in terms of device performance, some aspects can be remarked and their extrapolation to the integration of CNTs with conventional technologies may be useful.

# Extended deposition of catalyst Marks fabrication CNT synthesis CNT synthesis Marks fabrication CNT synthesis Marks fabrication CNT synthesis Electrical contacts fabrication

Alternatives of fabrication sequence

Figure 5.9 Four strategies are used to optimize the fabrication of CNTFETs. Extended deposition of catalyst before or after the alignment marks definition. Local deposition of catalyst before the marks fabrication or under the very same marks.

The first fabrication process comes directly from the technology used in the precedent section 5.2.1. Alignment and reference marks are defined along SiO<sub>2</sub> layer by EBL in many determined positions and transferred by metal deposition and resist lift off.

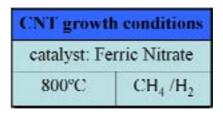

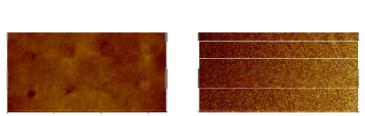

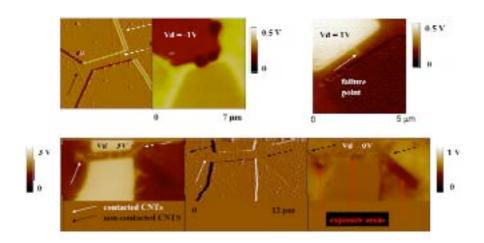

Next, the deposition of the catalyst material is realized. Metal catalyst is spread all over the chip from a solution. The solution concentration can be controlled, which was not the case for the solution used in previous section for depositing CNTs. Clean catalyst compound (for example, ferric nitrate nonahidrated) is weighted, solved in a determined quantity of proper solvent and sonicated for a certain time. Sample is covered with some drops of solution. The precipitation of the catalyst on the sample substrate can be done by two methods, in function of catalyst used. Whether the solution is drop delivered, left to rest on the chip and then rinsed or dissolution is poured while sample is spun at low spin speed. The results of the deposition are not fully controllable neither uniform. Process varies with many parameters: wettability, topography, roughness, catalyst, concentration, spin speed, etc in almost a non controllable way. Then, CVD is used for the tubes synthesis. Again, AFM inspection allows to determine the results of the growth and particularly, the exact coordinates of CNTs. Indeed, this imaging step is very time consuming due to the long time that it takes the acquisition of each high resolution image and sometimes also due to the low number of existing CNTs. As mentioned it is desirable that only one or two tubes lie near each inspected reference mark (Figure 5.10).

Amplitude data scale it.3 Y

Figure 5.10 Example of the result of CVD after the alignment mark fabrication. (Left) Thermal process degrades the mark. SWCNT is 7µm long. (Right) Growth conditions are almost common for all the cases.

Once this is done, the fabrication process is equivalent to the previous case. In particular, EBL is performed at 10 keV beam energy, tipically with a dose of ~120  $\mu$ C/cm<sup>2</sup> and developed in MIBK and IPA. Evaporation of Cr + Au thin layer is used for the metal contact definition. The results for the different catalyst materials, oxide thicknesses or synthesis processes are presented within device performance discussion (5.3).

However, the integrity of the metal marks can be ruined in the CVD process due to the high temperatures and reaction with the gaseous species. In consequence, AFM imaging for tubes coordinates determination can be more difficult, due to metal disgregation (Figure 5.10, left). and also EBL alignment may be afected

The second possibility interchanges the order of synthesis and mark fabrication steps and relies on the experience of contacting deposited CNTs. Once on the surface, CNTs are not easily detached from it. Thanks to this, it is possible to first realize CNT synthesis and then fabricate reference marks for the determination of tube coordinates. As can be seen in Figure 5.11, left, certainly tubes are not removed in the resist development, neither in the lift off of the resist after metal deposition for the pattern transfer of the marks (Figure 5.11, center). On the other hand, incrementing the number of catalyst particles deposition improves tube growth yield, but may interfere in device performance (Figure 5.11, right).

Figure 5.11 AFM images of the fabrication of CNTFETs using the second approach for extended catalyst deposition. (Left) CNT coordinates determination. (Center) Top view of one SWCNT contacted. (Right) 3D image of another contacted CNT. Spikes are due to the catalyst.

152

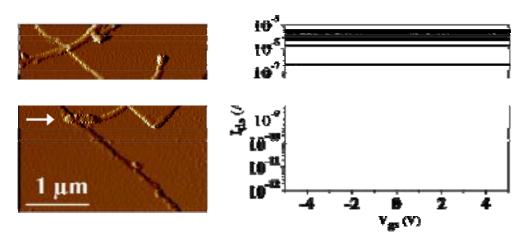

In the introduction, the convenience to control the placement of the CNTs has been highlighted specially for achieving batch production of CNT-based devices. It is necessary to realize devices, wherever it is desired, and also to increase the fabrication throughput. A third strategy is proposed for improving this issue.

In this case, the selective deposition of catalyst material aims to restrict the formation of nanotubes to the places surrounding the specific places where particles are deposited. Once deposited or in contact with the substrate surface, metal catalyst particles are strongly bonded to it and it is difficult to remove them.

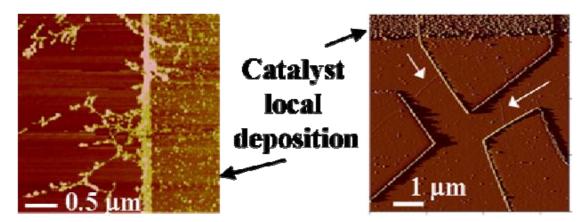

Taking advantage of this behaviour, selective deposition is realized through a resist mask patterned by EBL. For this, prior to the synthesis, the sample is spun with a single 950k MW PMMA layer at 1500 rpm and patterned with a variety of design configurations (areas down to 1  $\mu m^2$ ) on specific positions of the chip. PMMA is compatible with catalyst solution and can stand wetting process. Resist stripping is performed in acetone. Figure 5.12, demonstrates that selective metal catalyst deposition is been achieved. Subsequent CVD results in spacially constrained CNTs in a clean surface (Figure 5.12, right). The optimal design to selectively place catalyst could not be determined mainly due to the non reproducibility of synthesis results, caused by solution deposition, resist stripping and growth process uncertainties. However, sometimes the wet elimination of PMMA also dissolves metal particles and results in re-deposition of the catalyst material out of the patterned areas (Figure 5.12, left). Optimization of resist stripping with plasma etching might be convenient to minimize re-deposition of the metal particles.

Figure 5.12 (Left) AFM image shows a detail of selective catalyst deposition after PMMA stripping. Some rests are redeposited out of the patterned area. (Right) Two CNTs (white arrows) grown from selective catalyst deposition are contacted. In the upper part of the image the local deposition can be seen together with the cleanness of the rest of the surface.

The fabrication process follows with the definition of marks. It is performed by a second EBL aligned with selective catalyst deposition, metal deposition and lift off. Then, AFM inspection and fabrication of drain and source contacts, as described before. An example of the final result of CNT device fabrication is shown in Figure 5.12, right.

The fourth process sequence is a variation of the previous approach, but reduces its complexity to two lithography levels. In this case, the patterning of PMMA is used for reference and alignment marks definition together with selective deposition of the catalyst. After EBL and development, catalyst metal particles are deposited underneath the Cr + Au thin layer used for fabrication of the marks. Figure 5.13, left and center, shows that the strategy is valid for the CNT growth.

Figure 5.13 Results of local catalyst deposition under the alignment mark sites. (Left) Contacted CNT using the mark as contact interface. (Center) Example of a SWCNT grown with this technique. (Right) Optimization of marks shape and configuration may lead to precontacted CNTs.

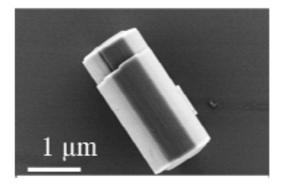

In addition, contact using metal mark interface after CVD is possible, as realized in Figure 5.13 (more details in section 5.3). AFM inspection corroborates that SWCNTs are obtained (Figure 5.13 center). Actually, this method is used for fabrication of many devices (Figure 5.27). An optimal design could tailor pre-contacted CNTs, as intented in Figure 5.13, right and make device fabrication easier or open to new catalyst materials or possibilities. As an example, ferrocene (catalyst) has been immobilised with a thin metal layer and subsequent CVD growth shows that it is possible to synthesize massive number or individual CNTs in selected places, Figure 5.14.

Figure 5.14 SEM images of potential application of this approach where catalyst is deposited below the thin metal layer (white arrow). Ferrocene has been used as the catalyst for the CNT synthesis.

# 5.3 Electrical characterization

The introduction of CNTs as part of electronic devices represents an evolutionary approach from existing silicon based technologies (common configuration). After more than four decades of improvement of electronic systems by the scaling down of transistors, the end of this development comes closer. Even if technologies continue to improve device dimensions with enhanced fabrication processes, Si-based nanoscale devices will account from loss of bulk properties of their constituent solids (materials). In consequence, leakage current, energy quantization, velocity saturation, drain and source series resistance, etc may disable further evolution.

The use of single molecules is suposed to be capable of overcoming this barrier by maintaining the operating principle of MOSFETs. Molecular based transistors should perform in signal amplification regime in order to allow separate signal treatment in logical operation chains. Moreover, noise is reduced by decreasing thermal fluctuations and environmental disturbances.

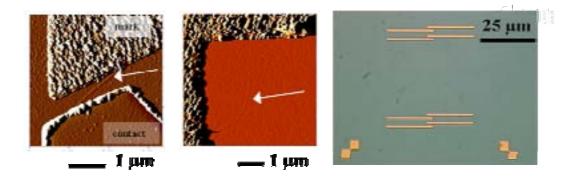

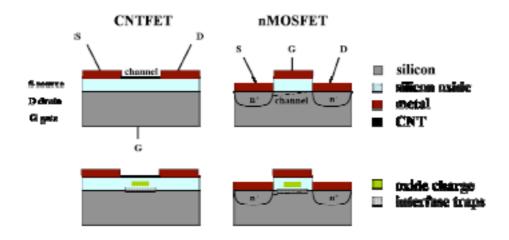

MOSFET is the most important device in the semiconductor industry. It is based on a configuration that consists of three terminals (a fourth terminal, substrate, is typically used, but it does not participate actively in device performance). Two electrodes (drain and source contacts) connect the two heavily doped areas and they are separated by the non doped Si channel. The third electrode acts as the gate and is isolated from the rest by a thin insulator layer (typically, SiO<sub>2</sub>) (Figure 5. 15).

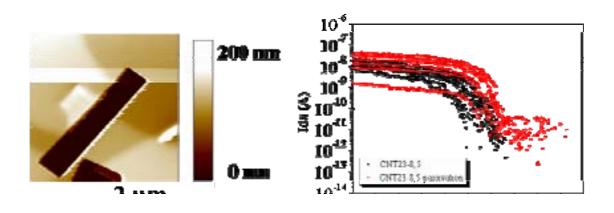

Figure 5.15 Comparison of FET configurations using the CNT as the device channel (top left) or with the conventional MOSFET structure (top right). In pMOSFETs, Si substrate is n type doped and proper device polarization induces the creation of the channel that starts device conduction. (Center) Comparison of electrical characteristics for two devices fabricated at the CNM. CNTFET (1 µm lenght channel) performance is nearly comparable to MOSFET (3x3 µm²), whereas device dimensions are significantly smaller for CNT-based device. (Bottom) Comparison table of experimental CNTFETs and MOSFETs from (21).

The working principle relies on the modification of channel resistivity by means of external electric fields. For the nMOSFET in Figure 5.15, the presence of positive charge on the gate (Vg) does not cause n-type channel conduction until a certain threshold voltage is applied between source and gate contacts. Hence, switching mechanism is based on channel resistance modulation.

For molecular based transistors, single molecules are proposed to play the role of channel conduction. As presented above, CNT structure (diameter and chirality) determines whether their intrinsic electronic transport is metallic or semiconducting. Theoretical studies based on local-density-functional and tight-binding calculations predict their electronic distribution (5). Semiconducting tubes are expected to be characterized by an energy gap,

$$E_{gap} = 2\gamma_0 a_{c-c}/d$$

,

where  $a_{c-c} = 0.142$  nm is carbon-carbon distance,  $\gamma_0$  is C-C tight binding overlap energy and d is the tube diameter.

Besides this, their quasi 1D structure reduces phase space for scattering, so ballistic transport is predicted for ideal SWCNTs due to their perfect symmetry and periodicity. Equivalent effective mass for electrons and holes leads to both negative and positive charge carrier mobility. Therefore, CNTs may stand out in electronic devices due to metallic and semiconducting transport for interconnections and transistors, respectively, high mobilities for high speed device applications, 1D confinement for decreasing channel length, ambipolar conduction controlled by  $V_{gate}$  for CMOS-like technology (logic circuits), etc (22, 23, 19).

Defects in their atomic structure are seen as scattering centers that interfere in the ideal charge transport. Chemical doping induces diffuse transport and impurities cause resistivity increase in SWCNTs. MWCNTs show also scattering effects and diffussive electron motion, with a characteristic localization of few nanometers and high tube-tube variability in conduction. What is more, semiconducting tubes are more difficult to analise due to interband scattering, but they are usually described in terms of classical physical laws of diffusivity, conduction in terms of effective mobility (24).

A model to explain the operation mechanism and to determine the expressions, which quantifies the FET conduction as a function of device properties, is detailed in the PhD thesis of Sami Rosenblatt from Cornell University ('Pushing the limits of Carbon Nanotube Transistors', January 2006). As mentioned, FET is a variable conductor, where the amount of carriers at the interface of the semiconductor is a function of the voltage applied to the gate (Vg). For the CNTFETs, the characteristics can be obtained analogous to the derivation of 3D FET, considering diffusive transport confined to 1D material. The steeped transistor operation is consequence of the application of band structure properties of the CNT. For the CNT relative to the gate contact, the configuration is equivalent to a MOS capacitor. The voltage applied to the gate modulates the position of CNT Fermi level from valence band to conduction band. Hence, the contact resistances between CNT and metal contacts determine the final operation of the device.

The device performance parameters that characterise a FET are common for both configurations, Si or CNT based FETs.

- On current (Ion) determines the amount of charge that is transmitted,

- On-off current ratio (Ion-off) quantifies the difference in conduction between on and off device state,

- Threshold voltage (Vth) determines the gate potential necessary to switch on the transistor effect,

- Transconductance (G) (or similarly, subthreshold slope) accounts for the dependence of current on gate voltage.

These parameters are the ones that are used in present section to evaluate the performance of actual fabricated CNT based devices.