# Code-Centric Domain Isolation: A Hardware/Software Co-Design for Efficient Program Isolation

Lluís Vilanova

<vilanova@ac.upc.edu>

Barcelona, 2015

Advisors:

Nacho Navarro

Universitat Politècnica de Catalunya Barcelona Supercomputing Center

Yoav Etsion Technion — Israel Institute of Technology Technion Computer Engineering Center

A thesis submitted in fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC International Doctorate Mention

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

Thanks to all the lights along the journey, without whom it would be too dark to travel.

# Abstract

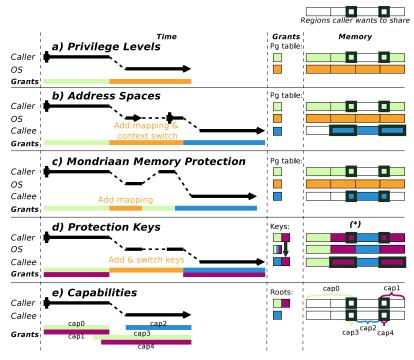

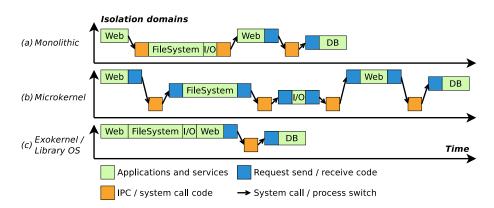

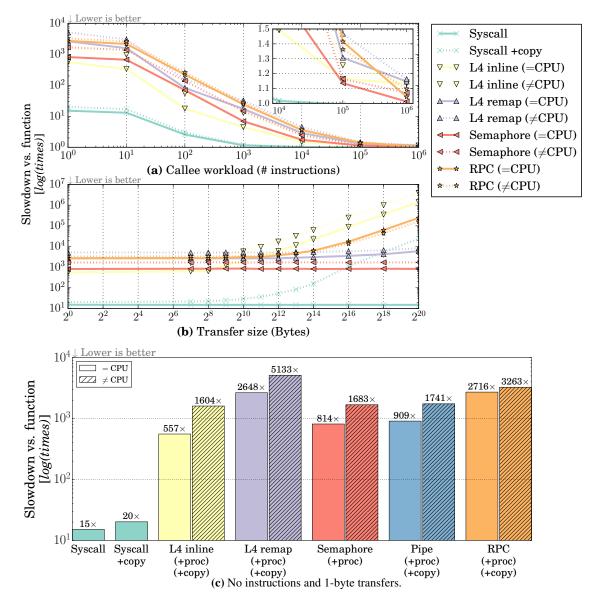

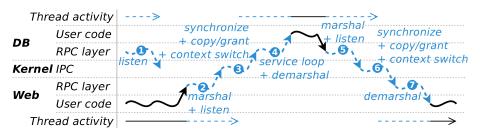

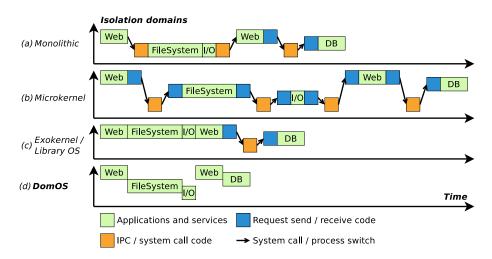

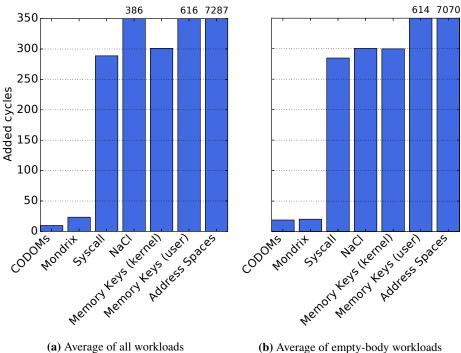

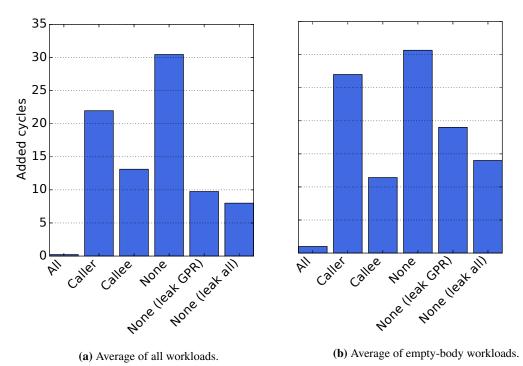

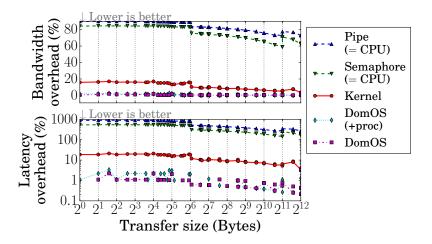

Current Operating Systems (OSs) employ a process-centric isolation model. This is partly attributed to existing processors providing memory isolation across page tables. In this prevailing model, threads are bound to their creating process, and invoking functionality across processes requires costly OS kernel mediation and application developer involvement to synchronize and exchange information through Inter-Process Communication (IPC) channels. Therefore, using processes as an isolation unit imposes performance and programmability overheads. Nonetheless, processes also serve two other necessary roles. First, they act as resource containers; OSs track resources like memory and open files at the process granularity. Second, processes provide in-memory persistence; using a process ensures that its state is consistent across the coming and going of other processes that communicate with it. The architectural foundations used for building processes impose performance overheads in the excess of  $10 \times$  and  $1000 \times$  compared to a function call; that is, privilege level and page table switches, respectively. Even more, part of these overheads are not attributable to the hardware itself, but to the inherent overheads imposed by current OS designs.

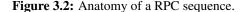

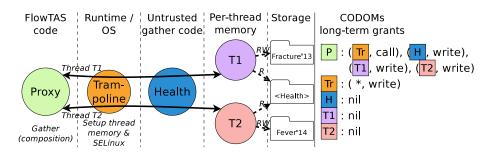

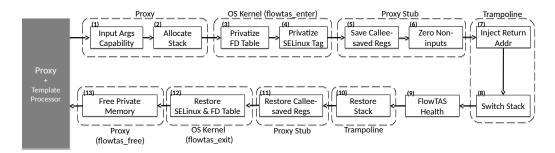

This thesis proposes a hardware and software co-design to eliminate the overheads of process isolation, while providing a path for gradual adoption for more aggressive optimizations. On the hardware side, this thesis proposes the CODOMs protection architecture. It provides memory and privilege protection across software components in a way that is at the same time very efficient and very flexible. This hardware substrate is then used to propose DomOS, which provides changes to the OS at the runtime and kernel layers to allow threads to efficiently and securely cross process boundaries using regular function calls. That is, a thread in one process is allowed to call into a function residing in another process without involving the OS in the critical communication path. This is achieved by mapping processes into a shared address space and eliminating IPC overheads through a combination of new hardware primitives and compile-time and run-time optimizations.

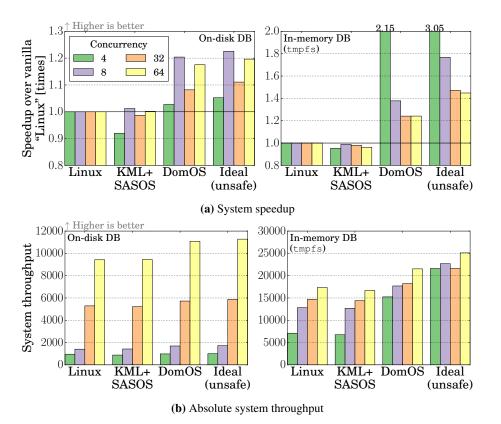

IPC in DomOS is up to  $24 \times$  times faster than Linux pipes, and up to  $14 \times$  times faster than IPC in L4 Fiasco.OC. When applied to a multi-tier web server, DomOS performs up to  $2.18 \times$  better than an unmodified Linux system, and  $1.32 \times$  on average. On all configurations, DomOS provides more than 85% of the ideal system efficiency.

# Contents

| 1 | Intr | oduction 1                                                            |  |  |  |  |  |

|---|------|-----------------------------------------------------------------------|--|--|--|--|--|

|   | 1.1  | The Granularity, Performance and Programmability Dilemma              |  |  |  |  |  |

|   | 1.2  | Conjoining Isolation, Performance and Programmability                 |  |  |  |  |  |

|   | 1.3  | Document Organization                                                 |  |  |  |  |  |

| 2 | A C  | Comparison of Related System Organizations and Isolation Primitives 7 |  |  |  |  |  |

|   | 2.1  | A Note on Nomenclature                                                |  |  |  |  |  |

|   | 2.2  | Hardware Protection Mechanisms    7                                   |  |  |  |  |  |

|   |      | 2.2.1 Privilege Levels                                                |  |  |  |  |  |

|   |      | 2.2.2 Address Spaces                                                  |  |  |  |  |  |

|   |      | 2.2.3 Machine Virtualization                                          |  |  |  |  |  |

|   |      | 2.2.4 Capability Architectures                                        |  |  |  |  |  |

|   | 2.3  | Operating System Organization Models                                  |  |  |  |  |  |

|   | 2.4  | Software Isolation Mechanisms                                         |  |  |  |  |  |

|   |      | 2.4.1 Processes                                                       |  |  |  |  |  |

|   |      | 2.4.2 Address Spaces                                                  |  |  |  |  |  |

|   |      | 2.4.3 Machine Virtualization                                          |  |  |  |  |  |

|   |      | 2.4.4 Software Fault Isolation                                        |  |  |  |  |  |

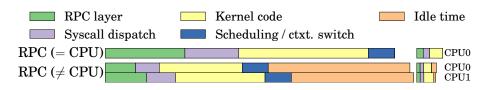

| 3 | The  | Interplay Between Isolation and System Design 19                      |  |  |  |  |  |

|   | 3.1  | The Inadequacies of Process-Based Isolation                           |  |  |  |  |  |

|   | 3.2  | Mismatch Between Procedure Call and IPC Semantics                     |  |  |  |  |  |

|   | 3.3  | False Concurrency                                                     |  |  |  |  |  |

|   | 3.4  | A Case for Configurable Isolation Policies                            |  |  |  |  |  |

| 4 | Effi | cient and Composable Isolation Primitives 27                          |  |  |  |  |  |

|   | 4.1  | Security Model                                                        |  |  |  |  |  |

|   | 1.1  | 4.1.1 Asymmetric Isolation Policies                                   |  |  |  |  |  |

|   | 4.2  | System Design Overview                                                |  |  |  |  |  |

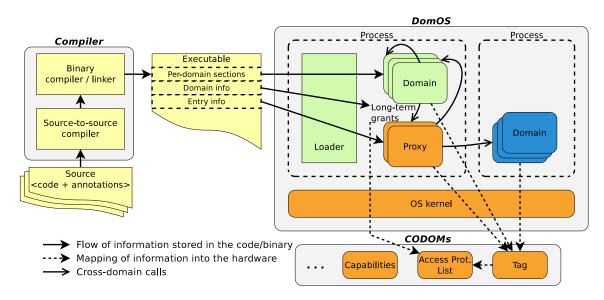

|   | т.2  | 4.2.1 CODOMs                                                          |  |  |  |  |  |

|   |      | 4.2.1 Condition Support                                               |  |  |  |  |  |

|   |      | 4.2.2 Complet Support                                                 |  |  |  |  |  |

|   | 12   |                                                                       |  |  |  |  |  |

|   | 4.3  | Isolation Scenarios                                                   |  |  |  |  |  |

| 5 | Har        | dware Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                  |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

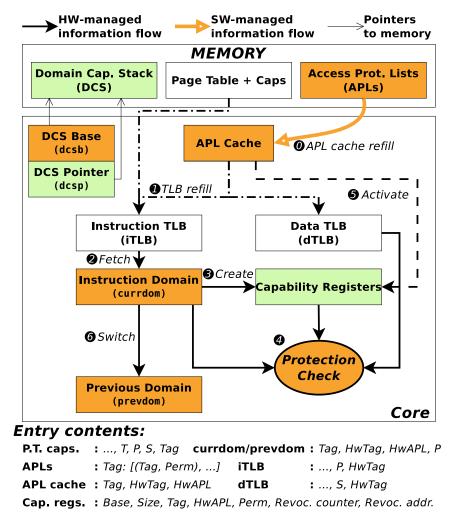

|   | 5.1        | Code-Centric Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                  |

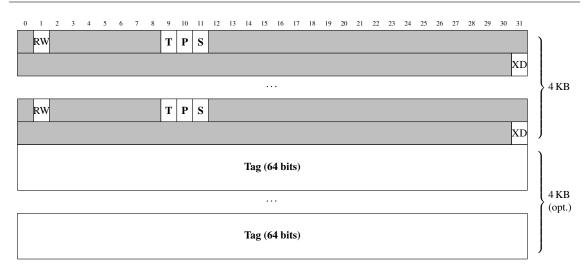

|   |            | 5.1.1 Page Table Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                  |

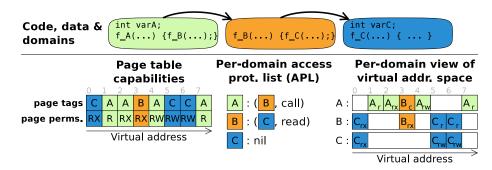

|   |            | 5.1.2 Domain Access Permissions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40                                                  |

|   |            | 5.1.3 Access Protection List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                  |

|   |            | 5.1.4 Example of Code-Centric Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                                  |

|   | 5.2        | Capability Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                  |

|   |            | 5.2.1 Example of Capability Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44                                                  |

|   |            | 5.2.2 Capability Confidentiality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                  |

|   |            | 5.2.3 Capability Unforgeability and Integrity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                  |

|   |            | 5.2.4 Domain Capability Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                  |

|   |            | 5.2.5 Capability Revocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                  |

|   | 5.3        | Enforcing Domain Entry and Exit Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                                                  |

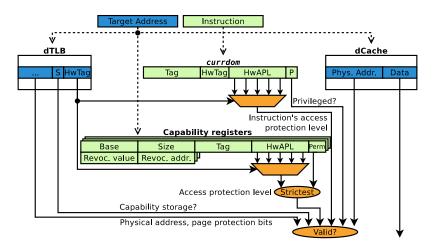

|   | 5.4        | Implementation of Access Protection Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                  |

|   | 5.5        | Efficient Execution in Out-of-Order Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                  |

|   | 5.6        | Revisiting Isolation Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                                  |

|   | 0.0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

| 6 | Con        | ipiler Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                                  |

|   | 6.1        | Language Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                  |

|   | 6.2        | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                  |

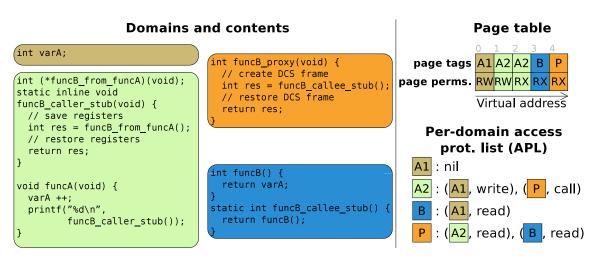

|   | 6.3        | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                  |

| - | 0          | - Contract Contract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                  |

| 7 | 7.1        | rating System Support         Processes and Threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>59</b><br>60                                     |

|   | 7.1        | Low-Level Isolation Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                  |

|   | 1.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                  |

|   |            | <ul> <li>7.2.1 Domain Management</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                  |

|   |            | 7.2.2       Entry Point and Cross-Domain Proxy Management         7.2.3       Capability Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                  |

|   | 7.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                  |

|   | 1.5        | Runtime Support    7.3.1      Program Loading    7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                  |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66                                                  |

|   | 7.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67                                                  |

|   | 7.4        | Implementation Details       7.4.1         Unified Virtual Address Space       7.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                  |

|   |            | 7.4.1 Unified Virtual Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

|   |            | 7.4.2 Thread Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                                                  |

|   |            | 7.4.2 Thread Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                  |

|   |            | 7.4.3 Thread-Local Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68                                                  |

|   |            | 7.4.3       Thread-Local Storage         7.4.4       Cross-Process Proxies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68<br>69                                            |