# Integration of CMOS-MEMS resonators for radiofrequency applications in the VHF and UHF bands

Jordi Teva Meroño Phd thesis

July 4, 2007

#### Departament d'Enginyeria Electrònica

| El Dr. Gabriel Abadal Berini, Professor Titular d'Electrònica del Departament d'Enginyeria Electrònica de la Universitat Autònoma de Barcelona,                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CERTIFICA                                                                                                                                                                                                                               |

| que la memoria Integration of CMOS-MEMS resonators for radiofrequency applications in the VHF and UHF bands que presenta Jordi Teva Meroño per optar al grau de Doctor en Enginyeria Electrônica, s'ha realitzat sota la seva direcció. |

| Bellaterra, juny de 2007                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                         |

Dr. Gabriel Abadal Berini

To my wife, Paola

#### **Abstract**

This thesis is focused on the monolithic integration of microresonators in a commercial CMOS technology, AMS-0.35 $\mu m$ , by using the standard layers of the process. The structures are released in a maskless post-CMOS process based on a wet hydrofluoric etchant. Those resonators will make the role of frequency selective devices replacing off-chip components of present front-end tranceivers communication systems relying on their reduced size, cost production and lower consumption.

In order to design and modelize those microresonators, an electromechanical model based on the real deflection of flexural resonator will be described allowing the designer to predict the maximum current levels at resonance. In addition to that, a set of mechanical design equations will be presented for all fabricated devices.

Along this report, different technological approaches using the available layers of the standard technology for fabricating microresonators will be introduced and discussed. From the design point of view, reducing the gap distance between resonator and driver becomes one of the relevant parameters that will enhance the electrical response of the device. Then, the approaches will be focused on reducing gap distances as much as possible. For the most promising approaches, limitations based on the vertical stiction in the releasing process will be considered in order to avoid the design of structures with limited performance.

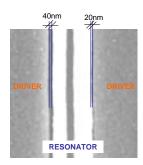

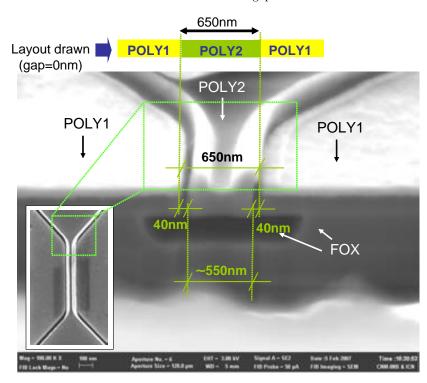

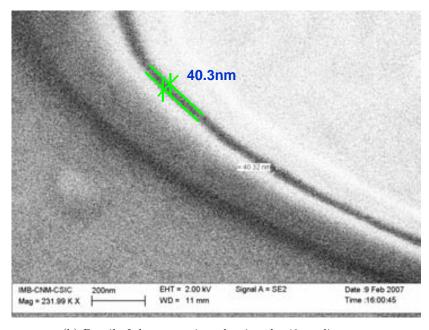

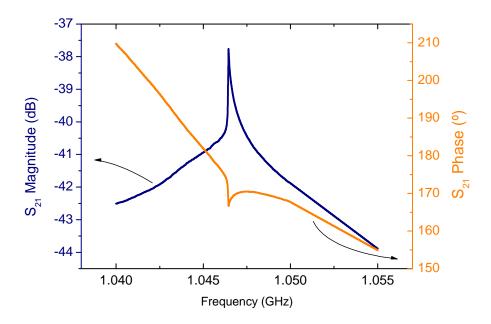

A fabrication approach based on the layers of the standard capacitance module will stand out as the most promising approach for successfully fabricate integrated MEMS resonators in the VHF and UHF frequency range, as expenses of 40nm gap distances. Devices exhibiting frequencies in the VHF range, with high quality factors up to 3000 at 290MHz will be presented, giving a figure of merit of  $Q \times f = 9 \cdot 10^{11} \text{Hz}$ . Furthermore, preliminary results on the characterization of a ring bulk acoustic resonator at 1GHz will be described.

La realització d'una tesi doctoral implica una relació més enllà de la purament laboral entre el doctorant i el seu entorn. Per això i per damunt de tot, voldria destacar la excepcional qualitat humana del meu director de tesi, en Gabriel Abadal i Berini, que m'ha proporcionat un ambient de treball idoni per a la realització d'aquesta tesi doctoral i al qual sempre li estaré agraït. A més a més, la seva professionalitat, la seva quantitat i qualitat d'idees, el seu suport, la seva paciència i les discussions compartides han fet possible el desenvolupament d'aquest projecte i el meu creixement professional.

Voldria estendre els meus agraïments a la cap de grup, na Núria Barniol i Beumala per haverme mostrat sempre la seva confiança i per l'oportunitat brindada a l'integrar-me en el seu grup de recerca col·laborant en els projectes Nanomass i Nanosys.

L'Arantxa Uranga i en Jaume Verd han estat els responsables de dissenyar la circuiteria CMOS que han acompanyat els 'meus' ressonadors. Sense la seva feina no hauria estat possible obtenir els resultats que al llarg de la tesi s'han presentat. L'ambient en el grup de recerca ha propiciat la discussió i l'aparició de moltes idees entre els meus companys, dels quals he après contínuament. Els haig d'agrair a tots ells per aquestes llargues discussions i de tot allò que m'han fet veure, sense distinció entre ells, a en Jaume Verd, l'Arantxa Uranga, en Francesc Torres i en Joan Lluís López.

Una col·laboració més estreta amb el meu company de despatx, en Francesc Torres, han donat resultats experimentals continguts en aquesta mateixa tesi. A ell li haig d'agrair l'obtenció dels resultats del procés de fabricació tecnològic, del qual ell ha estat el principal responsable a més de ser l'impulsor de totes les solucions als problemes aparescuts, la seva paciència al ensenyar-me el meravellós món de Coventor, i la seva particular visió del pessimisme positiu.

En Jaume Esteve ha estat sempre una persona molt oberta a col·laborar i a ajudar-me en tot el relatiu al post-procés CMOS. Les seves suggerencies han estat clau per l'èxit en aquesta

etapa; és clar, sense el bon fer de les 'Martes', res d'això no hagués estat possible. La Marta Duch i la Marta Gerboles han sigut un exemple continu de feina ràpida i ben feta.

Voldria agrair a en Francesc Pérez-Murano, la possibilitat de treballar amb ell durant el projecte del Nanomass i és clar, l'àmplia publicitat feta del sistema de mesura de freqüències naturals de ressonadors amb els piezoelèctrics, sistema que va ser desenvolupat amb la inestimable ajuda i suport d'en Xavier Jordà.

A en Zach Davis i a l'Anja Boisen els voldria agrair l'oportunitat d'incorporar-me durant quatre mesos al seu grup de recerca al MIC. Ells, conjuntament amb en Jan Hales, la Irene Fernández Cuesta l'Stephan Keller i en Anders Greeve van fer de la meva estada a Dinamarca un període profitós professionalment i a la vegada personalment enriquidor. Estenc aquests agraïments a tot el grup del Nanoprobes, i a tota la gent del MIC i Danchip per l'excel·lent ambient de treball que van fer de l'estada al MIC una etapa inoblidable.

No em voldria oblidar d'agrair tots els companys de departament, des de tots els becaris, associats, ajudants, titulars, agregats,..., fins al director, pels bons moments compartits. Mai oblidaré tot el suport logístic i personal que m'han brindat la Mari Carme, (darrerament també la Toñi) i en Javier Hellín, que ha patit la meva poca traça alhora de treballar al taller.

Ja de petit, els meus pares, l'Adela i en Manel, em van inculcar valors com la paciència, la confiança, i l'esforç per aconseguir aquells reptes que a primera vista podien semblar tan llunyans. De ben segur, que sense aquests valors avui no hi seria aquí. D'alguna manera ells són coautors i partíceps de tota aquesta feina. Ja farà uns quants anys, el meu germà Manel em va insistir en assistir-hi a unes classes extraescolars d'anglès, i sense saber-ho em va proporcionar una eina de futur molt valuosa, mai ho oblidaré. La Dolors, la meva germana, sempre m'ha demostrat la seva confiança en mi i m'ha donat peu a aconseguir tot allò que semblava un somni.

Hi ha persones que et fan ressaltar una part de la teva manera de ser i inconscientment et potencien les teves millors virtuts en front de les mancances. A la Paola, ara la meva dona, li vull agrair tot el seu constant suport i els seus ànims en la realització d'aquest treball.

# Contents

| 1                                         | Intr | Introduction                                                             |  |  |

|-------------------------------------------|------|--------------------------------------------------------------------------|--|--|

|                                           | 1.1  | Motivation                                                               |  |  |

|                                           | 1.2  | Transceiver Architectures                                                |  |  |

|                                           |      | 1.2.1 Superheterodyne transceiver                                        |  |  |

|                                           |      | 1.2.2 RF-MEMS in superheterodyne architectures                           |  |  |

|                                           | 1.3  | MEMS fabrication technologies                                            |  |  |

|                                           | 1.4  | Transduction in RF-MEMS                                                  |  |  |

|                                           |      | 1.4.1 General actuation and detection methods                            |  |  |

|                                           |      | 1.4.2 Capacitive transduction                                            |  |  |

|                                           | 1.5  | Objectives, challenges and outline of the thesis chapters                |  |  |

| 2 Resonator Electromechanical modeling    |      |                                                                          |  |  |

|                                           | 2.1  | The electromechanical model                                              |  |  |

|                                           |      | 2.1.1 Two-port modelization                                              |  |  |

|                                           |      | 2.1.2 Implementation in Pspice                                           |  |  |

|                                           |      | 2.1.3 Bulk acoustic resonators                                           |  |  |

|                                           |      | 2.1.4 Two-port modelization: In-Phase and Out-Phase resonance modes $32$ |  |  |

| 2.2 Flexural modes in beams               |      | Flexural modes in beams                                                  |  |  |

|                                           |      | 2.2.1 The flexural c-f beam                                              |  |  |

|                                           |      | 2.2.2 The flexural clamped-clamped beam                                  |  |  |

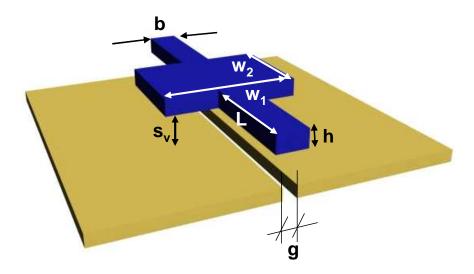

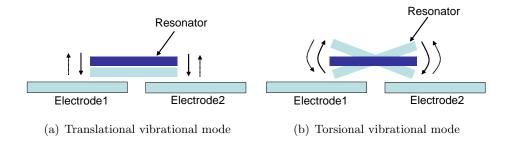

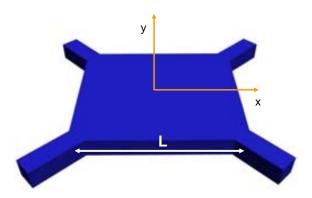

| 2.4 Longitudinal Bulk Acoustic Resonators |      | Torsional-Translational resonators. The paddle structure                 |  |  |

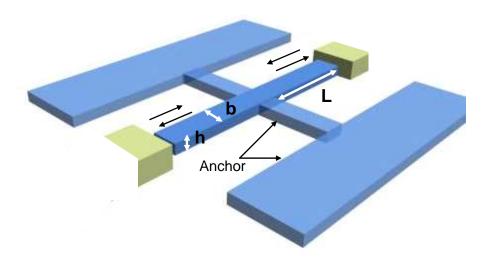

|                                           |      | Longitudinal Bulk Acoustic Resonators                                    |  |  |

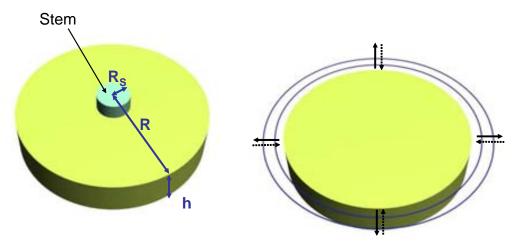

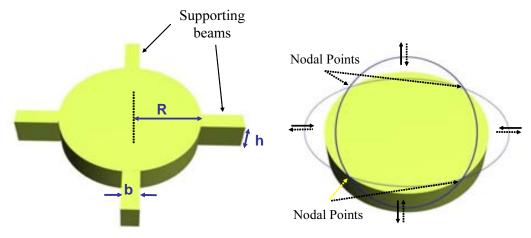

|                                           |      | Disk-shaped resonators in Radial Mode                                    |  |  |

|                                           | 2.6  | Disk-shaped resonators in Wine-Glass Mode                                |  |  |

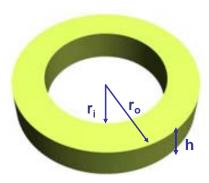

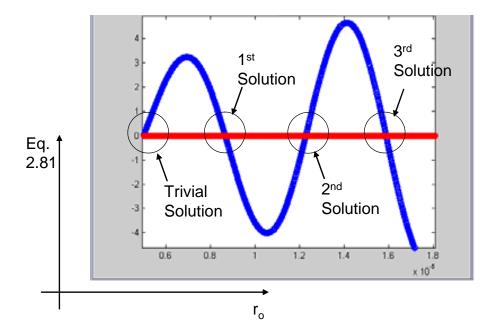

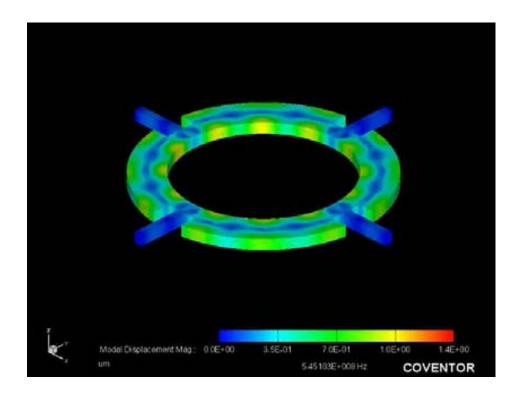

|                                           | 2.7  | Ring-shaped resonators                                                   |  |  |

|                                           | 2.8  | Square-shaped resonators                                                 |  |  |

|                                           | 2.9  | The Q-factor                                                             |  |  |

CONTENTS

|   |                                         | 2.9.1                                        | Losses in air                                        | 48         |  |  |  |  |

|---|-----------------------------------------|----------------------------------------------|------------------------------------------------------|------------|--|--|--|--|

|   |                                         | 2.9.2                                        | Suport losses                                        | 49         |  |  |  |  |

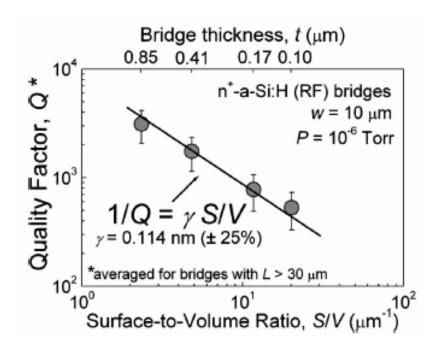

|   |                                         | 2.9.3                                        | Surface effect                                       | 49         |  |  |  |  |

|   |                                         | 2.9.4                                        | Thermoelastic damping, TED                           | 52         |  |  |  |  |

|   | 2.10                                    | Summ                                         | ary                                                  | 54         |  |  |  |  |

| 3 | Hybrid Approach for RF-MEMS Integration |                                              |                                                      |            |  |  |  |  |

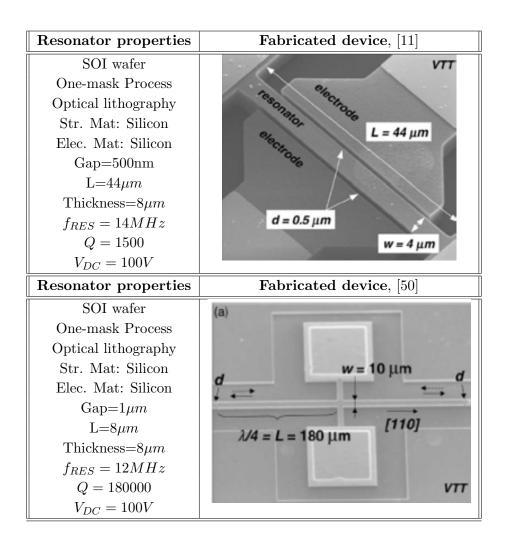

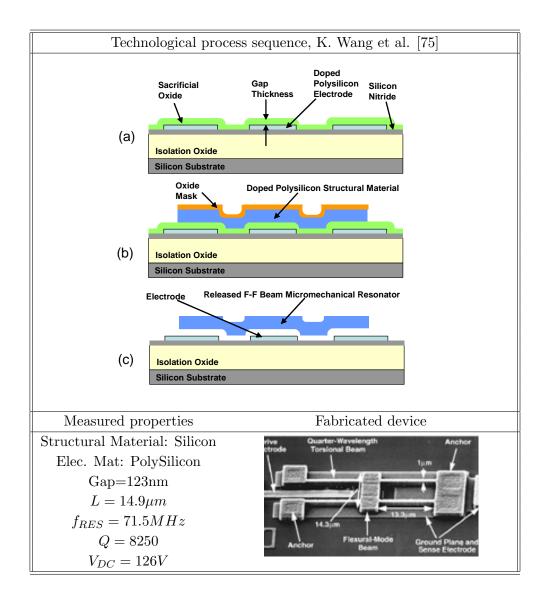

|   | 3.1                                     | State                                        | of the art for RF-MEMS fabrication                   | 57         |  |  |  |  |

|   |                                         | 3.1.1                                        | Reducing anchoring losses. Anchor material           | 64         |  |  |  |  |

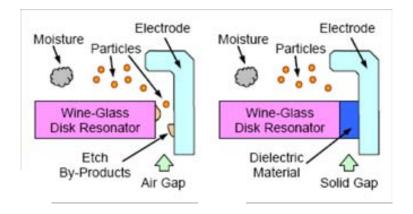

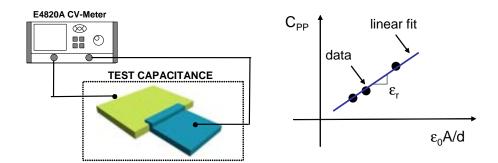

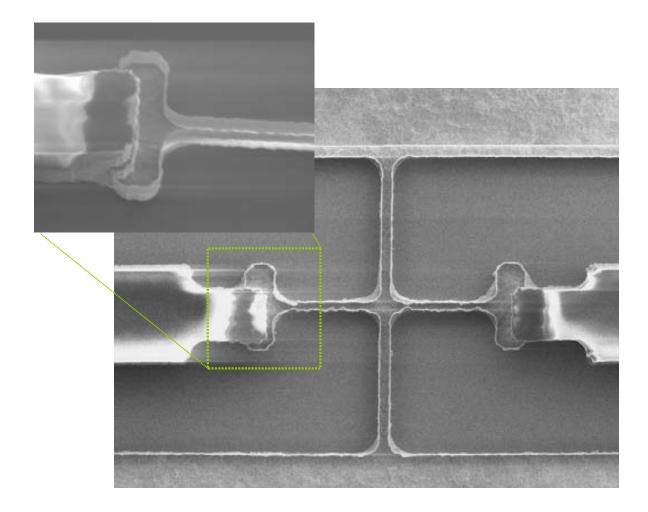

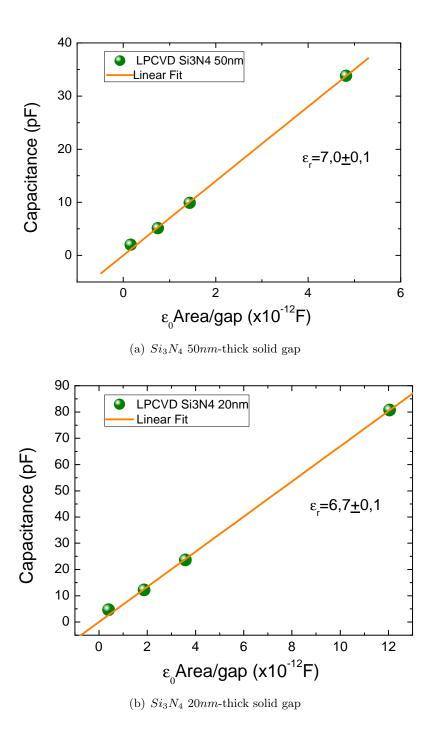

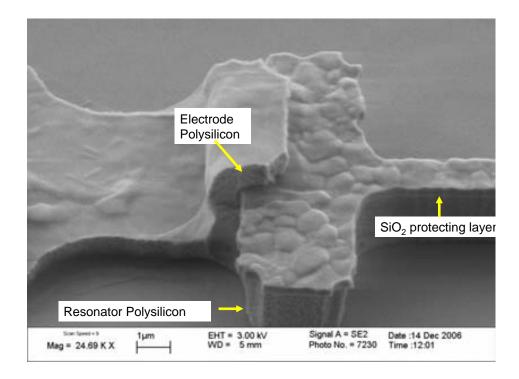

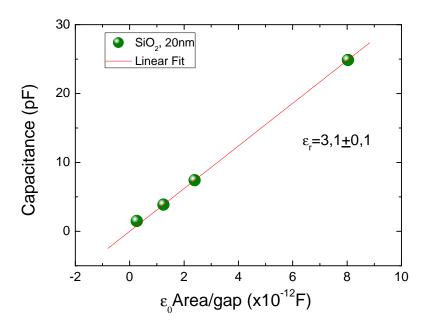

|   |                                         | 3.1.2                                        | The solid transducer gap                             | 66         |  |  |  |  |

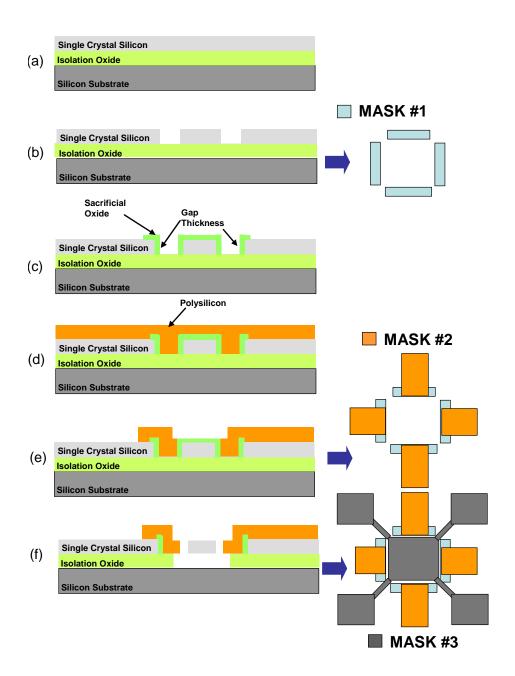

|   | 3.2                                     | Fabric                                       | eation process of air-gap resonators                 | 69         |  |  |  |  |

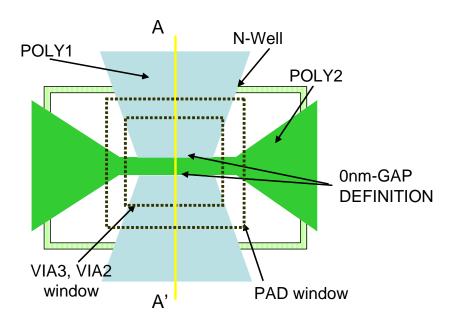

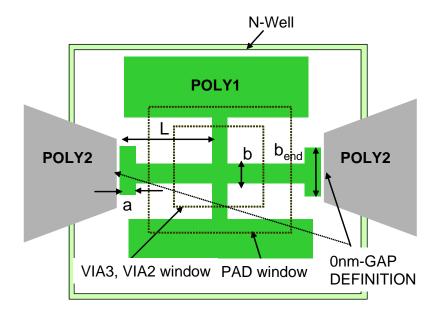

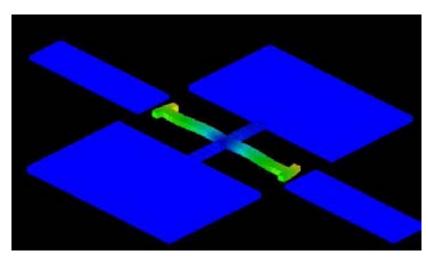

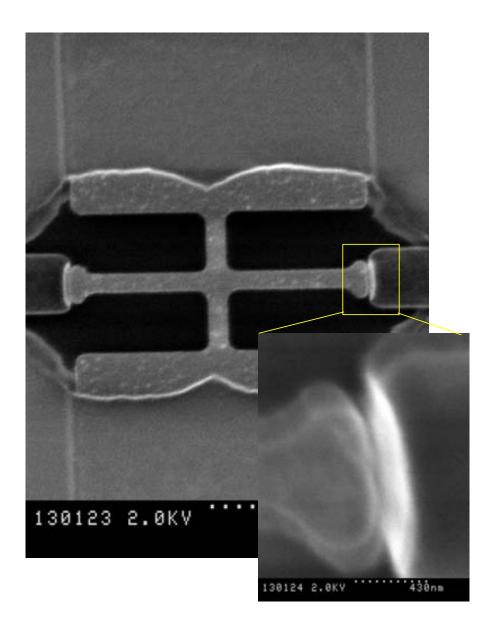

|   |                                         | 3.2.1                                        | Layout description                                   | 71         |  |  |  |  |

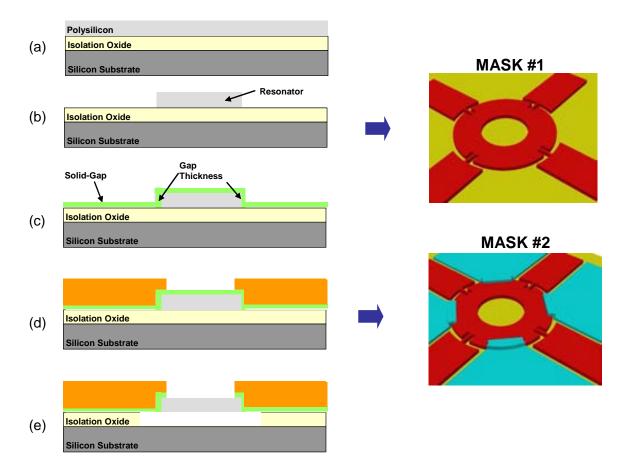

|   | 3.3                                     | Solid-g                                      | gap resonators                                       | 71         |  |  |  |  |

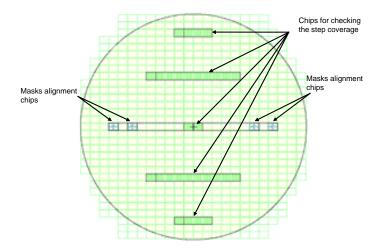

|   |                                         | 3.3.1                                        | Wafer description                                    | 73         |  |  |  |  |

|   |                                         | 3.3.2                                        | Chip description                                     | 74         |  |  |  |  |

|   | 3.4                                     | Summ                                         | nary                                                 | 77         |  |  |  |  |

| 4 | Mor                                     | nolithi                                      | c CMOS approach for RF-MEMS integration              | <b>7</b> 9 |  |  |  |  |

|   | 4.1                                     | Preced                                       | dents on CMOS-MEMS resonators fabrication            | 79         |  |  |  |  |

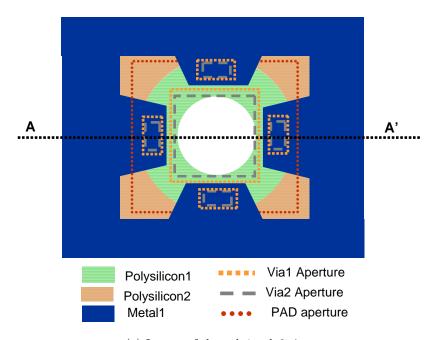

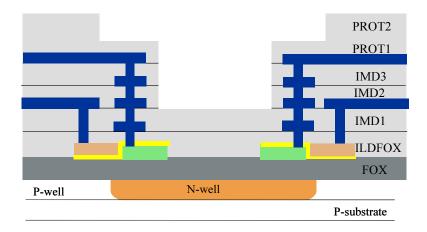

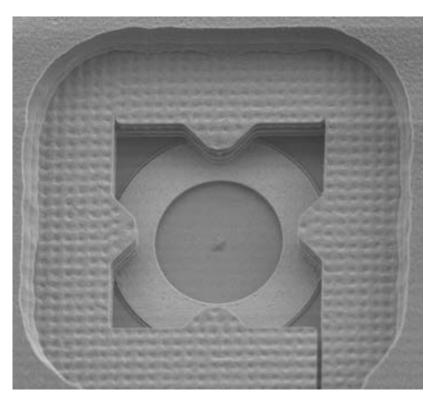

|   | 4.2                                     | AMS-0                                        | $0.35\mu m$ standard technology. General description | 81         |  |  |  |  |

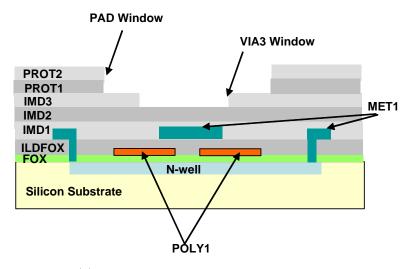

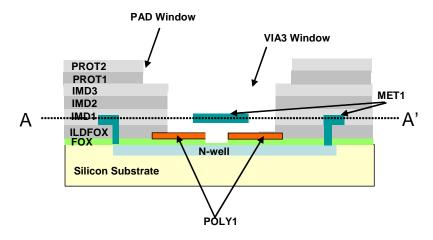

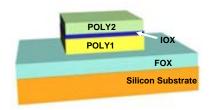

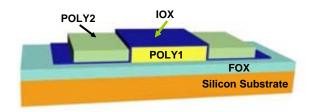

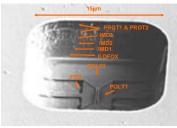

|   |                                         | 4.2.1                                        | Layers description                                   | 83         |  |  |  |  |

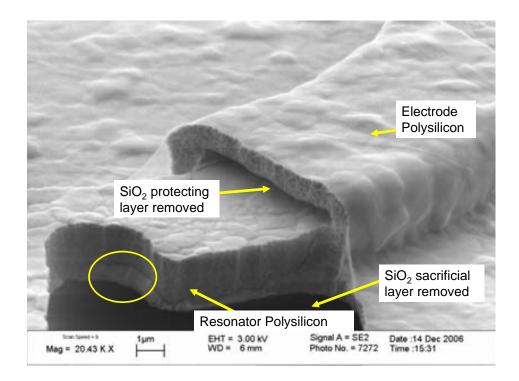

|   |                                         | 4.2.2                                        | Process for structure relasing                       | 84         |  |  |  |  |

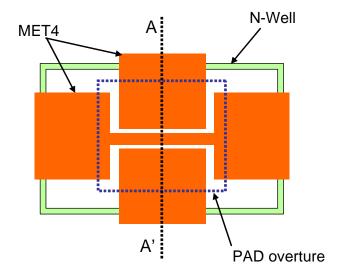

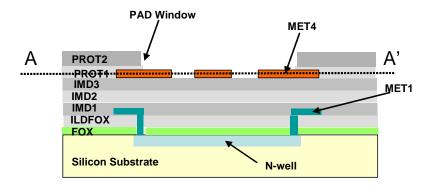

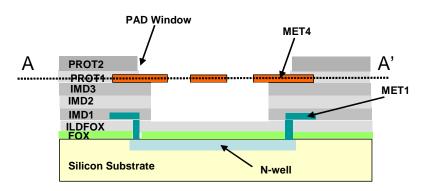

|   | 4.3                                     | Top M                                        | Ietal in-plane resonators                            | 87         |  |  |  |  |

|   | 4.4                                     | Vertical Metal-Polysilicon resonators        |                                                      |            |  |  |  |  |

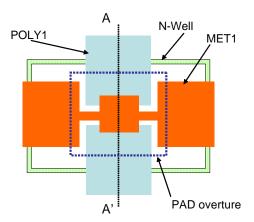

|   | 4.5                                     | Vertical and in-plane polysilicon resonators |                                                      |            |  |  |  |  |

|   | 4.6                                     | Limits                                       | s on CMOS-MEMS integration                           | 100        |  |  |  |  |

|   | 4.7                                     | Summ                                         | nary                                                 | 106        |  |  |  |  |

| 5 | Res                                     | ults or                                      | n RF-MEMS in the VHF band                            | 107        |  |  |  |  |

|   | 5.1                                     | Hybrid                                       | d resonators                                         | 107        |  |  |  |  |

|   |                                         | 5.1.1                                        | Air-gap resonators                                   | 107        |  |  |  |  |

|   |                                         | 5.1.2                                        | Solid-gap resonators                                 | 115        |  |  |  |  |

|   | 5.2                                     | Monol                                        | lithic resonators                                    | 133        |  |  |  |  |

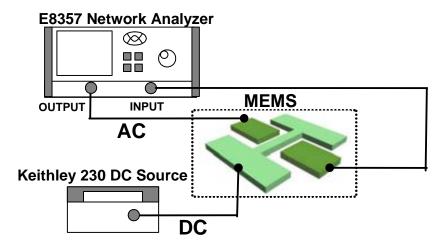

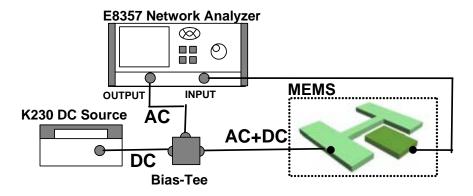

|   |                                         | 5.2.1                                        | CMOS readout circuitry                               | 133        |  |  |  |  |

|   |                                         | 5.2.2                                        | MET4 in-plane resonators                             | 137        |  |  |  |  |

|   |                                         | 5.2.3                                        | MET1-POLY1 vertical resonators                       | 143        |  |  |  |  |

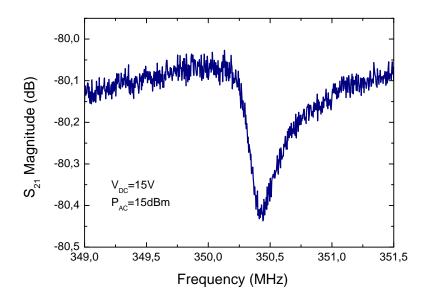

|   |                                         | 5.2.4                                        | POLY2-POLY1 vertical resonators                      | 148        |  |  |  |  |

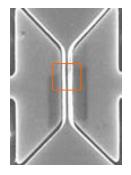

|   |                                         | 5.2.5                                        | POLY1-POLY2 in-plane resonators                      | 152        |  |  |  |  |

|   |                                         | 5.2.6                                        | POLY1 as structural layer. An improvement            | 158        |  |  |  |  |

|   | 5.3                                     | Summ                                         | nary                                                 | 167        |  |  |  |  |

## xi CONTENTS

| 6                | Res                       | cults on RF-MEMS in the UHF band               | 169                                                                                                                  |  |

|------------------|---------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

|                  | 6.1                       | Hydrid resonators in the UHF range             | 169                                                                                                                  |  |

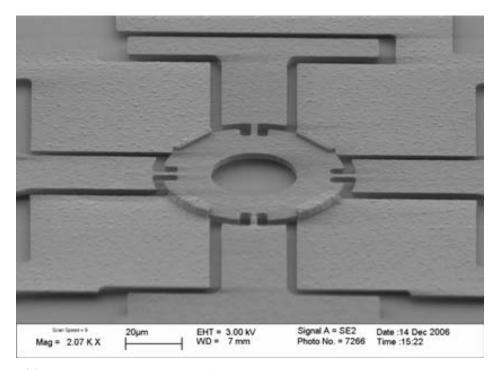

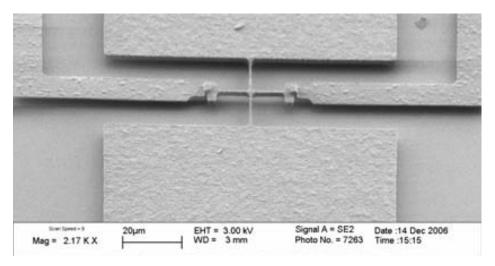

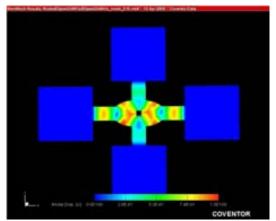

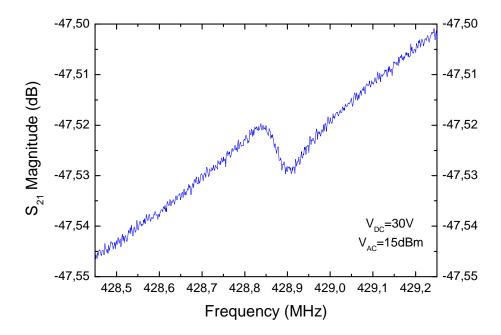

|                  |                           | 6.1.1 The elliptical resonator                 | 169                                                                                                                  |  |

|                  | 6.2                       | Monolithic resonators in the UHF range         | 172                                                                                                                  |  |

|                  |                           | 6.2.1 The Longitudinal Bulk Acoustic Resonator | 172                                                                                                                  |  |

|                  |                           | 6.2.2 The annular ring                         | 176                                                                                                                  |  |

|                  | 6.3                       | Summary                                        | 180                                                                                                                  |  |

| C                | onclu                     | asions                                         | UHF range       169         nator       169         he UHF range       172         Bulk Acoustic Resonator       172 |  |

| Bi               | bliog                     | graphy                                         | 185                                                                                                                  |  |

| $\mathbf{A}$     | bre                       | viations and Acronyms                          | 195                                                                                                                  |  |

| $\mathbf{A}_{]}$ | ppen                      | dices                                          | 199                                                                                                                  |  |

| $\mathbf{A}$     | Tec                       | hnologycal Processes                           | 199                                                                                                                  |  |

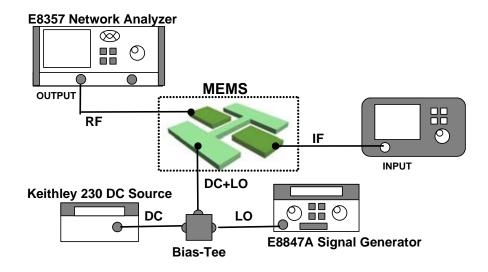

| В                | Mea                       | asurement techniques                           | 209                                                                                                                  |  |

| $\mathbf{C}$     | C List of publications    |                                                |                                                                                                                      |  |

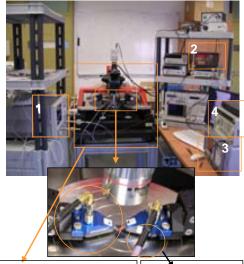

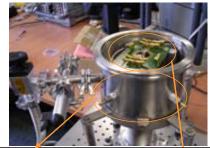

| D                | D Experimental facilities |                                                |                                                                                                                      |  |

# CHAPTER 1

Introduction

Micro Electro Mechanical Systems (MEMS) were predicted by the legendary physicist Richard P. Feynman, who theorized in 1959 that size was not a barrier to advanced technology ("there is plenty of room at the bottom" [1]). However, it took three decades until the first commercial MEMS appeared in cars in the early 1990s under the name of airbag. MEMS also exist in such diverse devices as ink jet printers, blood pressure monitors, Digital Light Processor (DLP) and digital video projection systems. The acronym MEMS, includes (at least) micro, electrical and mechanical systems that are fabricated by microfabrication techniques. In the large and dynamic world of MEMS, devices showing intrinsic frequencies in the RF band are taking more and more relevance in recent years, motivated by the appearance of new wireless and more autonomous demanding applications.

This chapter introduces main concepts related with microresonators fabrication technologies as well as present and future applications in RF communications front ends. Special attention is given to capacitive transduced resonators, which is the base of the work developed during this thesis.

#### 1.1 Motivation

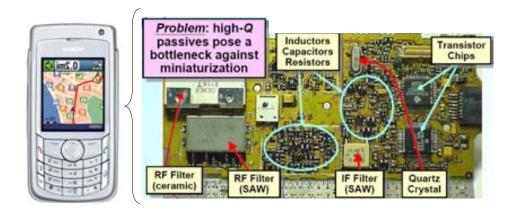

The increasing demand on mobile communications and devices, that is observed by the new generation of wireless protocols developed recently [2][3] that sum up to existing ones like Bluetooth [4] and Wifi [5], are driving to a miniaturization of radio transceivers. In this miniaturization process, tradeoff between cost, size and power consumption is crucial. In terms of size, passive off-chip components of the front-end transceiver architectures represents the bottle neck for miniaturization.

The possibility to implement the filtering, mixing and frequency control functionalities present in a front-end transceiver by MEMS devices, allow the system size and power consumption reduction, consequently improving the functionality and reducing costs.

The Radio Frequency Micro Electro Mechanical Systems (RF-MEMS) market includes products such as Bulk Acoustic Wave (BAW) resonators, switches, inductors and micromechanical resonators is expected to be the next major breakthrough for MEMS technology, driven by the RF systems for telecommunication offering the possibility to integrate and miniaturize, lowering power consumption, lowering losses and lowering costs.

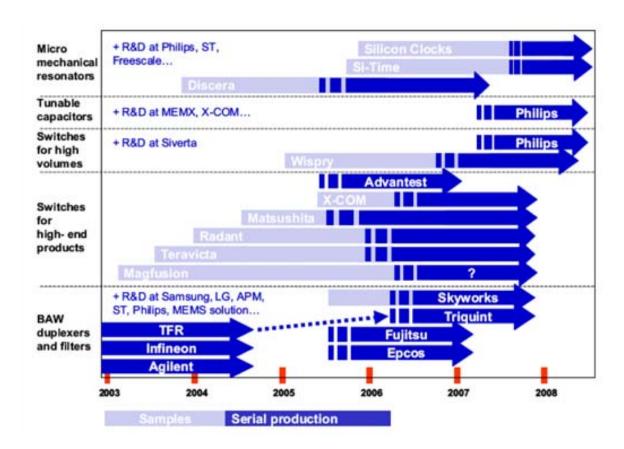

In figure 1.1 are depicted the commercial status from 2003 up to 2006 for 6 types of RF-MEMS components. BAW devices are currently the most mature components. On September 2005, several other companies were close to commercializing BAW, including EPCOS and FUJITSU. However, in the field of switches only a handful companies have started or are close to commercializing MEMS switches.

Figure 1.1: Commercialization of RF-MEMS products divided into 5 categories, showing the companies involved [6].

Recent progress on micro-mechanical resonators have been significant and specifically involves temperature stability and packaging. *DISCERA*, *SILICON CLOCKS* and *SiTIME* expect serial production by the end of this year.

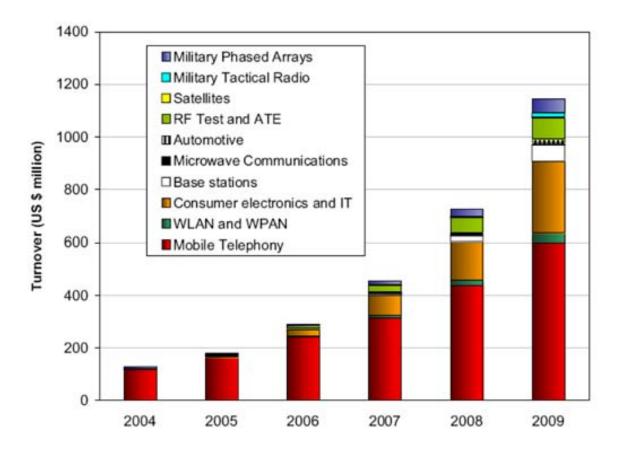

The market for RF-MEMS components was 126 million in 2004. Furtherthemore, it is expected to grow rapidly in the next few years to over 1.1 billion in 2009. In addition, the market will accelerate quickly in the period 2007 to 2009 as full-scale production starts for the majority of RF-MEMS components. The turnover forecast for the RF-MEMS market by application are shown in figure 1.2. Micromechanical resonators start to replace bulky off-chip quartz oscillators used as timing devices in consumer electronics. MEMS resonator-based clock devices will account for more than 20% of the RF-MEMS market in 2009. Switches are expected to penetrate cell phone applications from 2007 onwards, mainly for band and mode switching functions.

Figure 1.2: Forecasts for RF-MEMS components market, separated by applications, from 2004 to 2009 [6].

In this excellent situation for the RF market, this thesis has the main motivation of exploring, at the device component level, the integrability in a standard Complemetary Metal Oxide Semiconductor (CMOS) technology of MEMS resonators in the Very High Frequency (VHF) and Ultra High Frequency (UHF) frequency band.

#### 1.2 Transceiver Architectures

The evolution of radio transceivers was extraordinary in the last whole frequency and conditioned by the increasing request of available frequencies for radio-communication and with the limited frequency spectrum. In the second half of the last century, improvement was provided, mainly, by technological evolution and by the advent of digital modulation techniques. However, the typical radio architectures remain inalterable. Now, with the advent of portable revolution and the industrialization of MEMS devices, innovative radio-architectures are being designed to make possible the single chip fully integration.

#### 1.2.1 Superheterodyne transceiver

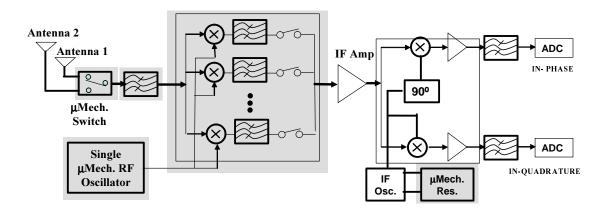

The superheterodyne transceiver is based on the idea of downconverting the signal band high frequency to lower frequencies in order to relax circuitry design. Figure 1.3 shows a typical superheterodyne transceiver architecture implemented in most of the actual RF communications transceivers. The transceiver is implemented with a collection of discrete-components filters and various technologies, Galium Arsenide (GaAs), Bipolar Complementary Metal Oxide Semiconductor (BiCMOS) and CMOS.

The integrated circuitry include the low noise amplifier, Low Noise Amplifier (LNA), and the Solid State Power Amplifier (SSPA), which has a similar function but in the transmit path), Phase Locked Loop (PLL) electronics and lower frequency digital circuits for baseband signal demodulation.

In superheterodyne receivers, the signal (centered at frequency  $f_{RF}$ ) captured by an antenna is initially filtered by the band selective filter and amplified by the LNA; then, that frequency is translated to the IF stage by the first mixer, driven by the local oscillator LO: the frequency  $f_{LO}$  is tunable and its value is a function of the carrier frequency of the channel that is received and demodulated ( $f_{LO} = f_C + f_{IF}$ ); the correct value of  $f_{LO}$  is fixed by an RF channel select frequency synthesizer. Note that the whole signal band is frequency translated, and not only the desired channel.

A first filtering of the received signal is performed at the IF stage (shadowed boxes in figure 1.3), in order to highlight only the desired channel. This filtering operation is performed at IF because channels they have typically a very narrow frequency occupation and then, excessive Q in the RF filter should be required. Then, the desired channel is amplified by a variable gain amplifier that adjust the desired signal in turn of reducing the dynamic range

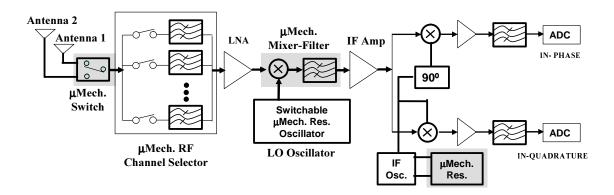

Figure 1.3: Block diagram for a RF channel-select receiver architecture showing potential replacements via MEMS-based components. Components to be replaced by MEMS are gray-shaded.

requirements of all subsequent blocks.

The most important thing in the design of a superheterodyne receiver concerns the choice of LO and IF frequencies. This choice is strictly related with the problem of the "image frequency,  $f_{IM}$ "; in a superheterodyne architecture, the bands symmetrically located above and below  $f_{LO}$  are downconverted to the same center frequency IF. The problem of the image is a serious one, whereas each wireless standard imposes constraints upon the signal emissions by its own users, it may have no control over the signals in other bands. Typically the channel at  $f_{IM}$  could be the channel of another user, and in general, can be very strong.

The classical solution to the image problem consist on the insertion, between the LNA and the mixer, of an image-rejection filter; this filter must present a relatively small loss in the desired band and a large attenuation in the image band. Obviously these two requirements can be simultaneously met if  $f_{IF}$  is sufficiently large (as  $f_{IF}$  increases, increases the distance in frequency between the channel frequency and its image with respect to  $f_{LO}$ , and decreases the performance on the image-rejection filter). If the choice of an high  $f_{IF}$  relaxed the Q requirement of the image-rejection filter, in order to relax the selectivity specifications of the channel selection filter,  $f_{IF}$  should be chosen as low as possible. This trade-off between image rejection and channel selection is the most important limitation of a superheterodyne receiver, and it can be lighten only using a multiple downconversion, each followed by filtering and amplification; this solution performs partial channel selection at progressively lower center frequencies, relaxing the required Q for each filter; this technique is known as "Dual-IF topology".

Figure 1.4: Optical image showing the replaceable off-chip components [8].

The last step of the transceiver depicted in figure 1.3 corresponds to the digital demodulation of the IF signal, that is performed in phase and in quadrature in order to minimize the effect of noise on the demodulation.

#### 1.2.2 RF-MEMS in superheterodyne architectures

In present superheterodyne communication transceiver depicted previously, vibrating components, such as crystal and Surface Acoustic Wave (SAW) resonators, are widely used because of their high quality factor and exceptional stability against thermal variations and aging.

High Q  $(10^2 - 10^3)$  in frequencies above 1GHz, low insertion losses, and large attenuation below and above the frequencies of interest shown by SAW and bulk acoustic wave-based resonators are used to achieve adequate frequency selection in the RF and IF stages [7]. On the other hand, those high Q values imply the required low phase noise and thermal stability to their local oscillators (LO). In order to complete the design of the superheterodyne architecture, off-chip discrete inductors and variable capacitors are used to properly tune and couple the front end sense and power amplifiers. However, this actual design is size limited because of the external off-chip resonator tanks and discrete passive elements, as shown in figure 1.4. In this sense, these devices pose a bottleneck against the ultimate miniaturization and portability of wireless transceivers.

The miniaturization of those high-Q resonators can be done as expenses of the high quality factors exhibited by MEMS devices. Furthermore, the rapid growth of IC-compatible micromachining technologies and the possibility to monolithically integrate those microresonators may bring the strategy to miniaturize on-chip those resonator components.

Among the off-chip components targeted for replacement are RF filters, including image rejection filters, with center frequencies ranging from 800MHz to 2.5GHz; IF filters, with

center frequencies ranging from 455kHz to 254MHz; high-Q, tunable and low phase noise oscillators, with frequency requirements in the 10MHz to 2.5 GHz range; and switches for transmit/receive (T/R) selection, antenna selection, and multi-band configurability. The main benefits form this replacement using MEMS are the size reduction, lower overall insertion losses and the ability to tailor the termination impedances required by RF and IF filters.

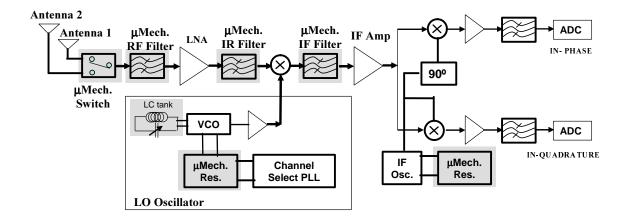

Figure 1.5: RF channel select receiver architecture using large number of micromechanical resonators to lower power consumption.

However, the direct replacement of off-chip high-Q passives is not the only possible approach using micromechanical resonators. A RF channel select architecture using a large number of high-Q micromechanical resonators in filter banks and switchable networks shown in figure 1.5 has been previously proposed [8]. By this approach, the RF architecture is based on two new blocks that minimize power consumption using the MEMS high-Q selectivity. The first new block is the *Switchable RF channel select filter bank*, where the channel selection is done at RF frequencies instead at IF frequencies, making following electronic blocks in the receiver path (LNA, *mixer*) no longer need to handle the power to alternate channel interferes. Then, a significant power reduction is achieved if the circuit is removed, or if the circuitry is maintained, more robust receivers are designed.

The use of a micromechanical mixer-filter (mixler) in the receive path (figures 1.3 and 1.5) eliminates the DC power consumption associated with the active mixer normally used in present day receiver architectures. This corresponds to power savings on the order of 10mW-20mW [8]. In addition to that, the requirements for designing the LNA are relaxed, because the mixler appears as purely capacitive, not requiring a driver stage to match a certain impedance characteristic of the present day mixers.

Figure 1.6: Advanced RF front end without LNA and based on MEMS devices.

Another approach to design a Radio Frequency (RF) architecture using MEMS devices is depicted in figure 1.6. By this new approach, the LNA amplifier is suppressed as expenses of the high-Q values with low insertion losses provided by the MEMS. Again, a band filter is necessary to solve the problem related with the image frequencies, that can be implemented by a bank of MEMS filters at high frequencies. Then, the signal follows a bank of narrow-band mixer-filter for the channel selection that feeds the subsequent electronics. In comparison to the front end architecture depicted in figures 1.3 and 1.5, the only active electronics operating at RF in this system are those associated with the LO, which uses a bank of micromechanical resonators, that can operate at 1 - 4mW. The architecture of figure 1.6 clearly presents enormous power advantages, eliminating completely the power consumption of the LNA and active mixer of figure 1.3, saving a total power of 40mW. However, the plausibility of this last front end scheme is subjected to implementing low insertion losses filter at high frequencies with high-Q factors.

## 1.3 MEMS fabrication technologies

In the 70's and early 80's, the incipient fabrication technology of MEMS devices was borrowed from the integrated circuitry (IC) industry. The batch-fabrication processing common in the IC industry, allowed to reduce costs as expenses of fabricating thousands of devices at the same time, thus significantly reducing the unitary cost.

Although many of the fabrication techniques and materials used to produce MEMS have been borrowed by the IC industry, the field of MEMS has also driven the development and

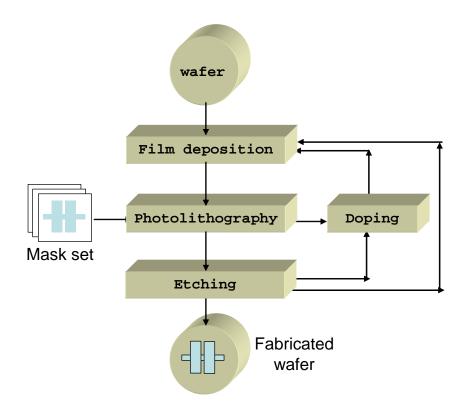

Figure 1.7: Flow diagram of IC fabrication technologies.

refinement of other microfabrication processes and materials like. For example, some relevant processes and new materials come from the hand of MEMS, like: anisotropic wet etching of single-crystal silicon, deep reactive-ion etching (Deep Reactive Ion Etching (DRIE)), X-ray, Atomic Force Microscopy (AFM) and Electron Beam Lithography (EBL) lithography as processes and piezoelectric films, magnetic films, Silicon Carbide (SiC), ceramics and polymers as new materials.

The fabrication of integrated circuits is based on four basic microfabrication techniques: deposition, patterning, doping and etching. The fabrication starts with the election of the wafer, typically single-crystal silicon is the standard substrate, and followed by iterative film deposition, patterning and etching processes, as shown in figure 1.7 [9].

The fabrication methodology to fabricate MEMS devices is derived from the scheme showed in figure 1.7. However, the necessity to release mechanical structures incorporates a new step in the overall process depicted previously for integrated circuitry fabrication. The film chosen to be the MEMS structure is named *structural material* whereas the film that has to be selectively etched in order to release the MEMS structure is named *sacrificial layer*.

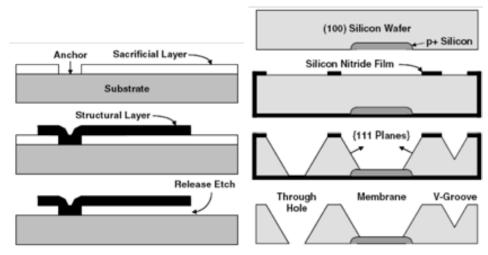

(a) Surface micromachining and the sacrifi- (b) Bulk micromachining along crystallocial layer technique graphic planes

Figure 1.8: Surface and bulk micromachining techniques.

The fabrication methodology for MEMS devices is classified into two large categories: surface micromachining and bulk micromachining. In the bulk micromachining, the substrate material, typically single-crystal silicon, is patterned and shaped to form an important functional component of the resulting device. On the other hand, in surface micromachining, the process fabrication follows an iteration of depositing, patterning and etching of a sequence of films. In this approach, the selective removing of the sacrificial layer is crucial. In figure 1.8 it is shown those two approaches used to fabricate MEMS.

In order to reduce the number of off-chip components required to operate in a sensing system, more and more building blocks are integrated together with the microresonator on the same chip. Then, to be able to produce systems-on-chip Systems On Chip (SoC) with integrated functions, the technology used to fabricate the microsensor must be merged with standard *IC* technologies, i.e., CMOS or bipolar process technology. The field in charge of integrating MEMS devices along CMOS processes is named CMOS-MEMS. The CMOS circuitry typically makes the role of amplification and conversion of the analog signal of the transducer to the digital domain [10].

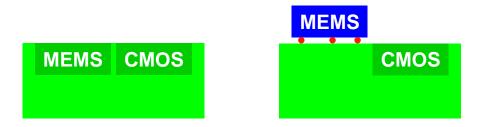

However, not all devices are fabricated by compatibilizing CMOS and MEMS fabrication processes. Figure 1.9 shows two different approaches for fabricating MEMS devices that need, for example a CMOS building block to implement conditioning signal performance. These two approaches are named CMOS-MEMS monolithic fabrication and CMOS-MEMS hybrid fabrication, respectively.

The monolithic CMOS-MEMS approach allows the highest integration density and shortest

Figure 1.9: Left: CMOS-MEMS monolithic fabrication; right: CMOS-MEMS hybrid fabrication approach.

electrical interconnections. This reduces parasitic loads and yields high operation speeds. Furthermore, process assembly steps are necessary. On the other hand, thermal budges and limitations due to the inherent integration will limit and conditione the design. As a example of the hybrid approach, a 14MHz oscillator based on a micromechanical resonator is the objective of this work [11]; in one chip the microresonator is fabricated whereas in the other chip a CMOS amplifier complements the design. Another similar work has been published more recently [12], also relating a fabrication of a MEMS-based oscillators.

As an example of the monolithic approach, a CMOS amplifier is integrated monolithically with the resonator [13], in order to build a gyroscope. The advantages of incorporating a design into a CMOS process are paid by the restrictions imposed by the layers technology. In that case, parasitic capacitances are reduced due to the proximity of the resonator with the circuitry and also the assembling (not the packaging) is easier. However, the standard technology will impose conditions that will limit the design of the resonator. Devices fabricated by the hybrid approach take advantage of the no imposed restrictions on the design step but then, the designer is forced to think about the assembly with the CMOS circuitry.

The CMOS-MEMS technological approaches can be divided into three different categories, depending when the micromachining module is fabricated with respect to the standard CMOS sequence [14].

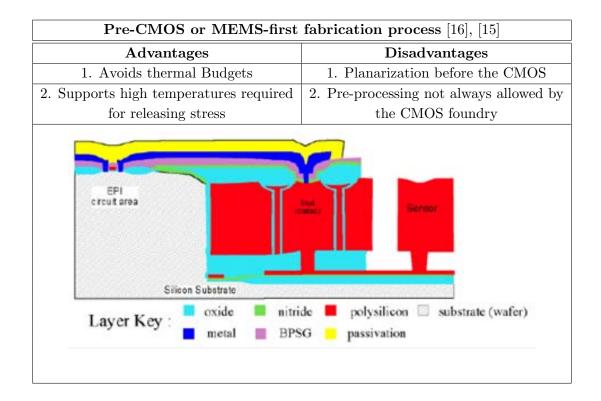

When the MEMS fabrication module precedes the standard CMOS, the CMOS-MEMS approach is named pre-CMOS. This approach, named also MEMS-first, avoids thermal budget constraints during the MEMS fabrication. Then, thermal annealing needed for thick polysilicon structural materials can be cointegrated with CMOS circuitry. Examples of polysilicon microstructures implemented in a pre-CMOS approach include the  $M^3EMS$  (modular, monolithic microelectromechanical systems) technology [15].

A recent work categorized in this approach is depicted in table 1.1 [16]. This new process module, called *Mod MEMS*, allows the integration of thick polysilicon structures (>  $6\mu m$ )

Table 1.1: Pre-CMOS or MEMS-first process fabrication.

annealed at  $1100^{\circ}C$  or higher temperatures for complete stress relief.

If the MEMS fabrication is performed in between the regular CMOS step, which is the most common case, is named intra-CMOS. This approach consists on inserting the micromachining process steps before the backend interconnect metalization, ensuring process compatibility with the polysilicon deposition and annealing.

An example of this approach was developed by Siemens and reported in [17], where is described the fully integration of a pressure sensor into a standard  $0.8\mu m$  analog BiCMOS process. One additional photolithography step and an etching step are necessary to achieve the micromachined structure whereas the sensor membrane is a 400nm polycrystalline silicon standard layer of the basic BiCMOS process. In table 1.2 is shown the cross section of the standard BiCMOS process within the integrated pressure sensor.

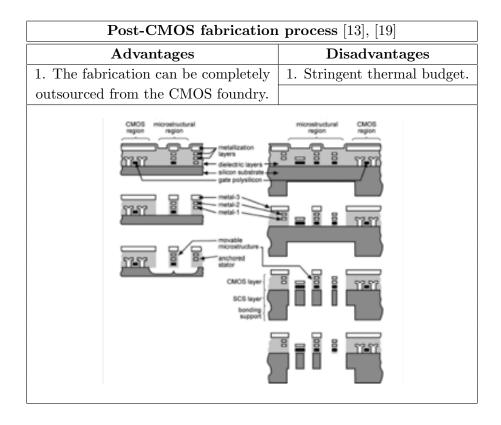

When the MEMS fabrication is completed after the CMOS fabrication, the approach is named post-CMOS. The main advantage in this case, is that the MEMS and CMOS fabrication processes can be performed in different foundries. However, this advantage is paid in terms of the thermal budget, that now is reduce down to  $450^{\circ}C$ , in order to prevent damaging on the aluminum metalization.

| Intra-CMOS fabrication process [17]                                          |                                                      |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Advantages                                                                   | Disadvantages                                        |  |  |

| 1. Process compatibility between 1. Anneal temp. limited to $900^{\circ}C$ . |                                                      |  |  |

| polysilicon deposition and anneal.                                           | 2. Polysilicon layer limited to few microns.         |  |  |

| oxide                                                                        | MOSFET sensor e boss air gap silicon membrane n-well |  |  |

Table 1.2: Intra-CMOS process fabrication.

Two general post-CMOS micromachining approaches can be distinguished: the microstructures are formed either by machining the CMOS layers themselves or by building the complete microstructures on top of the CMOS substrate. In the first approach, most of the microstructure is already created within the regular process sequence using the available standard layers. Then, the post-CMOS process module typically requires very few process steps, such as an etching step to release the microstructure. Building the complete MEMS on top of the CMOS substrate might require more process steps but can save valuable real estate, because the MEMS part can be build directly on top of the CMOS circuitry. However, the thermal budget is always limited below  $450^{\circ}C$ .

An interesting example of the first approach was developed and published by Prof. Fedder [13]. The MEMS structure is a sandwich of metals and inter-metal oxides that are patterned after the CMOS completion by DRIE techniques. A cross-section of the technology is depicted in table 1.3. The fabricated gyroscope has a noise floor of  $0.02^{\circ}/s/Hz^{1/2}$  at 5Hz. This technology also has been used to design a commercialized CMOS-MEMS microphone [18] and frequency selection elements in a RF transceiver [19].

In the second approach, the advances are focused on depositing at low temperatures the structural layer of the MEMS structure. Recent efforts have been done at Inter-universitary of Micro Electronics Centre (IMEC), in order to develop MEMS-structural and CMOS compatible layers in an above-CMOS technology [20]. Low tensile stress of hydrogenerated micro-

Table 1.3: Post-CMOS process fabrication where the microstructures are formed by machining the CMOS layers themselves.

crystalline silicon germanium ( $\mu cSiGe:H$ ) have been deposited on top of CMOS by Plasma Enhanced Chemical Vapor Deposition (PECVD) techniques at temperatures of  $300-400^{\circ}C$ , showing good mechanical and electrical properties.

In our research group at UAB [21], an effort to monolithically integrate MEMS based transducer along the CMOS circuitry has been performed in order to develop an ultrasensitive mass sensor. The integration approach has been developed, basically, in the framework of two research projects, Nanomass-II [22] and Nanosys [23]. In the Nanomass-II project, Si and SOI wafers were the starting point for the circuitry fabrication [24]. The structural layer for the resonator was a deposited polysilicon (for the Si wafer process) and the Single Crystal Silicon (SCS) (for the SOI wafer process) that was patterned after the circuitry finalization, by using different technological approaches, such as optical lithography, EBL [25] and by AFM-local [26] oxidation methodologies. The circuitry was based on a  $2.5\mu m$ -technology available at the Institut de Microelectrònica de Barcelona.

Following this research line, the *Nanosys* project envisaged the integration of multiple microresonators for frequency selection operation in future frontend transceivers in a standard and commercial CMOS technology. On that case, the post-CMOS process is designed just to

release the microresonators; the resonators are fabricated at the same time as the circuitry and only a maskless process will be necessary to remove the sacrificial layers and release the structures. Recently, a monolithically mass sensor has been fabricated by that CMOS compatibility, showing a mass sensitivity in the attogram/Hz range [27].

#### 1.4 Transduction in RF-MEMS

Microresonators exhibit typical mechanical resonant frequencies ranging from few kilohertz to Gigahertz, depending on their dimensions and resonance modes. Several techniques have been developed in order to excite the resonance state of such devices: electrostatic, thermal, electromagnetic, electromotive and piezoelectric; and different detection techniques have been developed in order to obtain experimental data concerning the dynamic state: capacitive, piezoresistive, inductive, optical and piezoelectric readout are the most common. Most of those techniques were first developed to excite and detect the resonance state of resonators used in sensor applications.

#### 1.4.1 General actuation and detection methods

The **Thermal actuation** technique uses the bimorph effect of a cantilever (as an example) with several layers each having a different thermal expansion coefficient. The cantilever is heated by placing a resistor on or near the cantilever. When a current is passed through this resistor, the temperature rises locally on the resonator and the material expands, bending the resonator due to stress. Resonant frequencies as high as 400kHz have been actuated and actuation frequencies in the MHz range are claimed to be possible, with cantilevers integrated on CMOS circuitry [28], [29].

The **Piezoelectric** technique utilizes the electromechanical coupling found in piezoelectric materials, such as single-crystalline quartz. The technique is to sandwich a piezoelectric material between two metal contacts, which is then placed on a silicon resonator. By again applying an alternating voltage across the piezoelectric material, one can actuate the resonator. The drawbacks of this technique are that most piezoelectric materials are not CMOS compatible.

The Magnetomotive actuation is done by applying a static magnetic field perpendicular to a beam structure and alternating an AC current through the beam. The Lorenz forces acting on the electrons will drive the resonator. The disadvantages are that in order to achieve a large actuation force, large magnetic fields need to be applied. This technique or similar techniques has been demonstrated in other works [30].

In the **Magnetic actuation** the cantilever is a magnetic material and an oscillating magnetic field is applied parallel to the vibration of the cantilever. The magnetic field induces a force on the cantilever. Several examples of this actuation method have been demonstrated [31],

[32]. The main problem with this method is the need for a magnetic material on the cantilever and the aligning of the magnetic field to the cantilever.

The most common detections methods are described hereby:

The **Piezoresistive readout** is a readout technique widely used since both single-crystal Si and poly-Si are good piezoresistive materials at the right doping level [33], [34]. The idea is that when the resonator bends, the resistance of the piezoresistor changes due to the stress in the material. Thus, one could detect the bending of a cantilever by simply measuring the resistance of the piezoresistor. A drawback for this detection method is that one needs to have a circuit on the actual resonator structure. This limits the minimum size of the resonator in the case of the cantilever, because one needs two contacts to the cantilever. Piezoresistive readout has been demonstrated for Si based AFM cantilevers [35], [36].

The **Optical detection** is based on the reflection of a laser beam on the cantilever and onto a position sensitive photo diode. When the cantilever bends, the movement is registered by the photo diode. This method is used in most AFM microscopes. However, since the typical laser spot diameter is approximately  $10\mu m$ , the minimal size of the mechanical device is limited. Another disadvantage is that this type of detection method requires a laser and photo diode, which takes up lots of space, and is not compatible with some possible applications.

#### 1.4.2 Capacitive transduction

Present MEMS components in transceiver architectures are based on two of the previous described approaches, piezoelectric resonant structures electrostatically excited and mechanical vibrating structures electrostatically driven and capacitively transduced. Each group of devices present some advantages and drawbacks that makes impossible to decide which are the best, so the final application will decide which is the most suitable in each case.

The main advantages of choosing Film Bulk Acoustic Resonator (FBAR) devices in front of mechanical microresonators capacitive transduced:

- The design, operability and implementation in the range of frequencies above 1GHz.

- The power management of such devices, leading to a low series resistances, mismatchable along the circuitry in the RF design.

However, the election of FBAR resonators presents some drawbacks:

- The piezoelectric material deposition is not CMOS compatible. This makes more difficult the fabrication process of the resonator even if the FBAR is fabricated in a different chip.

- The thickness of the piezoelectric material determines the frequency of operation, yielding to only one frequency per chip. Furthermore, the non-uniformity of piezoelectric

material thickness leads to variability on the resonance frequency. Some works have been focused on solving this restriction, for example, it has been suggested to use the piezoelectric lateral mode  $(d_{31})$  instead of the vertical mode  $(d_{33})$ .

• The capacitive transduced resonators can be easily switched off by removing the DC voltage applied. This is very useful when designing a bank of filters. However, for FBAR an additional switch is needed.

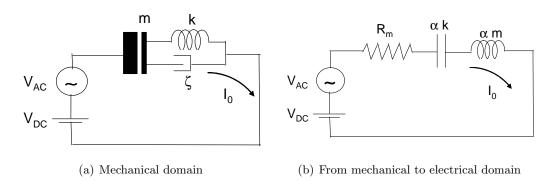

Due to the CMOS compatibility, and the possibility of integrating such devices in a CMOS commercial technology, the devices developed on this thesis are focused on capacitive transduced microresonators. In this microresonators, the excitation is done by an alternate voltage applied to a structure called excitation electrode and the signal detection is done by transducing the change on the capacitive due to the resonance mode in the read-out driver, as shows figure 1.10. A DC signal has to be applied to the resonator electrode in order to convert the capacitance change on electrical current.

The total capacitive current can be written as:

Figure 1.10: Equivalent electrical circuit for a resonator, showing the mechanical magnitudes, effective mass, spring constant and damping coefficient, and their conversion to a pure electrical domain: motional resistance, capacitance and inductive elements.

$$I_O = V_{DC} \frac{\partial C}{\partial t} + C \frac{\partial V}{\partial t} \simeq V_{DC} \frac{\partial C}{\partial t} + C \frac{\partial v_{ac}}{\partial t}$$

(1.1)

where C is the capacitance between resonator and electrode.

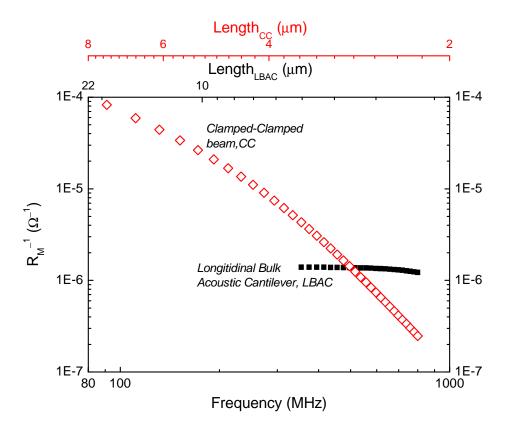

Electrostatic actuated and capacitive transduced MEMS resonators have been demonstrated up to GHz range frequencies exhibiting quality factors above 10.000 [37]. However, achieving good enough signal coupling becomes increasingly difficult as increasing the target frequency. The motional resistance is an equivalent electrical parameter related inversely proportional to the output current produced by the mechanical movement of the structure at resonance. This parameter will allow the reader to get in touch for the first time in the most relevant parameters related with the capacitive transduced MEMS.

$$R_{mot} = \frac{v_{ac}}{I_o} \simeq \frac{k_r}{\omega_0 V_{DC}^2} \frac{d_0^4}{\epsilon A^2} \frac{1}{Q}$$

(1.2)

where  $k_r$  is the equivalent elastic constant of the resonator at the modal frequency  $\omega_0$ .  $V_{DC}$  is the DC voltage applied to the resonator and d is the gap distance between the readout electrode and the resonator.  $\epsilon$  is the gap material permittivity and can be expressed as  $\epsilon = \epsilon_0 \times \epsilon_r$ , where subindex 0 and r refer to the value in air (or in vacuum) and to the relative permittivity of the medium, respectively. As it will be explained in future chapters, a way to increase the read-out current is fabricate these devices with a solid high permittivity transducer gap. A is the coupling area between resonator and electrode. This factor is closely related with the reduced electrical transduction that occurs when dimensions are reduced for increasing the frequency.

And finally, the parameter Q represents the mechanical quality factor of the structure. This dimensionless parameter models the losses in a resonating system. The definition can be written as:

$$Q = 2\pi \frac{Energy \quad stored \quad per \quad cycle}{Energy \quad dissipated \quad per \quad cycle}$$

(1.3)

The quality factor can be written also in terms of the damping coefficient  $(\xi)$ ,  $Q = \frac{1}{2\xi}$ . When the resonator in immersed in a fluid, the sources of damping are related directly to the friction with the fluid [38], [39]. The friction with the surrounding fluid represents two terms on the total damping. The first contribution is due to the friction of the resonator movement with the fluid whereas the second term is a consequence of the capacitive transduction as expenses of the proximity of the read-out electrode. However, when the resonator is in a low pressure ambient, losses are then due, basically, to the acoustic vibrations transmitted through the anchor structure supporting the resonator [38], the surface effects in thin resonators [40] and the thermoelastic damping inherent to the structure [41].

In general, the Q factor can be expressed as:

$$\frac{1}{Q_{Total}} = \frac{1}{Q_{Air-Damping}} + \frac{1}{Q_{Air-Squeezing}} + \frac{1}{Q_{Anchor}} + \frac{1}{Q_{surface}} + \frac{1}{Q_{TED}} \tag{1.4}$$

In air, the Q-factor is limited by the air damping and squeezing. In vacuum, the main losses are due to the anchoring, surface effects and in minor importance, thermoelastic losses.

In order to integrate MEMS devices along circuitry in RF frontend receivers, an equivalent  $50\Omega$ -motional resistance is often desired and pursued. Then, the maximum quality factor (Q), together with the coupling area (A), the gap distance (d), the applied voltage ( $V_{DC}$ ) and the gap spacer permittivity are the design parameters in order to achieve that goal.

#### 1.5 Objectives, challenges and outline of the thesis chapters

This phd thesis is defined in the framework of the Nanosys project, which main purpose is the monolithically fabrication of a MEMS-based oscillator operating at 1GHz.

Then, the main objective of this thesis is the monolithic fabrication of RF microresonators in a commercial technology using available standard layers of the technology. The conception of the post-CMOS process is a maskless process in order to release the resonators.

This main objective presents some challenges from the design point of view, due to the lack of knowledge of the technological process. The MEMS designer only has the electrical datasheets of the technology, and the information regarding the mechanical properties of the structural layers and how the process is being carried out is not provided by the foundry, and has to be deduced from run to run. Then, different approaches will be defined starting from the crossection of the technology and one of the aims is to conclude which of the technological approaches is the best option and which are the real limits for fabricating MEMS resonators using this technology.

This limitation of information together with the limitation in costs and in time, condition the development and the achievement of the main goal of the project.

Secondary objectives that have been pursued during the achievement of this phd thesis are:

- 1. Electromechanical modelization. From the circuitry design point of view, it is desired to predict the current levels that will be produced by the resonator. Then, an electrical equivalent model of the resonator will be developed. Furthermore, resonance modes for different vibrating structures will be presented, in order to have a library of resonators to match the target frequencies.

- 2. Hybrid fabrication. In addition to monolithic integrated resonators, two technological process sequences independent of the CMOS circuitry will be implemented in order to study resonators fabricated in single crystal silicon and to study the transduction by a solid dielectric gap resonator.

The thesis is divided into six chapters. The first chapter gives an introduction to the microresonators electrostatic excited and capacitive transduced, depicting their frequency selection functions in present superheterodyne transceiver architectures. Furthermore, a state of the art for CMOS-MEMS technologies will be presented.

The second chapter is focused in the design and modelization of the vibrating structures in order to accomplish the target frequency as well as predicting the resonance current levels crucial for the CMOS circuitry design.

The third and fourth chapters are dedicated to the MEMS fabrication. In the third chapter the microresonators are fabricated by the hybrid approach; two different technological

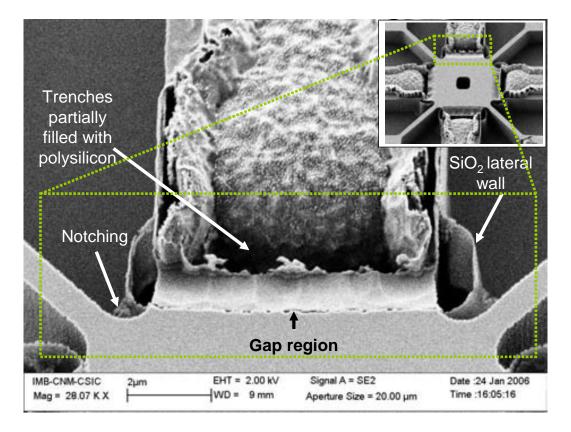

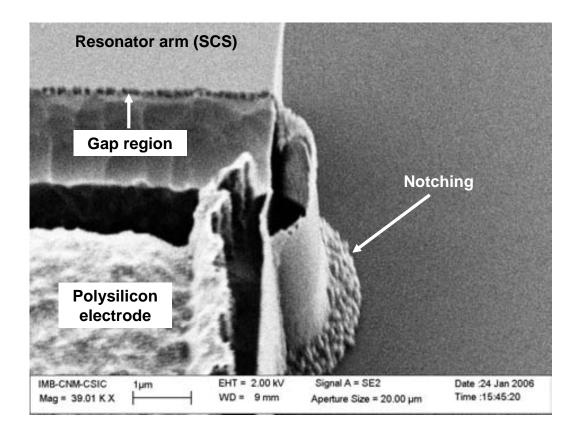

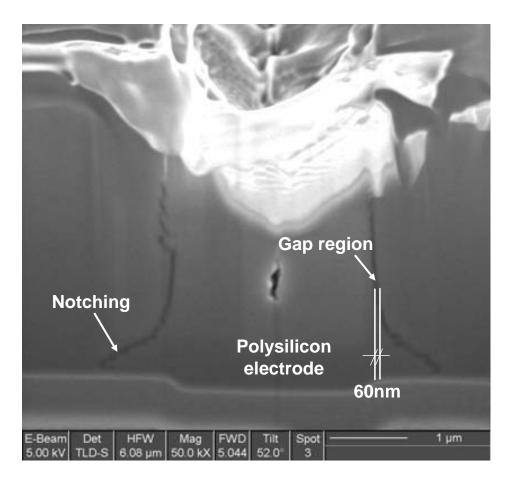

processes will be presented: the first one is focused on fabricating resonators in SCS with gaps smaller than 100nm; the second hybrid approach has as main characteristic to study the transduction by a solid dielectric gap.

In chapter 4 different alternatives are discussed in order to fabricate monolithically RF microresonators using the standard layers available in the Austria Micro Systems (AMS)-0.35 $\mu m$  technology.

In chapter 5 and 6, the electrical as well as the structural characterization of the resonators fabricated by the previous technological processes will be described. The experimental results are divided regarding the intrinsic frequency of the devices; then, in chapter 5 will be described the resonators with resonating frequencies in the VHF (10MHz) up to 300MHz range, and in chapter 6 the resonators showing resonance frequencies in the UHF (from 300MHz up to 1GHz) range.

### Resonator Electromechanical modeling

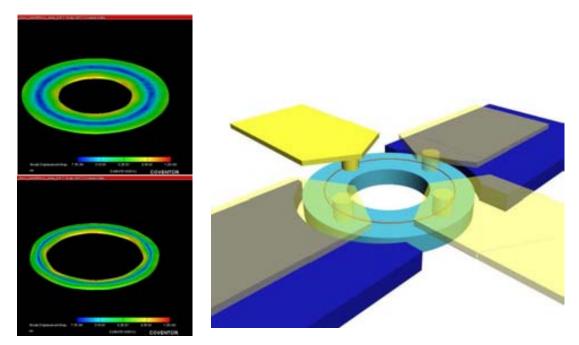

In this chapter an electromechanical model of the capacitive readout system, electrostatically excited, has been described and implemented. The model was firstly conceived to modelize a cantilever-driver system for mass sensing [42], and afterwards was used to modelize a clamped-clamped beam. The chapter starts with the description of the electromechanical model and its implementation in *Matlab* [43] and *Spice* [44]. The extension of this model to bulk acoustic resonators is of immediate application. For all resonators devices designed along this phd thesis, a set of equations relating resonance frequency and effective mass in the proposed vibrational modes is done. In some cases, those design equations have been complemented with Finite Element Method (FEM) solver simulations in order to corroborate the analytically calculated data.

#### 2.1 The electromechanical model

In the design phase of a microresonator it is very important to predict approximately output current levels, as well as maximum DC voltages that can be applied without collapsing the structure and resonance frequencies for the different vibrational modes.

In that sense, FEM tools (ANSYS [45], Coventor [46]), give to the designer the possibility to simulate and predict accurately resonance frequencies, and hence extract effective mass and spring constants. This is really helpful when designing structures that do not have analytical equations for resonance frequency, elastic constant and effective mass, for example when designing an elliptical-shaped microresonator. However, this programs tends to fail when performing transient analysis or if not, they are time consuming. For this reason it is highly recommended to have an approximated model but non-time consuming and easily reconfigurable.

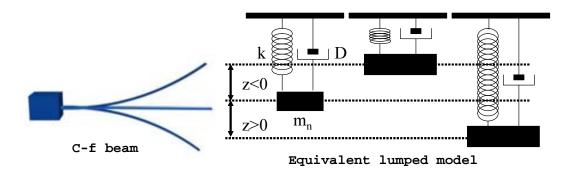

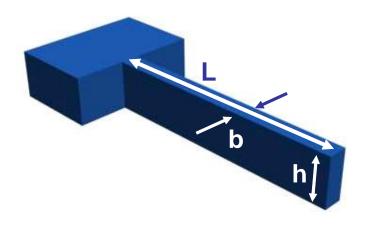

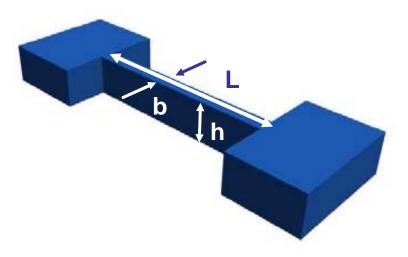

Figure 2.1: Clamped-Free beam modelized by the lumped model approximation. The static mass of the system  $m_0$  is modelized by  $m_n$ , taking into account the n vibrational mode.

The model here depicted is based on a lumped model but taking into account the real deflection for flexural microresonators, like clamped-free beams and clamped-clamped beams. For bulk acoustic resonators, with inherent lower displacements at resonance a simplification of the model is done.

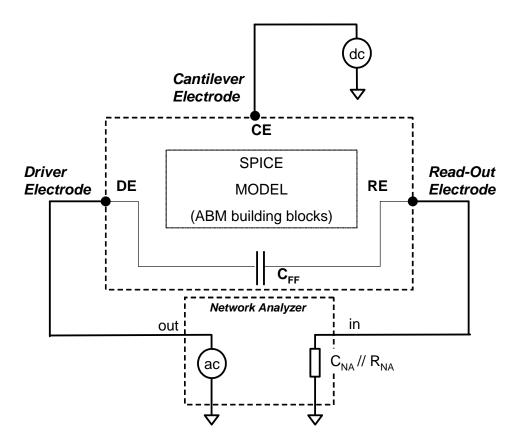

Two different versions of the model have been carried out; the first version is based on the implementation of the equation of movement in *Matlab*, which allows calculation of the current levels around resonance as well as frequency calculation, effective mass and spring constant. However, the limitation of the model arises when demanding electrical parameter such as transmission power and equivalents. For that reason, the same model has been done in a pure electrical environment *Spice* with the same functionalities. In addition to that, and due to the inherent conditions of an electrical environment, the model allows to simulate directly the transmission curves of the microresonator adding electrical impedances and circuitry elements.

This tool is very important for predicting the behavior of the transducer along with the CMOS circuitry. Then, the CMOS designer has a simulation tool to predict accurately microresonators output levels in order to evaluate (previous to fabrication), the CMOS circuitry performance in a preliminary design phase.

The start point of the model is the second degree equation of movement 2.1, which has implicit the lumped model approximation. Under this approximation, the resonator system is described under one variable with an effective mass  $(m_n)$  that accounts for the movement of the whole resonator in terms of the maximum displacement point. For a clamped-free beam, the maximum displacement point is the free end of the structure, whereas for a clamped-clamped beam that point is the middle of the structure. The equation of movement is described in terms of the variable z, which represents the movement of the maximum dis-

placement point.

This lumped mass model approximation is depicted in figure 2.1. The system, in that case a resonating clamped-free beam of static mass  $m_0$  is modelized via a lumped model approximation. The parameter that takes into account the pondered movement of the whole beam in the one-variable time dependent (z) is the effective mass.

$$m_n \cdot \frac{d^2 z}{dt^2} + D \cdot \frac{dz}{dt} + k \cdot z = F_{ext}(t, z)$$

(2.1)

which is derived from the system hamiltonian, H:

$$H = \frac{p^2}{2 \cdot m_n} + \frac{k \cdot z^2}{2} + \int \frac{D}{m_n} \cdot p \cdot dz + W_{ext}$$

(2.2)

by the second Newton's law:

$$m_n \cdot \frac{d^2 z}{dt^2} = -\nabla \cdot H \tag{2.3}$$

The first term in equation 2.1 is the inertial force of the system.  $m_n$  is the effective mass of the system at the vibrational mode n, taking into account the movement carried out by the whole resonator. The second term is due to losses of the system. D is the damping factor which is related with the quality factor Q by:

$$D = \frac{\omega_n \cdot m_n}{Q} \tag{2.4}$$

where  $\omega_n$  is the resonance frequency in rad/s of the n-vibrational mode. Typically, operating in a fluid, the system loses are mainly associated to the friction with the fluid. However, when operating in vacuum, losses are due to other sources of dissipation, like anchor losses  $(Q_{anchor})$ , surface effects  $(Q_{surface})$  and intrinsic thermo-elastic loses  $(Q_{TED})$ . So, in general, the quality factor can be written as:

$$\frac{1}{Q_{Total}} = \frac{1}{Q_{Air-Damping}} + \frac{1}{Q_{Air-Squeezing}} + \frac{1}{Q_{Anchor}} + \frac{1}{Q_{surface}} + \frac{1}{Q_{TED}}$$

(2.5)

In the following section 2.9 it will be described in more detail the mechanisms of dissipation as well as analytical equations in order to predict approximately those values, which are an input parameter in the modelization and simulation process.

The third term in equation 2.1 is due to the recovering force on the system that tries to force the position of the system to its equilibrium. In general, this term is kz where k is the equivalent elastic constant of the system and z is the displacement. For large displacements it has to be taken into account non-linear terms that appear in the equation of movement 2.1. For example, in clamped-clamped beams some non-linearities are observed when deflections

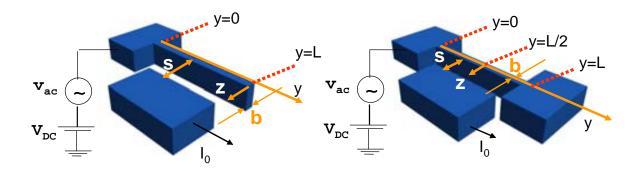

Figure 2.2: c-f (left) and c-c (right) resonators in one port configuration. For the c-f resonator, the maximum displacement is produced at the free end (z = L); for the c-c beam, the maximum displacement is obtained at Z = L/2. b and s are the beam width and lateral gap distance, respectively.

are bigger than 0.02L (where L is the length). On those cases the non-linear term is expressed as  $k_3z^3$ , where  $k_3$  is the non-linear elastic term [47].

In electrostatic excited MEMS microresonators, the external force on equation 2.1 is due to alternate electric field applied to the driver electrode ( $F_{ext}$ ). In general this electrostatic force is written as:

$$F_{ext} = \frac{1}{2}V^2(t)\frac{\partial C}{\partial z} \tag{2.6}$$

where C is the capacitance between the resonator and the driver electrode.  $V\left(t\right)$  is the voltage applied between driver electrode and resonator, with AC and DC components:

$$V(t) = V_{DC} + v_{ac} \cdot \sin \omega_{ext} \tag{2.7}$$

where  $v_{ac}$  is the amplitude of the AC applied voltage.

For flexural resonators, characterized with large oscillation amplitudes, the dependence of the displacement on the capacitance can not be neglected. Then, the capacitance is function of the displacement: C(z,t). Let's consider the direction along the microresonator as y, as shows figure 2.2. Then the capacitance is the integral of the deflection profile along the beam length (L):

$$C(z(t)) = \frac{C_0}{L} \int_0^L s \frac{dy}{\left(1 - \frac{z(y)}{s}\right)}$$

(2.8)

where  $C_0$  is the static capacitance between resonator and driver:

$$C_0 = \frac{\epsilon_0 \cdot h \cdot L}{s} \tag{2.9}$$

Figure 2.3: The figure shows how the resonator (a c-f beam in this case) is sliced into 10 elements. The total capacitance between resonator and driver is the sum of the capacitance of each element.

Because the profile displacement z(y) depends on the external force, and the external force depends on the displacement profile, the profile is determined numerically by a FEM solver in static conditions. The FEM solver allows to calculate by static modelization the displacements along the direction y of the resonator. This has been done by Coventor and/or Sugar. A model of the transducer has to be designed in this FEM tools slicing the beam length L in finite lengths  $l_i$ . Each sliced element i is displaced a quantity  $z_i$  when applying an external force. In the FEM tool, a set of voltages are simulated, obtaining a matrix of displacements  $z_i$  versus z. Then, when solving equation 2.1 by numerical methods (Matlab, Spice or others), the matrix of containing  $z_i$  values is invoked.

Then, the total capacitance between driver and electrode is calculated as the addition of each sliced beam i, supposing N sliced elements. Displacements  $z_i$  are obtained from the FEM solver. The length of sliced elements,  $l_i$ , can be logarithmic in order to describe better the free end without increasing N too much. In case the spacing is linear,  $l_i = \frac{L}{N}$ .

Equation 2.8 can be rewritten as, substituting the integral by the sum of each capacitance to the total beam capacitance:

$$C(z(t)) = \frac{C_0}{L} \sum_{i}^{N} \left( \frac{l_i}{\left(1 - \frac{z_i}{s}\right)} \right)$$

(2.10)

The external force can be rewritten as:

$$F_{ext}(z(t),t) = \left(\frac{V^2(t)}{2} \frac{C_0}{L \cdot s}\right) \left(\sum_{i}^{N} \left(\frac{l_i \cdot z_i}{\left(1 - \frac{z_i}{s}\right)^2}\right)\right)$$

(2.11)

When computing equation 2.1, the set of displacements previously calculated by a FEM tool are used to compute the total capacitance, and hence the total force for each time of the transient analysis. Those lateral displacements are obtained from previous calculation on a FEM solver platform, named Sugar [48]. Those displacements were corroborated by another FEM solver, Coventor [46] It shall be pointed that the matrix of values  $z_i$  is invoked by the value of the variable z(t) at each time t of the simulation. So for each value of z corresponds a vector of displacements  $z_i$ . In fact the nodal displacement of each sliced element can be expressed as a function of the maximum displacement z as:

$$z_i = b_i \cdot z \qquad \forall \qquad i = 1 \dots N \tag{2.12}$$

Equations 2.10 and 2.11 are complemented by the fringing field contribution on the capacitance between resonator and electrode. Due to the proximity of the resonator with respect to the electrode, the static capacitance is enhanced due to the fringing fields that appears between both structures. The fringing field correction is modelized by an analytical equation which depends only on the cantilever driver geometry. That term is inspired from a semiempirical formulation developed to determine the fringing field contribution to adjacent lines in a CMOS circuitry [49]. Then, the total electrostatic force applied to the cantilever can be written as:

$$C_{0-ff} = C_0 \times \left(1 + \alpha \left(\frac{s}{h}\right) \left(\frac{b}{s}\right)^{0.222}\right) \tag{2.13}$$

Replacing  $C_0$  for  $C_{0-ff}$  in equations 2.10 and 2.11, allows the consideration of the fringing capacitance on the modelization. Then, the term of the external forces  $F_{ext}$  takes into account the two main features previously presented: the cantilever real deflection shape and the fringing field correction. Focusing in the real deflection consideration, the model calculates the external electrical force applied to the resonator by slicing the resonator length in N components and computing the time-variable capacitance of each sliced element.

The output electrical current is also calculated when solving numerically equation 2.1. The output current is given by the equation:

$$I_0(t) = \frac{d(C \cdot V)}{dt} = V(t) \frac{\partial C(z(t))}{\partial z} \frac{dz}{dt} + C_0 \frac{dV(t)}{dt}$$

(2.14)

where the first term takes into account the resonance current due to the movement of the resonator at resonance; the second terms takes into account the parasitic current between excitation electrode (in one-port measurement -as described in appendix B- this electrode is the resonator itself) and the readout electrode. The capacitance  $C_0$  is the static capacitance between both electrodes. In two-port measurements (see appendix B), parasitic capacitance between resonator and readout electrode is reduced, lowering the specific weight of the parasitic current in the overall current.

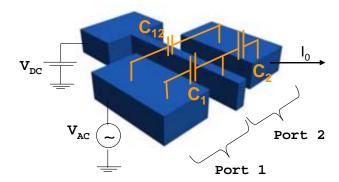

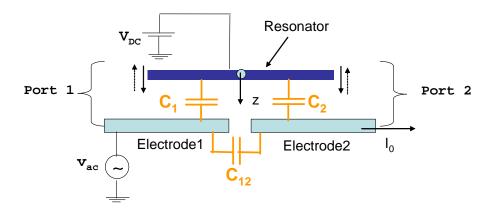

#### 2.1.1 Two-port modelization

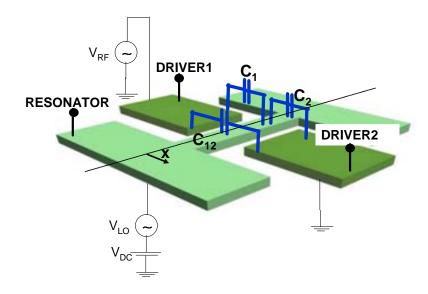

Figure 2.4 shows a c-f resonator in a two port configuration scheme. The benefits of using a two port configuration is that the effect of the parasitic current (generated as a consequence of applying an AC voltage to driving the structure to resonance) is minimized in the output resonator current. In that case, the AC and DC voltages are applied separately in the driver electrode and resonator, respectively. The output current is collected at the readout electrode, as shows figure 2.4.

The consequences in the modelization are that the external force has two contributions, one force term for each driver, named  $F_{ext_1}$  and  $F_{ext_2}$ , that appear due to the differences of voltages between excitation driver and resonator  $(V_1(t))$  and between resonator and detection electrode  $(V_2(t))$ .

$$F_{ext_{1}^{2}}(z(t),t) = \left(\frac{V_{1}^{2}(t)}{2}\right)^{2} \frac{\partial C_{2}}{\partial z} =$$

$$= \mp \left(\frac{V_{1}^{2}(t)}{2}\right)^{2} \left(\frac{C_{0-ff}}{s} \cdot \left(\sum_{i}^{N} \left(\frac{l_{i} \cdot z_{i}}{\left(1 \pm \frac{z_{i}}{s}\right)^{2}}\right)\right)\right)$$

(2.15)

$l_i$  and  $b_i$  are the length and the normalized lateral displacement (on the lateral direction, z) of the sliced element i, respectively.

The voltages of each port, taking the configuration of figure 2.4, can be written as:

$$V_1(t) = V_{DC} + v_{AC} \sin(\omega_{ext}t)$$

$$V_2(t) = V_{DC}$$

(2.16)

The output current is the sum of the resonance current and the parasitic current, very similar to expression 2.14. The only difference is that now, the parasitic capacitance from AC input signal to output current signal is given by the fringing capacitance between excitation and readout drivers  $(C_{12})$ , as depicted in figure 2.4.

Figure 2.4: Scheme showing a c-f beam resonator in the two port configuration. Voltages and capacitances related with each port are named  $C_1$ ,  $V_1$  and  $V_2$  and  $C_2$ .

$$I_{0}(t) = \frac{d(C \cdot V)}{dt} = V(t) \frac{\partial C(z(t))}{\partial z} \frac{dz}{dt} + C_{12} \frac{dV(t)}{dt}$$

(2.17)

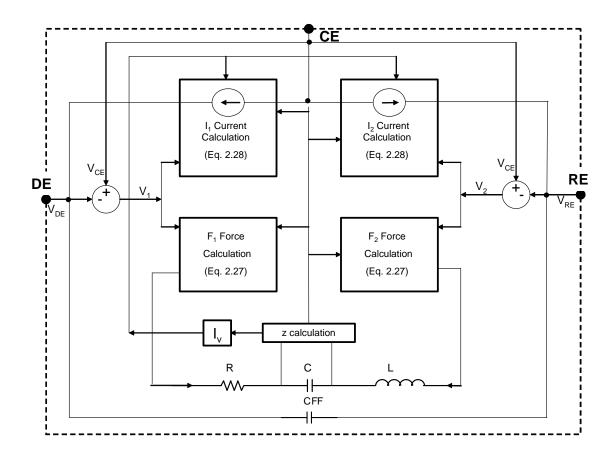

### 2.1.2 Implementation in Pspice

The implementation of the previous described model in an electrical environment opens new and interesting possibilities from the modelization point of view. Despite the implementation of the model in *Matlab* platform favors a fast and dynamic implementation of the model due pre-designed functions focused on numerical methods, some difficulties arise when electrical elements are added to the transducer. An electrical environment facilitates the addition of such devices into the simulation panel as well as allows to work easily with electrical variables, as transmission magnitude and phase.

However, in order to translate the modelization to an electrical environment the following conversion from mechanical to electrical variables is needed:

$$F_{ext} \xrightarrow{T} U_{ext} = \frac{F_{ext}}{T} \qquad z \xrightarrow{\dot{T}} I_v = T \cdot \dot{z}$$

(2.18)

where the external force  $(F_{ext})$  has been transformed to an external voltage in the new domain  $(U_{ext})$ , and the velocity  $(\dot{z})$  has been transformed to an equivalent current  $(I_v)$ . The factor which defines the transformation between the two domains is given by the equation:

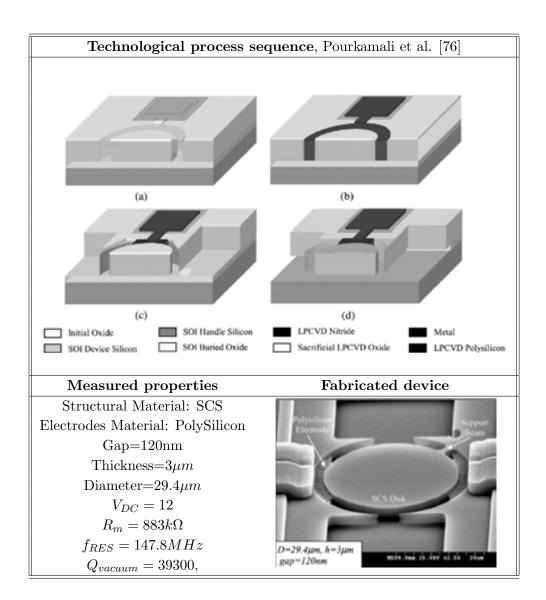

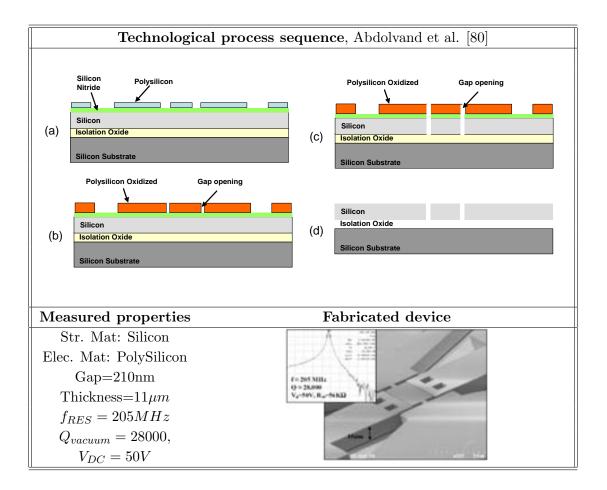

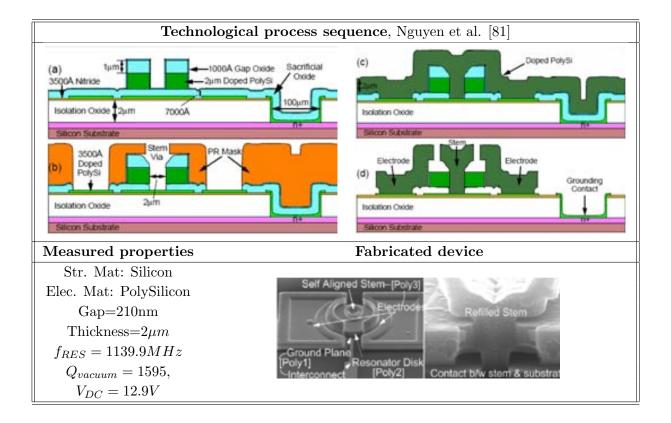

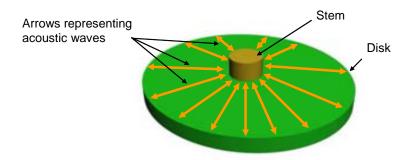

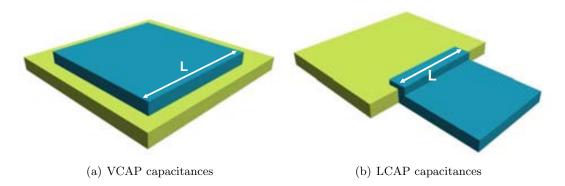

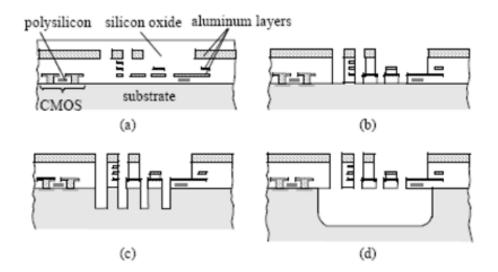

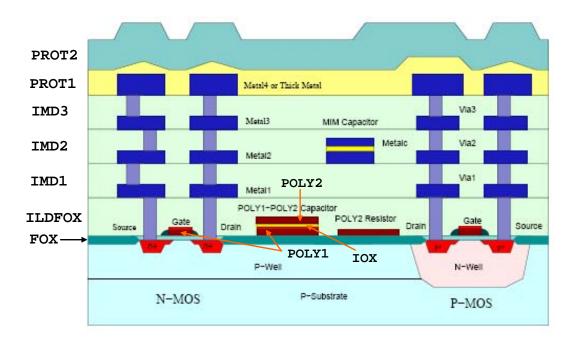

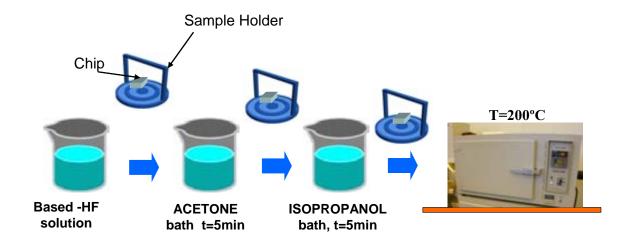

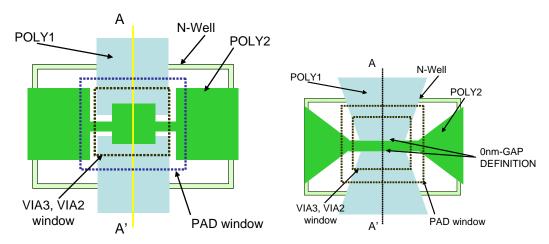

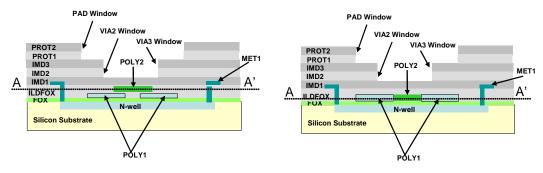

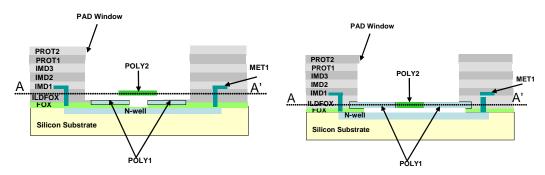

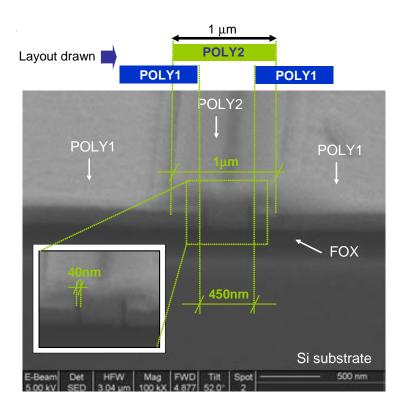

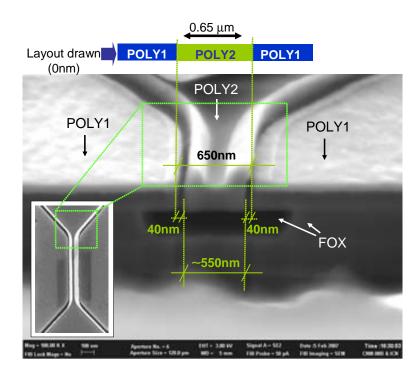

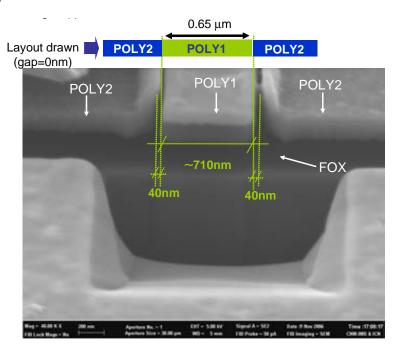

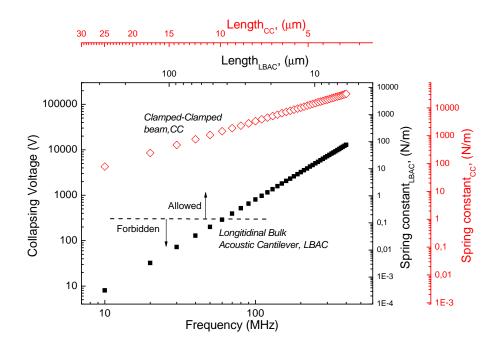

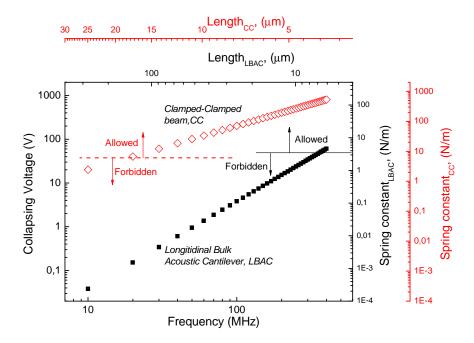

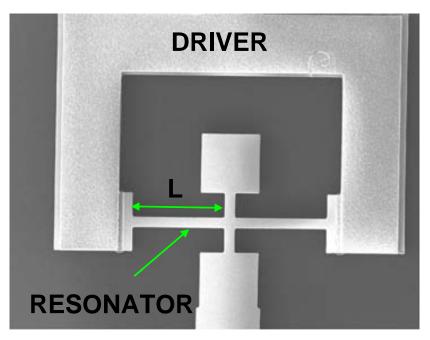

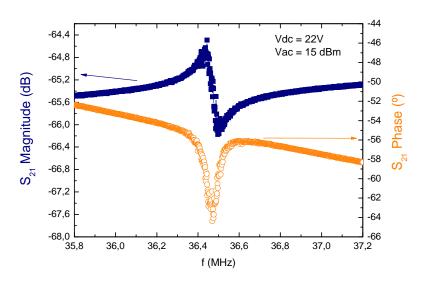

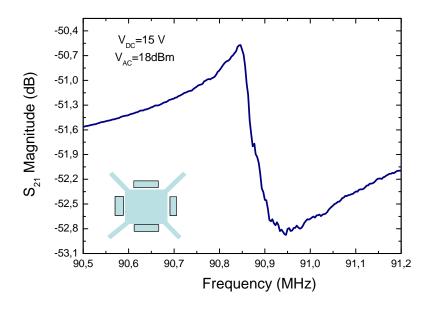

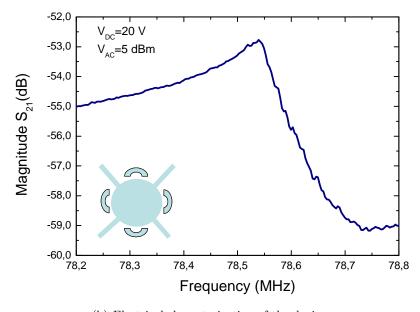

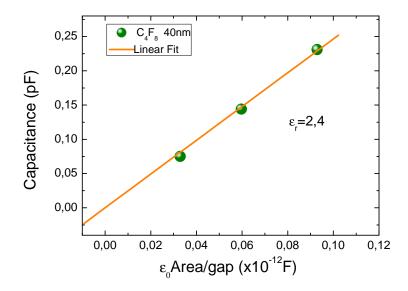

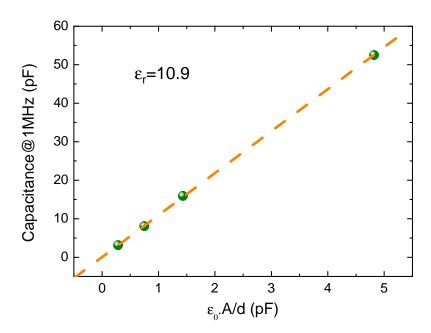

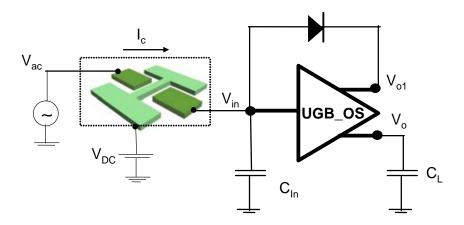

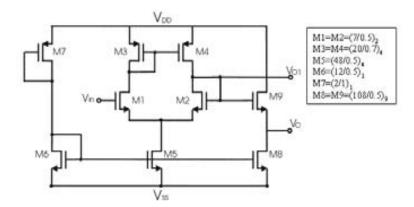

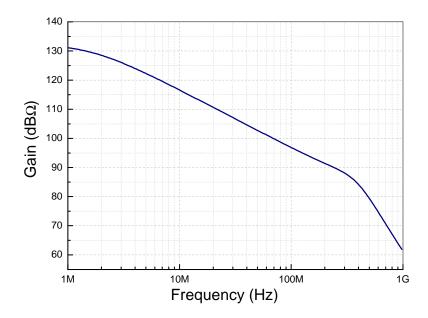

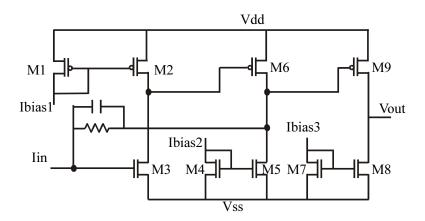

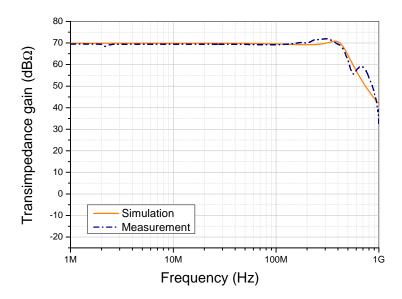

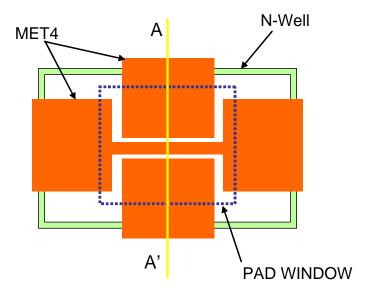

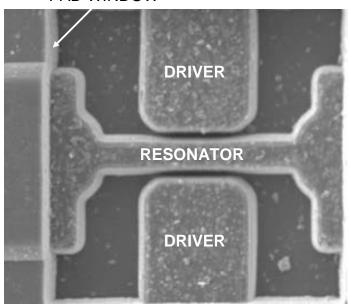

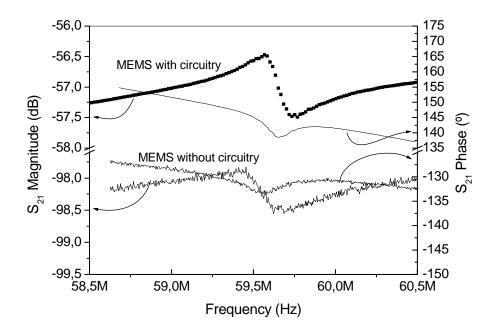

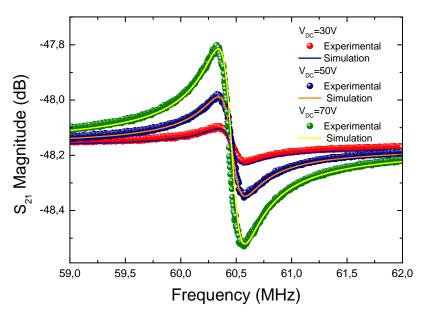

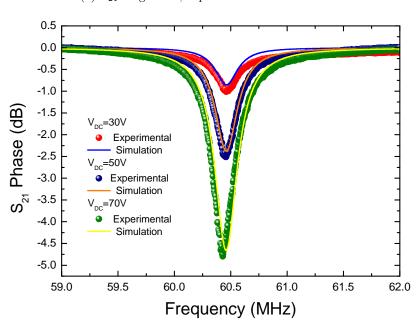

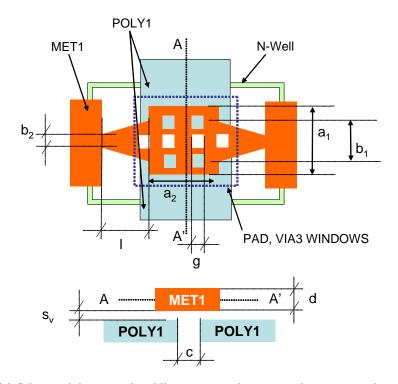

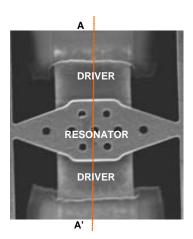

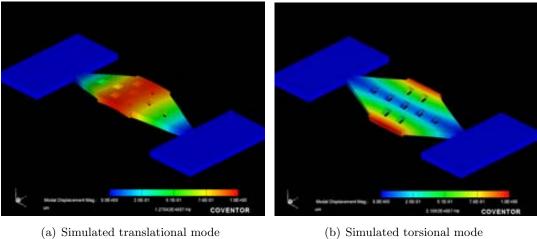

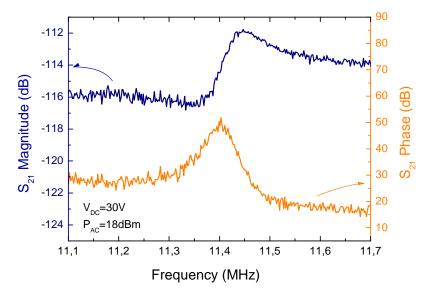

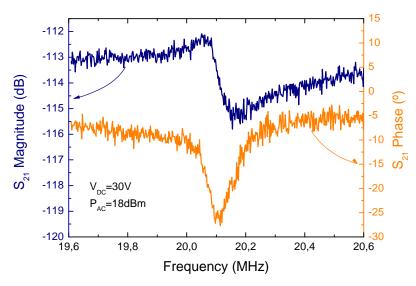

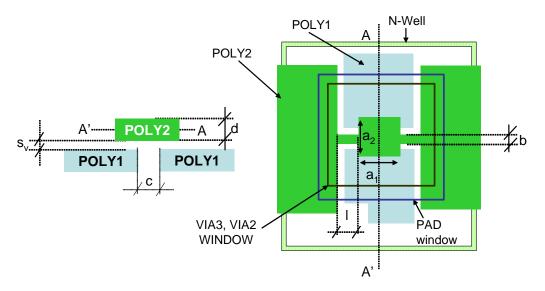

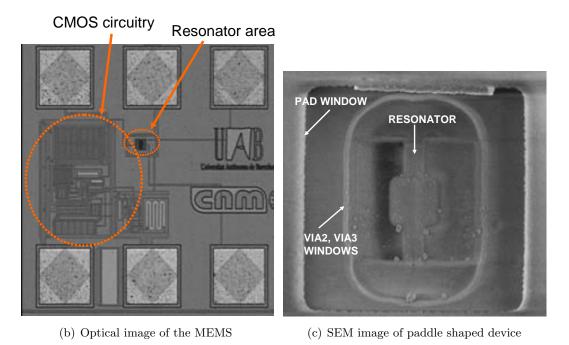

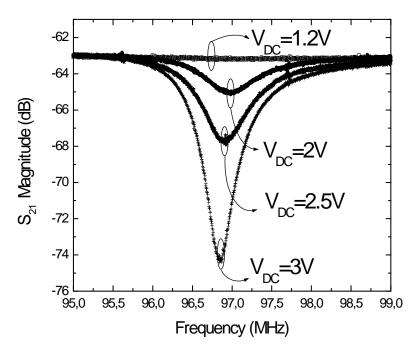

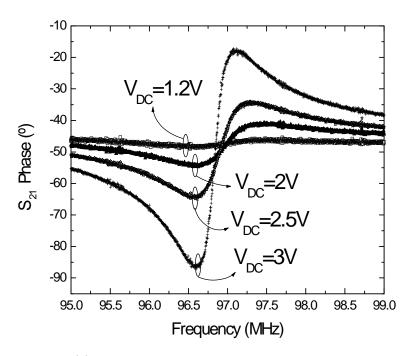

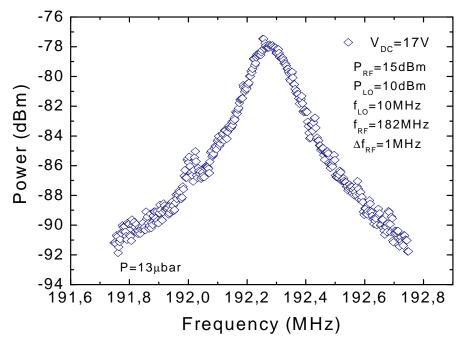

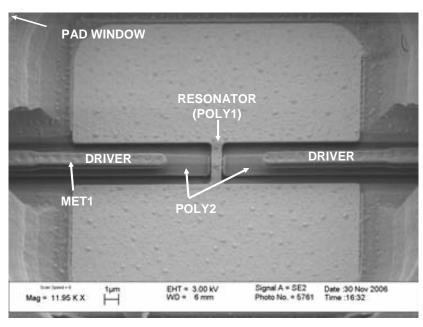

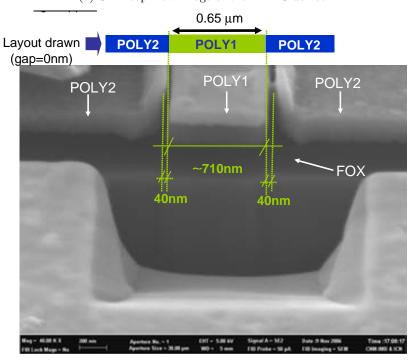

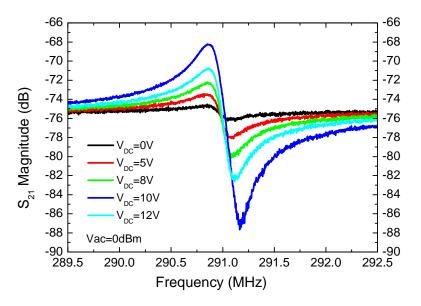

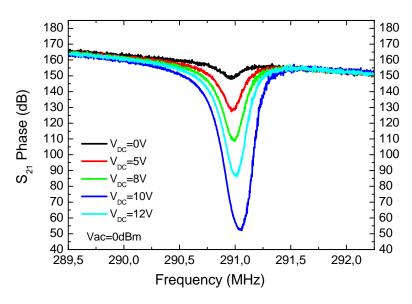

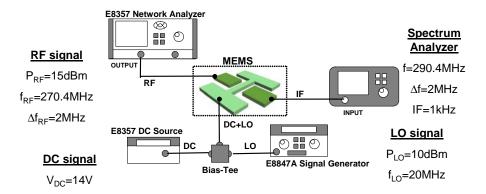

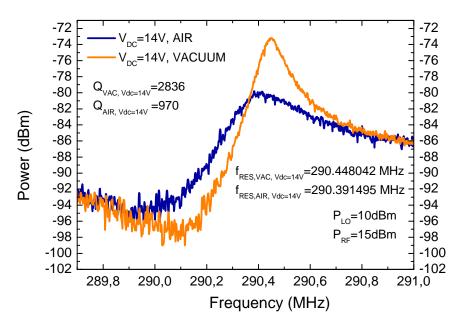

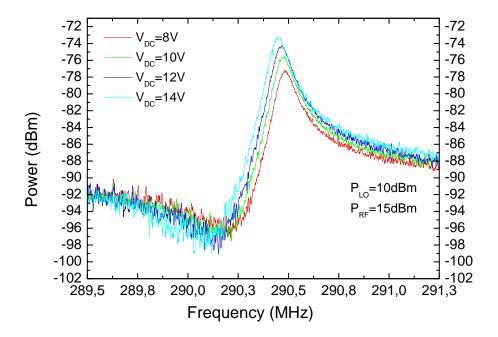

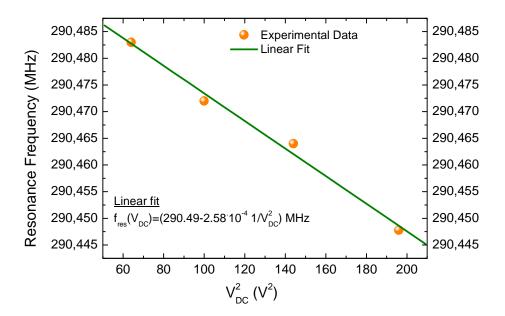

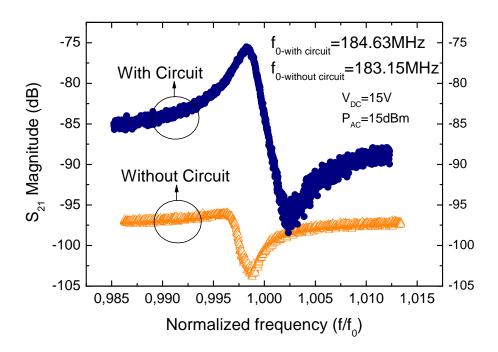

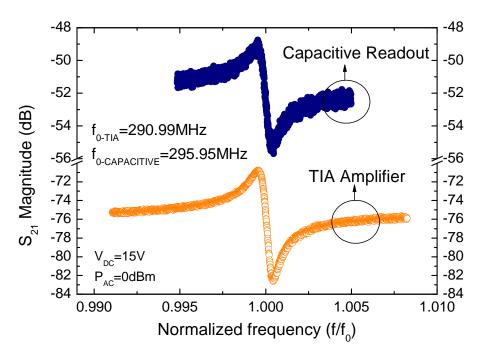

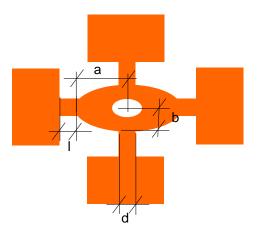

$$T = \frac{C_0}{s} U_R \quad [N/V] \tag{2.19}$$