# A CMOS PIXEL VERTEX DETECTOR FOR THE SUPER KEK-B EXPERIMENT SEMICONDUCTOR TRACKER

# A DISSERTATION SUBMITTED TO THE GRADUATE DIVISION OF THE $UNIVERSITAT\ AUT\^ONOMA\ DE\ BARCELONA\ IN\ PARTIAL$ FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN

# ELECTRICAL ENGINEERING FROM THE UNIVERSITAT AUTÒNOMA BARCELONA

MAY 2008

By María Elena Martín Albarrán

Dissertation Committee:

Prof. J. Aguiló, Chairperson Dr. M. Lozano, Secretary Prof. A. Diéguez Dr. H.-G. Moser Dr. G. Rizzo UNIVERSITAT AUTÒNOMA DE BARCELONA

Departament de Microsistemes i Sistemes Electrònics

A CMOS PIXEL VERTEX DETECTOR FOR THE SUPER KEK-B

EXPERIMENT SEMICONDUCTOR TRACKER

Dissertation presented to obtain the degree of Doctor of Philosophy in Elec-

trical Engineering

Author: María Elena Martín Albarrán

Directors: DR. GARY S. VARNER AND DR. CARLES FERRER I RAMIS

Dr. Gary S. Varner, Assistant Professor from the University of Hawai'i,

Dr. Carles Ferrer i Ramis, Professor from the Universitat Autònoma de

Barcelona

CERTIFY:

that the dissertation "A CMOS pixel vertex detector for the

Super KEK-B experiment semiconductor tracker ", presented by Ms.

María Elena Martín Albarrán to obtain the degree of Doctor of Philosophy in

Electrical Engineering, has been done under their direction at the University

of Hawaii and the Universitat Autònoma de Barcelona.

Barcelona, March 2008

Dr. Gary S. Varner

Dr. Carles Ferrer i Ramis

iii

Una de las lecciones más claras de la historia, incluida la historia reciente, es que los derechos no son graciosamente concedidos, sino conquistados.  $Noam\ Chomsky$

Aprendí que no se puede dar marcha atrás, que la esencia de la vida es ir hacia adelante. La vida, en realidad, es una calle de sentido único.  $Agatha\ Christie$

### Acknowledgements

During the course of this research, I have benefited from the support of many individuals and institutions. I would like to express my appreciation to all. In first place, I would like to thank my supervisor from the University of Hawaii Prof. Gary S. Varner for his everyday guidance and giving me the opportunity to work on such an exciting project. The next person I have to thank is my other supervisor from the Universitat Autònoma de Barcelona Prof. Carles Ferrer Ramis for his continuous support and encouragement until the end of this dissertation. My special thanks go also to Doctor Marlon Barbero who was always ready to give me a helping hand and an explanation during all the hard work involved in the CAP3 testing. I also have to thank Doctor Herbert Hoedlmoser, Mike Cooney for his support and help with the CAP4 testing. I also have to acknowledge Jim Kennedy for his help, support and continuous help in all kind of technological problems. Finally I also want to thank Larry Ruckman and Aaron Koga for their help in all these projects that may have not been included in this dissertation, but have also taught me so much. I would like to express my gratitude to the team from the IDLab and the High Energy Physics Department that help me so much with fruitful discussions and patient explaining technological details. Among these people I want to specially name Prof. Steven Olsen, Prof. Tom Browder, Doctor Marc Rosen, Doctor Jin Li, Tom Roy, Jamal Roire, Chenyan Song and all the Phd and Bachelor student I had the great pleasure to work, discuss and learnt with. The last people in this list, but not for this reason the less important are Jan Bruce, Josie Nanao, Peter Huang, Diana Ibaraki and Jacky Li, the people that help me with all the paperwork that took me to the US and that provided me all the assistance at work available. I gratefully acknowledge the team spirit within the Belle collaboration as well as the SOI R&D collaboration. My special thanks go to Prof. Y. Arai, from whom I learnt a lot. The list for these acknowledgments cannot miss the people that also participated in the SOI project, from different scientific institutes, like Doctor Grzegorz Deptuch from FNAL, to whom I am specially thankful for all his help, support and strength, as well as Doctor Hiro Tajima from SLAC. I should not forget to

thank to my friends and colleagues with whom I used to work during my Ph. D. studies at the University of Hawaii, especially Hulya Guler, Sara Couto da Silva, Juanita Matthews and everybody I may be forgetting present in TGIF, like Pepe, etc,... for the endless discussions and their friendship. None of this work would have succeeded without the continuous support and encouragement of my friends and family. I shall be always grateful to them.

#### ABSTRACT

This dissertation is entitled A CMOS pixel vertex detector for the super KEK-B experiment semiconductor tracker. It will explain the research that has been done at the IDLab at the University of Hawai'i for the upgrade of the pixel detector. This summary will briefly explain the contents of each chapter that has been included.

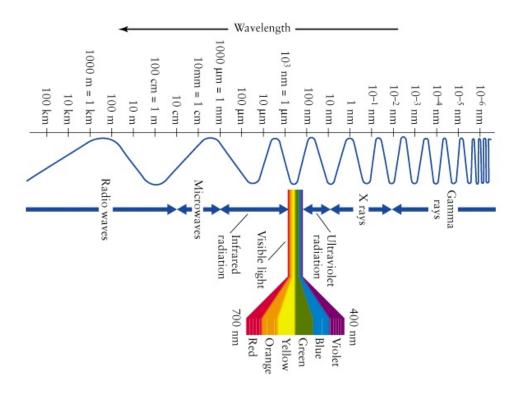

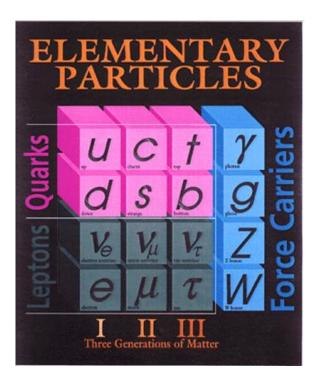

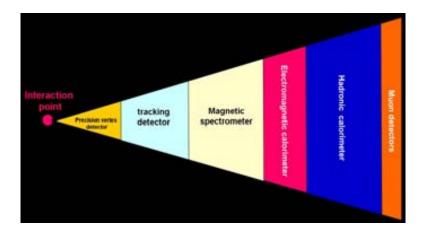

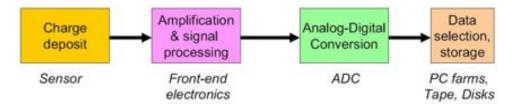

Chapter 1 Introduction This chapter makes an overview of the fields that this dissertation has been developed. The first field is related to experimental particle physics and a brief description of the different kind of detectors that can be found in a complete detector environment, like a tracking detector. A tracking detector can be a semiconductor detector, which is the kind of detectors presented in this dissertation. From all the different possibilities, the option studied in this work is Monolithic (or Semi-Monolithic) Active Pixel Sensor (MAPS), that will be briefly introduced. The next aspect to be explained is a Belle experiment overview that explains the reason for the need for the upgrade of the vertex detector.

Chapter 2 Particle Detection and Tracking This chapter includes a technology review. This technology review describes drift and Charge-Coupled Device (CCD) detectors and their more successful applications in the field of high energy physics. The next kind of detectors explained include hybrid and monolithic (and semi-monolithic) detectors. The detectors that have been evaluated in this dissertation correspond to monolithic detectors: Complementary Metal Oxide Semiconductor (CMOS) with epitaxial layer and CMOS on Silicon on insulator (SOI). These two options are explained, specially the SOI technology, highlighting all the advantages and disadvantages presented by them. The next aspect that is explained in this chapter is how the detection is performed. The basis of all this semiconductor detectors are the p-n junction, where the junction capacitance, charge collection and signal formation are analyzed. The last aspect to be presented is the different pixel detector architectures, from the basic Passive Pixel Sensor (PPS) to the more complex

Active Pixel Sensor (APS). The most commonly used is the APS, because it includes amplification at pixel level. This approach has been evolving through the years, presenting a more complex architecture that will go from the basic 3 Transistor (3T) structure to the digitalization at pixel level.

Chapter 3 Principle of Detector Operation This chapter start listing the most important characteristics of the Silicon, that convert it as the most used material in pixel detector development and microelectronics digital/analog circuitry. The next aspect to be considered is the interaction of radiation with matter. There will be an analysis that includes the energy loss of heavy charged particles, and analyzing what are the fluctuations of loss. A similar analysis is performed for the energy loss by electrons and photons. The last aspects that are explained here include the energy for charge carrier generation in a semiconductor material and the multiple coulomb scattering.

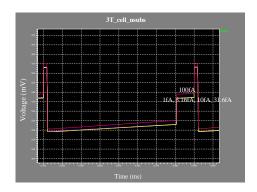

Chapter 4 Belle Experiment Upgrade This chapter is used to introduce the environment where the pixel detector has to be working. To start this introduction basic particle physics and the Belle Experiment in Research Institute for High Energy Physics (KEK) are explained. The second explanation is related to B-Factories, specially to KEK. KEK is the accelerator where the Belle experiment is taking place. After this general introduction, the results obtained with the two first prototypes are introduced. Continuous Acquisition Pixel 1 (CAP1) is the first prototype, it consists of a basic 3T cell and irradiation studies and an analysis of the read-out speed is also presented. Continuous Acquisition Pixel 2 (CAP2) is the second prototype, it consists of a basic structure with 10 storage cells per pixel, that can be used to perform Correlated Double Sampling (CDS) read-out. As well as happened with CAP1, test beam results, irradiation studies and an analysis of the read-out speed is done.

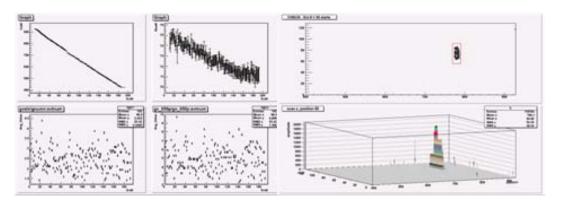

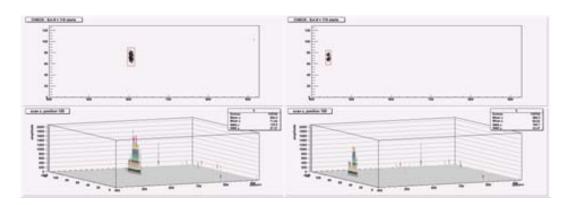

<u>Chapter 5</u> Continuous Acquisition Pixel 3 (CAP3) This chapter is used to explain the architecture of Continuous Acquisition Pixel 3 (CAP3) and to describe all the testing results obtained with the laser set-up. CAP3 was

developed using TSMC with a feature size of  $0.25\mu m$ . The pixel architecture used here includes a double 8 group of storage cells per pixel. The laser spot was detected. But the output speed obtained with this chip was too slow, because the capacitance at the output lines were too high.

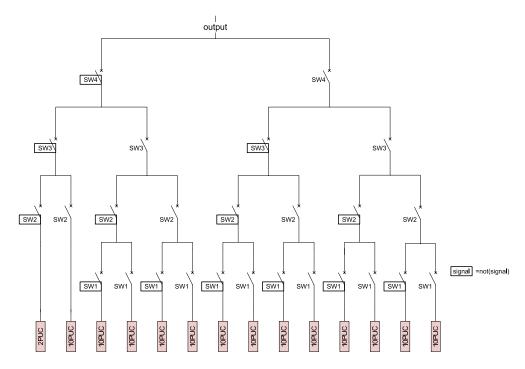

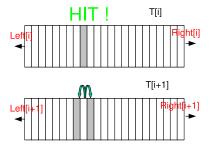

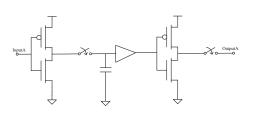

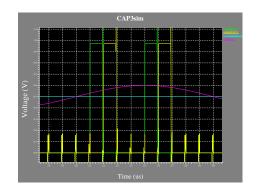

Chapter 6 Continuous Acquisition Pixel 4 (CAP4) This chapter is used to explain the architectures of Continuous Acquisition Pixel 4 (CAP4). In this chapter the laser testing set-up is explained with more detail. The Compound Operational Board Interface (COBI)/Particle Electronics Test & Readout Application Board (PETRA) board are introduced as a part of the new environment used for the development of the Continuous Acquisition Pixel (CAP) family. Then, the CAP4 architecture will be generally explained, to enter into more detail in the 2 architectures included in this chip: the Wilkinson and the Binary read-out. Wilkinson read-out prototype keeps studying the analog read-out kind of system. This architecture would include two main advantages. The use of a tree output structure to decrease the capacitance at the output node. And the inclusion of a comparator every few rows that would digitalized the signal obtained at pixel level The second option evaluated in this CAP4 was a more complex digitalization pixel structure. It analyzed the possibilities of using a pixel with circuitry that would take responsibility of the detection of a hit based on a general threshold signal. The main characteristic of this approach is the transmission pixel-by-pixel of the signal obtained for both sides, left and right. There were two different pixel layout included in the CAP4 layout. The main difference was the number of Positive-channel Metal-Oxide Semiconductor (PMOS) used. The approach with higher number of PMOS transistors showed results based in a read-out speed of 10Mhz.

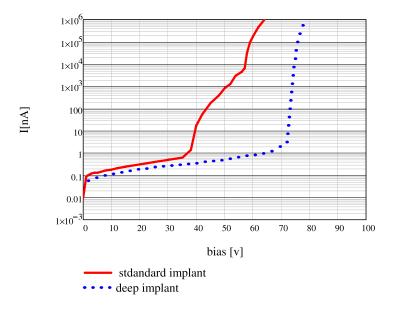

Chapter 7 Continuous Acquisition Pixel 5 (CAP5) Continuous Acquisition Pixel 5 (CAP5) chapter analyzed the possibility of overcoming the limitation of PMOS transistor that appears in a CMOS with epilayer technology. The usage of a SOI process was available through a collaboration with KEK and OKI Electric Industry Co. Ltd. (OKI). This prototypes were fabricated using a second run of a  $0.15\mu m$  SOI process. The pixel that were submitted for

this process included the same architectural approach as CAP4 binary. The basic read-out cell, with the reset transistor and source-follower was working according to our expectations, but the comparator and all the digital circuits showed a very poor performance. This chip was used to characterized the transistors and see the real effects of using the openings on the variation of the threshold voltage, showing results that were never reported before.

Chapter 8 Conclusions This section presents the main achievements presented in all the dissertation, they are novelty of the pixel architecture used, even though the experimental results obtained have not been as successful as expected. CAP6 prototype will also continue evaluating the Wilkinson architecture in the  $0.35\mu m$  TSMC process was done in October 2007. CAP7 prototype will be evaluating the binary solution. This binary solution will be fabricated using a  $0.20\mu m$  SOI process of OKI. This process has been developed for several years and has shown great performance. CAP7 submission was done in January 2008 with improved binary solution to correct the pixel chatter problem.

#### RESUMEN

Esta tesis doctoral se titula A CMOS pixel vertex detector for the Super KEK-B experiment semiconductor tracker. Esta tesis explicará toda la investigación que se ha desarrollado en el laboratorio IDLab, que se encuentra en la University of Hawai'i, y que corresponde al upgrade del detector de pixel. Este resumen explicará brevemente los contenidos de cada capítulo presente en esta memoria.

Capítulo 1 Introducción Este capítulo presenta una revisión de algunos de los campos de conocimientos en los cuales se desarrolla esta tesis. El primer campo que se menciona está relacionado con física experimental de partículas y introduce brevemente los diferentes tipos de detectores que pueden ser encontrados en el entorno de un detector a nivel general, como podría ser un detector de tracking. Un ejemplo de detector de tracking es el detector basado en semiconductores, que es el tipo de detectores que es presentado y desarrollado en esta tesis. De todas las diferentes opciones, el tipo de tecnología escogida para desarrollar en est tesis corresponde a MAPS, que también será presentado. El siguiente aspecto que se explicará es una visión general del experimento Belle y que explicará las razones que han llevado a la necesidad de la actualización del vertex detector.

Capítulo 2 Detección y Rastreo de Partículas Este capítulo presenta una revisión tecnológica. Esta revisión describe brevemente a los detectores de drift y basados en CCD y tambien sus aplicaciones más exitosas en el campo de la física de altas energías. El siguiente tipo de detectores que se explican incluyen los detectores híbridos y monolíticos (y semi-monolíticos). Los detectores que han sido evaluados en esta tesis corresponden a detectores monolíticos (o MAPS) en dos de sus modalidades: CMOS con capa epitaxial y CMOS con tecnología SOI. Estas dos opciones tecnológicas son explicadas detalladamente, especialmente la tecnología SOI, y se procede a resaltar las ventajas y desventajas más importantes presentes en ambas tecnologías. El siguiente aspecto que se explica en este capítulo es como se realiza la detección

de las partículas. La base de todos los detectores es la unión pn, y se hace un análisis detallado de la capacidad de unión presente, la carga capturada y como se realiza la creación de la señal que será posteriormente detectada. El último aspecto que se presenta aquí es un análisis de las diferentes arquitecturas a nivel de pixel, que iran desde la bàsica PPS a la más compleja APS. La mayormente utilizada es la APS, debido a la amplificación que se incluye en cada pixel presente. Esta arquitectura ha ido evolucionando a lo largo de los años, presentado una arquitectura que se encuentra desde la estructura básica llamada 3T a la que incluye una digitalización a nivel de pixel.

Capítulo 3 Principos de Operación para un Detector Este capítulo se inicia con un listado de las características más importantes del silicio, que lo convierten en el material más usado en el desarrollo de detectores de píxel y en la tradional circuitería digital o analógica que se desarrolla en el campo de la microelectrónica. El siguiente aspecto considerado es la interacción de la radiación con la materia. Se presenta un análisis que incluye las pérdidas de energía de partículas cargadas pesadas y también se analizan las fluctuaciones que aparecen en las pérdidas. Un análisis similar se produce tambien para las pérdidas de energia producida por electrones y fotones. Los últimos aspectos que se explican aquí incluyen la energía por generación de portadores en un material semiconductor y el multiple coulomb scattering.

Capítulo 4 Upgrade del Experimento Belle Este capítulo se utiliza para introducir el entorno donde el detector de pixel tiene que acabar trabajando. Para empezar esta introdución se hará una descripción de conceptos básicos de física de partículas, del experimento Belle, y también de KEK. La segunda explicación es una descripción de las características más importantes de las B-Factories y especialmente sobre KEK. KEK es el acelerador donde el experimento Belle tiene lugar. Despué de esta introducción general, se presentan los resultados obtenidos con los dos primeros prototipos. CAP1 es el primer prototipo, consiste de una celda 3T básica, con el cual se presentan los resultados de la radiació a la que el prototipo ha sido expuesto, a parte de estos resultados se hace un análisis de la velocidad de lectura obtenida. CAP2 es

el segundo prototipo, y presenta una estructura básica que contiene 10 celdas de almacenaje por pixel. Estas 10 celdas pueden ser utilizadas para hacer una lecture con CDS. Tal y como se hizo anteriormente con CAP1, los resultados de la irradiación a la que el prototipo ha sido expuesto se presentan, y también se realizará un análisis de la velocidad de lectura obtenida.

<u>Capítulo 5</u> Continous Acquisition Pixel 3 (CAP3) Este capítulo se utiliza para explicar la arquitectura de CAP3 y para describir todos los resultados de test obtenidos con el set-up del laser. CAP3 se fabricó utilizando el proceso de TSMC de  $0.25\mu$ m. La arquitectura de pixel usada aquí incluye un grupo doble de 8 celdas de almacenaje por pixel. El laser infrarrojo era detectado claramente, pero la velocidad de lectura que se obtenía con este chip era muy baja, en parte, debido a que las capacidades que se encontraron en las líneas de salida eran muy altas.

Capítulo 6 Continous Acquisition Pixel 4 (CAP4) Este capítulo se utiliza para explicar las arquitecturas que se utilizan en CAP4. En este capítulo se describirá con mayor detalle el set-up de test del laser. Las placas COBI/PETRA son presentadas como partes del nuevo entorno que se usara para el desarrollo de la familia CAP. Después de esto, la arquitectura del CAP4 se explicará de un manera general, para despues entrar en detalle en las dos arquitecturas presentes en este chip: Wilkinson y Binary. El prototipo con lectura de salida tipo Wilkinson es la continuación del estudio del tipo de lecturas de salida tipo analógico. Esta arquitectura presenta dos ventajas. La primera es la utilización de una estructura tipo árbol para disminuir la capacidad del nodo de salida. La inclusión de un comparador cada 3-4 filas permiten la digitalización de la señal obtenida a nivel de pixel. La segunda opción evaluada en el CAP4 era una estructura que realiza una mucho más compleja digitalización a nivel de pixel. Esta opción analiza la posibilidad de utilizar un pixel con gran número de circuitería que se encargaría de la  $\det$ ección de un hit dependiendo de una señal humbral. La característica más importante de esta aproximación es la transmisión de la información de pixel a pixel, hacia la derecha y hacia la izquierda. Esta arquitectura presenta dos

tipos diferentes de *layout*, que difieren en el número de transistores PMOS utilizados. El *layout* que presentaba mayor número de transistores PMOS presentó resultados para velocidades de lectura de 10Mhz.

Capítulo 7 Continous Acquisition Pixel 5 (CAP5) El capítulo que describe CAP5 estudia la posibilidad de evitar las limitaciones del número de transistores PMOS utilizados, que aparece en la utilización de CMOS con capa epitexial. La utilización de un proceso SOI es posible gracias a una colaboración de KEK con la empresa OKI. Estos prototipos se fabricaron utilizando un run del proceso 0.15μm de SOI. El pixel que se envió a fabricar seguía la misma arquitectura que en el CAP4 binary. La celda de lectura básica, con el transistor de reset y con la estructura de source-follower funcionaron de acuerdo con las expectativas, pero el comparador y toda la circuitería digital mostró un funcionamiento muy pobres. Este chip se utilizó para caracterizar los transistores y comprobar los efectos de utilizar las aberturas para las implantaciones en las variaciones de tensión humbral, mostrando resultados que no se habían mostrado antes.

Capítulo 8 Conclusiones Este capítulo presenta los mayor logros conseguidos a lo largo de esta tesis. Entre ellos esta la presentación de una arquitectura a nivel pixel (binary) que nunca antes había sido utilizada, aunque los resultados experimentales no son tan exitosos como era de esperar. Se presentará al prototipo de CAP6 que continuará evaluando la arquitectura de Wilkinson con un proceso de TSMC de  $0.35\mu$ m que se envió a fabricar en Octubre de 2007. El prototipo de CAP7 continuará evaluando la solución binary. Esta solución se fabricará utilizando el proceso de SOI de  $0.20\mu$ m de OKI. Este proceso se ha desarrollado y utilizado durante años y ha mostrado un funcionamiento excelente. La fabricación de CAP7 se realizó en Enero del 2008 incluyendo una solución binary donde el problema de chattering presente en CAP4 se intenta evitar.

#### **SUMARI**

Aquesta tesi doctoral es titula *A CMOS pixel vertex detector for* the Super KEK-B experiment semiconductor tracker. Aquesta tesi explicarà tota la investigació que s'ha desenvolupat en el laboratorio IDLab, que es trobas a la University of Hawai'i, i que correspon a l'upgrade del detector de pixel. Aquest resum explicarà breument els continguts de cada capítol present en aquesta memòria.

Capítol 1 Introducció Aquest capítol presenta una revisió d'alguns dels camps de coneixement en els quals es desenvolupa aquesta tesi. El primer camp que es menciona està relacionat amb la física experimental de partícules i introdueix breument els diferent tipus de detectors que es poden trobar en l'entorn d'un detector en termes molt generals, com podria ser un detector de tracking. Un exemple de detector de tracking és el detector bast en semiconductors, que és el tipus de detector presentat i desenvolupat en aquest tesi. De totes les diferents opcions, el tipus de tecnologia escollida per desenvolupar en aquesta tesi correspon a MAPS, que també serà presentat. El següent aspecte que s'explicarà és una visió general de l'experiment Belle i que explicarà les raons que han portat a la necesitat d'actualització del vertex detector.

Capítol 2 Detecció i Tracking de Partícules Aquest capítol presenta una revisió tecnològica. Aquesta revisió descriu breument els detectors de drift i basats en CCD i també les seves aplicacions més exitoses en el camp de la física d'altes energies. El següent tipus de detectors que s'expliquen inclouen els detectors híbrids i monolítics (i semi-monolítics). Els detectors que s'han evaluat en aquesta tesi corresponen a detectors monolítics (o MAPS) en dos de les modalitats possibles: CMOS amb capa epitaxial i CMOS amb tecnologia SOI. Aquestes dues opciones tecnològiques són explicades detalladament, especialment la tecnologia SOI, i es procedeix a resaltar les avantatges i desvantatges més importants presents en ambdues tecnologies. El següent aspecte que s'explica en aquest capítol és com es realitza la detecció de les partícules. La base de tots els detectors és la unió pn, i es fa una anàlisis detallat de la

capacitat d'unió present, la càrrega capturada i com es realitza la creació de la senyal que será posteriorment detectada. L' últim aspecte que es presenta aquí és un anàlisi de les diferents arquitectures a nivell de pixel, que aniran desde la bàsica PPS a la més complexa APS. La majorment utilitzada és la APS, degut a l'amplificació que s'inclou en cada pixel present. Aquesta arquitectura ha anat evolucionant al llarg dels anys, presentant una arquitectura que es troba desde l'estructura bàsica que es diu de 3T a la que inclou una digitalització a nivell de pixel.

Capítol 3 Principis d'Operació per un Detector Aquest capítol s'inicia amb un llistat de les característiques més importants del silici, que el convierteixen en el material més utilitzat en el desenvolupament de detectores de píxel i en la tradional circuitería digital o analògica que es desenvolupa en el camp de la microelectrònica. El següent aspecte considerat és la interacció de la radiació amb la materia. Es presenta un análisi que inclou les pèrdues d'energía de partícules carregades pesades i també s'analitzen les fluctuacions que apareixen en les pèrdues. Un anàlisi similar es produeix també per les pèrdues d'energia produïda per electrons i fotons. Els últims aspectes que s'explican aquí inclouen l'energía per generació de portadors en un material semiconductor i el multiple coulomb scattering.

Capítol 4 Upgrade de l'Experiment Belle Aquest capítol s'utilitza per introduir l'entorn on el detector de pixel ha d'acabar treballant. Per començar aquesta introdució es farà una descripció de conceptes bàsics de física de partícules, l'experiment Belle, i de KEK. La segona explicació és una descripció de les característiques més importants de les *B-Factories* i especialment sobre KEK. KEK és l'accelerador on l'experiment Belle té lloc. Després d'aquesta introducció general, es presenten els resultats obtinguts amb els dos primers prototips. CAP1 és el primer prototipus, consisteix en una cel·la 3T bàsica, per la qual es presenten els resultats per la radiació a la qual el prototipus ha esta exposat, a part d'aquests results es fa un anàlisi de la velocitat de lectura obtinguda. CAP2 és el segon prototipus, i presenta una estructura bàsica que conté 10 cel·les d'emmagatzament per pixel. Aquestes cel· poden

ser utilitzades per fer lectures amb CDS. De la mateixa maner que es va fer amb CAP1, els resultats de la radiació a la que el prototipus ha estat exposat es presenten, i també es realizarà un anàlisi de la velocitat de lectura obtinguda.

<u>Capítol 5</u> Continous Acquisition Pixel 3 (CAP3) Aquest capítol s'utiltza per explicar l'arquitectura de CAP3 i per descriure tots els resultats de test obtinguts amb el set-up del laser. CAP3 es va fabricar utilitzant el procés de TSMC de  $0.25\mu m$ . L'arquitectura de pixel utilitzada aquí inclou un grup doble de 8 cel·les d'emmagatzament per pixel. El laser infraroig era detectat clarament, pero la velocitat de lectura que s'obtenia amb aquest chip era molt baixa, en part, degut a que les capacitats que es trobaben a les línees de sortida eren molt altes.

Capítol 6 Continous Acquisition Pixel 4 (CAP4) Aquest capítol s'utiliza per explicar les arquitectures que s'utilizan en CAP4. En aquest capítol es descriurà amb més detall el set-up de test del laser. Les plaques COBI/PETRA són presentades com a parts del nou entorn que s'utilitzarà pel desenvolupament de la familia CAP. Després d'això, l'arquitectura del CAP4 s'explicarà d'una manera general, per després entrar en detall en les dues arquitectures presents en aquest xip: Wilkinson i Binary. El prototipus amb lectura de sortida tipus Wilkinson és la continuació de l'estudi del tipus de lecturas de sortida tipus analògic. Aquesta arquitectura presenta dues aventatges. La primera és la utilizació d'una estructura tipus arbre per disminuir la capacitat del node de sortida. La inclusió d'un comparador cada 3-4 files permet la digitalització de la senyal obtinguda a nivell de pixel. La segona opció evaluada en el CAP4 era una estructura que realitza una molt més complexa digitalització a nivell de pixel. Aquest opció analitza la posibilitat d'utilizar un pixel amb gran nombre de circuiteria que s'encargaria de la detecció d'un hit depenent d'una senyal llindar. La característica més important d'aquesta aproximació és la transmisió de la informació de pixel a pixel, cap a la dreta i cap a l'esquerra. Aquesta arquitectura presenta dos tipus diferents de layout, que difereixen en el número de transistors PMOS utilitzats. El layout que presentava més número de transistors PMOS va presentar resultats per velocitats de lectura de 10Mhz.

Capítol 7 Continous Acquisition Pixel 5 (CAP5) El capítol que descriu CAP5 estudia la posibilitat d'evitar les limitacions del número de transistors PMOS utilizats, que apareixen en la utilizació de CMOS amb capa epitexial. La utilizació d'un procés SOI és possible gràcies a una colaboració de KEK amb l'empresa OKI. Aquests prototipus es van fabricar utilitzant un run del procés 0.15μm de SOI. El pixel que es va enviar a fabricar seguia la mateixa arquitectura que en el CAP4 binary. La cel·la de lectura bàsica, amb el transistor de reset i amb l'estructura de source-follower van funcionant d'acord amb les expectatives, però el comparador i tota la circuiteria digital va mostrar un funcionament molt pobres. Aquest xip es va utilitzar per caracteritzar els transistors i comprovar els efectes d'utilizar les obertures per les implantacions en les variacions de tensió llindar, mostrant resultats que no s'havien mostrat abans.

Capítol 8 Conclusions Aquest capítol presenta els majors assoliments aconseguits al llarg d'aquesta tesi. Un d'ells és la presentació d'una arquitectura a nivell pixel (binary) que mai abans habia estat utilitzada, encara que els resultats experimentals no són tan exitosos como era d'esperar. Es presentarà al prototipus de CAP6 que continuarà evaluant l'arquitectura de Wilkinson amb un procés de TSMC de  $0.35\mu m$  que s'ha enviat a fabricar en Octubre de 2007. El prototipus de CAP7 continuarà evaluant la solució binary. Aquesta solució es fabricarà utilitzant el procés de SOI de  $0.20\mu m$  de OKI. Aquest procés s'ha desenvolupat i utilitzat durant anys i ha mostrat un funcionament excel·ent. La fabricació de CAP7 es va realitzà al Gener del 2008 incloent una solució binary on el problema de chattering present en CAP4 s'ha intentat evitar.

## Glossary

**3T** 3 Transistor. x, xiv, xviii, 10, 11, 50, 79, 122, 123, 134, 168, 170, 171, 175–177, 182, 185, 188

ACC Aerogel threshold Cherenkov Counters. 67

**ADC** Analog-to-Digital Converter. 69, 70, 76, 97, 108, 109, 114, 116, 125, 127, 190

ALICE A Large Ion Collider Experiment. 15, 17

AMS Austria MicroSystems. 115, 165, 190

**APS** Active Pixel Sensor. ix, xiv, xviii, 11, 49

**ASIC** Application-Specific Integrated Circuit. 20

ATLAS A Toroidal LHC ApparatuS. 17, 18

BABAR B/B-bar. 18

BE Back-End. 76

**BESOI** Bonded and Etched-Back Silicon-On-Insulator. 19, 27

**BJT** Bipolar Junction Transistor. 21

**BOX** Buried Oxide Layer. 25, 27–29, 33, 37, 152, 154, 156

BTev BlueTrait Event Viewer. 17

**CAP** Continuous Acquisition Pixel. xi, xv, xix, 10, 12, 50, 65, 69, 71, 75, 113, 116, 121, 124, 142, 147, 164, 165, 168, 189

- **CAP1** Continuous Acquisition Pixel 1. x, xiv, xviii, 10, 68–71, 73, 75, 76, 78, 116, 125, 128

- **CAP2** Continuous Acquisition Pixel 2. x, xiv, xviii, 10, 70, 71, 73, 75, 76, 78, 116, 125, 128, 187

- **CAP3** Continuous Acquisition Pixel 3. x, xv, xix, 10, 73, 75, 76, 78, 79, 83, 86, 91, 110, 111, 116, 122, 125, 128, 187

- **CAP4** Continuous Acquisition Pixel 4. xi, xv, xvi, xix, xx, 10, 111, 114, 115, 131, 144, 145, 147, 165, 168, 170, 188, 189

- **CAP5** Continuous Acquisition Pixel 5. xi, xvi, xix, 161, 165, 167, 168, 175, 182, 188

- CCD Charge-Coupled Device. ix, xiii, xvii, 7, 9, 13–16, 49, 63, 190

- CDC Central Drift Chamber. 67

- **CDS** Correlated Double Sampling. x, xiv, xviii, 19, 49, 70, 75, 76, 78, 79, 83, 102, 104

- CERN Centre Européenne pour la Recherche Nucléaire. 15–19, 114

- CMOS Complementary Metal Oxide Semiconductor. ix, xi, xiii, xvi, xvii, xix, 7, 9, 11, 13, 19–22, 25, 29, 33, 49, 51, 63, 116, 131, 134, 136–140, 147, 148, 152, 164, 188–190

- CMS Compact Muon Solenoid. 17, 18

- COBI Compound Operational Board Interface. xi, xv, xix, 12, 113, 144, 173, 174, 187

- **CP** Charge conjugation Parity. 8, 9, 67

- CVD Chemical Vapour Deposition. 14, 18

- CW Continuous Wave. 112, 113

- **DAC** Digital-to-Analog Converter. 11, 182–185

**DEPFET** DEpleted P-channel Field Effect Transistor. 7, 20

**DSSD** Double Sided Silicon Detector. 8, 76

**EFC** Extreme Forward Calorimeter. 67

**ENC** Equivalent Noise Charge. 24

FAPS Flexible Active Pixel Sensor. 50

FD-SOI Fully-Depleted Silicon-On-Insulator. 29, 32–35, 37, 39, 148

FE Front-End. 17, 70, 76, 113

**FET** Field Effect Transistor. 14

FPGA Field Programmable Gate Array. 10, 113, 139, 189

FPN Fixed-Pattern Noise. 49, 78

FWHM Full Width at Half Maximum. 58

**HAPS** Hybrid Active Pixel Sensor. 7, 14, 17

**HEP** High Energy Physics. 3, 13, 14, 49, 65, 114

**HV** High Voltage. 173–176, 182, 183, 185, 190

IC Integrated Circuit. 21, 22

**IGFET** Insulated-Gate Field-Effect Transistor. 25

IHXCP Imaging Hard X-Ray Compton Polarimeter. 179

ILC International Linear Collider. 21, 50

**IR** Infrared. 79, 112, 113, 144

ITOX Internal Oxidation. 27

**JAXA/ISAS** Japan Aerospace Exploration Agency /Institute of Space and Astronautical Science. 151

**KEK** Research Institute for High Energy Physics. x, xi, xiv, xvi, xviii, xx, 8, 10, 20, 50, 65, 69, 70, 147, 148, 151, 158, 188, 189

LBNL Lawrence Berkeley National Laboratory. 151

LHC Large Hadron Collider. 15, 17, 18

LHCb Large Hadron Collider beauty. 17

LV Low Voltage. 164, 173, 174

LVDS Low-voltage differential signaling. 69, 70

**MAPS** Monolithic (or Semi-Monolithic) Active Pixel Sensor. ix, xiii, xvii, 7, 9, 10, 14, 16, 22, 28, 50, 67, 68, 131

MCM Multi-Chip Module. 7, 17

MIMOSA Minimum Ionising Particle MOS Active Pixel Sensor. 24, 50

MIP Minimum Ionizing Particle. 18, 19, 24, 56, 57, 62

MOS Metal Oxide Semiconductor. 19, 20, 28, 29, 48, 49

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor. 19, 25, 29, 32, 33, 35, 37

MPW MultiProject Wafer. 151

MWPC Multi-Wire Proportional Chamber. 6

**NMOS** Negative-channel Metal-Oxide Semiconductor. 116, 131, 134–138, 154, 156, 158, 159, 162, 165, 170, 188

**OKI** OKI Electric Industry Co. Ltd.. xi, xii, xvi, xx, 10, 12, 20, 33, 147, 148, 158, 159, 161, 164, 188–190

**PAW** Physics Analysis Workstation. 114

PD-SOI Partially-Depleted Silicon-On-Insulator. 29, 34, 35

**PETRA** Particle Electronics Test & Readout Application Board. xi, xv, xix, 12, 114, 144, 187

**PMOS** Positive-channel Metal-Oxide Semiconductor. xi, xv, xvi, xix, 131, 134–137, 145, 154, 158, 159, 165, 170, 182, 188

**PPS** Passive Pixel Sensor. ix, xiv, xviii

**PUC** Pixel Unit Cell. 117, 122, 123, 128, 132

**PVD** Pixel Vertex Detector. 75

**RHIC** Relativistic Heavy Ion Collider. 15

SDD Silicon Drift Detectors. 14, 15

SEE Single Events Effects. 25

**SER** Soft Error Rate. 30

SIMOX Separation by IMplantation of OXygen. 19, 25, 27

**SLC** Stanford Linear Collider. 16

**SNR** Signal-to-Noise Ratio. 16, 39, 44, 69, 70

**SOI** Silicon on insulator. ix, xi–xiii, xvi, xvii, xx, 7, 10–13, 19, 24, 25, 27–35, 43, 51, 147, 148, 151, 152, 158, 164, 178, 181, 188–190

**SOITEC** Silicon on Insulator Technologies. 19

**SPS** Super Proton Synchroton. 15

SVD Silicon Vertex Detector. 8, 9, 67, 189

TCAD Technology Computer Aided Design. 12, 147, 154

**TEG** Test Element Group. 11, 12, 158

**TEM** Transmission Electronic Microscopy. 151, 154

**TESLA** Tera-electronvolt Energy Superconducting Linear Accelerator. 17, 20

${\bf TID}\,$  Total Ionizing Dose. 33

${f TOF}$  Time-of-Flight. 67

$\mathbf{TPC}$  Time Projection Chamber. 6

TRISTAN Tri Ring Intersecting STorage Accelerators at Nippon. 65

${f ZMR}$  Zone-Melting Recrystallization. 19

# Contents

| A            | cknov                           | m vledgements                                  | vii                                    |

|--------------|---------------------------------|------------------------------------------------|----------------------------------------|

| $\mathbf{A}$ | bstra                           | ct                                             | ix                                     |

| $\mathbf{R}$ | $\mathbf{esum}$                 | en                                             | xiii                                   |

| Su           | ımari                           | ;                                              | xvii                                   |

| Ta           | able o                          | of Contents x                                  | xix                                    |

| Li           | st of                           | Tables                                         | xxi                                    |

| Li           | st of                           | Figures xx                                     | xiii                                   |

| 1            | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Particle Physics and Experimental Methods      | 1<br>4<br>5<br>6<br>9                  |

| 2            | Par                             | cicle Detection and Tracking                   | 11                                     |

|              | 2.1                             | Technology review                              | 11<br>12<br>13                         |

|              | 2.2                             | Hybrid Detectors                               | 14                                     |

|              | $\frac{2.3}{2.4}$               | Monolithic and Semi-Monolithic Pixel Detectors | 16<br>19<br>20                         |

|              | 2.5                             | SOI Technology                                 | 22<br>23<br>26<br>29<br>32<br>34<br>35 |

|              | 2.6                             | Introduction to Detection                      | 37<br>38                               |

|   |     | 2.6.2 High-Field Region and the Diode                                                   | 8 |

|---|-----|-----------------------------------------------------------------------------------------|---|

|   |     | 2.6.3 Junction Capacitance                                                              | 2 |

|   |     | 2.6.4 Charge Collection                                                                 | 3 |

|   |     | 2.6.5 Signal Formation                                                                  | 4 |

|   |     | 2.6.6 Noise in Detectors                                                                | 5 |

|   | 2.7 | Pixel Detector Architectures                                                            | 7 |

|   | 2.8 | Conclusions                                                                             |   |

| 3 | Pri | ciple of Detector Operation 5                                                           | 1 |

| • | 3.1 | Silicon as the Detector Material                                                        |   |

|   | 3.2 | Interaction of Radiation with Matter                                                    |   |

|   | 3.3 | Energy Loss of Heavy Charged Particles                                                  |   |

|   | 0.0 | 3.3.1 Fluctuations in Energy Loss                                                       |   |

|   | 3.4 | Energy Loss by Electrons                                                                |   |

|   | 3.5 | Energy Loss by Photons                                                                  |   |

|   | 3.6 | Radiation Length                                                                        |   |

|   | 3.7 | Energy for Charge Carrier Generation in Semiconductor Material 6                        |   |

|   | 3.8 | Multiple Coulomb Scattering                                                             |   |

|   | 3.9 | Conclusions                                                                             |   |

|   |     |                                                                                         |   |

| 4 |     | Experiment Upgrade 63                                                                   |   |

|   | 4.1 | B-Factories and KEK                                                                     |   |

|   | 4.2 | CAP1                                                                                    |   |

|   |     | 4.2.1 Test Beam Results, Irradiation Studies and Read Out Speed . 6                     |   |

|   | 4.0 | 4.2.2 CAP1 Read-Out Speed and Concept                                                   |   |

|   | 4.3 | CAP2                                                                                    |   |

|   |     | 4.3.1 Test Beam Results, Irradiation Studies and Read Out Speed 6                       |   |

|   | 4.4 | 4.3.2 CAP2 Read-Out Speed and Concept                                                   |   |

|   | 4.4 | Conclusions                                                                             | 1 |

| 5 | Con | inuous Acquisition Pixel 3 $(CAP3)$ 73                                                  |   |

|   | 5.1 | Description of CAP3                                                                     |   |

|   | 5.2 | Testing Results                                                                         |   |

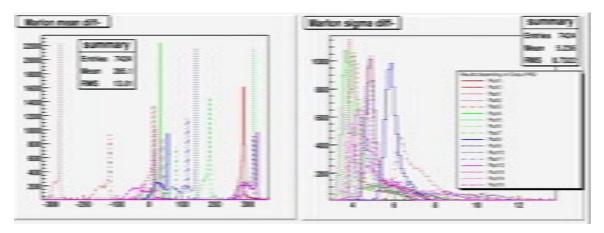

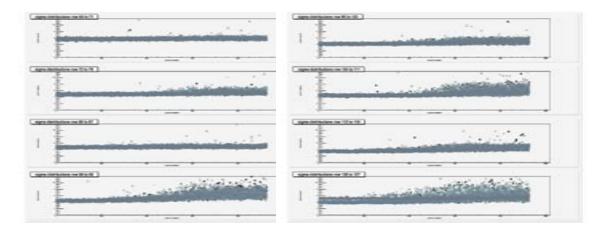

|   |     | 5.2.1 Noise Measurement                                                                 | 6 |

|   | 5.3 | Laser Testing                                                                           |   |

|   |     | 5.3.1 DC initial results                                                                |   |

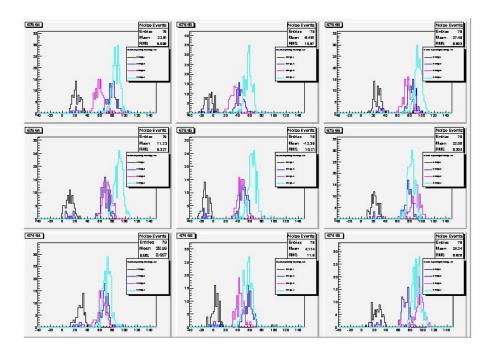

|   |     | 5.3.2 Noise analysis of the 16 Output PADS                                              |   |

|   |     | 5.3.3 Noise analysis of 9 pixels                                                        |   |

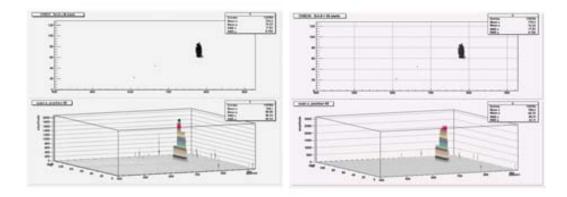

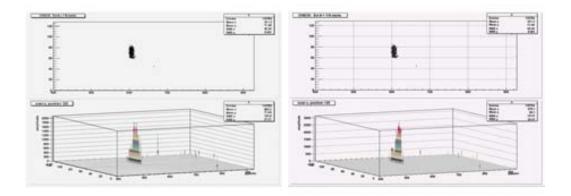

|   |     | 5.3.4 Z scan                                                                            |   |

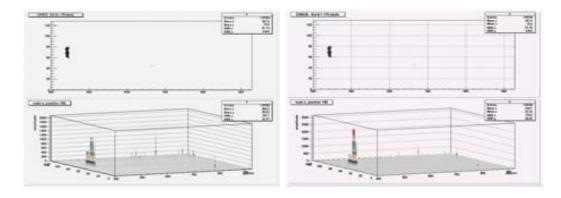

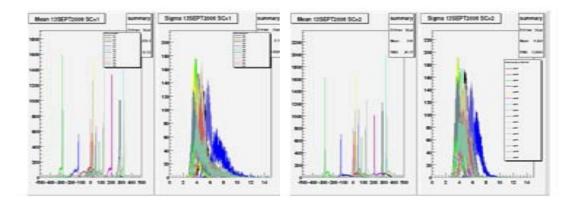

|   |     | 5.3.5 CAP3 Uniformity                                                                   |   |

|   |     | 5.3.6 X scan with CAP3                                                                  |   |

|   |     | 5.3.7 Calibration Coefficients for CAP3                                                 |   |

|   |     | 5.3.8 Laser spot and noise value plot for X scan                                        |   |

|   |     | 5.3.9 Pipeline Preliminary test results: noise measurement 9                            | 2 |

|   |     | 5.3.10 Pipeline/Pulsed laser preliminary test results: laser $pulsewidth$               |   |

|   |     | vs recorded signal                                                                      | 2 |

|   |     | $5.3.11 \text{ Laser}_{pulsewidth} \text{ vs signal recorded for column } 420 \dots 96$ | 5 |

|   |     | 5.3.12 Spill-over and pipeline                                                          | 8 |

|    | 5.4                                   | Conclusions                                                        | . 108 |

|----|---------------------------------------|--------------------------------------------------------------------|-------|

| 6  | Con                                   | ntinuous Acquisition Pixel 4 (CAP4)                                | 109   |

|    | 6.1                                   | Laser Set-Up                                                       |       |

|    | 6.2                                   | Description of the COBI Board                                      |       |

|    | 6.3                                   | General Characteristics of CAP4                                    | . 113 |

|    |                                       | 6.3.1 CMOS-Opto $0.35\mu\mathrm{m}$ AustriaMicroSystems Process    | . 114 |

|    |                                       | 6.3.2 Calculation of charge deposition for CAP4 using the IR Laser |       |

|    |                                       | in the Wilkinson Configuration                                     | . 116 |

|    |                                       | 6.3.3 Calculation of pixel capacitance and noise values for CAP4   | . 118 |

|    |                                       | 6.3.4 Analysis of CAP4                                             | . 119 |

|    | 6.4                                   | Wilkinson Solution                                                 | . 120 |

|    |                                       | 6.4.1 Architecture for the Wilkinson Solution                      | . 121 |

|    |                                       | 6.4.2 Wilkinson Test Results                                       |       |

|    |                                       | 6.4.3 Constant Reset with no Laser Applied                         |       |

|    |                                       | 6.4.4 Test Results                                                 |       |

|    | 6.5                                   | Binary Approach Theory                                             |       |

|    | 6.6                                   | Binary Solution                                                    |       |

|    | 0.0                                   | 6.6.1 NMOS Mostly Solution                                         |       |

|    |                                       | 6.6.2 CMOS Solution                                                |       |

|    | 6.7                                   |                                                                    |       |

|    | 0.7                                   | Conclusions                                                        | . 142 |

| 7  | Continuous Acquisition Pixel 5 (CAP5) |                                                                    |       |

|    | 7.1                                   | SOI Pixels using OKI Process                                       | . 145 |

|    | 7.2                                   | TCAD studies                                                       |       |

|    | 7.3                                   | Test Element Group Test                                            |       |

|    |                                       | 7.3.1 BareN Cell results                                           |       |

|    | 7.4                                   | CAP5 test results                                                  |       |

|    | • • •                                 | 7.4.1 CAP5 OKI chip submission                                     |       |

|    |                                       | 7.4.2 Simulations for CAP5 binary                                  |       |

|    |                                       | 7.4.3 CAP5 testing                                                 |       |

|    | 7.5                                   | X-ray telescope                                                    |       |

|    | 1.0                                   | 7.5.1 Hard X-Ray Sensor Principles                                 |       |

|    |                                       | 7.5.2 X-Ray Telescope Background                                   |       |

|    |                                       |                                                                    |       |

|    |                                       | 7.5.3 General Characteristics of SOI X-ray                         |       |

|    |                                       | 7.5.4 XRAY testing                                                 | . 179 |

| 8  | Con                                   | nclusions                                                          | 183   |

|    | 8.1                                   | Contributions to the CAP development                               | . 183 |

|    | 8.2                                   | Future Developments                                                |       |

|    |                                       |                                                                    |       |

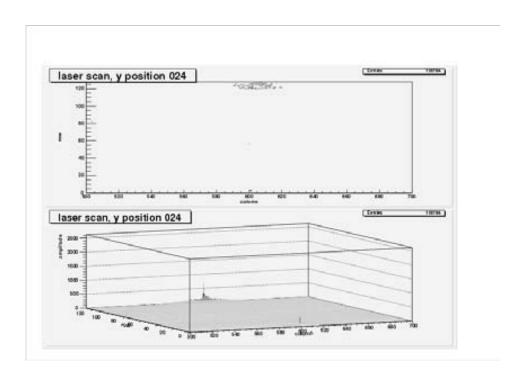

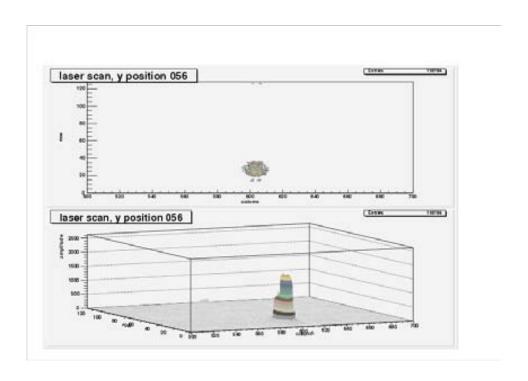

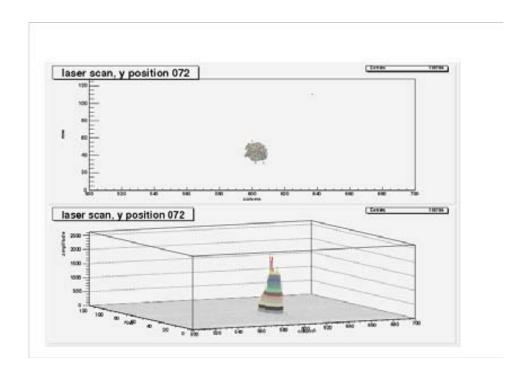

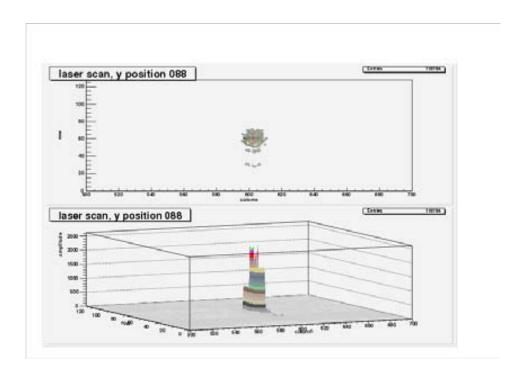

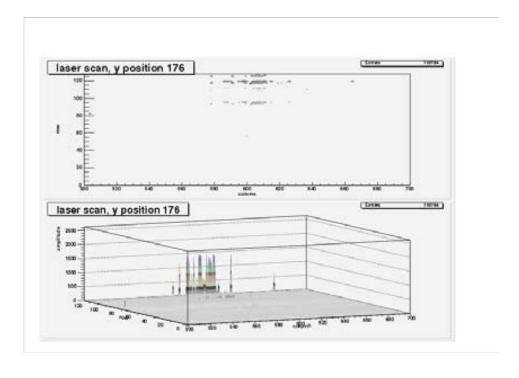

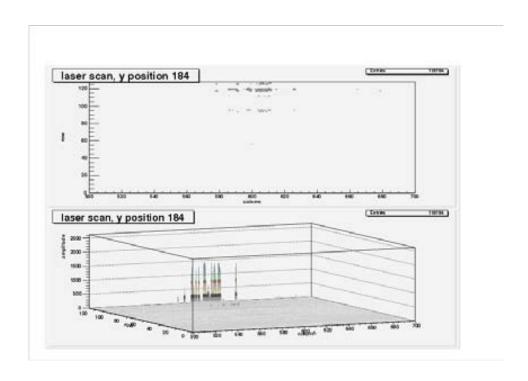

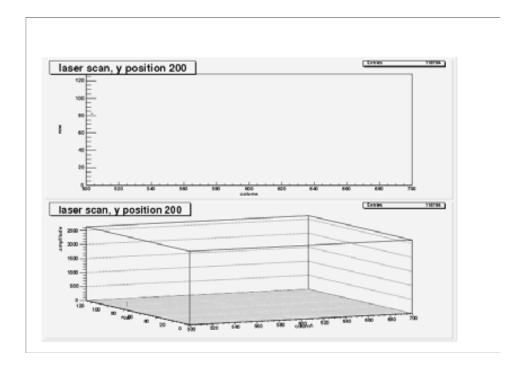

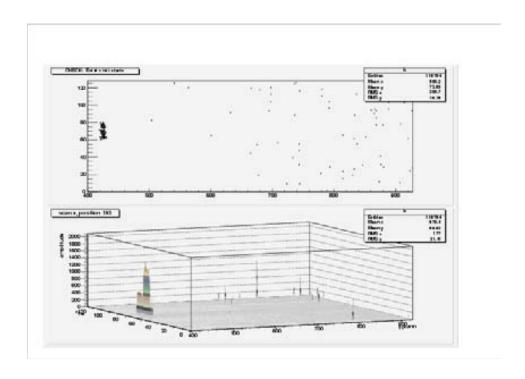

| A  |                                       | P3 Testing Results                                                 | 187   |

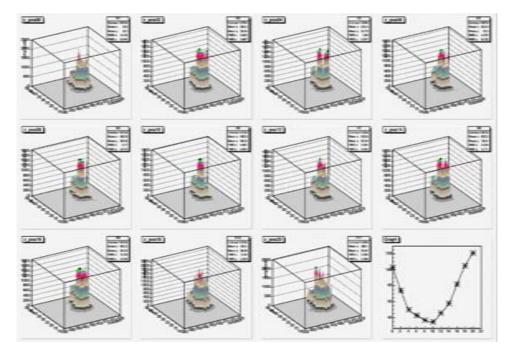

|    |                                       | Y Axis Scan                                                        |       |

|    | A.2                                   | X Axis Scan                                                        | . 194 |

| В  | Pro                                   | graming Files Sample for CAP4                                      | 205   |

| D: | hlias                                 | graphy                                                             | 215   |

|    | DHOS                                  | 71 ALULY                                                           | 416   |

# List of Tables

| 1.1        | Table with the most important characteristics of the SVD of the Belle |     |

|------------|-----------------------------------------------------------------------|-----|

|            | Experiment                                                            | 6   |

| 3.1<br>3.2 | Summary of physical constants used in this section                    |     |

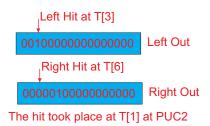

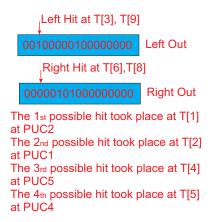

| 6.1        | Timing example for Left and Right Output signals                      |     |

| 7.1        | Process characteristics of the OKI SOI process                        | 149 |

| 7.2        | BareN Cell transistor description                                     | 157 |

| 7.3        | Transistor parameters for SOI process                                 | 157 |

| 7.4        | BareN Cell transistor threshold measurement obtained with HV float-   |     |

|            | ing                                                                   | 157 |

# List of Figures

| 1.1  | Electromagnetic Spectrum                                          | 2  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Elementary particles according to the Standard Model              | 2  |

| 1.3  | Detector Concept, showing different architectures                 | 4  |

| 1.4  | Simplified block diagram of a typical particle detector           | 4  |

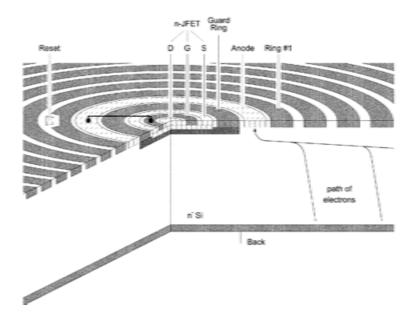

| 2.1  | Geometry of a radial silicon drift detector                       | 13 |

| 2.2  | CCD structure                                                     | 14 |

| 2.3  | Three phase CCD structure                                         | 14 |

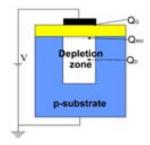

| 2.4  | Charge generation from an incident high-energy particle           | 20 |

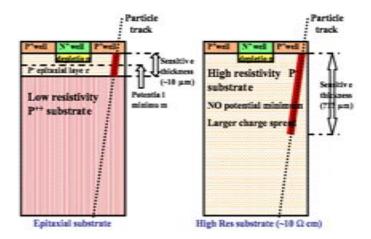

| 2.5  | Cross Section of Epi/non-Epi pixel sensor                         | 21 |

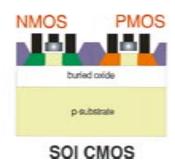

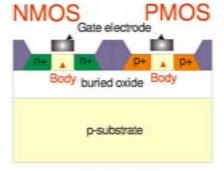

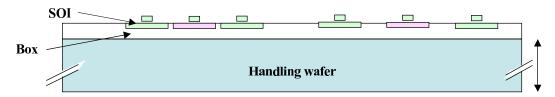

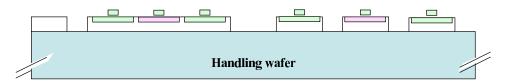

| 2.6  | Conventional integrated circuit done in SOI technology            | 23 |

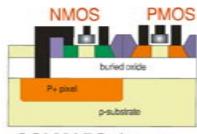

| 2.7  | Radiation detector produced in SOI technology                     | 23 |

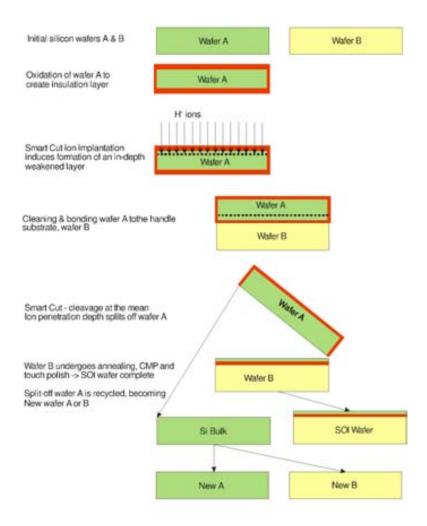

| 2.8  | Process description for the wafer fabrication using the Smart-Cut |    |

|      | method                                                            | 24 |

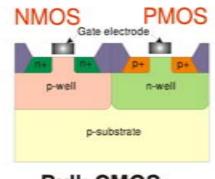

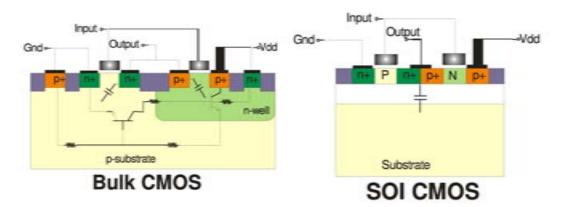

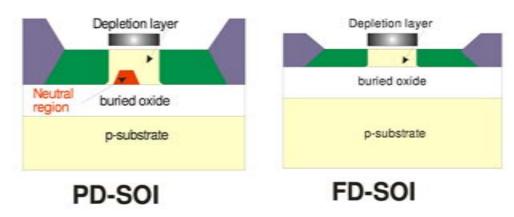

| 2.9  | Cross section of bulk CMOS transistors                            | 26 |

| 2.10 | Cross section of SOI CMOS transistors                             | 26 |

| 2.11 | Parasitic PNPN structure in bulk CMOS structure                   | 27 |

|      | Parasitic structure in SOI CMOS structure                         | 27 |

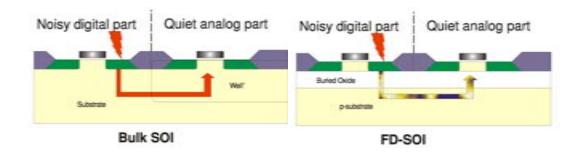

| 2.13 | Noise travelling path in bulk devices                             | 28 |

| 2.14 | Noise travelling path in SOI devices                              | 28 |

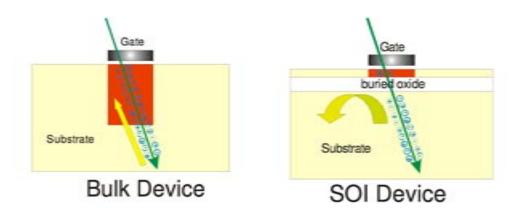

|      | Soft error immunity in bulk devices.                              | 28 |

| 2.16 | Soft error immunity in SOI devices                                | 28 |

| 2.17 | Cross section of bulk CMOS transistors                            | 32 |

| 2.18 | Cross section of SOI CMOS transistors                             | 32 |

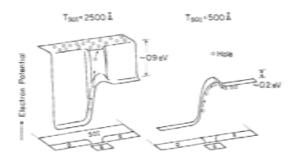

| 2.19 | Two-dimensional electron potential in PD- and FD-SOI MOSFET       | 33 |

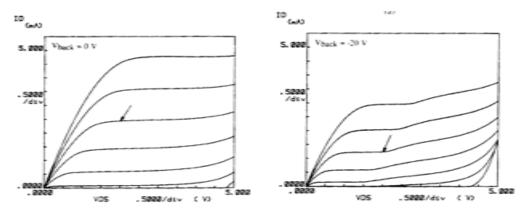

|      | $I_{ds} V_{ds}$ characteristics of a FD-SOI nMOSFET               | 34 |

|      | $I_{ds}$ $V_{ds}$ characteristics of a PD-SOI nMOSFET             | 34 |

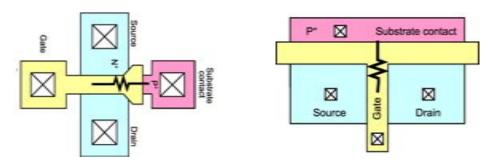

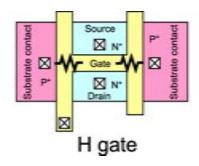

|      | I-gate device schematic.                                          | 34 |

| 2.23 | T-gate device schematic                                           | 34 |

|      | H-gate device schematic                                           | 35 |

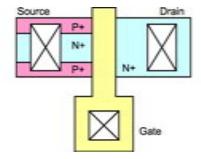

|      | N-channel transistor with source body ties                        | 35 |

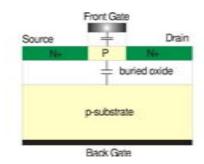

|      | Schematic illustration of FD-SOI cross-section                    | 35 |

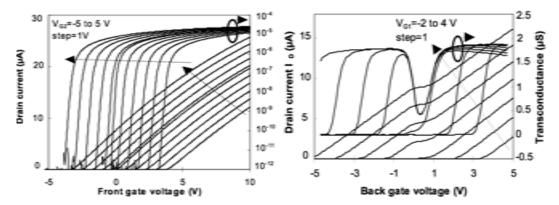

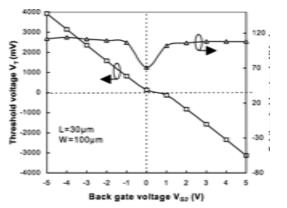

|      | $I_{drain}vs$ front gate bias in a 3nm thick transistor           | 36 |

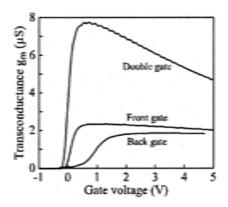

|      | I <sub>drain</sub> and transconductance versus back gate bias     | 36 |

|      | $V_{Threshold}$ and subthreshold swing versus back gate bias      | 36 |

|      | Transconductance versus gate voltage                              | 36 |

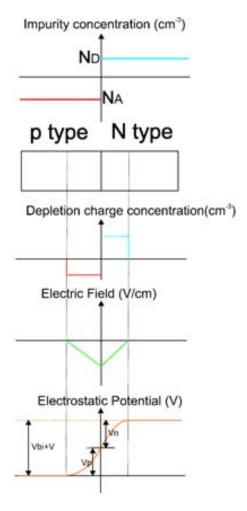

|      | P-N junction cross-section                                        | 40 |

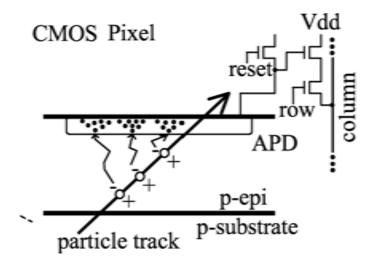

| 2.32       | Active pixel schematic                                                                                                                  | 48       |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

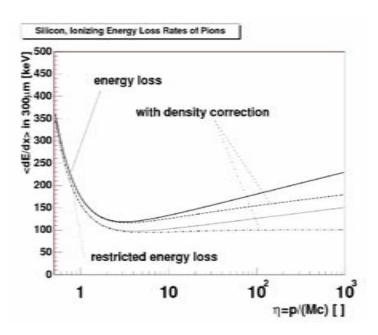

| 3.1        | Energy loss rate and restricted energy loss rate as a function of $\eta$ in Silicon                                                     | 55       |  |  |  |  |

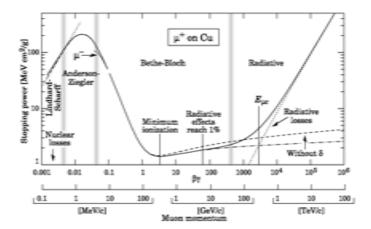

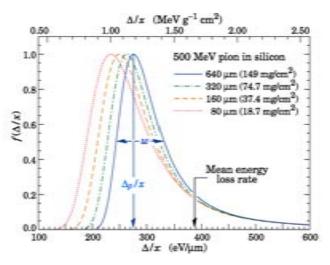

| 3.2<br>3.3 | Stopping power for positive muons in copper as a function of $\beta\gamma = p/Mc$ 5 Straggling functions in silicon for 500 MeV pions 5 |          |  |  |  |  |

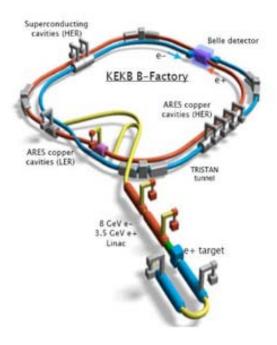

| 4.1        | General schematic Layout of KEKB                                                                                                        | 64       |  |  |  |  |

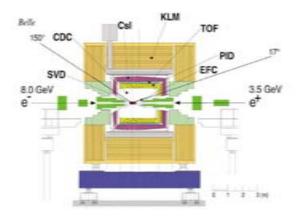

| 4.2        | Side View of the Belle Detector                                                                                                         | 64       |  |  |  |  |

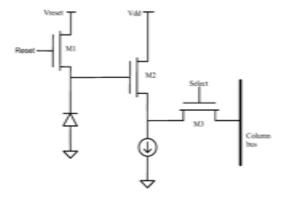

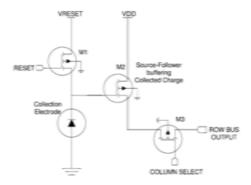

| 4.3        | Simple three-transistor cell, which is the basis of the CAP1 detector.  66 Schematic of a CAP2 pixel                                    |          |  |  |  |  |

| 4.4        | Schematic of a CAP2 pixel                                                                                                               |          |  |  |  |  |

| 4.5        | $4 { m GeV/c}$ pion track in the 4 layer detector configuration 70                                                                      |          |  |  |  |  |

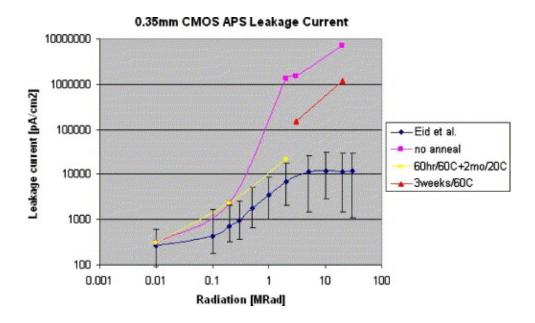

| 4.6        | Measured leakage current versus MeV gamma irradiation dose                                                                              | 71       |  |  |  |  |

| 5.1        | FE board with ADC converter, support electronics and connectors                                                                         | 75       |  |  |  |  |

| 5.2        | CAP3 prototype bonded to a separate board for use with the FE board.                                                                    | 75       |  |  |  |  |

| 5.3        | Back-End board (BE) ready to be used with 4 FE boards                                                                                   | 75       |  |  |  |  |

| 5.4        | Schematic used for CAP3 testing                                                                                                         | 76       |  |  |  |  |

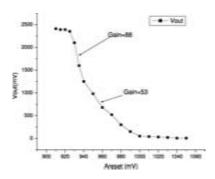

| 5.5        | Transfer function obtained from CAP3 testing                                                                                            | 76       |  |  |  |  |

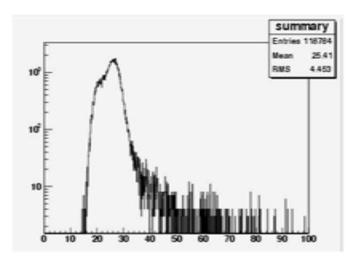

| 5.6        | Noise distribution for the 118,784 pixels of a CAP3 sensor                                                                              | 77       |  |  |  |  |

| 5.7        | Schematic of the DC Laser set-up configuration                                                                                          | 78       |  |  |  |  |

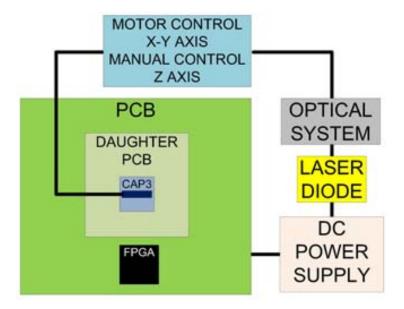

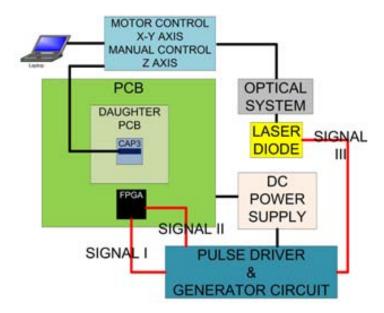

| 5.8        | Schematic of the Pulsed-Mode Laser set-up configuration                                                                                 | 79       |  |  |  |  |

| 5.9        | Measured output results when the PCB is covered                                                                                         | 80       |  |  |  |  |

| 5.10       | Measured output results when PCB is uncovered                                                                                           | 80       |  |  |  |  |

| 5.11       | Analysis of the pad performance firstorage cell number 1                                                                                | 81       |  |  |  |  |

| 5.12       | Analysis of the pad performance when using storage cell number 3.                                                                       | 81       |  |  |  |  |

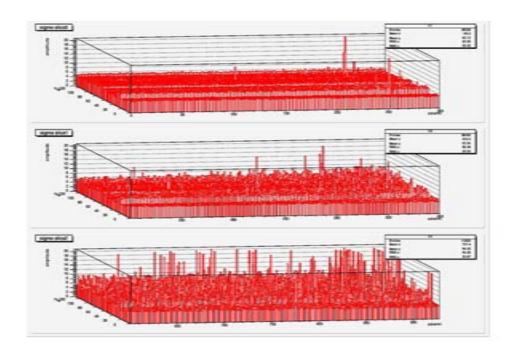

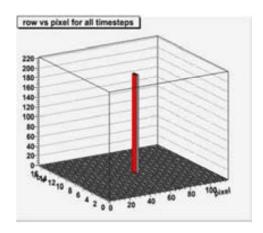

| 5.13       | Lego representation of a single event with a DC signal                                                                                  | 82       |  |  |  |  |

| 5.14       | 2D representation of a single event with a DC laser signal                                                                              | 82       |  |  |  |  |

| 5.15       | Analysis of the noise for 9 pixels depending on the storage cell                                                                        | 83       |  |  |  |  |

| 5.16       | Z-scan results using a DC laser signal to minimize the size of the laser                                                                |          |  |  |  |  |

|            | spot                                                                                                                                    | 84       |  |  |  |  |

|            | Intensity plot of the z-scan results I                                                                                                  | 85       |  |  |  |  |

|            | Intensity plot of the z-scan results II                                                                                                 | 85       |  |  |  |  |

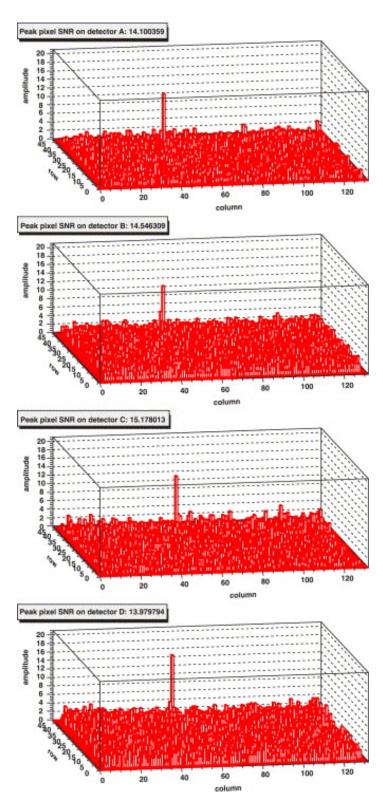

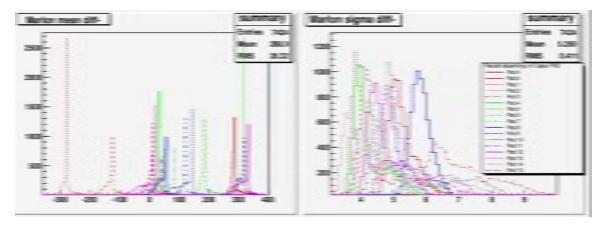

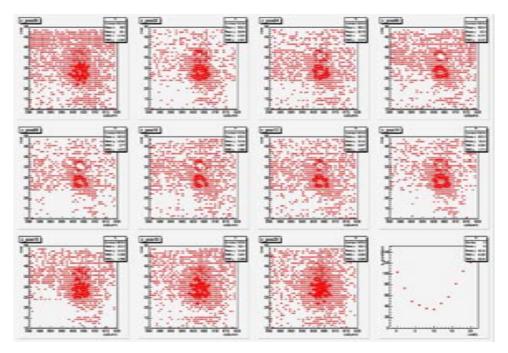

|            | Noise map of the complete CAP3                                                                                                          | 86       |  |  |  |  |

|            | Noise map of CAP3 rows 0-31                                                                                                             | 87       |  |  |  |  |

| 5.21       | Noise map of CAP3 rows 32-63                                                                                                            | 87       |  |  |  |  |

| 5.22       | Noise map of CAP3 rows 64-95                                                                                                            | 87       |  |  |  |  |

|            | Noise map of CAP3 rows 95-127                                                                                                           | 87       |  |  |  |  |

|            | Laser Signal for event 60                                                                                                               | 90       |  |  |  |  |

|            | Laser Signal calibrated for event 60                                                                                                    | 90       |  |  |  |  |

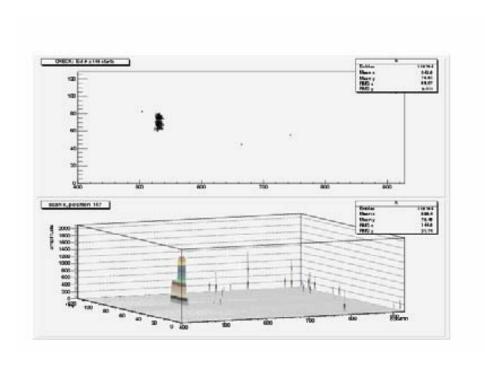

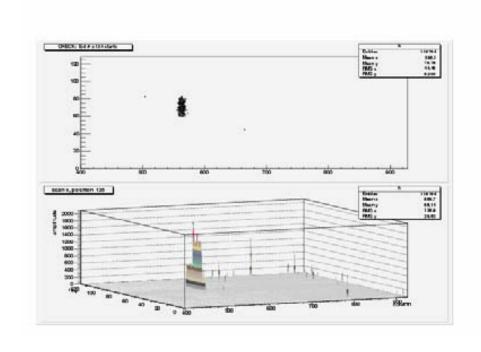

| 5.26       | Laser Signal for event 120                                                                                                              | 90       |  |  |  |  |

|            | Laser Signal calibrated for event 120                                                                                                   | 90       |  |  |  |  |

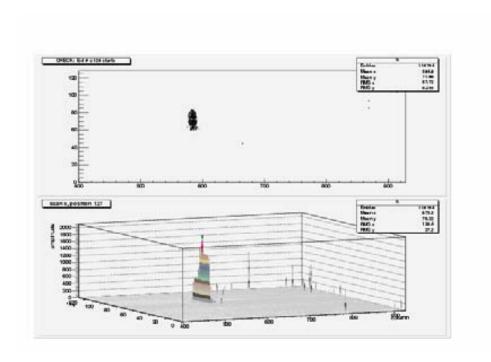

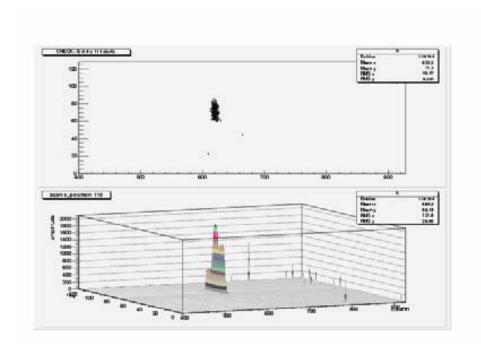

|            | Laser Signal for event 180                                                                                                              | 90       |  |  |  |  |

| 5.29       | Laser Signal calibrated for event 180                                                                                                   | 90       |  |  |  |  |

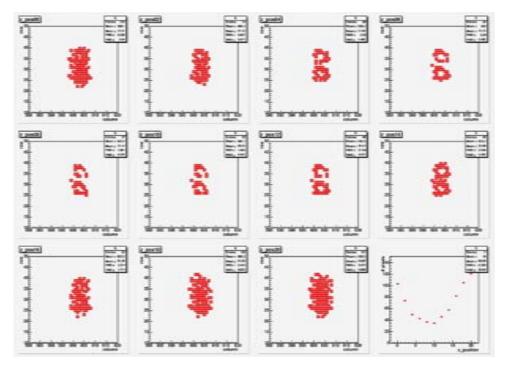

| 5.30       | Spot column and row number for the X scan                                                                                               | 91       |  |  |  |  |

|            | Excluded region for Event 60                                                                                                            | 91       |  |  |  |  |

|            | Excluded region for Event 180                                                                                                           | 91<br>91 |  |  |  |  |

| 3.33       | Excluded region for Event 180                                                                                                           | 91       |  |  |  |  |

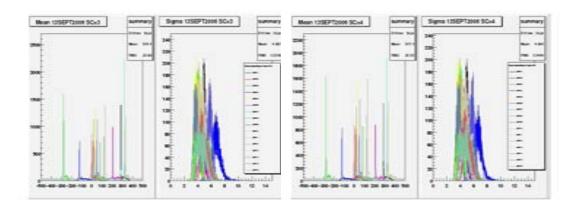

| 5.34 | 9 cells noise acquisition results                                        | 92  |

|------|--------------------------------------------------------------------------|-----|

|      | Noise results for pipeline data for storage cell 1                       | 93  |

|      | Noise results for pipeline data for storage cell 2                       | 93  |

|      | Noise results for pipeline data for storage cell 3                       | 93  |

|      | Noise results for pipeline data for storage cell 4                       | 93  |

|      | Noise results for pipeline data for storage cell 5                       | 93  |

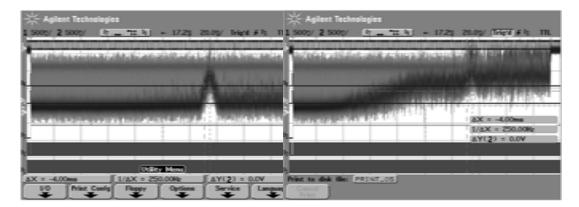

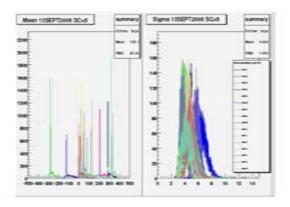

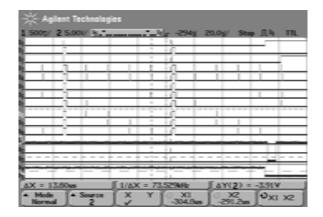

|      | Asynchronous trigger and laser for a $10\mu$ s laser pulse               | 94  |

|      | Asynchronous trigger and laser for a $2\mu$ s laser pulse                | 94  |

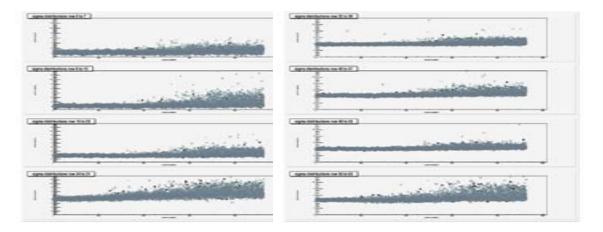

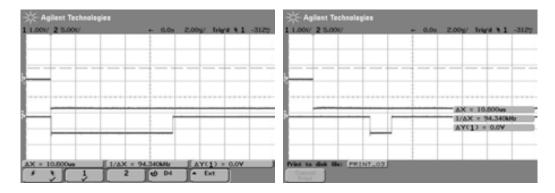

|      | Evolution of the total signal recorded as a function of the laser pulse  |     |

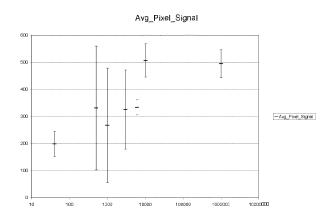

|      | width                                                                    | 95  |

| 5.43 | Evolution of the total signal recorded as a function of the laser pulse  |     |

|      | width II                                                                 | 95  |

| 5.44 | Average signal recorded as a function of the laser pulse width           | 96  |

|      | Evolution of the total signal recorded as a function of the laser pulse  |     |

|      | width I                                                                  | 96  |

| 5.46 | Evolution of the number of pixels passing the significance cut           | 97  |

|      | Average signal recorded in each firing pixel                             | 97  |

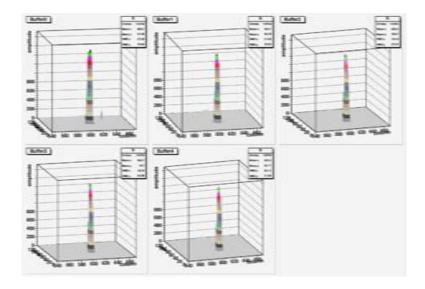

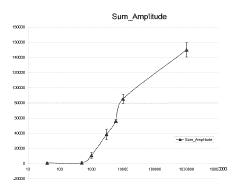

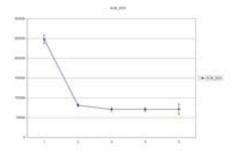

|      | Operating conditions for 1st tests of spillover                          | 99  |

|      | Sum of signal for Buffer 2 with significance greater than 10             | 100 |

|      | Pixel with significance above 10 for Buffer 2                            | 100 |

|      | Average signal recorded in a pixel above the significance of 10 for      |     |

|      | Buffer 2                                                                 | 100 |

| 5.52 | Buffer 2 read out although trigger was in window 1                       | 100 |

|      | Buffer 2 read out although trigger was in window 2                       | 100 |

|      | Buffer 2 read out although trigger was in window 3                       | 100 |

|      | Buffer 2 read out although trigger was in window 4                       | 101 |

|      | Buffer 2 read out although trigger was in window 5                       | 101 |

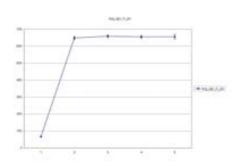

|      | Sum of signal for Buffer 3 with significance greater than 10             | 102 |

|      | Pixel with significance above 10 for Buffer 3                            | 102 |

|      | Average signal recorded in a pixel above a significance of 10 for Buffer |     |

|      | 3                                                                        | 102 |

| 5.60 | Buffer 3 read out although trigger was in window 1                       | 102 |

| 5.61 | Buffer 3 read out although trigger was in window 2                       | 102 |

| 5.62 | Buffer 3 read out although trigger was in window 3                       | 102 |

|      | Buffer 3 read out although trigger was in window 4                       | 103 |

|      | Buffer 3 read out although trigger was in window 5                       | 103 |

|      | Sum of signal for Buffer 4 with significance greater than 10             | 104 |

| 5.66 | Pixel with significance above 10 for Buffer 4                            | 104 |

|      | Average signal recorded in a pixel above a significance of 10 for Buffer |     |

|      | 4                                                                        | 104 |

| 5.68 | Buffer 4 read out although trigger was in window 1                       | 104 |

|      | Buffer 4 read out although trigger was in window 2                       | 104 |

|      | Buffer 4 read out although trigger was in window 3                       | 104 |

|      | Buffer 4 read out although trigger was in window 4                       | 105 |

|      | Buffer 4 read out although trigger was in window 5                       | 105 |

|      | Schematic representation of the signal depending on the trigger          | 106 |

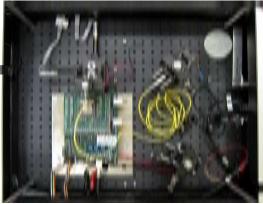

| 6.1  | Side view photograph of the laser set-up used and described in thi section.    |                   |  |  |

|------|--------------------------------------------------------------------------------|-------------------|--|--|

| 6.2  | Top view photograph of the laser set-up used and described in thi              |                   |  |  |

| 0.2  | section.                                                                       |                   |  |  |

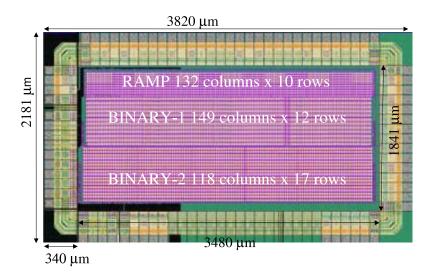

| 6.3  | Schematic view of CAP4 layout                                                  |                   |  |  |

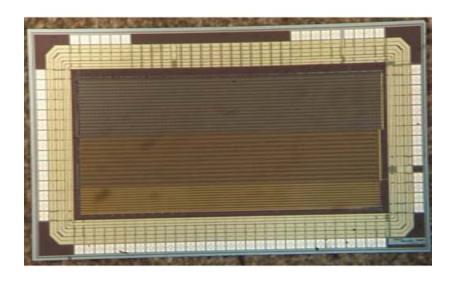

| 6.4  | Photograph from CAP4 using process AMS $0.35\mu m$                             |                   |  |  |

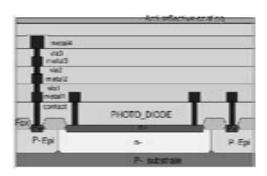

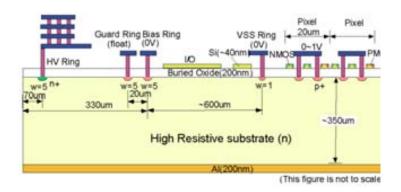

| 6.5  | Wafer Cross Section of the Opto $0.35\mu\mathrm{m}$ process                    |                   |  |  |

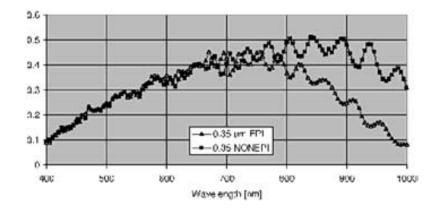

| 6.6  | Responsitivity of the CMOS-Opto $0.35\mu\mathrm{m}$ process of Austria MicroSy |                   |  |  |

|      | tems                                                                           |                   |  |  |

| 6.7  | Schematic for the calculation of the charge deposition                         | . 116             |  |  |

| 6.8  | Resolution simulation for different cluster sizes                              |                   |  |  |

| 6.9  | Detailed layout for the Wilkinson Pixel Cell, including dimensions.            | . 121             |  |  |

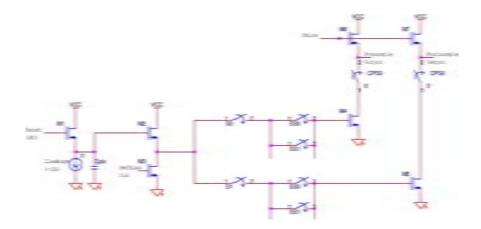

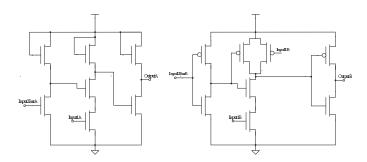

| 6.10 | Detailed schematic for the Wilkinson Solution                                  | . 122             |  |  |

| 6.11 | 3.3V Reset Results obtained with the Wilkinson Solution                        | 123               |  |  |

| 6.12 | 2.3V Reset Results obtained with the Wilkinson Solution                        | 123               |  |  |

| 6.13 | 1.3V Reset Results obtained with the Wilkinson Solution                        | . 124             |  |  |

| 6.14 | Signal distribution for 2.6V at Reset                                          | 124               |  |  |

| 6.15 | Voltage correspondence for ADC counts                                          | . 124             |  |  |

| 6.16 | Tree structure used for capacitor control at Wilkinson                         | 125               |  |  |

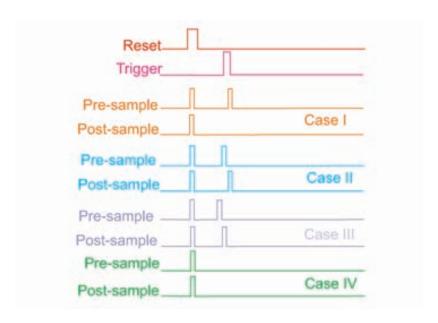

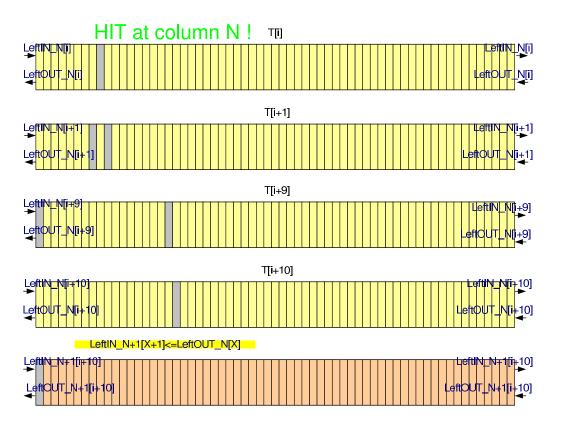

| 6.17 | Simple example of temporal behavior of the Binary architecture                 | 126               |  |  |

| 6.18 | Example for the calculation of 1 hit with 6 PUC                                | . 127             |  |  |

| 6.19 | Example for the calculation of 2 hits with 6 PUC                               | . 128             |  |  |

| 6.20 | Example for the calculation of 2 hits with 6 PUC with possible error           | or. 128           |  |  |

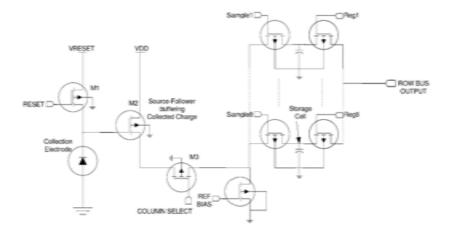

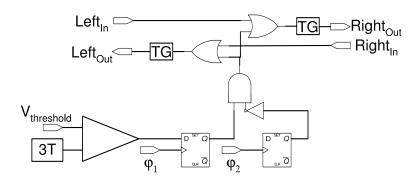

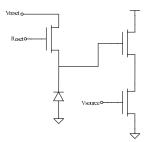

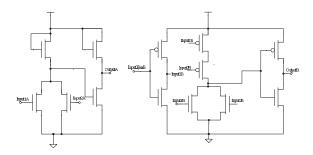

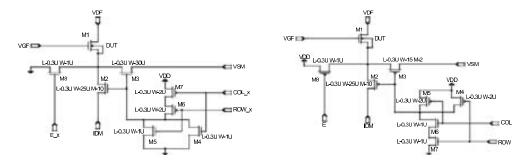

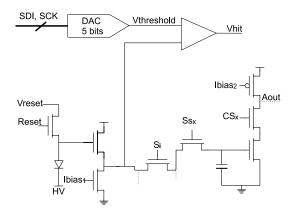

| 6.21 | Schematic of the basic pixel cell of the Binary architecture 129               |                   |  |  |

| 6.22 | Detailed layout for the NMOS Binary Pixel Cell, including dimension            | $\mathrm{ns.}130$ |  |  |

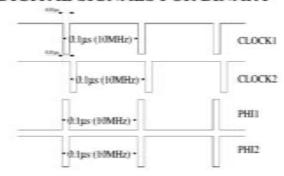

| 6.23 | Detailed timing scheme for the digital signals                                 | . 131             |  |  |

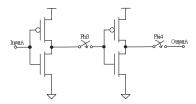

| 6.24 | 3T structure schematic                                                         | . 131             |  |  |

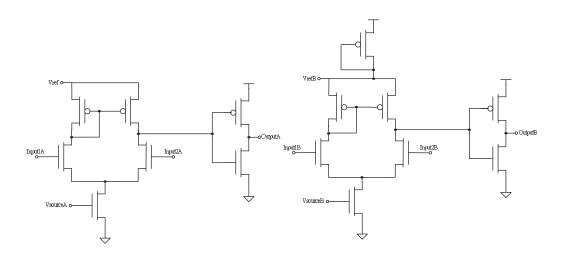

| 6.25 | Comparator schematic for NMOS (left) and CMOS (right)                          | . 132             |  |  |

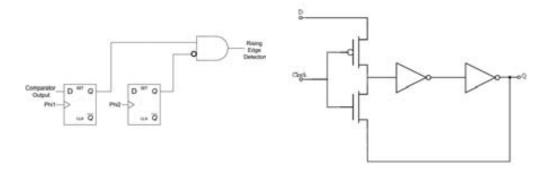

| 6.26 | Rising Edge detector schematic                                                 | 133               |  |  |

| 6.27 | Register schematic                                                             | 133               |  |  |

| 6.28 | AND Gate with 1 inverted input schematic for NMOS (left) and                   | d                 |  |  |

|      | CMOS (right)                                                                   | . 133             |  |  |

| 6.29 | OR Gate schematic for NMOS (left) and CMOS (right)                             | . 134             |  |  |

| 6.30 | Transmission Gate schematic for NMOS and CMOS                                  | . 134             |  |  |

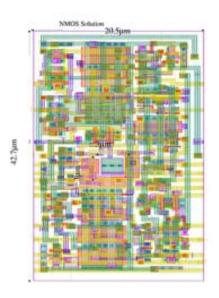

| 6.31 | Detailed layout for the CMOS Binary Pixel Cell, including dimension            | ${ m ns.136}$     |  |  |

| 6.32 | Plot obtained for 1 Hit in the CMOS Pixel architecture                         | . 137             |  |  |

| 6.33 | Top View of Cut Package                                                        | . 138             |  |  |

| 6.34 | Top View of Bad Cut Package                                                    | . 138             |  |  |

| 6.35 | Bottom View of Bad Cut Package                                                 | . 138             |  |  |

| 6.36 | Top View of epoxied Package                                                    | . 138             |  |  |

| 6.37 | Zig-zag test performed with CMOS Binary                                        | . 140             |  |  |

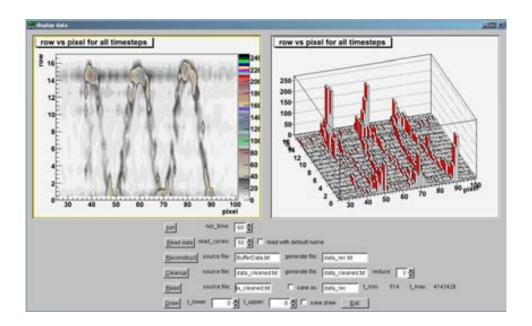

|      | Pre-filter image obtained                                                      |                   |  |  |

| 6.39 | Post-filter image obtained                                                     | . 141             |  |  |

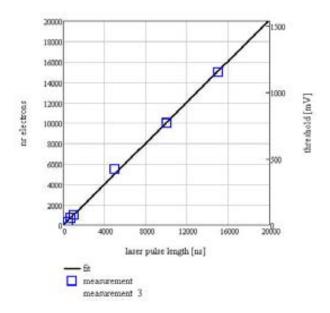

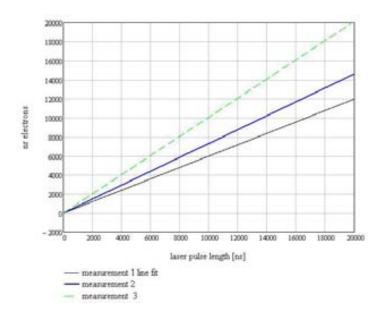

| 6.40 | Threshold Value vs Laser pulse length                                          | . 142             |  |  |

| 6.41 | Threshold Value vs Laser pulse length                                          | . 143             |  |  |

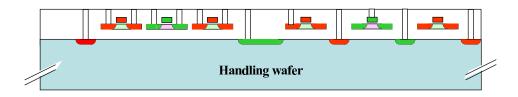

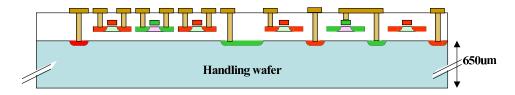

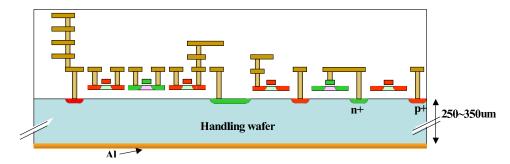

| 7.1  | Two different diode structures analyzed to test the handle wafer               | . 146             |  |  |

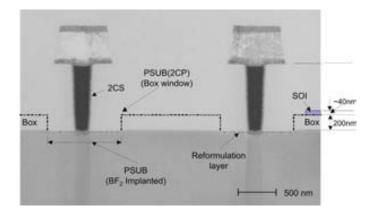

| 7.2  | TEM photographs of the contacts and implants of the handle wafer.              | 146  |

|------|--------------------------------------------------------------------------------|------|

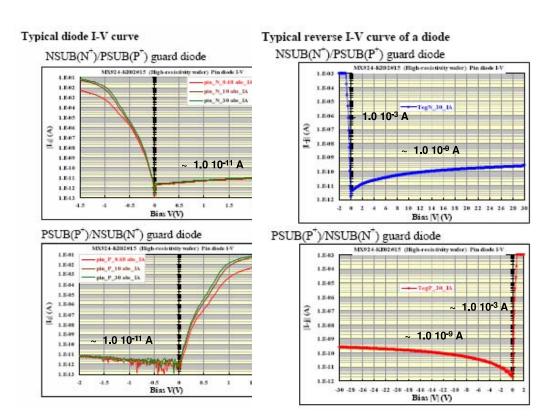

| 7.3  | Typical diode I-V curve for the n-substrate                                    | 147  |

| 7.4  | Typical reverse I-V curve for the n-substrate                                  | 147  |

| 7.5  | Typical diode I-V curve for the n-substrate                                    | 148  |

| 7.6  | Typical diode C-V curve for the n-substrate                                    | 148  |

| 7.7  | After Gate formation for CMOS processing the stack formation takes             |      |

|      | place                                                                          | 150  |

| 7.8  | Photolithography and etching                                                   | 150  |

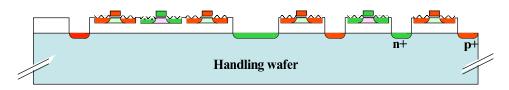

| 7.9  | S/D Implantation followed by S/D annealing and Salicidation                    | 150  |

| 7.10 | 1 <sup>st</sup> ILD filling and CMP planarization (after Salicide formation)   | 150  |

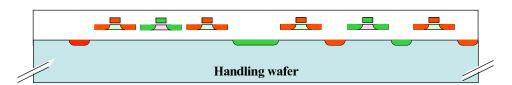

| 7.11 | Contact etching (for gate of transistor and for substrate)                     | 150  |

| 7.12 | Contact plug filling and $1^{st}$ Metal formation                              | 151  |

|      | 5 Metal layer formation followed by Backside polishing and Au coat-            |      |

|      | ing                                                                            | 151  |

| 7.14 | TEM photograph of the p <sup>+</sup> implant and contact cross section         | 152  |

| 7.15 | I/O buffer layout, improved with Guard Ring consisting of a p+ im-             |      |

|      | plantation.                                                                    | 152  |

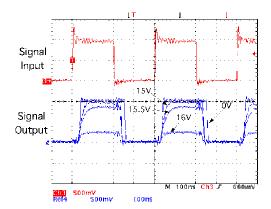

| 7.16 | Signal obtained with the buffer, with no p+ implantation                       | 152  |

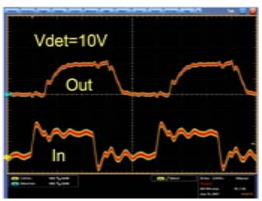

| 7.17 | Buffer signal, with p+ implantation, detectable for $V_{bq} \sim 10 V$         | 153  |

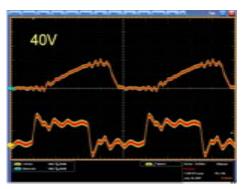

|      | Buffer signal, with p+ implantation, detectable for $V_{ba} \sim 40 \text{ V}$ | 153  |

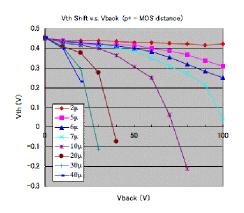

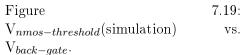

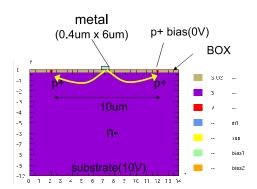

| 7.19 | $V_{nmos-threshold}(simulation)$ vs. $V_{back-gate}$ .                         | 153  |

| 7.20 | Schematic of the structure used to analyze the cross-talk                      | 153  |

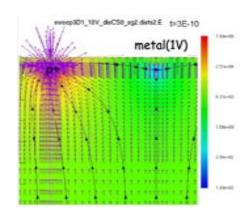

| 7.21 | Potential distribution around a p+ sensor node simulated using ENEXS           | S[1] |

|      |                                                                                | 154  |

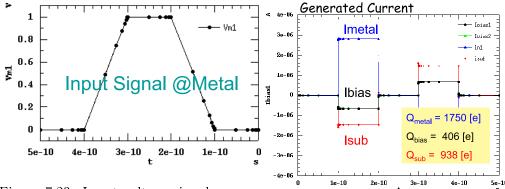

| 7.22 | Electric field map and lines of electric force around a $p+$ sensor            | 154  |

| 7.23 | Input voltage signal applied to top metal layer                                | 154  |

| 7.24 | Output current (and charge injection) result                                   | 154  |

| 7.25 | NMOS transistor circuit                                                        | 155  |

| 7.26 | PMOS transistor circuit                                                        | 155  |

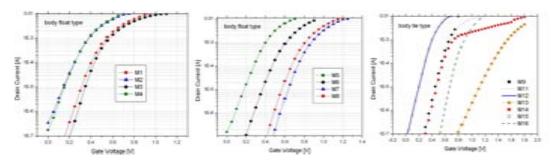

| 7.27 | $I_{drain}$ for $M_1$ - $M_4$ , Table 7.2 for details.                         | 158  |

| 7.28 | $I_{drain}$ for $M_5$ - $M_8$ , Table 7.2 for details                          | 158  |

|      | $I_{drain}$ fpr $M_9$ - $M_{16}$ , Table 7.2 for details                       | 158  |

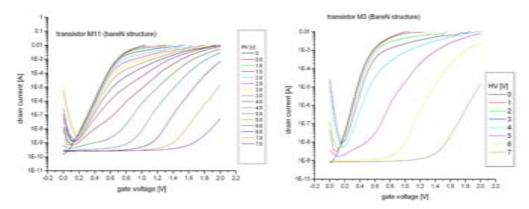

| 7.30 | $I_{ds} \ vs \ V_{gs}$ for transistor M11                                      | 158  |

| 7.31 | $I_{ds} \ vs \ V_{gs}$ for transistor M3                                       | 158  |

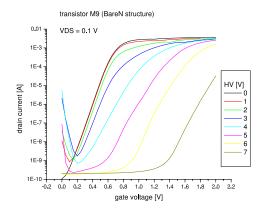

| 7.32 | $I_{ds}$ versus $V_{gs}$ for transistor M9                                     | 159  |

| 7.33 | $I_{ds}$ versus $V_{gs}$ for transistor M9                                     | 159  |

| 7.34 | $I_{ds}$ versus $V_{gs}$ for transistor M12                                    | 160  |

| 7.35 | $I_{ds}$ versus $V_{gs}$ for transistor M12                                    | 160  |

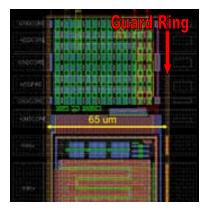

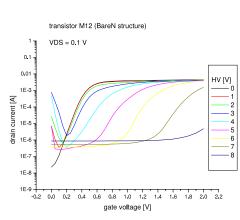

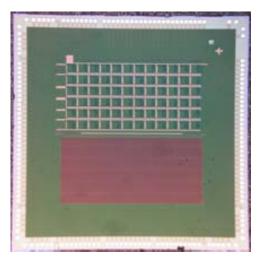

| 7.36 | General Layout submitted for fabrication using process OKI $0.15 \mu m$ .      | 164  |

| 7.37 | Dimension schematic corresponding to the Guard Ring present in the             |      |

|      | SOI chip                                                                       | 165  |

| 7.38 | Example of Hit signal transmission through the pixel detector                  | 166  |

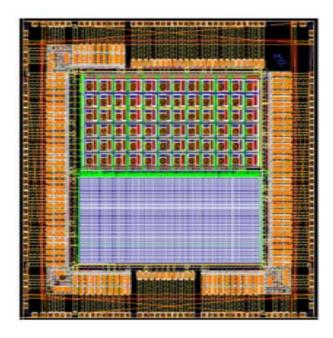

| 7.39 | General micrograph of the SOI chip                                             | 166  |

| 7.40 | General photograph of the SOI chip setup                                       | 166  |

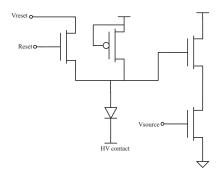

| 7.41 | Modified 3T transistor structure used in CAP5                                  | 167  |

| 7.42 | Simulation of the electrode at different leakage current                       | 167  |

| 7.43 | Schematic for the Transfer Cell                                                | 167  |

| 7.44 | 6 Cell Simulation with Tanner                                                 | 7 |  |  |  |

|------|-------------------------------------------------------------------------------|---|--|--|--|

| 7.45 | 6 Cell schematic Simulation                                                   | 3 |  |  |  |

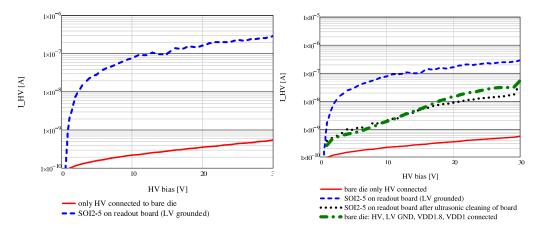

| 7.46 | Leakage current measurement comparison for 2 different implants 170           | J |  |  |  |

| 7.47 | Leakage current for the standard implant                                      | 1 |  |  |  |

| 7.48 | Leakage current for the standard implant                                      |   |  |  |  |

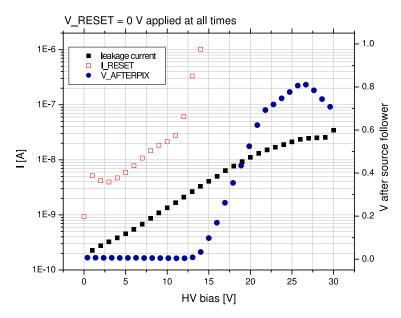

| 7.49 | $V_{AfterPixel}$ for HV>13 V for constant reset                               | 2 |  |  |  |

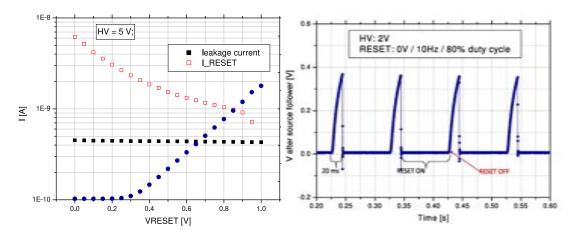

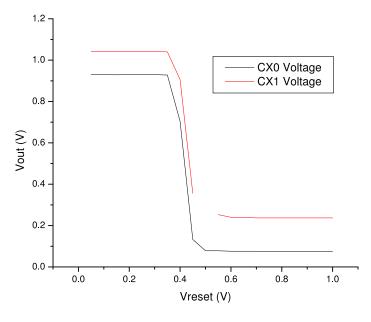

|      | $V_{After Pixel}$ after the source follower with a sweep over reset level 173 | 3 |  |  |  |

|      | Signal after source follower for a slow pulsed reset                          | 3 |  |  |  |

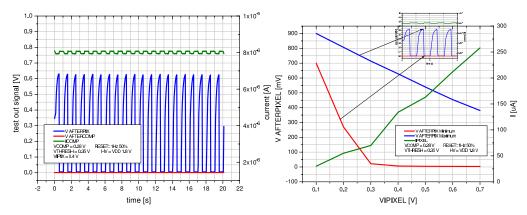

|      | Comparator output with a pulsed reset signal of 1 Hz                          | 4 |  |  |  |

|      | Detail of Fig. 7.52 with same conditions                                      | 4 |  |  |  |

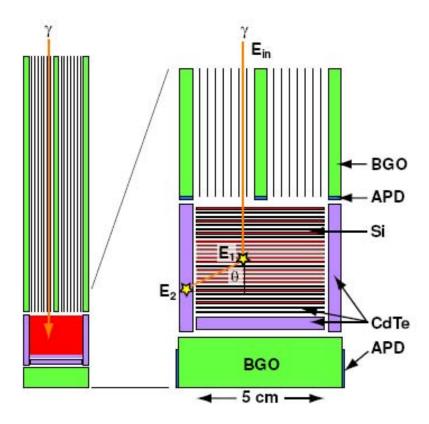

|      | The Imaging Hard X-ray Compton Polarimeter (IHXCP) concept 17                 | 7 |  |  |  |

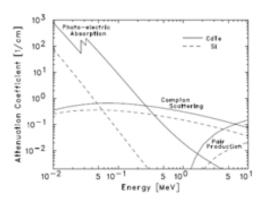

|      | Linear attenuation coefficients in Si and CdTe                                | 3 |  |  |  |

| 7.56 | An example of polarization determination as a function of scattering          |   |  |  |  |

|      | angle                                                                         | 3 |  |  |  |

| 7.57 | Schematic of the n-type substrate sensor architecture                         | 3 |  |  |  |

|      | Transfer curve of XRAY testing structure                                      | 9 |  |  |  |

| 7.59 | Register results for HV=3V                                                    | ) |  |  |  |

|      | Register results for HV=7V                                                    | ) |  |  |  |

| 7.61 | Register results for HV=8V                                                    | 1 |  |  |  |

| 7.62 | Register results for HV=9V                                                    | 1 |  |  |  |

| 7.63 | Register results for HV=10V                                                   | 1 |  |  |  |

|      | Register results for HV=11V                                                   | 1 |  |  |  |

|      |                                                                               |   |  |  |  |

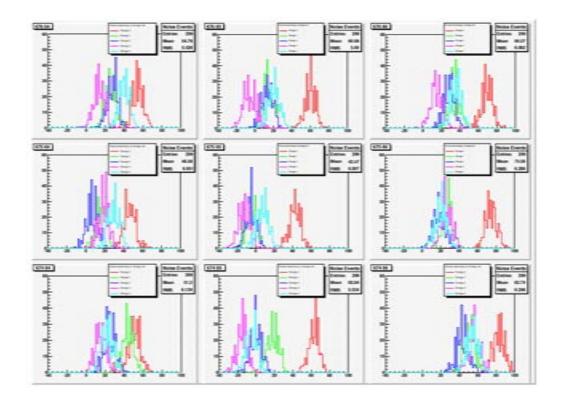

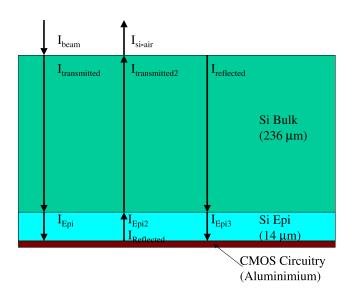

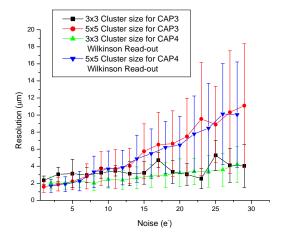

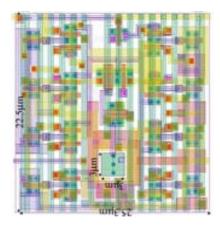

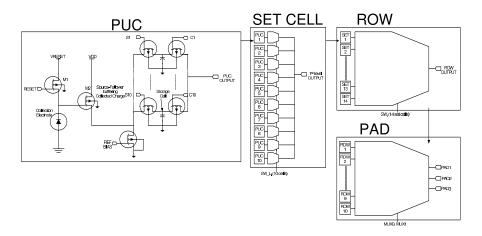

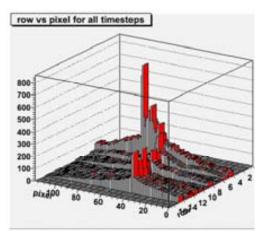

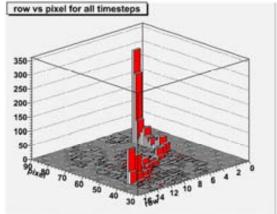

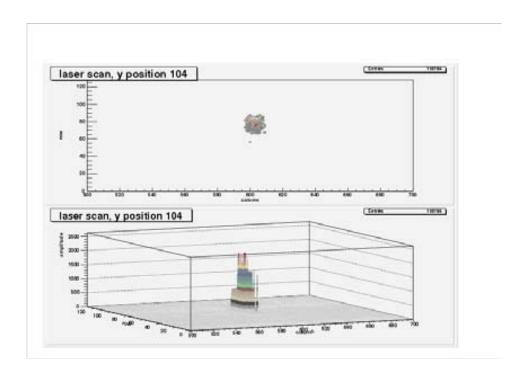

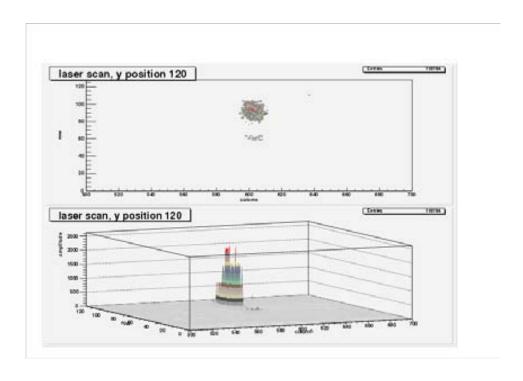

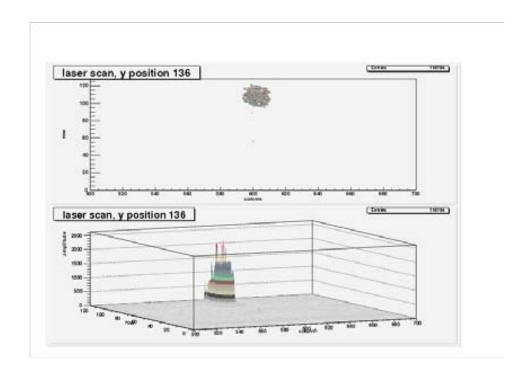

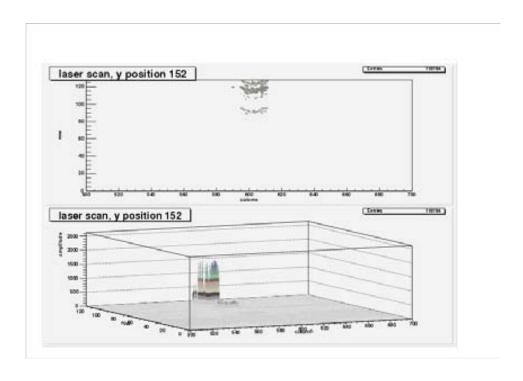

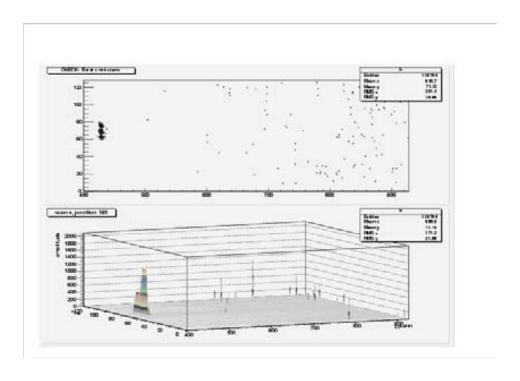

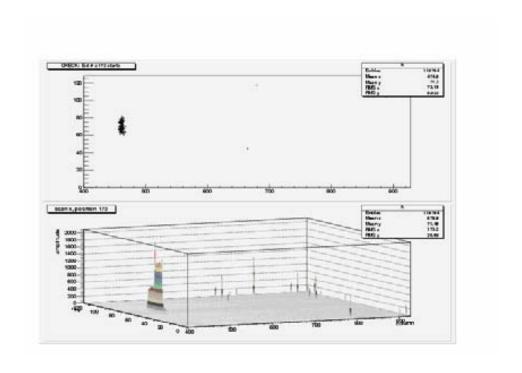

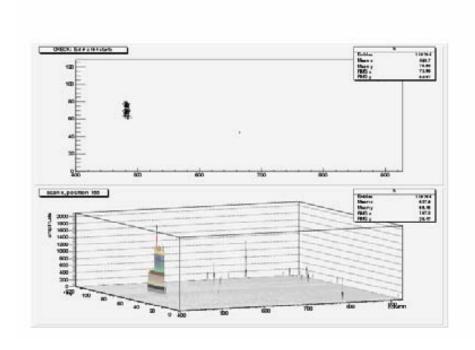

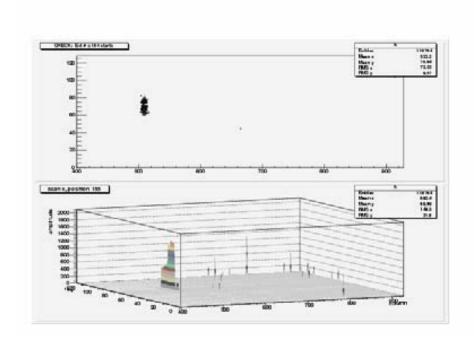

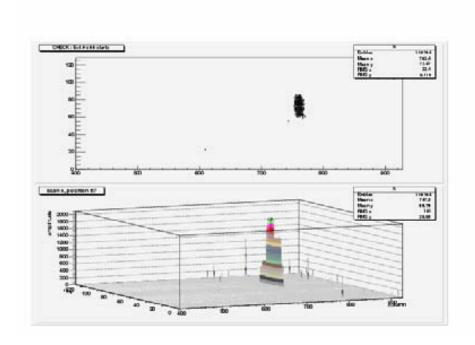

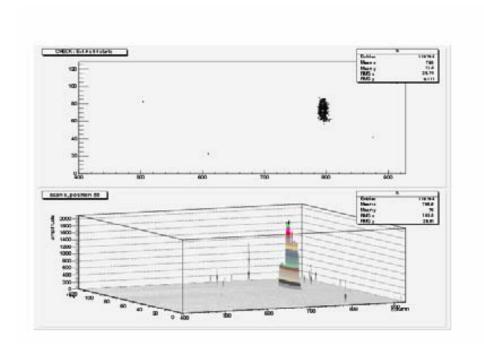

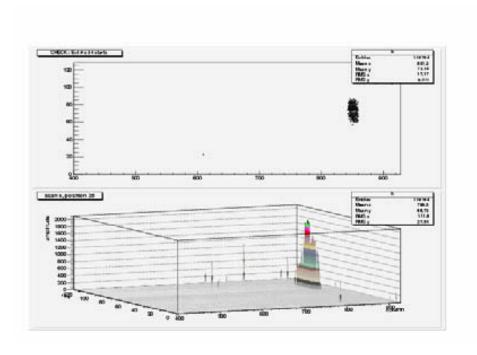

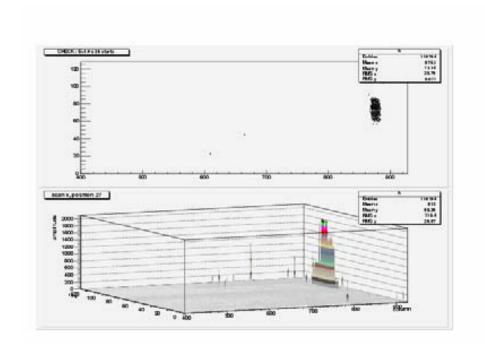

| A.1  | Pos 008 of y axis scan                                                        |   |  |  |  |