## **Contents**

| List of Publications                                                   | 5  |

|------------------------------------------------------------------------|----|

| List of Symbols                                                        | 10 |

| List of Figures                                                        | 16 |

| Chapter 1                                                              |    |

| State of the Art and Current Trends for Multiple Gate MOS Devices      |    |

| 1A. Introduction                                                       | 25 |

| 1B. Compact modeling                                                   | 35 |

| 1C. Numerical simulations                                              | 41 |

| 1D. Capacitance model                                                  | 42 |

| Chapter 2                                                              |    |

| Current, Charge and Capacitance Model for Multiple Gate MOSFETs        |    |

| 2A. Compact model for highly-doped symmetrical Double Gate SOI MOSFETs |    |

| 2A.1. Introduction                                                     | 50 |

| 2A.2. Model                                                            | 53 |

| 2A.2.1 Drain Current Model                                             | 58 |

| 2A.2.2 Charge and Capacitance Model                                    | 68 |

| 2A.2.3 Simulation Results                                                                    | 69  |

|----------------------------------------------------------------------------------------------|-----|

| 2A.3 Continuous modeling of symmetrical DG M from low to high doping values                  |     |

| 2A.3.1 Introduction                                                                          | 77  |

| 2A.3.2 Formulation of the Poisson's equation                                                 | 79  |

| 2A.3.3 Calculation of the potentials                                                         | 82  |

| 2A.3.4. Derivation of the drain current and                                                  |     |

| charge models                                                                                | 91  |

| 2A.3.5 Simulation Results                                                                    | 94  |

| 2B. Compact model for undoped symmetrical Dou SOI MOSFETs, including Volume Inversion regime |     |

| characterization                                                                             | 100 |

| 2B.1. Introduction                                                                           | 101 |

| 2B.2. Compact Model of a symmetrical undoped                                                 |     |

| MOSFET                                                                                       |     |

| 2B.2.1 Drain Current Model                                                                   | 104 |

| 2B.2.2. Charge and Capacitance Model                                                         | 108 |

| 2B.2.3 Simulation Results                                                                    | 114 |

| 2B.3 Volume Inversion impact on symmetrical u<br>DG MOSFETs' capacitances                    | _   |

| 2B.3.1 Volume-Inversion Effect                                                               |     |

| 2B.3.2 Simulation results                                                                    |     |

|                                                                                              |     |

| 2B.4. Short Channel Effects in symmetrical undo                                              | •   |

| MOSFETs                                                                                      | 131 |

| 2B.4.1. Model                                                                                | 131 |

| 2B.4.2.Simulation Results                                                             | 146 |

|---------------------------------------------------------------------------------------|-----|

| 2C. Compact model for undoped Ultra-Thin-Body (UT MOSETs                              |     |

| 2C.1. Introduction                                                                    | 155 |

| 2C.2 Model                                                                            | 157 |

| 2C.2.1. Explicit Drain-Current Model                                                  | 159 |

| 2C.2.2. Charge and Capacitance Model                                                  | 162 |

| 2C.3. Simulation Results                                                              | 166 |

| 2D. Compact model for undoped cylindrical Surroundin Gate MOSFETs                     | •   |

| 2D.1. Introduction                                                                    | 171 |

| 2D.2. Model                                                                           | 172 |

| 2D.2.1 Drain Current Model                                                            | 174 |

| 2D.2.2 Charge and Capacitance Model                                                   | 176 |

| 2D.3 Simulation Results                                                               | 178 |

| Chapter 3                                                                             |     |

| Parasitic Capacitances Related to Multiple-Gate Field-Eff<br>Transistor Architectures | ect |

| 3.1. Introduction                                                                     | 186 |

| 3.2. Capacitance Analysis                                                             | 187 |

| 3.2.1. Integration level                                                              | 192 |

| 3.2.2 Impact of SEG technology                                                        | 193 |

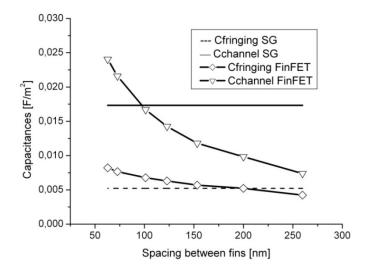

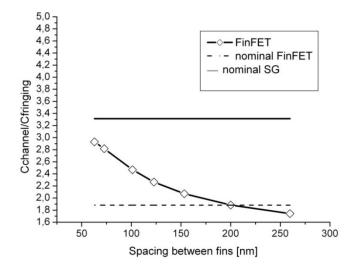

| 3.2.3 Impact of fin spacing                                                           | 195 |

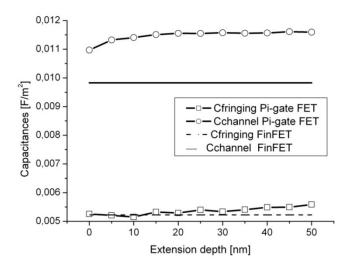

| 3.2.4 Impact of gate extension depth into the BOX                                     | 197 |

| UNIVERSITAT ROVIRA I VIRGILI                                                                                  |

|---------------------------------------------------------------------------------------------------------------|

| DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFETS                            |

| Oana Moldovan                                                                                                 |

| ISBN: 978-84-691-8839-2/DL: T-1263-2008<br>Development of Compact Small-Signal Quasi Static Models for MuGFET |

| Development of Compact Small-signal Quasi Static Models for Mudf En                                           |

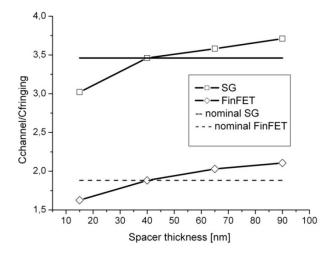

| 3.2.5 Impact of spacer width                    | 197 |  |

|-------------------------------------------------|-----|--|

| 3.3. Cutoff Frequencies                         | 199 |  |

| Chapter 4                                       |     |  |

| Conclusions and recommendations for future work |     |  |

| 4.1 Conclusions                                 | 211 |  |

| 4.2 Recommendations for future work             | 217 |  |

| Appendix                                        | 219 |  |

| References                                      | 223 |  |

### **List of Publications**

#### International Journals

- 1. "Accurate Prediction of the Volume Inversion impact on Undoped DG MOSFETs' Capacitances", **Oana Moldovan**, Ferney A. Chaves, David Jiménez, Jean-Pierre Raskin and Benjamin Iñiguez- submitted

- 2. "A quasi two-dimensional compact drain current model for undoped symmetric double gate MOSFETs including short-channel effects", F. Lime, B.Iñiguez and **O. Moldovan** accepted for publication in *IEEE Transaction on Electron Devices*

- 3." Compact Charge and Capacitance Modeling of Undoped Ultra-Thin-Body (UTB) SOI MOSETs", **Oana Moldovan**, Ferney A. Chaves, David Jiménez and Benjamin Iñiguez-accepted for publication in *Solid-State Electronics*

- 4. "Modeling of Potentials and Threshold Voltage for Symmetric Doped Double-Gate MOSFETs", Antonio Cerdeira, **Oana Moldovan**, Benjamín Iñiguez and Magali Estrada, *Solid-State Electronics*, Vol. 52, Issue 5, May 2008

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

- 5. "Explicit Analytical Charge And Capacitance Models Of Undoped Double Gate MOSFETs", Oana Moldovan, David Jiménez, Jaume Roig, Ferney A. Chaves and Benjamin Iñiguez, IEEE Transaction on Electron Devices, Vol. 54, no. 7, July 2007

- 6. "Compact Model For Doped Double-Gate MOSFETs targeting baseband analog applications", Oana Moldovan, Antonio Cerdeira, David Jiménez, Jean-Pierre Raskin, Valeria Kilchytska, Denis Flandre, Nadine Collaert, and Benjamin Iñiguez, Solid-State Electronics, Vol.51, Issue 5, May 2007

- 7. "Analytical Charge And Capacitance Models Of Undoped Cylindrical Surrounding Gate MOSFETS", Oana Moldovan, Benjamin Iñiguez, David Jiménez and Jaume Roig, IEEE Transaction on Electron Devices, Vol. 53, no. 1, January 2007

- 8. "A Compact Quantum Model of Nanoscale Double-Gate MOSFET for High Frequency and Noise Simulations", A.Lázaro, B.Nae, O. Moldovan, B.Iñiguez, Journal of Applied Physics, Vol. 100, N.8, Oct. 2006

#### • International Conferences

- 1. "Compact Charge and Capacitance Modeling of Undoped Ultra-Thin-Body (UTB) SOI MOSETs", Oana Moldovan, Ferney A. Chaves, David Jiménez and Benjamin Iñiguez, *EUROSOI* Fourth Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits, Tyndall National Institute, Cork, Ireland, Jan 23-25th, 2008

- 2."Finite Element Simulations of Parasitic Capacitances Related to Multiple-Gate Field-Effect Transistors Architectures", O. Moldovan, D. Lederer, B. Iñiguez, J.-P. Raskin, 8<sup>th</sup> Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF 2008), Orlando, Florida, USA, January 23-25, 2008

- 3."A New Explicit Compact Charge And Capacitance Model For Undoped Symmetric Double Gate MOSFETs", Oana Moldovan, Benjamin Iñiguez, David Jiménez and Jaume Roig, Walk-in Poster at the *Conference on Simulation of Semiconductor Devices and Processes (SISPAD), Vienna, Austria*, September 25-27, 2007

- 4."Charge-Based Compact Modeling of Multiple-Gate MOSFETs", B. Iñiguez, A. Lázaro, H. Abd-ElHamid, **O. Moldovan**, B. Nae, J. Roig, D. Jiménez, *IEEE Custom Integrated*

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

Circuits Conference (CICC), San José (California, USA),

September 16-19, 2007

- 5."Compact Model for Long-Channel Symmetric Doped DG MOSFETs", A. Cerdeira, O. Moldovan, B. Iñiguez and M. Estrada, Poster at MOS-AK/ESSDERC/ESSCIRC Workshop, Munich, Germany, September 14, 2007

- 6."Compact Model for Symmetric Doped Double-Gate MOSFETs including SCE", A. Cerdeira, O. Moldovan, J. Alvarado, B. Iñiguez and M. Estrada - EUROSOI 2007, Third Workshop of the Thematic Network on Silicon on Insulator technology, devices and circuits, Leuven, Belgium, January 24 -26, 2007

- 7. "Compact Model of Double-Gate MOSFETs for Low Power Analog Applications", Oana Moldovan, Antonio Cerdeira, David Jiménez, Jean-Pierre Raskin, Denis Flandre, Nadine Collaert, Benjamin Iñiguez - XXI Conference on Design of Circuits and Integrated Systems, Barcelona, Spain, November 22-24, 2006

- 8. "Compact RF modeling of multiple gate MOSFETs", Benjamín Iñiguez, Antonio Lázaro and Oana Moldovan, European Microwave Week, Manchester, UK, September 10-15 2006

9. "DC to RF Small-Signal Compact DG MOSFET model", B. Iñíguez, A.Lázaro, **O. Moldovan**, A. Cerdeira and T.A. Fjeldly, *NSTI Nanotechnology Conference and Trade Show - Nanotech* 2006 – Boston, Massachusetts, U.S.A., May 7-11, 2006

## **List of Symbols**

- ρ charge density

- $\phi$  potential

- $\beta$  thermal potential

- $\phi d$  potential difference at any voltage

- $\phi d_{BT}$  potential difference below threshold

- $\phi d_M$  potential difference at  $V_{GM}$

- $\phi d_T$  potential difference at threshold

- $\mu_{eff}$  effective mobility with series resistance

- $\phi_F$  Fermi level

- $\phi_{Fn}$  quasiFermi level for electrons

- $\phi_{Fp}$  quasiFermi level for holes

- $\phi o$  potential at the center of the Si layer

- $\phi o_{BT}$  potential at the center of the Si layer below threshold

- $\phi o_T$  potential at the center of the Si layer at threshold

$\epsilon_{ox}$  gate dielectric constant

$\phi s$  surface potential

$\phi s_{BT}$  surface potential below threshold

$\epsilon_{Si}$  Si dielectric constant

$\phi s_T$  surface potential at threshold

$\Delta L$  length of the saturation region

μ electron mobility

$\mu_0$  low field mobility

$\mu_{eff}^{0}$  effective mobility without series resistance

A actual occupied planar silicon die area

C<sub>dg</sub> drain-gate capacitance

C<sub>ds</sub> drain-source capacitance

C<sub>f</sub> fringing capacitance

C<sub>gd</sub> gate-drain capacitance

C<sub>gg</sub> total gate capacitance

C<sub>gs</sub> gate-source capacitance

C<sub>ov</sub> overlap capacitance

Oana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

gate capacitance per unit area

$C_{sd}$ source -drain capacitance

$C_{sg}$ source -gate capacitance

$C_{Si}$ Si layer capacitance per unit area

longitudinal electric field at the drain  $E_{ld}$

Es surface electric field

maximum available gain cutoff frequency

$f_T$ current gain cutoff frequency

fin height in FinFETs  $h_{fin}$

drain current  $I_{DS}$

k Boltzmann constant

L transistor channel length

Lambert function LW

Si layer doped concentration  $N_A$

$N_{\mbox{\scriptsize Amax}}$  Na at the maximum of the potential at the center

electron concentration  $n_{e}$

N<sub>fin</sub> number of fins in FinFETs

n<sub>i</sub> intrinsic carrier concentration

N<sub>poly</sub> polysilicon layer doped concentration

N<sub>ss</sub> surface state concentration

- p hole concentration

- Q induced charge carriers

- q electron charge

- Q<sub>B</sub> total back gate charge

- Q<sub>d</sub> induced charge carriers at the drain

- Q<sub>D</sub> total drain charge

- q<sub>D</sub> normalized depletion charge

- q<sub>d</sub> normalized induced charge at the drain

Q<sub>Dep</sub> modulus of the total depletion charge in the Si layer

- Q<sub>F</sub> total front gate charge

- Q<sub>G</sub> total inversion charge at gate

- Q<sub>m</sub> mobile charge in the saturated region

- Q<sub>S</sub> total source charge

- $Q_{s}$ induced charge carriers at the source

- $q_{s}$ normalized induced charge at the source

- total inversion charge  $Q_{Tot}$

- S<sub>fin</sub> fins spacing in FinFETs

- T temperature

- gate dielectric thickness  $t_{ox}$

- polysilicon thickness

- Si layer thickness  $t_{Si}$

- V potential along the channel

- $V_{bi}$ source and drain junction built-in voltage

- V<sub>DS</sub> drain voltage

- V<sub>E</sub> Early voltage

- V<sub>FB</sub> flat band voltage

- V<sub>GB</sub> back gate voltage

- V<sub>GM</sub> maximum analyzed gate voltage

- V<sub>GS</sub> gate voltage

V<sub>sat</sub> saturation potential

v<sub>sat</sub> saturation velocity

V<sub>t</sub> threshold voltage

W channel width

$W_{\text{fin}} \quad \text{fin width in FinFETs} \quad$

$\Delta\phi$   $\,\,$  work function difference between the gate electrode and the intrinsic silicon

$\lambda_{DIBL}$  characteristic length for the DIBL

- $\theta_1$  mobility attenuation coefficients of the first order

- $\theta_2$  mobility attenuation coefficients of the second order

# **List of Figures**

| Fig.1A.1 A Fully depleted SOI MOSFET, B-Partially depleted SOI MOSFET                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Fig.1A.2 The schematic device structures of MuGFETs28                                                                                   |

| Fig.1A.3 Dependence of cut-off frequency of DG and SG devices for various channel lengths                                               |

| Fig.1A.4 Schematic of a single-gate UTB SOI MOSFET34                                                                                    |

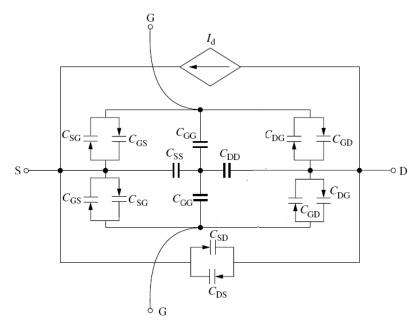

| Fig.1D.1.1 Intrinsic large-signal DG MOSFET equivalent circuit                                                                          |

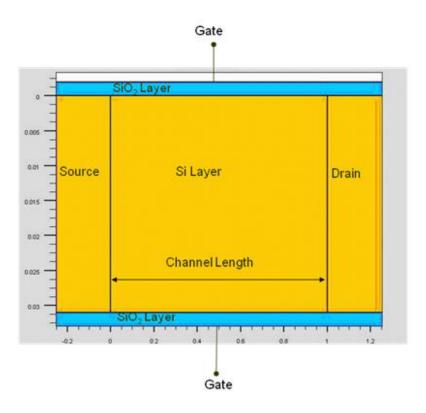

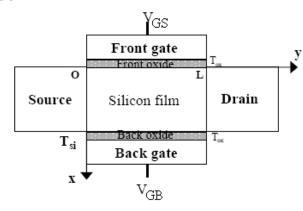

| Fig.2A.1 ATLAS simulation of the DG MOSFET considered 54                                                                                |

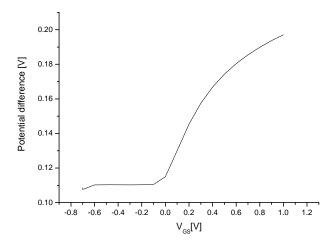

| Fig.2A.2 Difference between the surface and mid-film potentials $\phi_S - \phi_0$ of the DGMOSFET, as a function of the gate voltage 58 |

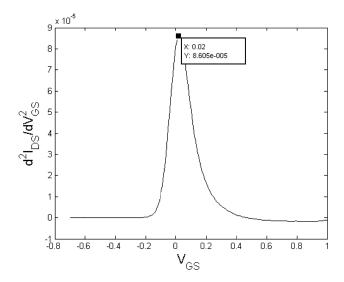

| Fig.2A.3 Maximum transconductance change (TC) method, applied to our numerically simulated model                                        |

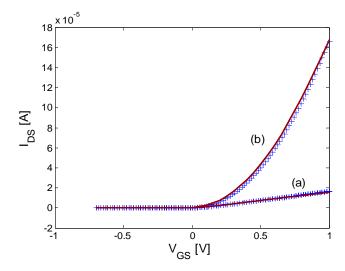

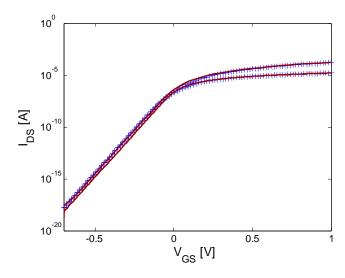

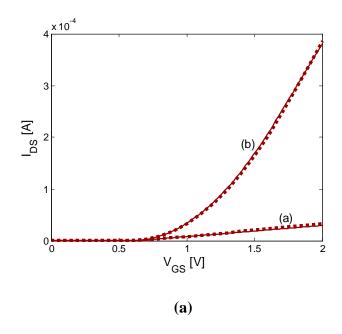

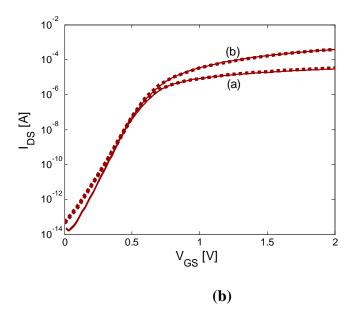

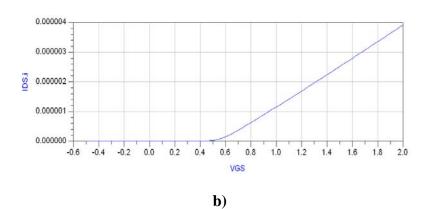

| Fig.2A.4 Transfer characteristics, for $V_{DS}$ =0.05V (a) and for $V_{DS}$ =1V (b) in linear scale.                                    |

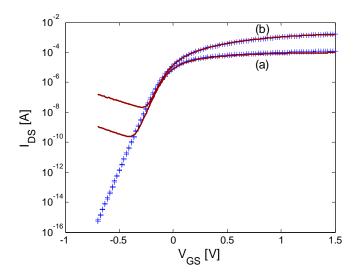

| Fig.2A.5 Transfer characteristics, for $V_{DS}$ =0.05V (b) and for $V_{DS}$ =1V (a) in logarithmic scale67                              |

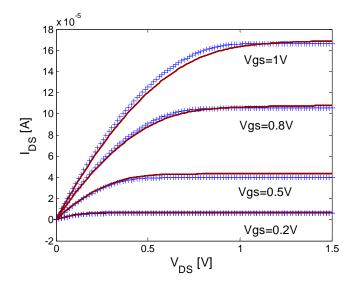

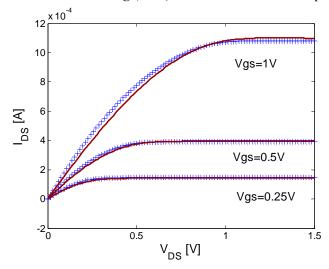

| Fig.2A.6 Output characteristics                                                                                                         |

| Fig.2A.7 Transfer characteristics, for $V_{DS}$ =0.05V (a) and for $V_{DS}$ =1V (b) in linear scale. Solid line: FinFET measurements; Symbol line: our model                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.2A.8 Transfer characteristics, for $V_{DS}$ =0.05V (a) and for $V_{DS}$ =1V (b), in logarithmic scale. Solid line: FinFET measurements; Symbol line: our model                                                        |

| Fig.2A.9 Output characteristics. Solid line: FinFET measurements; Symbol line: our model                                                                                                                                  |

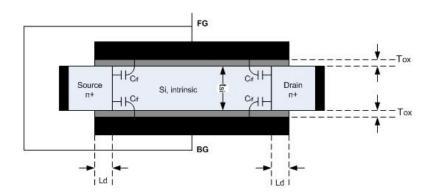

| Fig.2A.10 Intrinsic fringing capacitances in a DG MOSFET 73                                                                                                                                                               |

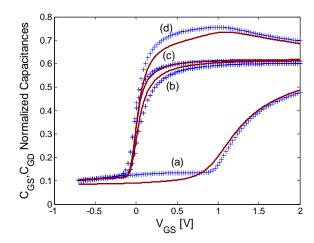

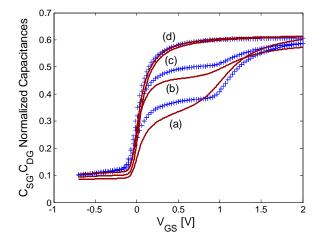

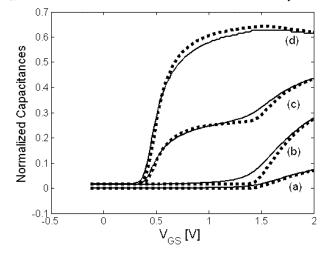

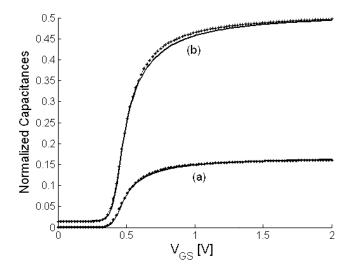

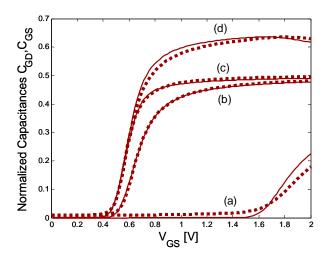

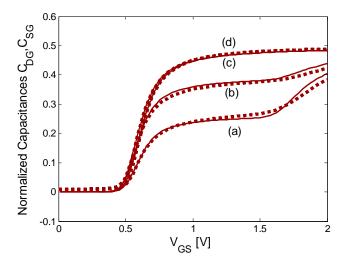

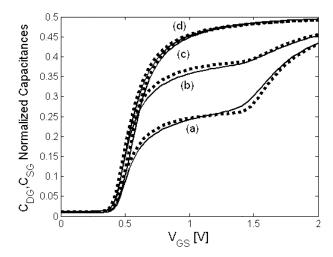

| Fig.2A.11 Normalized gate to drain capacitance $(a, b)$ and gate to source capacitance $(c, d)$ with respect to the gate voltage, for $V_{DS}=1V(a,d)$ and $V_{DS}=0.05V(b,c)$                                            |

| Fig.2A.12 Normalized drain to gate capacitance $(a, c)$ and source to gate capacitance $(b, d)$ with respect to the gate voltage, for $V_{DS}$ =1V $(a, b)$ and $V_{DS}$ =0.05V $(c, d)$                                  |

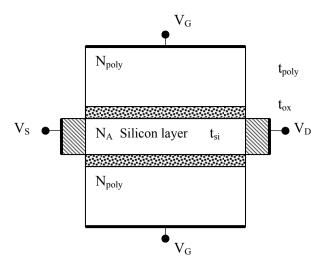

| Fig.2A.13 Diagram of the double-gate MOSFET structure analyzed                                                                                                                                                            |

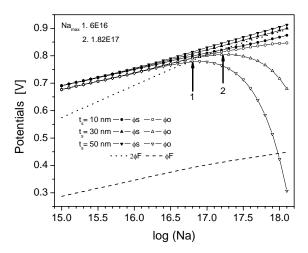

| Fig.2A.14 Modeled and numerically calculated potentials at the surface and at the center of the Si layer as function of $N_A$ in threshold condition for silicon layer thickness of 10, 30 and 50 nm. $t_{ox}$ = 2.24 nm. |

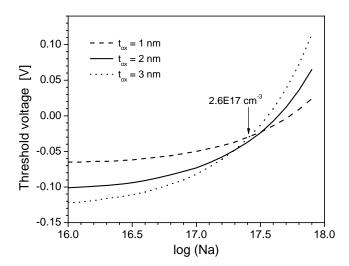

| Fig.2A.15 Modeled and extracted from 2D simulation threshold voltage as function of $N_A$ for three gate oxide thickness: $t_{ox} = 1$ , 2 and 3 nm and $t_{si} = 34$ nm.                                                 |

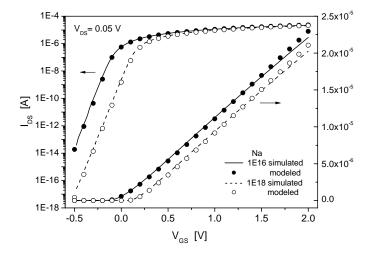

| Fig.2A.16 Comparison between simulated and modeled linear transfer characteristics for $V_{DS}$ = 0.05 V and two Si layer doping concentrations: $10^{16}$ cm <sup>-3</sup> and $10^{18}$ cm <sup>-3</sup>                |

| * ***** *** = ** * * ****                                                                                   |

|-------------------------------------------------------------------------------------------------------------|

| ISBN:978-84-691-8839-2/DL:T-1263-2008                                                                       |

| ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs |

|                                                                                                             |

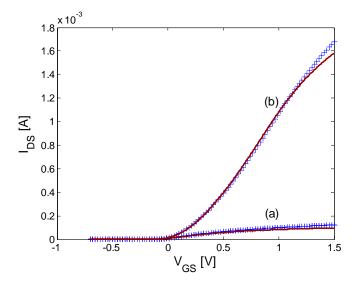

| Fig.2A.17 Comparison between simulated and modeled transfer characteristics in saturation for $V_{DS}$ = 1 V and two Si layer doping concentrations: $10^{16}$ cm <sup>-3</sup> and $10^{18}$ cm <sup>-3</sup> 96                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

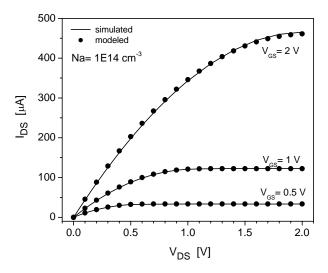

| Fig.2A.18 Simulated and modeled output characteristics for $V_{GS}$ = 0.5, 1 and 2 V for a Si layer doping concentration                                                                                                               |

| of 10 <sup>14</sup> cm-397                                                                                                                                                                                                             |

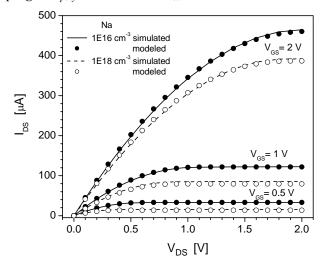

| Fig.2A.19 Simulated and modeled output characteristics for $V_{GS}$ = 0.5, 1 and 2 V and two Si layer doping concentrations: $10^{16} \text{ cm}^{-3}$ and $10^{18} \text{ cm}^{-3}$                                                   |

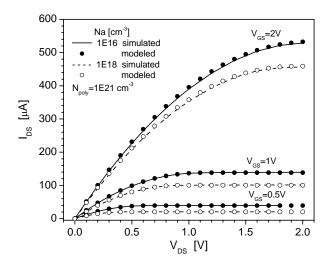

| Fig.2A.20 Simulated and modeled output characteristics for $V_{GS}$ = 0.5, 1 and 2 V and two silicon layer doping concentrations: $10^{16}$ cm <sup>-3</sup> and $10^{18}$ cm <sup>-3</sup>                                            |

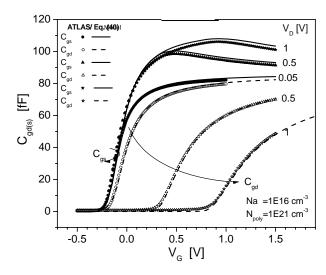

| Fig.2A.21 Gate-source and gate-drain capacitances at drain voltages equal $0.05V$ , $0.5V$ and $1$ $V$ . Si layer doping concentrations equal $10^{16}$ cm <sup>-3</sup> and a polysilicon doping equal $to10^{21}$ cm <sup>-3</sup> . |

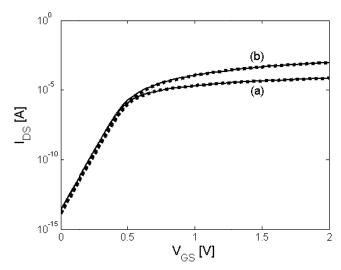

| Fig.2B.1 Transfer characteristics, for $V_{DS}$ =0.05 $V$ (a) and for $V_{DS}$ =1 $V$ (b), for $t_{Si}$ =20nm in logarithmic scale107                                                                                                  |

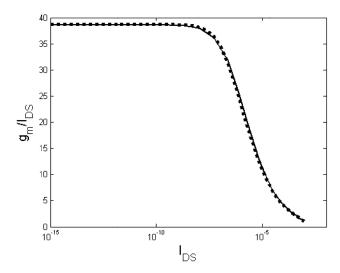

| Fig.2B.2 The transconductance $g_m$ normalized to the drainsource current, for $t_{Si}$ =20nm and $V_{DS}$ =1 $V$                                                                                                                      |

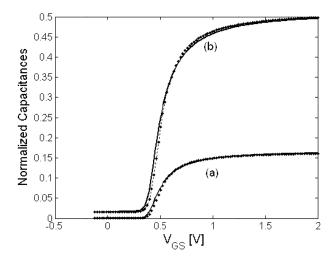

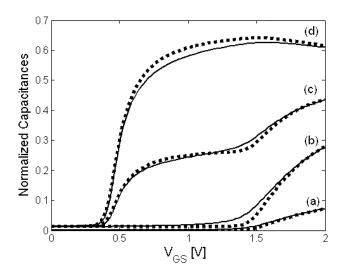

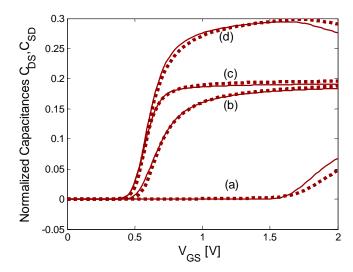

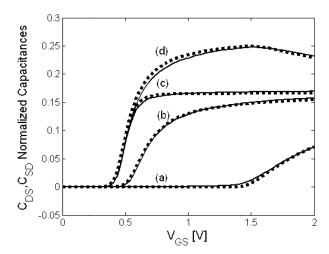

| Fig.2B.3 Normalized source-to-drain capacitance in (a), gate-to-drain capacitance, gate-to-source capacitance and drain-to-gate capacitance in (b) with respect to the gate voltage, for $V_{DS}$ = 0 V, for $t_{Si}$ =20nm. 113       |

| Fig.2B.4 Normalized source-to-drain capacitance in (a), gate-to-drain capacitance in (b), drain-to-gate capacitance in (c) and                                                                                                         |

| gate-to-source capacitance in (d) with respect to the gate                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| voltage, for VDS = 1V, for tSi = 20nm.                                                                                                                                                                                                                   |

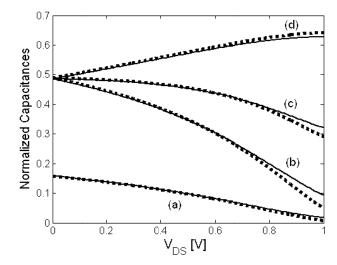

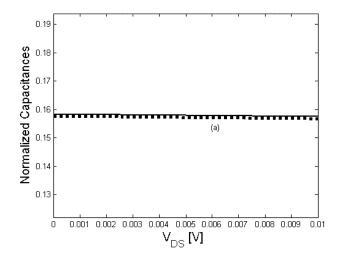

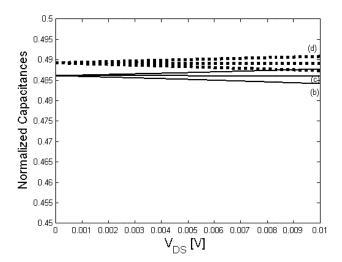

| Fig.2B.5a Normalized source-to-drain capacitance in (a), gate-to-drain capacitance (b), drain-to-gate capacitance (c) and gate-to-source capacitance (d) with respect to the drain voltage, for $V_{GS} = 1.5 \text{ V}$ , for $t_{Si} = 20 \text{nm}$ . |

| Fig.2B.6 Normalized source-to-drain capacitance in (a), gate-to-drain capacitance, gate-to-source capacitance and drain-to-gate capacitance in (b) with respect to the gate voltage, for $V_{DS} = 0 \ V$ , for $t_{Si}$ =10nm                           |

| Fig.2B.7 Normalized source-to-drain capacitance in (a), gate-to-drain capacitance in (b), drain-to-gate capacitance in (c) and gate-to-source capacitance in (d) with respect to the gate voltage, for $V_{DS} = 1V$ , for $t_{Si} = 10$ nm.             |

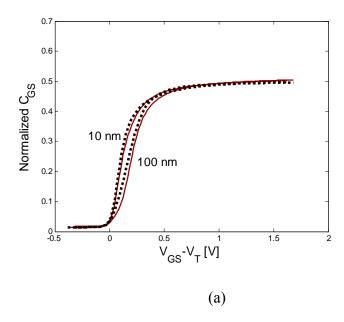

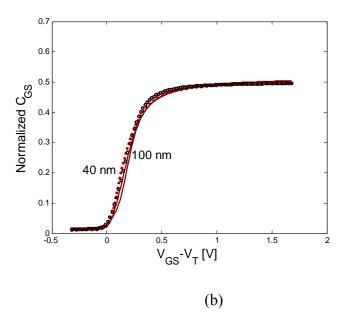

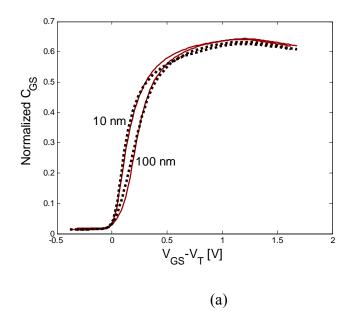

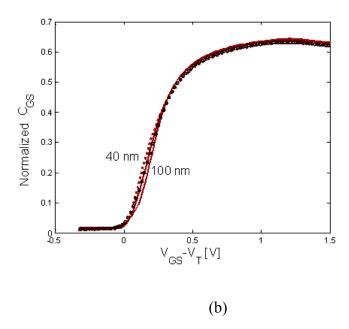

| Fig.2B.8 Normalized gate-to-source capacitance, with respect to the gate overdrive, for $V_{DS} = 0.05 \ V$ , (a) for $t_{Si} = 10$ and $100 \ nm$ , and (b) for $t_{Si} = 40$ and $100 \ nm$ .                                                          |

| Fig.2B.9 Normalized gate-to-source capacitance, with respect to the gate overdrive, for $V_{DS} = 1 \ V$ , (a) for $t_{Si} = 10$ and $100 \ nm$ , and (b) for $t_{Si} = 40$ and $100 \ nm$ .                                                             |

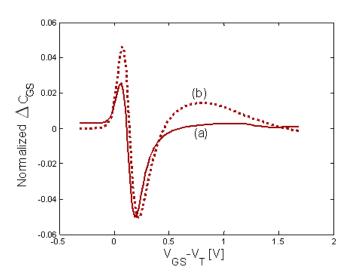

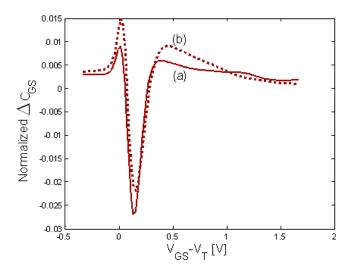

| Fig.2B.10 Normalized $\Delta$ $C_{gs}$ with respect to the gate overdrive, for $V_{DS} = 1$ $V$ , $\Delta$ $C_{gs} = C_{gs}$ ( $t_{Si} = 100$ nm) - $C_{gs}$ ( $t_{Si} = 10$ nm) 128                                                                     |

| Fig.2B.11 Normalized $\Delta$ $C_{gs}$ with respect to the gate overdrive, for $V_{DS} = 1$ $V$ , $\Delta$ $C_{gs} = C_{gs}$ ( $t_{Si} = 100$ nm) - $C_{gs}$ ( $t_{Si} = 40$ nm) 129                                                                     |

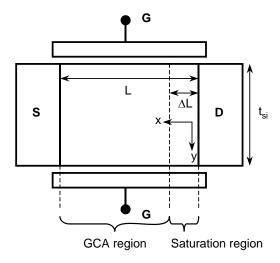

| Fig.2B.12 Schematic representation of the DGMOSFET considered in this section                                                                                                                                                                            |

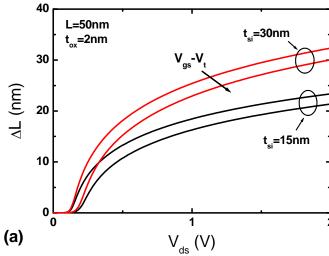

| Fig.2B.13a Plots of $\Delta L(V_{DS})$ for two different values of the silicon thickness $t_{si}$ , with $V_{GS}$ - $V_t$ =0.25 and 0.5V. a) for $L=50$ nm, b) for $L=120$ nm.                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

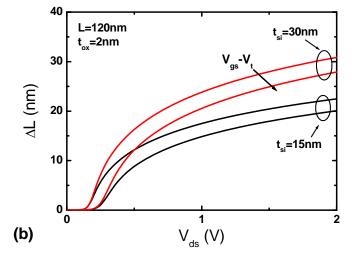

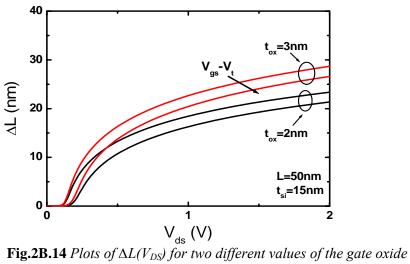

| Fig.2B.14 Plots of $\Delta L(V_{DS})$ for two different values of the gate oxide thickness $t_{ox}$ , with $V_{GS}$ - $V_t$ =0.25 and 0.5 $V$                                                                                                                                    |

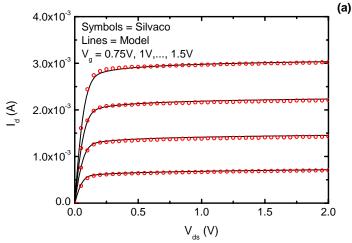

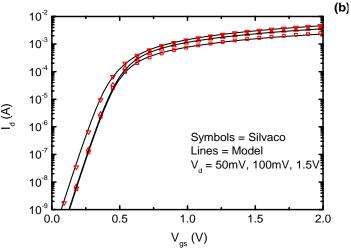

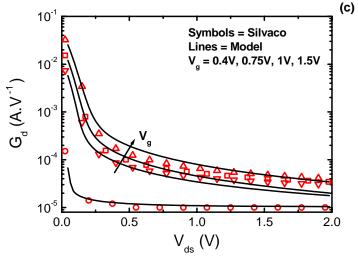

| Fig.2B.15a Comparison of the model with Silvaco simulations, for a DGMOS with $t_{ox}$ =2nm, $t_{si}$ =15nm and L=50nm                                                                                                                                                           |

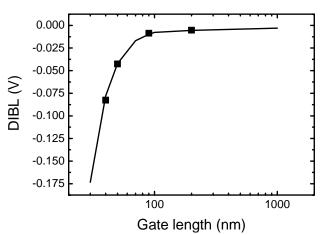

| Fig.2B.16 DIBL defined in weak inversion as the $V_{GS}$ offset between $I_{DS}@V_{DS}=1V$ and $I_{DS}@V_{DS}=50mV$ , $t_{si}=15nm$ to $to x=2nm$                                                                                                                                |

| Fig.2C.1 Schematic of the asymmetric DG MOSFET used in this section                                                                                                                                                                                                              |

| Fig.2C.2 Transfer characteristics, for $V_{DS}$ =0.05 $V$ (a) and for $V_{DS}$ =1 $V$ (b) in linear scale for $t_{Si}$ =31nm (Fig.2C.2.a). Transfer characteristics, for $V_{DS}$ =0.05 $V$ (a) and for $V_{DS}$ =1 $V$ (b) in logarithmic scale for $t_{Si}$ =31nm (Fig.2C.2.b) |

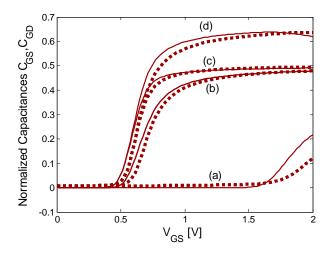

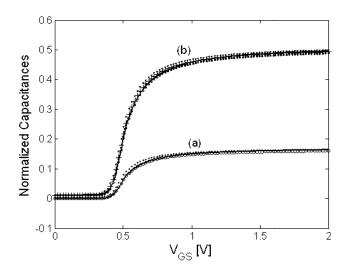

| Fig.2C.3 Normalized gate-to-drain capacitance $(a, b)$ and gate-to-source capacitance $(c, d)$ with respect to the gate voltage, for $V_{DS}$ =0.05 $V$ $(b,c)$ and $V_{DS}$ =1 $V$ $(a,d)$ ; $t_{si}$ =31 $nm$                                                                  |

| Fig.2C.4 Normalized drain-to-gate capacitance $(a, c)$ and source-to-gate capacitance $(b, d)$ with respect to the gate voltage, for $V_{DS}$ =1V $(a, b)$ and $V_{DS}$ =0.05V $(c, d)$ ; $t_{si}$ =31nm165                                                                      |

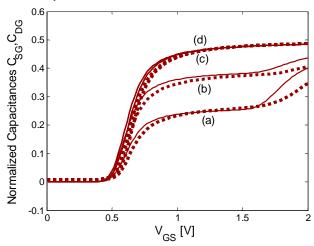

| Fig.2C.5 Normalized source-to-drain capacitance $(a, b)$ and drain-to-source capacitance $(c, d)$ with respect to the gate voltage, for $V_{DS}=1V(a, d)$ and $V_{DS}=0.05V(b, c)$ ; $t_{si}=31$ nm166                                                                           |

| Fig.2C.6 Normalized gate-to-drain capacitance $(a, b)$ and gate-to-source capacitance $(c, d)$ with respect to the gate voltage, $V_{DS}=0.05V$ $(b,c)$ and $V_{DS}=1V$ $(a,d)$ ; $t_{si}=20$ nm.                                                                 | for  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig.2C.7 Normalized drain-to-gate capacitance $(a, c)$ and source-to-gate capacitance $(b, d)$ with respect to the gate voltage, for $V_{DS}$ =1V $(a, b)$ and $V_{DS}$ =0.05V $(c, d)$ ; $t_{si}$ =20nm                                                          | 168  |

| Fig.2C.8 Normalized source-to-drain capacitance $(a, b)$ and drain-to-source capacitance $(c, d)$ with respect to the gate voltage, for $V_{DS}=1V$ $(a, d)$ and $V_{DS}=0.05V$ $(b, c)$ ; $t_{si}=20$ nm                                                         | 169  |

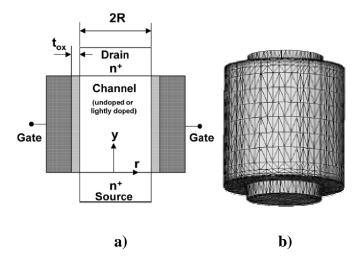

| Fig.2D.1 a) Cross section of the surrounding gate MOSFET by Simulated surrounding gate MOSFET structure                                                                                                                                                           |      |

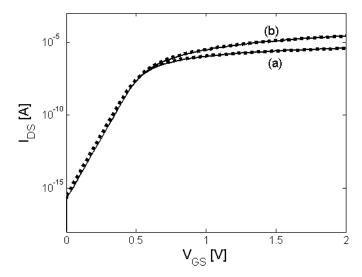

| Fig.2D.2 Transfer characteristics, for $V_{DS}$ =0.1V (a) and for $V_{DS}$ =1V (b) in logarithmic scale                                                                                                                                                           | 175  |

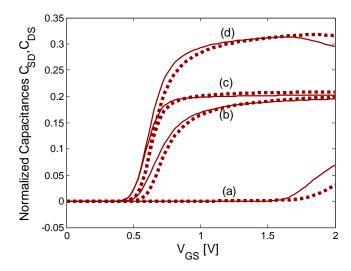

| Fig.2D.3 Normalized gate to drain capacitance $(a, b)$ and gate source capacitance $(c, d)$ with respect to the gate voltage, for $V_{DS}$ =0.1V $(b,c)$ and $V_{DS}$ =1V $(a,d)$                                                                                 | •    |

| Fig.2D.4 Normalized drain to gate capacitance $(a, c)$ and source to gate capacitance $(b, d)$ with respect to the gate voltage, for $V_{DS}$ =1V $(a, b)$ and $V_{DS}$ =0.1V $(c, d)$                                                                            | 181  |

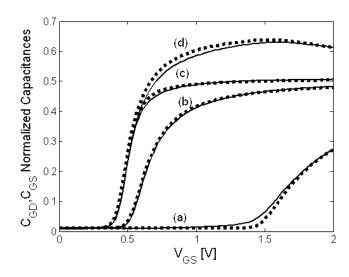

| Fig.2D.5 Normalized drain to source capacitance (c,d) and source to drain capacitance (a, b) with respect to the gate voltage, for $V_{DS}$ =1V (a, d) and $V_{DS}$ =0.1V (b, c)                                                                                  | 181  |

| Fig.2D.6 Normalized drain to source capacitance, source to drain capacitance in (a), gate to drain capacitance, gate to source capacitance, drain to gate capacitance and source to gate capacitance in (b) with respect to the gate voltage, for $V_{DS}$ =0 $V$ | 187  |

| , DO                                                                                                                                                                                                                                                              | . 02 |

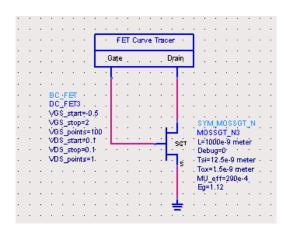

| Fig.2D.7 a) Simulation of the SGT structure in AGILENT ADS (Advanced Design System). b) Result for the transfer characteristics, for $V_{DS}$ =0.1V, in AGILENT ADS (Advanced Design System) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

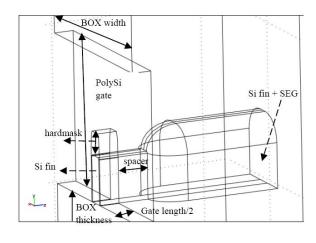

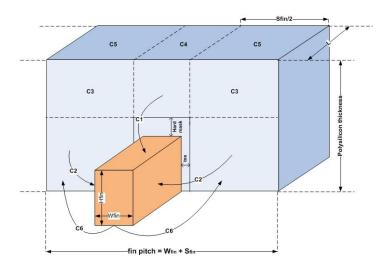

| Fig.3.1 (a) 3-D structure for half of a FinFET fin simulated with COMSOL, (b) front 2-D view of the same structure                                                                           |

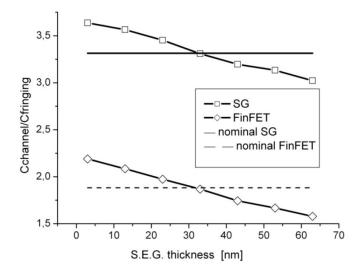

| Fig.3.2 C <sub>channel</sub> /C <sub>fringing</sub> ratio versus SEG thickness                                                                                                               |

| Fig.3.3 Fringing and channel capacitances versus fin                                                                                                                                         |

| spacing. 196                                                                                                                                                                                 |

| Fig.3. 4 C <sub>channel</sub> /C <sub>fringing</sub> ratio versus fin spacing                                                                                                                |

| Fig.3.5 Fringing and channel capacitances vs. gate extension depth                                                                                                                           |

| Fig.3.6 C <sub>channel</sub> /C <sub>fringing</sub> ratio versus spacer thickness198                                                                                                         |

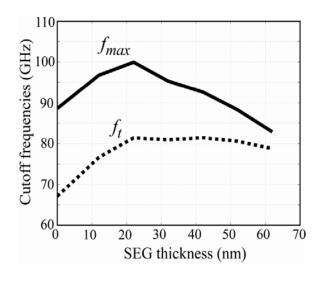

| Fig.3.7 Cutoff frequencies vs. (a) SEG thickness and (b) fin spacing for L=50nm                                                                                                              |

| Fig.3.8 Fringing capacitances considered for one fin in the nominal FinFET. 202                                                                                                              |

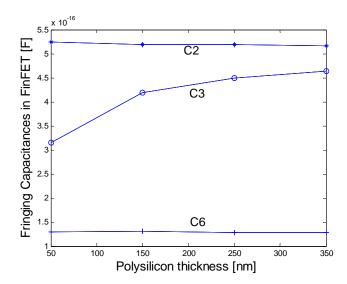

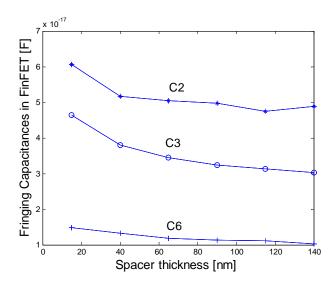

| Fig.3.9 $C_2$ , $C_3$ , $C_6$ versus polysilicon thickness                                                                                                                                   |

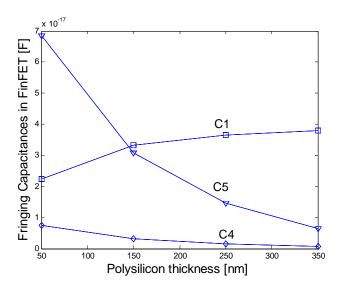

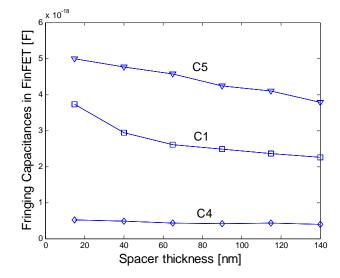

| Fig.3.10 $C_1$ , $C_4$ , $C_5$ versus polysilicon thickness                                                                                                                                  |

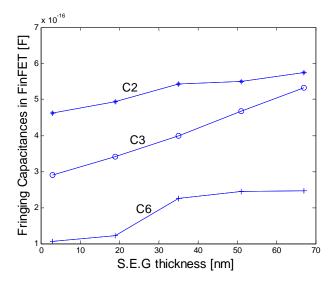

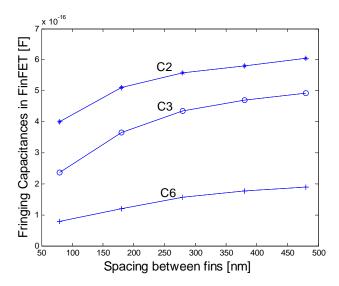

| Fig.3.11 C <sub>2</sub> , C <sub>3</sub> , C <sub>6</sub> versus S.E.G. thickness                                                                                                            |

| Fig.3.12 C <sub>1</sub> , C <sub>4</sub> , C <sub>5</sub> versus S.E.G. thickness                                                                                                            |

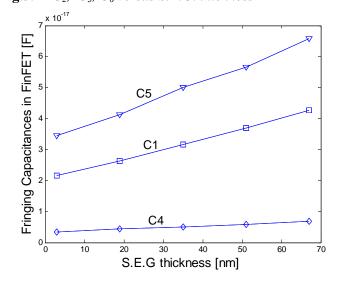

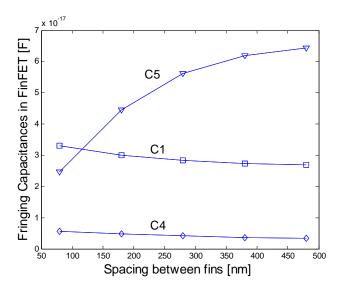

| Fig.3.13 $C_2$ , $C_3$ , $C_6$ versus spacing between fins                                                                                                                                   |

| UNIVERSITAT ROVIRA I VIRGILI                                                      |    |

|-----------------------------------------------------------------------------------|----|

| DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFE: | ΓS |

| Oana Moldovan                                                                     |    |

| ISBN:978-84-691-8839-2/DL:T-1263-2008                                             |    |

| Fig.3.14 $C_1$ , $C_4$ , $C_5$ versus spacing between fins                          | 07 |

|-------------------------------------------------------------------------------------|----|

| Fig.3.15 $C_2$ , $C_3$ , $C_6$ versus spacer thickness                              | 38 |

| Fig.3.16 C <sub>1</sub> , C <sub>4</sub> , C <sub>5</sub> versus spacer thickness20 | 08 |

List of Figures

UNIVERSITAT ROVIRA I VIRGILI

DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFETS

Oana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

# **Chapter 1**

# State of the Art and Current Trends for Multiple Gate MOS Devices

#### 1A. Introduction

Since the invention of the integrated circuit (IC) in 1958, engineers and researchers around the world have worked on how to put more speed, performance and value onto smaller chips of silicon. The semiconductor industry has made considerable progress, especially regarding the Metal Oxide Semiconductor Field Effect Transistor (MOSFET). The fundamental driver has been the continued shrinking of its feature sizes, allowing the exponential growth in device count that tracks the well-known Moore's Law [1], first formulated by Intel co-founder Gordon Moore. Shrinking down feature sizes (at a rate of approximately 0.7 times every 18 months) allows more transistors to be packed onto a piece of silicon, with each one running at higher speeds. This combination translates into higher computing capabilities,

ana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

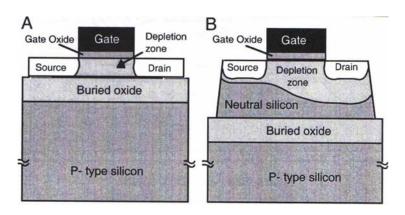

> ultimately delivering better value to the end user. However, this law is a rough prediction of the future of IC expansion. The need of a more accurate forecast defined the International Technology Roadmap for Semiconductors (ITRS) [2], which has been predicting and driving the pace of semiconductor technology at the same time. In the past century, together with the reduction of the MOSFET dimensions, also materials used for fabrication have changed: bulk silicon wafers changed to Silicon-on-Insulator (SOI) wafers. Also, the thickness of SOI varied, leading to MOS transistors in Partially-Depleted mode (thick SOI), and in Fully-Depleted mode (thin SOI). One of the main advantages of this wafer is the drastic reduction of all the parasitic effects coming from the silicon substrate. [3].A SOI wafer is actually a piece of a pure silicon wafer placed on an insulating device, such as silicon dioxide, called buried oxide. The transistors are then built on this thin silicon layer. If the silicon film is thin enough the depletion zone below the gate extends all the way through the buried oxide, and the device is said to be fully depleted (Fig.1A.1 A), if not it is called partially depleted (Fig.1A.1B). The remarkable feature of the fully depleted SOI MOSFET is that the current drive is higher than in bulk MOSFET and its subthreshold slope is sharper (better), due to a much smaller body factor [4].

Fig.1A.1 A Fully depleted SOI MOSFET, B-Partially depleted SOI MOSFET [5]

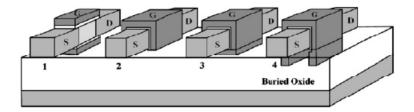

However, even in ultrathin-film SOI technology, results have shown that the transconductance and AC characteristics of Single-Gate (SG) MOS structures, for gate lengths down to 40 nm are deteriorated due to Short Channel Effects (SCE) [6]. This means that the shrinking process will come to an end if no new technology can be found. The gate controls the channel of the transistor through capacitive coupling. The problem is that, when the MOSFET gate is shrunk, the drain is pulled closer to the middle of the channel, increasing the capacitive coupling between the drain and the channel. If the devices are too small, the drain has enough coupling to the channel that a leakage current will flow, only with a drain voltage applied, and no gate voltage. Being faced with this problem, ITRS proposes as one of the solutions, the implementation of novel devices like multiplegate SOI MOSFETs, which will allow the gates to control the channel from several sides (solving the SCE problem) and so the gate length to be further reduced. The idea of the Double-Gate (DG) MOSFET was first introduced by J-P. Colinge [7]. Since then, other multiple-gate SOI MOSFETs have been introduced [8,9] such as Triple-Gate (TG), FinFET, Pi-Gate (PG), Quadruple-Gate (QG), Surrounding-Gate (SGT), also called Gate-All-Around (GAA), Omega-Gate ( $\Omega$ -G), etc. (Fig.1A.2)

Fig. 1A.2 The schematic device structures of MuGFETs[10]:1)doublegate,2)triple-gate,3)quadruple-gate, 4)PI-gate

Pi-gate MOSFETs are basically triple gate devices with an extension of the gate electrode below the active silicon island, which increases current drive and improves short-channel effects. The gate extension forms a virtual, field induced, gate electrode underneath the device that can block drain electric field lines from encroaching on the channel region at the bottom of the active silicon. Instead the lines terminate on the gate extensions. This gate structure is very effective at reducing short-channel effects. Such devices can be called 3+ (triple-

plus)-gate devices because their characteristics lie between those of triple- and quadruple-gate devices [11].

The FinFET proves to be an interesting alternative to SG MOSFET [12-14] also, due to the fact that this structure has been used to set new world records for smallest gate length, in various research laboratories: the current record is 3nm gate length [15]. It is important to note that during the same process flow, conventional planar transistors can be also produced side by side on the same chip as the FinFETs. However, it is well known that the double-gate (top and bottom gate) silicon-oninsulator (SOI) MOSFET and the gate-all-around device are the most suitable device structures for suppressing short-channel effects such as DIBL (Drain Induced Barrier Lowering) and subthreshold slope degradation [7], [16-18]. Even though there is a lot of research around these different types of multiple-gate MOSFETs, until now, only the DG MOSFET is predicted to be introduced in 2011 due to its advantages [2]. So, the DG technology is presenting itself not as a possibility but as a certain long-term solution. The DG architecture can be defined as planar or non-planar. For example, a FinFET can be seen as a non-planar DG MOSFET if the width of the silicon fin is much smaller that its height. If the width of the silicon fin becomes comparable to its height, the structure changes to a triple-gate MOSFET.

DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFETS

Dana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

An interesting characteristic of the multiple-gate devices is the volume inversion concept, introduced by Balestra et al.[19]: if the Si film is thicker than the sum of the depletion regions induced by the two gates, no interaction is produced between the two inversion layers, and the operation of this device is similar to the operation of two conventional MOSFETs connected in parallel. However, if the Si thickness is reduced, the whole silicon film is depleted and an important interaction appears between the two potential wells. In such conditions the inversion layer is formed not only near the two silicon-oxide interfaces, but throughout the entire silicon film thickness. It is then said that the device operates in "volume inversion," i.e., carriers are no longer confined at one interface, but distributed throughout the entire silicon volume. Several authors have claimed that volume inversion presents a significant number of advantages, such as enhancement of the number of minority carriers; increase in carrier mobility [20] and velocity due to reduced influence of scattering associated with oxide and interface charges and surface roughness; as a consequence of the latter, an increase in drain current and transconductance [19,21]. This increase in the carrier mobility is due to the fact that when the film is fully inverted, a big fraction of the current flows around the center of the film, sufficiently far away from the interfaces, roughness thus reducing the surface scattering. This

-

phenomenon usually takes place around the threshold voltage and it depends also on the doping concentration in the channel. For a thin film, a low or intrinsic doping is needed in order to assure the volume inversion. In fact, undoped films can be used, because the full depletion of the thin film prevents punch-through. Also, we can avoid the problems resulting from dopant-impurity location randomness and improve carrier transport by the consequent mobility enhancement.

DC analysis of DG devices has shown that the drain current  $(I_{DS})$  and transconductance  $(g_m)$  of a DG MOSFET are higher than twice the drain current and transconductance, respectively, of a SG SOI MOSFET [9,19,22], due to volume inversion phenomena, thus suggesting to overcome the static and dynamic limitations of ultra deep submicron SG devices for high frequency analog applications.

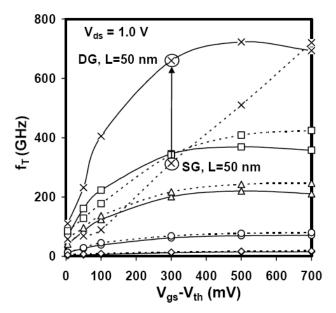

Even if one of the disadvantages is the increase in the gate-source capacitance of DG devices, which is nearly twice that of SG devices, at high gate overdrive ( $V_{GO}=V_{GS}-V_{th}$ ), at ultra short channel lengths ( $L \leq 50$  nm) and lower gate overdrives ( $V_{GO} \leq 400 \text{mV}$ ), DG devices show significantly higher values of the cut-off frequency,  $f_T$  (=  $g_m/(2\pi(C_{GS}+C_{GD}))$ ) as compared to SG devices (due to the transconductance increase), thus presenting DG MOSFET as a serious candidate for microwave analog applications [23].

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

Fig.1A.3 Dependence of cut-off frequency of DG and SG devices for various channel lengths at Vds = 1.0V (DG-, SG ---, X 50 nm,  $\Box$ 75 nm,  $\Delta 100 \, nm$ , o 200 nm,  $\Diamond 500 \, nm$ ). [23]

Results have also shown that the DG architecture exhibits speed superiority compared to SG devices [24]. The increase in the parasitic capacitances for the DG MOSFETs compared to SG, will not deteriorate the overall speed. Another device that is of interest, but does not appear referred in [2] is the 4-terminal driven DG MOSFET (4T-DG) or Asymmetric DG MOSFET. This double-gate MOSFET can be driven in a genuine 4ISBN:978-84-691-8839-2/DL:T-1263-2008

State of the Art and Current Trends for Multiple Gate MOS Devices

terminal mode with two independent gates controlled separately. This means that the transistor operation speed can be controlled to an optimum, and the power loss caused by leak current during standby is substantially nullified, due to the Vth controllability. The 4T-DG MOSFET can also be regarded as a MOSFET equipped with an arithmetic operation feature based on independent two-input capability. A single device with such a circuit function indicates the possibility of extensively reduction of the number of devices in VLSIs.

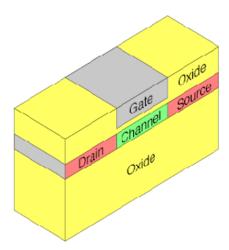

Among the non-classic CMOS device concepts the ultra-thin-body silicon-on-insulator (UTB-SOI) is one of the most promising approaches for future CMOS scaling to feature sizes below 50 nm [25-29]. Ultra-thin body SOI has a very thin layer of single-crystal silicon, the ultra-thin silicon body (5-40 nm), on top of a silicon dioxide insulating layer (the buried oxide, or "BOX"), which itself is on top of the silicon substrate. The ultra-thin body forms the channel of the MOSFET. The advantages of ultra-thin body SOI for highly scaled MOSFETs include reduced junction capacitance, improved electrical isolation, the possibility of optimal operation with relatively light channel doping, and certain advantageous circuit characteristics. The ultra-thin body SOI may be either a single-gate (see structure in Figure 1A.4) or a DG MOSFET. One type of DG MOSFET is similar to the ultra-thin body SOI single-gate transistor, with the

Oana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

addition, in the BOX, of a bottom gate electrode fully selfaligned to the top gate electrode.

**Fig.1A.4** *Schematic of a single-gate UTB SOI MOSFET*

It is clear that multiple-gate devices will respond to the future ITRS demands. These architectures have very good electrical characteristics even at nanoscale gate lengths, due to the excellent control of the charges in the channel. One of the main advantages of multiple-gate MOSFETs is the increase of the total current as compared to SG devices. The increase of the drain current per channel is related to the increased number of gates. Also, due to the short channel and thin film, the small dimensions of these devices allow a high packaging density. As shown above, they present a very good potential for RF and microwave analog applications. In digital applications, the small subthreshold swing of multiple gate devices keeps a high ratio

ISBN:978-84-691-8839-2/DL:T-1263-2008

between on current and off current even for devices with channel lengths of the order of nm [30].

### 1B. Compact modeling

Compact models of devices are used in circuit simulators, in order to predict the functionality of circuits. These multiple-gate devices will be preferred in nanoscale circuits, thus calling for accurate and reliable compact models, including new device specific effects. These compact models that accurately describe the novel devices, and are computationally efficient are an important prerequisite for successful circuit design. The currently available compact models are facing enormous challenges in modeling the observed physical phenomena in the sub-90-nm technologies [31]. The demands for advanced models, which can describe nanoscale silicon devices in analog and mixed-signal applications and can account for the physical effects on small geometry devices, have led to enormous R&D efforts in the development of advanced physics-based compact models.

The models should consist of high order continuity expressions, to prevent lack of convergence in circuit simulations. Smoothening functions are often used to assure continuity between the operating regimes. Also, a good model should be based on explicit expressions, as iterations require a higher computational time.

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

For the multiple-gate MOSFETs, the principles of modeling will change as compared to the traditional SG MOSFET, first because they will have to introduce the volume inversion effect, then, contrary to bulk MOSFETs, depletion charges in multiplegate devices are negligible because the silicon film is undoped (or lightly doped). Thus, only the mobile charge term needs to be included in Poisson's equation. Therefore, the exact analytic solutions to 1D Poisson's and current continuity equations based on GCA (gradual-channel-approximation, which assumes that the quasi Fermi potential stays constant along the direction perpendicular to the channel) can be derived, without the charge-sheet approximation. It is considered that the electrostatic control of the gates is good enough to neglect SCE associated to 2D effects. Most models presented so far are for undoped devices with a long enough channel to assume that the transport is due to the drift-diffusion transport mechanism [32-35].

Using the above principles, some models for undoped doublegate [33-36] and surrounding gate [32,37] have been published, showing good agreement with three dimensional numerical simulations.

In the case of a long-channel symmetrical undoped device, an analytical solution of 1D Poisson's equation is obtained [33], [34]. Making some approximations, a charge control model based on this solution can be derived [38].

If the film is strongly doped, an exact analytical solution of the 1-D Poisson's equation is not possible. Some approximations have been used to find an approximate analytical solution in the moderate inversion regime [39], in the weak inversion regime [40], or assuming a uniform mobile-charge sheet density along the thickness of the film [41] (which is valid from weak to moderate inversion).

For devices that are short enough, i.e., where the gate length is comparable to the body thickness, the electrostatic potential should be derived from a 2-D Poisson's equation. If the transport mechanism is drift-diffusion, a compact analytical solution seems difficult to obtain, since it has to be determined self-consistently with the current continuity equation, which includes the quasi-Fermi potential. An exception is the subthreshold regime where the quasi-Fermi potential is constant in most of the channel [42]. If the doping is high and the mobile charge can be neglected in the subthreshold regime, a simple solution for the potential can be obtained, which leads to an analytical expression of the threshold voltage that includes the scaling dependences (and therefore the threshold voltage rolloff and DIBL). In DG MOSFETs, this solution is written as a superposition  $\Phi(x, y) = \Phi 1(y) + \Phi 2(x, y)$ , where  $\Phi 1(y)$  is the solution of the 1-D Poisson's equation, which includes the

Dana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

doping charge term, and  $\Phi$  2(x, y) is the solution of the remaining 2-D Laplace equation [43]. In GAA MOSFETs, the solution is written as:  $\Phi(x, r) = \Phi(x, r) + \Phi(x, r)$ . However, in these previous works, additional approximations were needed to solve the 2-D Laplace's equation [44–46]. Furthermore, their analyses were quasi-2-D rather than fully 2-D, which required the use of fitting parameters. In an undoped device, analytical solutions of the 2-D Poisson's equation were obtained at low V<sub>DS</sub>, which accurately predicted the threshold voltage rolloff [42,47]; but at high  $V_{DS}$ , the problem becomes more complex. The solution also has two contributions, but the 2-D contribution is not the solution of a Laplacian, since the mobile charge is not ignored. At high  $V_{\rm DS}$ , an expression for the quasi-Fermi potential along the channel length is necessary to solve the 2-D Poisson's equation. In [43], an approximate expression of the quasi-Fermi potential is used, although it was derived for long-channel bulk MOSFETs. An alternative assumption is to neglect the mobilecharge sheet density in the subthreshold even for an undoped device [48]. Again, the analysis used to solve the 2-D Poisson's equation was quasi-2-D. The threshold voltage is calculated from the value of the minimum of the surface potential [39,40,46]. The solution of the Poisson's equation in the subthreshold allows calculating the subthreshold swing [42,47,49].

A very promising modeling approach presented recently is based on the solution of Laplace's equation for the extended body (including the gate insulators) of the short-channel nanoscale DG MOSFETs using conformal mapping techniques [50-52]. This technique was first explored for bulk longchannel MOSFETs [53] and later for sub-0.1- $\mu$ m MOSFETs [54], and finally for DG MOSFETs.

However, for devices with channel lengths shorter than 50nm, the transport mechanism will probably not be drift-diffusion; ballistic or quasi-ballistic transport may appear. We cannot define a continuous quasi- Fermi potential that varies from the source to the drain and controls the mobile-charge distribution. What will happen is that carriers injected from the source will depend on the Fermi potential at the source, and carriers injected from the drain will depend on the Fermi potential at the drain.

For this, accurate models that will include the ballistic or quasi-ballistic regime are needed [55-66]. On the other hand, for films smaller than 10 nm, quantum confinement in the film may not be negligible.

Thus, accurate MOSFET models that include these new physical behaviours are crucial to design and optimize advanced VLSI circuits for nanoscale CMOS technology.

However, drain-current model is not enough for circuit simulation [67]. In order to calculate the dynamic behaviour of the device and so, to enable AC and transient circuit simulation,

terminal charge and capacitance modelling of multiple-gate MOSFETs are needed. Unfortunately, less work has been dedicated to this modelling domain. The recently presented study in [68] which is consistent with the drain current model of the study in [33], for symmetric and asymmetric DG devices is not analytical, since it requires numerical integration or integral function tabulation, which is too time-consuming to be carried out. Thus, analytical charges and capacitances, associated with each terminal are preferred in circuit simulation. Regarding the surrounding-gate MOSFET, our group was the first to develop and publish a model of the charges and intrinsic capacitances [69], which is also analytic and explicit. Starting from an exact solution of the Poisson's equation, the model will be derived from Ward and Dutton charge partition scheme [70]. Every terminal charge or capacitance is described by an analytic function (See section 2D).

Another important area of study and modeling, due to its high influence in short-channel novel devices, is represented by the parasitic resistances and capacitances. One of the disadvantages of multiple-gate devices is the increase in the parasitic resistive and capacitive components (like fringing and overlap capacitances) that become comparable in magnitude or even larger than intrinsic ones [71]. Capacitive coupling with parasitic resistances even dominates device characteristics in analog/radio frequency (RF) ICs [72], a very important arena for the application of nanoscale devices.

#### 1C. Numerical simulations

The advent and technological development of supercomputers in the last decade has dramatically improved the quality of scientific research, allowing the possibility for numerical simulations of unprecedented dynamical range and sophistication of physical modeling. In addition to the wealth of details necessary for an accurate treatment of complex processes, numerical simulations often also offer unparalleled insight into the understanding of a physics problem.

Numerical simulation is a powerful tool in the semiconductor industry because it can analyze and predict the behaviour of novel devices, without the high cost necessary to fabricate the real components. The TCAD (Technology Computed Aided Design) has the potential to reduce development costs by as much as 40% "if appropriately used" [2]. The simulation tool can include different materials, various fabrication processes, study of 1D, 2D and 3D structures, etc.

In order to remain useful for future technology nodes, process simulation has to follow shifts of state-of-the-art processes and new materials for future nanoelectronics devices. New requirements on TCAD can be found in the Modelling and Simulation Section of the ITRS.

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

However, the simulation tools remain the easiest way to test the accuracy of compact models, in laboratories around the world, due to its low cost and also, to the limited number of measurements of optimized novel devices.

#### 1D. Capacitance model

In real circuit operation, the device operates under time-varying terminal voltages. Depending on the magnitude of the time-varying voltages, the dynamic operation can be classified as large-signal operation or small-signal operation [73]. If the variation in voltages is sufficiently small, the device can be modeled with linear resistors, capacitors, current, sources, etc. Such a model is called a small-signal model. This type of dynamic operation is influenced by the device's capacitive effects. Thus, a capacitance model describing the intrinsic and extrinsic components of the device capacitance is another essential part of a compact MOSFET model for circuit simulation.

The capacitance model is almost always based on the quasistatic approximation, which assumes that the charges in a device can follow the varying terminal voltages immediately, without any delay. Generally MOSFET capacitances can be divided into two groups, the intrinsic and the extrinsic capacitances. The intrinsic capacitances are much more complex than the extrinsic ISBN:978-84-691-8839-2/DL:T-1263-2008

components. The early intrinsic capacitances models, such as the Meyer model [74], simply treated the MOSFET capacitance as three separated lumped capacitances, gate-to-source capacitance ( $C_{GS}$ ), gate-to-drain capacitance ( $C_{GD}$ ) and gate-to-bulk capacitance ( $C_{GB}$ ). It has the disadvantage of the charge non-conservation, unlike the charge-based capacitance model, which we also used for multiple-gate MOSFETs.

However, the Meyer model has been widely used in simulators and continues to be used occasionally as an optional model for its simplicity and efficiency.

## 1D.1 Intrinsic charge-based capacitance model for DG MOSFET

In a charge-based approach, the emphasis is put on the charge, rather than the capacitances. The idea is to determine the charges in the drain, source and gate, and the capacitances are then computed through mathematical differentiation of the charge with respect to the voltage. The charge-based capacitance model will ensure the charge conservation, as long as the following equation is satisfied:  $Q_G + Q_D + Q_S = 0$ .

$Q_G$  can be obtained directly by integrating the corresponding charge density over the channel [75].  $Q_{INV}$ =- $Q_G$ , so, it is easy to calculate the total inversion charge in the channel. However, it is difficult to model the charges on the source and drain terminals, because only the total mobile channel charge  $Q_{INV}$ = $Q_D$ + $Q_S$  is

known and a partition of Q<sub>INV</sub> into Q<sub>D</sub> and Q<sub>S</sub> is needed. As discussed by Ward and Dutton [70], the partitioning proposed leads to a set of charge-conserving and nonreciprocal different intrinsic between the capacitances (nonreciprocity means that Cij is not equal to Cji, where i and j denote source, drain or gate).

Fig.1D.1.1 Intrinsic large-signal DG MOSFET equivalent circuit including a complete set of nonreciprocal and charge-conserving transcapacitances. The transcapacitances Cij are defined in the text. Based on Fjeldly T. A., Ytterdal T., and Shur M. (1998) Introduction to Device Modeling and Circuit Simulation, John Wiley & Sons, New **York**

The partitioning scheme is the following: the mobile charge  $Q_{INV}$  of a MOSFET is divided into a source charge  $Q_S = FpQ_{INV}$  and a drain charge  $Q_D = (1 - Fp)Q_{INV}$ , where Fp is a partitioning factor.

Cij=k

$$\frac{\partial Qi}{\partial Vj}$$

where  $k = \begin{cases} -1 & \text{for } i \neq j \\ 1 & \text{for } i = j \end{cases}$

The elements Cii are called self-capacitances. Cij contain information on how much the charge Qi assigned to terminal i changes by a small variation in the voltage Vj at terminal j. To illustrate why Cij may be different from Cji, assume a MOSFET in saturation. Then the gate charge changes very little when the drain voltage is perturbed since the inversion charge is very little affected, making  $C_{GD}$  small. However, if  $V_{GS}$  is perturbed, the inversion charge changes significantly and so does  $Q_{D}$ , making  $C_{DG}$  high.

Based on the formula of the charges and the charge partition for drain and source charges, an admittance matrix for the device can be created. All of the capacitance terms in the matrix are non-zero and non-reciprocal. The elements in each column and each row must sum to zero owing to the constraints imposed by charge conservation (which is equivalent to obeying Kirchhoff's current law) [76]. Some capacitances, such as C<sub>SD</sub> and C<sub>DS</sub> are negative as they should be [77] and out of the 9 DG MOSFET elements, only 4 are independent.

ISBN: 978-84-691-8839-2/DL: T-1263-2008

Development of Compact Small-Signal Quasi Static Models for MuGFETs

$$C = \begin{bmatrix} C_{GG} & C_{GS} & C_{GD} \\ C_{SG} & C_{SS} & C_{SD} \\ C_{DG} & C_{DS} & C_{DD} \end{bmatrix}$$

(1D.1.1)

Similarly, these intrinsic capacitances can be obtained for an asymmetric (different front and back gate voltages) DG MOSFET, where  $Q_G \neq Q_B$ .  $Q_B$  represents the charge in the backgate, so  $Q_{INV}$ =-( $Q_G$ + $Q_B$ ).

In this thesis we will develop explicit compact charge and capacitance models adapted for doped and undoped long-channel devices (doped DG MOSFETs, undoped DG MOSFETs, undoped UTB MOSFETs and undoped SGT) from a unified charge control model derived from Poisson's equation. We also show the impact of important geometrical parameters such as source and drain thickness, fin spacing, spacer width, etc. on the parasitic fringing capacitance component of multiplegate field-effect transistors (MuGFET). Our results have been verified with numerical simulation results from different numerical simulators and when allowable, with experimental results that were obtained at the Microelectronics Laboratory, Université Catholique de Louvain, Belgium. The thesis is organized as follows: Chapter (1) presents the state of the art,

UNIVERSITAT ROVIRA I VIRGILI

DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFETS

Oana Moldovan

ISBN:978-84-691-8839-2/DL:T-1263-2008

State of the Art and Current Trends for Multiple Gate MOS Devices

Chapter (2) the compact modeling of the four devices: doped DG MOSFETs, undoped DG MOSFETs, undoped UTB MOSFETs and undoped SGT; in Chapter (3) we study the fringing capacitances in MuGFETs. Finally Chapter (4) summarizes the work done and the future points that need to be studied.

UNIVERSITAT ROVIRA I VIRGILI

DEVENLOPMENT OF COMPACT SMALL SIGNAL QUASI STATIC MODELS FOR MULTIPLE GATE MOSFETS

Oana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

### Chapter 2

# Current, Charge and Capacitance Model for Multiple Gate MOSFETs

## 2A. Compact model for highlydoped symmetrical Double-Gate SOI MOSFETs

#### In this section

an analytical and continuous compact model is developed, for a highly-doped double gate SOI MOSFET, in which the channel current, charge and capacitances are expressed as continuous, explicit functions of the applied voltages. The model is based on a unified charge control model derived from Poisson's equation.

The results are compared with DG MOSFET simulations and FinFET experimental measurements [78]. Also, an extension to this model has been done, making it functional for a wide range of doping concentrations, between  $10^{14}$  and  $3x10^{18}$  cm<sup>-3</sup> [79].

#### 2A.1. Introduction

As explained before, among SOI devices, double-gate (DG) transistors are considered to be a very attractive option to improve the performance of CMOS devices and overcome some of the difficulties encountered in further downscaling of MOS field-effect transistors into the sub-50 nanometer gate length regime [2]. One of the limiting factors in MOSFET downscaling is the static power consumption, due to short channel effects (SCEs), such as threshold voltage roll-off, drain-induced barrierheight lowering (DIBL) and subthreshold slope degradation [80]. These effects increase the off state leakage current. In the DG MOSFETs, the control of the channel by the gate is stronger than in single gate MOSFETs. This leads to a significant reduction of DIBL, threshold voltage roll-off, off-state leakage and channel-length modulation [81,82].

Thanks to such advantages, DG devices will be one of the preferred devices in nanoscale circuits, thus calling for an accurate and CAD compatible DG SOI MOSFET model. Some Oana Moldovan

ISBN:978-84-691-8839-2/DL:T-1263-2008

Compact Model for Highly-Doped Symmetrical DG SOI MOSFETs

compact models have been introduced before, but they are valid only for undoped DG MOSFETs, like in [33,34,37,38,83], whereas actual devices are doped, due to the fact that there is a small unintentional doping during real process. Moreover, doping can be used to adjust the threshold voltage without the need of changing the gate material, targeting multi-V<sub>T</sub> processes which are very attractive [13]. In this section we present a model for the doped double gate MOSFET, which is analytical, explicit and continuous through all regimes of operation (from weak to strong inversion, as well as linear to saturation). It is based on a previous work done in [40], which presented a current model valid for low V<sub>DS</sub>. The current expression is based on a unified charge control model, written in terms of charge densities at the source and drain ends [84] and derived for a doped DG MOSFET. We use an accurate explicit expression of the inversion charge densities in terms of the applied bias. No fitting parameters are used in the charge control model. The model is valid up to well above threshold. This model includes expressions of current, charge and capacitances, thus resulting also in a complete small-signal model. Although the model has been developed from the 1D Poisson's equation in the direction perpendicular to the channel (which leads to neglecting shortchannel effects), it is in fact the first compact model developed for doped DG MOSFETs. Besides, short-channel effects are less stronger than in single gate devices with the same channel

Oana Moldovan

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

length. The explicit model of the channel current shows a good agreement with the 2D numerical device simulations and also with the experimental I-V measurements performed on comparable FinFETs. A good agreement is observed also for all the capacitances expressions compared to the 2D device numerical simulations. Therefore, this complete small signal model is suitable to be used in circuit simulators, a direct application targeting baseband analog designs in which very short transistors are not used, but moderate inversion is standard [85]. As mentioned above, an extension of this model has been done. A compact analytical model for long channel symmetric double-gate MOSFETs is presented in section 2A.3, which considers a doped silicon layer in a wide range of concentrations, between 10<sup>14</sup> and 3x10<sup>18</sup> cm<sup>-3</sup>. Analytical expressions are presented to model the behavior of the potential at the surface and the difference between potentials at the surface and at the center of the doped silicon layer. No fitting parameters are required. All the equations obtained for the potentials were validated using rigorous numerical calculation, for different doping concentrations as well as for several doublegate structure dimensions and applied voltages.

Using the expression for the potential and difference of potentials, analytical expressions for the current-voltage and capacitance-voltage characteristics are further derived. Comparison of modeled and simulated (using the ATLAS device simulator) transfer characteristics in linear and saturation regions, of output characteristics and of gate-drain and gate-source capacitance-voltage characteristics shows an excellent agreement within the practical range of gate and drain voltages, gate dielectric and silicon layer thicknesses.

#### 2A.2. Model

In doped double gate MOS transistors, in the normal operating regimes, the majority carrier concentration (holes) is negligible in comparison with electron carrier concentration so that by using the gradual channel approach [33,40] (therefore, neglecting the derivative of the lateral field in the direction of the channel length) Poisson's equation reads as:

$$\frac{d^2\phi(x,y)}{dy^2} = \frac{q}{\varepsilon_{Si}} \left[ N_A + n_e(x,y) \right] = \frac{q}{\varepsilon_{Si}} \left[ N_A + \frac{n_i^2}{N_A} e^{\frac{q}{kT} \left[\phi(x,y) - V(x)\right]} \right]$$

(2A.1)

Fig.2A.1 ATLAS simulation of the DG MOSFET considered

The y-axis is perpendicular to the surface and the x-axis starts in source (x=0) and ends in drain (x=L) region. Fig.2A.1 represents the ATLAS simulation of the DG MOSFET considered in this section. N<sub>A</sub> represents the doping density. The potential  $\phi(x,y)$ is referred to the neutral region of one equivalent bulk MOS transistor. V(x) is the electron quasi-Fermi potential depending on the voltage applied to the channel between source and drain ISBN:978-84-691-8839-2/DL:T-1263-2008

and is assumed to be independent of y [40]. The surface electric field can be written in terms of the mobile charge density (in absolute value) per unit area at each interface, Q, and the depletion charge density per unit area (in absolute value)  $Q_{Dep}=qN_At_{Si}$  ( $t_{Si}$  being the Si film thickness) whatever x:

$$E_{S}(x) = \frac{Q(x) + \frac{Q_{Dep}}{2}}{\varepsilon_{Si}}$$

(2A.2)

In order to obtain the  $I_{DS}(V_{GS})$  characteristic, we have to evaluate the surface electric field as a function of the gate voltage. Therefore we multiply both sides of Poisson's equation by  $2[d\phi(x)/dy]$ . Then, by integrating (2A.1) between the centre (y=0) and the top surface of the film (y=-t<sub>si</sub>/2) we obtain [40]:

$$E_{S}(x) = \sqrt{\frac{2qN_{A}}{\varepsilon_{Si}}} \sqrt{(\phi_{s} - \phi_{0}) + \frac{kT}{q} \frac{n_{i}^{2}}{N_{A}^{2}} e^{\frac{q}{kT} [\phi_{S} - V(x)]} \left(1 - e^{-\frac{q}{kT} (\phi_{s} - \phi_{0})}\right)}$$

(2A.3)

where  $\phi_S = \phi(x, -t_{Si}/2)$  is the surface potential and  $\phi_o = \phi(x, 0)$  is the potential in the middle of the film. Contrary to the bulk case where the potential at the end of the depletion region is known to be zero, in fully-depleted SOI unfortunately  $\phi_0$  is unknown and (2A.3) cannot be analytically integrated for the potential, but it is observed, from numerical simulations, that the difference  $\phi_S - \phi_0$  keeps a constant value from the subthreshold region to well above threshold [40]. In subthreshold, Poisson's

Oana Moldovan

equation can be reduced to its depletion form:

$$\frac{d^2\phi(x)}{dy^2} = \frac{qN_A}{\varepsilon_{Si}} \tag{2A.4}$$

therefore, the following expression is obtained for the difference  $\phi_S - \phi_0$ .

$$\phi_{S} - \phi_{0} = \frac{qN_{A}t_{Si}^{2}}{8\varepsilon_{Si}} = \frac{Q_{Dep}}{8C_{Si}}$$

(2A.5)

where  $C_{Si} = \varepsilon_{Si} / t_{Si}$  represents the silicon film capacitance. This approximation is valid from subthreshold to well above threshold, which is demonstrated by the correct agreement with simulations and measurements, for low and moderate V<sub>GS</sub>(~2V) and for all V<sub>DS</sub> values [40]. For high V<sub>GS</sub>, the surface potential increases much more rapidly than the mid-film potential, making the approximation less correct. However, the numerical simulations have shown that (2A.5) is not a bad approximation for highly-doped devices (N<sub>A</sub> $\ge 10^{17}$  cm<sup>-3</sup>), even well above

threshold. The term  $e^{-\frac{q}{kT}\frac{Q_{Dep}}{8C_{Si}}}$ , coming from (2A.3) and (2A.5), has been neglected, but this is also a valid approximation for highly doped devices. In Fig.2A.2 we can see that the increase of the difference between the surface and mid-film potentials is certainly small (less than 0.1V), up to well above threshold. The validity of the above approximation from subthreshold to well above threshold will also be proved/supported by the good agreement between model and numerical simulations.

Equating (2A.2) and (2A.3), applying the Kirchoff voltage law applied on the gate oxide, and using the two approximations discussed above, we obtain the following charge control model:

$$V_{GS} - V_{FB} - V - \left(\frac{Q_{Dep}}{2C_{ox}} + \frac{kT}{q} \log \left[\frac{q^{2}}{kT} \frac{N_{A}^{3}}{n_{i}^{2}} \frac{t_{Si}^{2}}{2\varepsilon_{Si}}\right]\right) =$$

$$= \frac{Q}{C_{ox}} + \frac{kT}{q} \log \left[\frac{Q}{Q_{Dep}}\right] + \frac{kT}{q} \log \left[\frac{Q + Q_{Dep}}{Q_{Dep}}\right]$$

(2A.6)

Note that V varies from source to drain, being V=0 at the source and V= $V_{DS}$  at the drain [84].  $V_{FB}$  is the flat-band voltage,  $C_{ox}$  the oxide capacitance per unit area.

Fig.2A.2 Difference between the surface and mid-film potentials  $\phi_S - \phi_0$  of the DGMOSFET, as a function of the gate voltage. Simulation conditions: doping level  $N_A=6\cdot10^{17}~{\rm cm}^{-3}$ ; silicon film thickness  $t_{Si}$ =31nm; effective oxide thickness  $t_{ox}$ =2nm; channel length  $L=1\mu m$  and width  $W=1\mu m$

#### **2A.2.1 Drain Current Model**

The drain current is calculated, as usually, from:

$$I_{DS} = \frac{2W\mu}{L} \int_{0}^{V_{DS}} Q(V)dV$$

(2A.7)

where W represents the width of the device, µ the effective mobility of the electrons and L the channel length. The term 2 appears because of the 2 gates.

ISBN:978-84-691-8839-2/DL:T-1263-2008

From (2A.6) we get:

$$dV = -\frac{dQ}{C_{ox}} - \frac{kT}{q} \left( \frac{dQ}{Q} + \frac{dQ}{Q + Q_{Dep}} \right)$$

(2A.8)

Therefore the expression of  $I_{DS}$  can be written in terms of carrier charge densities. Integrating (2A.7) using (2A.8), between  $Q_s$  and  $Q_d$  (Q=Q<sub>s</sub> at source end and Q=Q<sub>d</sub> at the drain end), we have:

$$I_{DS} = \frac{2W\mu}{L} \left[ 2\frac{kT}{q} (Q_s - Q_d) + \frac{Q_s^2 - Q_d^2}{2C_{ox}} + \frac{kT}{q} Q_{Dep} \log \left[ \frac{Q_d + Q_{Dep}}{Q_s + Q_{Dep}} \right] \right]$$

(2A.9)

In order to compute the charge densities from an explicit expression of the applied bias, since (2A.6) does not yield a closed form for Q, we find an approximate explicit expression of Q in the asymptotic limits of subthreshold and above threshold.[84]. We can see that in (2A.6), well above threshold the two logarithmic terms in RHS (Right-Hand-Side) are smaller than the first term in RHS, and (2A.6) can be approximated as:

$$V_{GS} - V_{FB} - V - \left(\frac{Q_{Dep}}{2C_{ox}} + \frac{kT}{q} \log \left[\frac{q^2}{kT} \frac{N_A^3}{n_i^2} \frac{t_{Si}^2}{2\varepsilon_{Si}}\right]\right) = \frac{Q}{C_{ox}}$$

(2A.10)

and therefore

$$Q = C_{ox} (V_{GS} - V_0 - V)$$

(2A.11)

ISBN: 978-84-691-8839-2/DL: T-1263-2008 Development of Compact Small-Signal Quasi Static Models for MuGFETs

where