### Eliana Isabel Arango Zuluaga

# Modelling and Control of an Asymmetric Interleaved DC to DC Switching Converter

**Doctoral Thesis**

Supervisors

Dr. Javier Calvente Calvo

Dr. Roberto Giral Castillón

Departament d'Enginyeria Electrónica Elèctrica i Automàtica

Tarragona 2009

### Departament d'Enginyeria Electrònica, Elèctrica i Automàtica Escola Tècnica Superior d'Enginyeria

Edifici L-1, 3a planta despatx 331 Avda. Paisos Catalans, 26 Campus Sescelades 43007 Tarragona SPAIN Tel.:+ 34 977 559 610 Fax:+ 34 977 559 605

We, Javier Calvente Calvo and Roberto Giral Castillón, associate professors in the Department of Electronics, Electric and Automatic Engineering of the Rovira i Virgili University,

#### CERTIFY:

That the present work, entitled "Modelling and Control of an Asymmetric Interleaved DC to DC Switching Converter", submitted by Eliana Isabel Arango Zuluaga for the award of the degree of Doctor, has been carried out under our supervision at the Department of Electronics, Electric and Automatic Engineering of this university.

| Tarragona, April 20th, 2009. |                               |

|------------------------------|-------------------------------|

|                              |                               |

|                              |                               |

|                              |                               |

|                              |                               |

|                              |                               |

| Javier Calvente Calvo, PhD.  | Roberto Giral Castillón, PhD. |

ROVIRA I VIRGILI UNIVERSITY MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

### AGRADECIMIEN70S

La elaboración de mi tesis doctoral ha sido no sólo un proceso intelectual y académico, sino también un proceso personal, que ha hecho de la futura doctora que escribe estas líneas, una mujer integramente capacitada para los retos de su desempeño profesional.

En cuanto a lo académico, agradezco especialmente a:

Mi Director de Tesis Javier Calvente Calvo, por haber sabido reconducir mi trabajo de tesis aportando claridad y metodología, por desempeñar su labor con paciencia, constancia y buen ánimo; y por la confianza que depositó en mí, al conseguirme la ayuda que permitió llevar esta tesis a buen puerto.

Mi Codirector de Tesis Roberto Giral Castillón, por haber orientado el inicio del doctorado, por sus ideas creativas que dieron origen a esta tesis, por su colaboración con las mediciones experimentales y por las múltiples revisiones y correcciones de todo este manuscrito.

Por su ayuda con el trabajo de laboratorio también doy las gracias a Josep María Bosque y a Carlos Ramos.

Agradezco a Alexander Vergara su ayuda en la corrección lingüística del capítulo 1 A mis compañeros de laboratorio, Carlos Restrepo y Carlos Torres, les doy las gracias por el buen ambiente de trabajo y su ayuda con los programas de dibujo.

Agradezco en general a todos los miembros del Grupo de Automática y Electrónica Industrial (GAEI) y del Departamento de Ingeniería Electrónica, Eléctrica y Automática (DEEEA), especialmente a todo el Personal de Administración y Servicios, por su colaboración oportuna en diferentes momentos y aspectos del desarrollo de esta tesis.

A la Universitat Rovira i Virgili, el DEEEA y el GAEI, agradezco la beca predoctoral y demás ayudas económicas que hicieron posible la realización de este trabajo.

En cuanto a lo personal, quiero mencionar a quienes han dejado un aporte especial en mi vida:

Gracias a mi JAMILIA en Tarragona, mis actuales y anteriores compañeras de piso: Lorena, Paula Andrea, Marlene, Noelia, Marina, Sabine y Danja.

Loli: ¡Gracias! Tu guía ha sido decisiva en mi proceso personal: Has creado un oasis del alma. Gracias a tus colaboradores y alumnos, especialmente a Jose M.

ISBN:978-84-692-6903-9 / DL:T-1849-2009 Modelling and control of an asymmetric interleaved DC to DC switching converter

Anna i Carles: ¡Gràcies! l'amistat que m'heu brindat m'ha ajudat a recuperar la confiança. Gràcies també per la guia amb flors de bach, pnl, kinesiologia i ioga.

Mi corazón agradece a dos amigas que han estado siempre presentes, que han sabido iluminar algunos momentos de oscuridad con sus palabras, su compañía y esos abrazos oportunos y necesarios: Nuria y Stella.

Agradezco la ayuda econômica brindada por Luz Helena, Gloria Elena y Diego.

Gracias a mis amigas y a mis amigos que me han apoyado con paciencia y cariño en diferentes espacios y momentos de este proceso: Justyna, Maru, Isabel, Cata, Vessy, Olguita, Alexander, Olimpo, Erney y Jorge Alberto.

Agradezco a mis compañeras y compañeros de la Sec-DEIM: Olga, Mónica y Xavier y al DEIM en general, por brindarme un ambiente de trabajo agradable y de aceptación y por darme muchos ánimos en mis últimos años de tesis.

Doy las Gracias a quienes me ayudaron a reencontrarme con mi vocación docente y, sin saberlo, me brindaron una motivación más para terminar mi tesis, mis alumnas y alumno: Aïda, Clara, Elena, Irene, Andrea y Víctor.

Zuiero agradecer a todas las personas de nacionalidades diferentes con quienes compartí en estos años, por la oportunidad de aprender acerca de otras culturas, de otras formas de entender, sentir y vivir la vida.

A todos mis familiares y mis amigos de Colombia, que no alcanzaría a mencionar aquí uno a uno, doy las gracias por el interés que demostraron siempre en mis avances con este trabajo de tesis.

Para toda mi gran y hermosa familia, las palabras no alcanzan para expresar mi gratitud. Todos han confiado siempre en mis capacidades, incluso en los momentos en que yo misma había perdido la confianza. Han respetado mi proceso y me han amado siempre sin juzgarme. Me han apoyado de todas las maneras posibles: económicamente, con sus palabras, sus oraciones y su amor. Y su presencia constante en mi vida, a pesar de la lejanía física, me ha ayudado a recuperar la confianza y la fe. Gracias Madre y Padre: María del Socorro y Tomás. Gracias Hermanas y Hermanos: Gloria Patricia, Ana Milena, Juan Fernando, David Alejandro y Andrés Felipe. Gracias también a sus Esposas y Esposo: Berenice, Claudia Andrea y Javier. Gracias a los pequeños: Matthew, Melisa, Juan José y Tomás por las alegrías y sonrisas. Gracias a mi Abuelita Julia, a mi padrino Guillermo y a mi Tío Gabriel.; Los amo! mi sentimiento de gratitud con ustedes es inconmensurable.

Por último, parafraseando una canción de Violeta Parra:

"¡Gracias a la vida que me ha dado tanto!

Me dio el corazón que agita su marco:

¡Cuando miro el fruto del cerebro humano!

¡Gracias a la vida!...

¡Gracias a la vida!"

# **ABSTRACT**

The two main topics presented in this thesis are the generation and mathematical modelling of new converter structures.

The fundamental idea behind the methodology used to generate the new converter structures was to break the symmetry. This involved modifying the circuit structure on the basis of the simulation results. This methodology allowed the generation of the family of asymmetrical interleaved converters, which consists of the AIDB, the AIDBB and the AIDF-group.

A new conceptual modelling approach was developed on the basis of ideas taken from previous research which is reviewed in the state of the art. This approach was called Modified Averaging Using Graphical Methods. Because of its features, this new method can be used to model the state space average of the new converter family presented here.

The accuracy of the AIDB converter small signal model was verified by measuring the frequency response and by designing an LQR controller.

### RESUMEN

La generación de nuevas estructuras convertidoras y su modelado matemático son las dos temáticas principales estudiadas en esta tesis.

El seguimiento de una metodología que modifica la estructura del circuito, realizando una ruptura de la simetría con base en los resultados de simulación, permitió generar la familia de convertidores en "interleaving" asimétrico compuesta por el AIDB, el AIDBB y el grupo-AIDF.

En el apartado de modelado se ha desarrollado una nueva aproximación conceptual inspirada en las ideas de trabajos previos que se estudian en el estado del arte. El nombre dado a esta nueva aproximación es: Promediado Modificado Usando Métodos Gráficos. Este nuevo enfoque ha sido utilizado para obtener el modelo promediado de la nueva familia de convertidores en el espacio de estados.

Las mediciones experimentales de la respuesta en frecuencia del convertidor AIDB y el diseño del controlador LQR permitieron verificar la aproximación del modelo en pequeña señal obtenido.

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

Modelling and control of an asymmetric interleaved DC to DC switching converter

This page was left blank intentionally.

# **CONTENTS**

| INTRODUCTION                                                                                      | 1              |

|---------------------------------------------------------------------------------------------------|----------------|

| 1. STATE OF THE ART: GENERATION AND MODELLING OF DC-TO-DC SWITCHING CONVERTERS                    | 3              |

| 1.1 Elementary aspects of DC-TO-DC SWITCHING CONVERTERS  1.1.1 The PWM controlled boost converter | <b> 4</b><br>4 |

| 1.2 GENERATION AND CLASSIFICATION OF PWM DC-TO-DC CONVERTERS                                      | 7              |

| 1.2.1 The converter cell                                                                          | 8              |

| 1.2.1.1 Another schemes of generation and classification                                          | 9              |

| 1.2.1.2 Converter analysis with converter cells                                                   | 10             |

| 1.2.2 The interleaving as a strategy of converter generation                                      | 10             |

| 1.2.2.1 Complementary interleaving                                                                | 11             |

| 1.3 SWITCHING CONVERTERS OPERATION MODES                                                          | - 12           |

| 1.3.1 Continuous conduction mode CCM                                                              |                |

| 1.3.2 Discontinuous conduction mode DCM                                                           | 12             |

| 1.3.3 Discontinuous quasi-resonant mode DQRM                                                      | 13             |

| 1.3.4 Other discontinuous modes                                                                   | 14             |

| 1.3.5 Example                                                                                     | 14             |

| 1.4 An overview in converters modelling and simulation                                            | 16             |

| 1.4.1 Initial analysis and simulation                                                             |                |

| 1.4.2 Mathematical and Circuit Modelling                                                          | 17             |

| 1.4.2.1 Switched state-space model method                                                         | 18             |

| 1.4.2.2 State space averaged modelling method                                                     | 20             |

| 1.4.2.3 Injected-absorbed current method                                                          | 28             |

| 1.4.2.4 Circuit averaging and the averaged switch methods                                         | 30             |

| 1.4.2.5 Generalized averaging and dynamic phasors                                                 | 34             |

| 1.4.2.6 Sampled-data modelling method                                                             | 36             |

| 1.4.3 A specialization in converters modelling: the DCM mode                                      | 40             |

| 1.4.3.1 Reduced-order averaged models                                                             | 40             |

| 1.4.3.1.1 Conventional state-space averaging                                                      | 41             |

| 1.4.3.1.2 Slow-fast variables approach 1.4.3.1.3 Circuit averaging                                | 44             |

| 1.4.3.1.3 Circuit averaging                                                                       |                |

| 1.4.3.2.1 Equivalent duty ratio method                                                            | <del>4</del> 5 |

| 1.4.3.2.2 Average-switch models                                                                   | 46             |

| 1.4.3.2.3 Sampled Data Models                                                                     |                |

| 1.4.3.2.4 Current Injected Approach                                                               | 52             |

| 1.4.3.2.5 Loss-free resistor model                                                                | 52             |

| 1.4.3.2.6 Revised averaging approach                                                              | 53             |

| 1.4.3.3 Later Developments                                                                        | - 60           |

| 1.4.4 Simulation of switched and averaged dynamic models                                          | 62             |

| 1.4.4.1 Transient response analysis                                                               | 63             |

| 1.4.4.2 Steady-state and small-signal analysis                                                    | 63             |

| 1.4.4.3 Use of simulators in circuit generation                                                   | 63             |

ROVIRA I VIRGILI UNIVERSITY MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

| i | Modelling and control | l of an a | asymmetric | interleaved DO | c to D | C switching conve | erter |

|---|-----------------------|-----------|------------|----------------|--------|-------------------|-------|

|---|-----------------------|-----------|------------|----------------|--------|-------------------|-------|

|    | 1.5 Chapter conclusions                                                     | - 64  |

|----|-----------------------------------------------------------------------------|-------|

|    | 1.6 REFERENCES                                                              | 66    |

| 2. | ASYMMETRICAL INTERLEAVED DC-TO-DC SWITCHING CONVERTERS CIRCUITS: GENERATION | ı73   |

|    | 2.1 THE BASIC INTERLEAVING CONCEPT                                          |       |

|    | 2.2 THE PREVIOUS WORKS                                                      |       |

|    | 2.2.1 Complementary interleaving                                            |       |

|    | 2.2.2 Initial Circuit: IDB                                                  | 77    |

|    | 2.2.3 Modifications of the IDB converter                                    |       |

|    | 2.2.4 The Switched Capacitor Inductor Dual Boost – SCIDB                    | 78    |

|    | 2.3 GENERATION OF THE ASYMMETRICAL INTERLEAVED DUAL BOOST AIDB              | - 80  |

|    | 2.3.1 The first modifications introduced to SCIDB                           |       |

|    | 2.3.2 The AIDB                                                              | 82    |

|    | 2.4 AIDB OPEN LOOP SIMULATION RESULTS                                       | 83    |

|    | 2.4.1 Analysis of the results: waveforms and tables                         | 83    |

|    | 2.4.2 AIDB topologies                                                       | 88    |

|    | 2.4.3 First approximation of the AIDB operating point                       | 89    |

|    | 2.4.3.1 Mean values of the capacitor voltages in steady state               | 90    |

|    | 2.4.3.2 Expressions for the duration of the operation intervals             | 90    |

|    | 2.4.3.3 Mean values of the inductor currents in steady state                | 91    |

|    | 2.4.3.4 Comparisons with the simulation results                             | 92    |

|    | 2.4.4 Comparison between AIDB and interleaving boost including parasitics   |       |

|    | 2.5 THE FAMILY OF ASYMMETRICAL INTERLEAVING CONVERTERS                      | 96    |

|    | 2.5.1 The AIDBB                                                             |       |

|    | 2.5.1.1 Structure generation                                                | 9/    |

|    | 2.5.1.2 Simulation results: Waveforms                                       |       |

|    | 2.5.1.4 AIDBB Topologies                                                    |       |

|    | 2.5.1.4 AIDBB Topologies                                                    |       |

|    | 2.5.1.5.1 Mean values of the capacitor voltages in steady state             |       |

|    | 2.5.1.5.2 Expressions for the duration of the operation intervals           |       |

|    | 2.5.1.5.3 Mean values of the inductor currents in steady state              |       |

|    | 2.5.1.6 Comparison with the IBB                                             | 105   |

|    | 2.5.2 The AIDF-group                                                        |       |

|    | 2.5.2.1 Generation of the converters' group                                 | 106   |

|    | 2.5.2.2 Analysis of simulation results: waveforms and tables                | 106   |

|    | 2.5.2.3 Topologies of the AIDF-group                                        | - 109 |

|    | 2.5.2.3.1 Topologies of the positive output AIDF                            | - 109 |

|    | 2.5.2.3.2 Topologies of the negative output AIDF                            | 110   |

|    | 2.5.2.3.3 Topologies of the others converters of the AIDF-group             |       |

|    | 2.5.2.4 First approximation to the AIDF-group operating point               |       |

|    | 2.5.2.4.1 Mean values of the capacitor voltages in steady state             |       |

|    | 2.5.2.4.2 Mean values of the inductor currents in steady state              | - 112 |

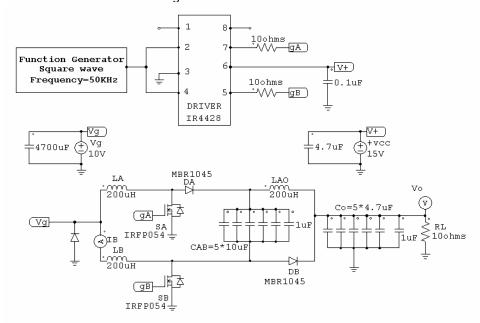

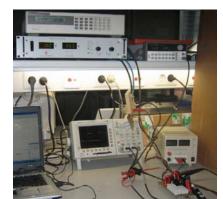

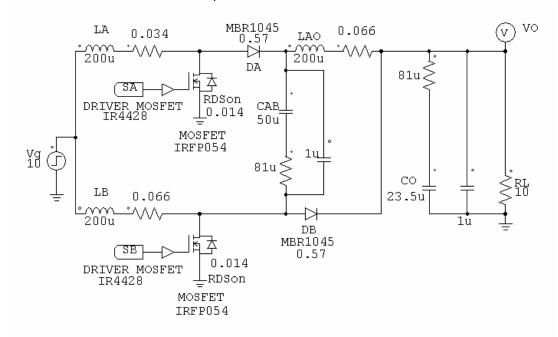

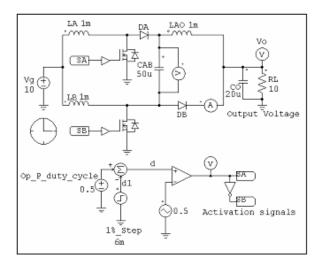

|    | 2.6 OPEN LOOP EXPERIMENTAL RESULTS IN TIME DOMAIN                           | 114   |

|    | 2.6.1 AIDB circuit prototype                                                | - 114 |

|    | 2.6.2 PSIM Simulations of the AIDB circuit prototype                        | - 116 |

ISBN:978-84-692-6903-9 / DL:T-1849-2009

Contents

iii

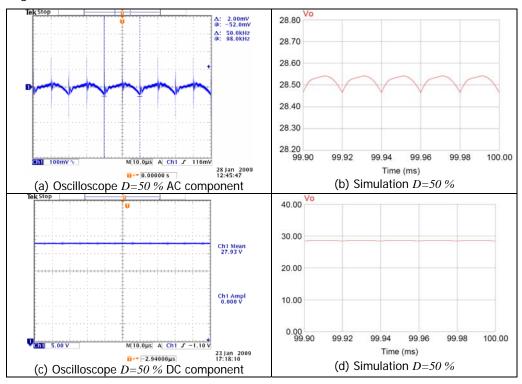

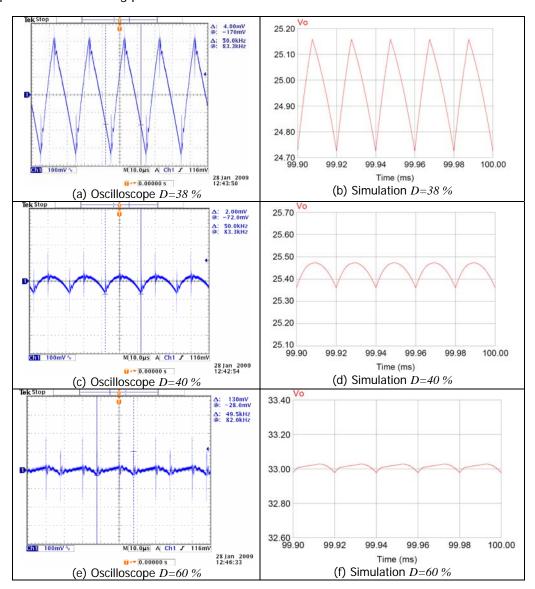

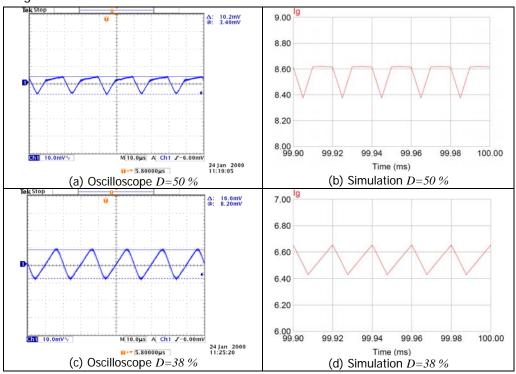

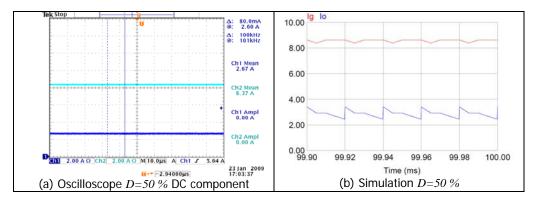

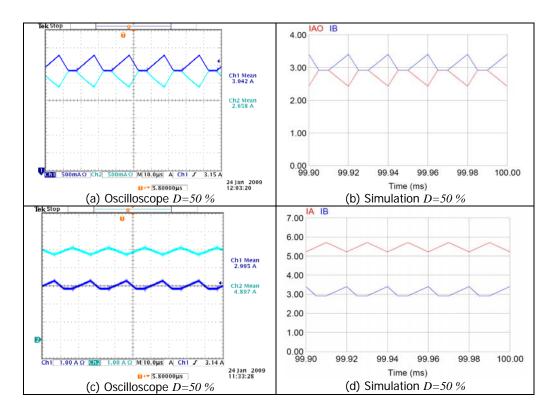

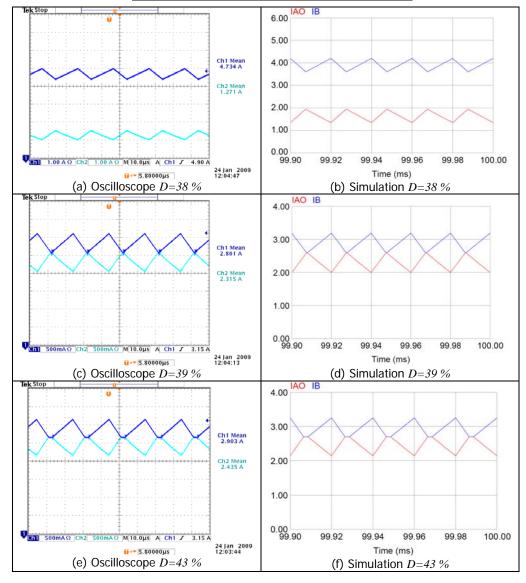

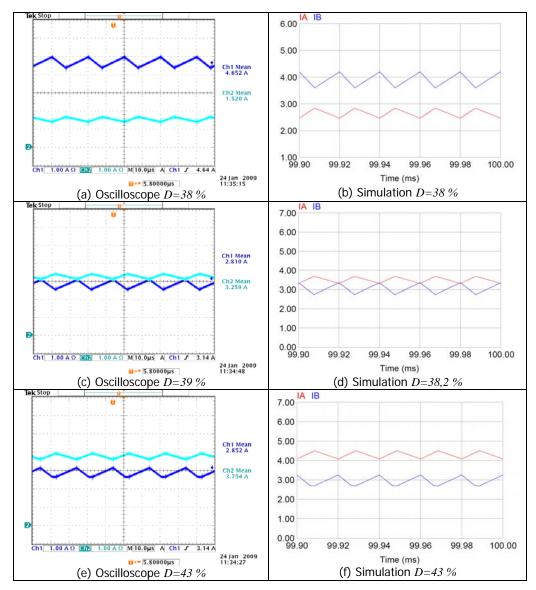

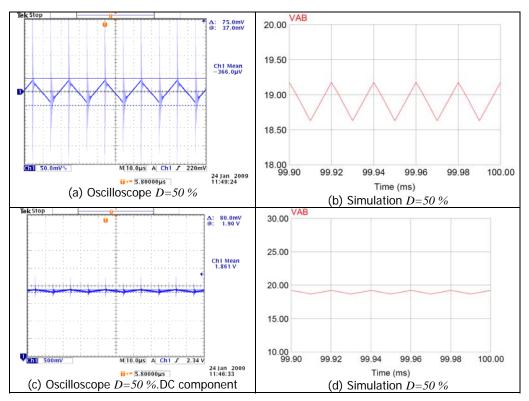

|               | 2.6.3 Experimental measurements, simulations and comparisons       | 116 |

|---------------|--------------------------------------------------------------------|-----|

|               | 2.6.3.1 Output Voltage Waveforms                                   | 117 |

|               | 2.6.3.2 Input Current Waveforms                                    | 119 |

|               | 2.6.3.3 DC values of input and output currents                     | 119 |

|               | 2.6.3.4 Inductor Current Waveforms                                 | 120 |

|               | 2.6.3.5 Intermediate capacitor voltage waveforms                   | 123 |

|               | 2.6.3.6 Comparative Graphics                                       | 124 |

| 2             | 2.7 Chapter conclusions                                            | 126 |

| 2             | 2.8 References                                                     | 127 |

|               |                                                                    |     |

| 3. <b>A</b> s | YMMETRICAL INTERLEAVED DC TO DC SWITCHING CONVERTERS CIRCUITS: MOD |     |

| 3             | 3.1 AIDB ANALYSIS                                                  |     |

|               | 3.1.1 AIDB Modelling using the revised averaging method            | 130 |

|               | 3.1.1.1 Averaging and correction applied to the AIDB converter     | 130 |

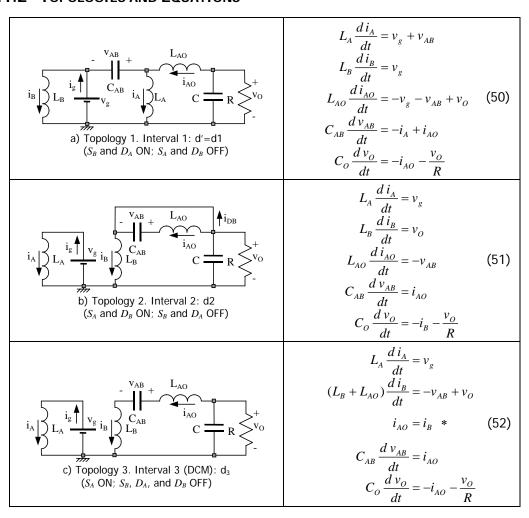

|               | 3.1.1.1.1 Topologies and equations                                 | 130 |

|               | 3.1.1.1.2 Conventional averaging                                   |     |

|               | 3.1.1.1.3 Correction                                               |     |

|               | 3.1.1.2 Duty-ratio constraint applied to the AIDB converter        |     |

|               | 3.1.1.3 New method for calculating the second duty cycle           |     |

|               | 3.1.1.4 SSA for the AIDB using the revised averaging               | 135 |

|               | 3.1.1.4.1 Operating point                                          |     |

|               | 3.1.1.4.2 Linear equations around the operating point              | 137 |

|               | 3.1.1.4.3 Small Signal Transfer Functions                          | 138 |

|               | 3.1.1.5 Simulations in the frequency domain                        | 138 |

|               | 3.1.2 The new modified averaging approach applied to AIDB          | 139 |

|               | 3.1.2.1 Origins of the new approach                                | 139 |

|               | 3.1.2.2 Modifications in topology and equations                    | 139 |

|               | 3.1.2.3 New SSA for the AIDB including modifications               | 140 |

|               | 3.1.2.4 Graphical calculation of the new variable                  |     |

|               | 3.1.2.5 SSA of the AIDB by the modified averaging approach         | 143 |

|               | 3.1.2.5.1 Operating point                                          |     |

|               | 3.1.2.5.2 Operating point by an averaging on the waveforms         |     |

|               | 3.1.2.5.3 Linear equations around the operating point              | 146 |

|               | 3.1.2.5.4 Small Signal Transfer Functions                          | 147 |

|               | 3.1.2.6 Simulations in frequency domain                            | 147 |

| 3             | 3.2 MODIFIED AVERAGING USING GRAPHICAL METHODS                     | 148 |

|               | 3.2.1 Previous work                                                |     |

|               | 3.2.2 Detail description of this new approach                      | 149 |

|               | 3.2.2.1 Modifications included                                     | 149 |

|               | 3.2.2.2 Steps                                                      | 149 |

|               | 3.2.2.3 Why is it necessary to apply this new approach?            | 149 |

|               | 3.2.2.4 Converters analyzed with this method                       | 150 |

| 3             | 3.3 Applying modified averaging using graphical methods            | 150 |

|               | 3.3.1 Analysis of the AIDBB                                        | 150 |

|               | 3.3.1.1 Previous simulations                                       | 150 |

|               | 3.3.1.2 Topologies and Equations                                   |     |

|               | 3.3.1.3 Averaging                                                  | 152 |

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

|      | 3                                                                                                        | .3.1.4 Additional variables calculation                       | 152                                            |

|------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|

|      | 3                                                                                                        | .3.1.5 SSA with the modifications included                    | 153                                            |

|      | 3                                                                                                        | .3.1.6 Operating point                                        |                                                |

|      |                                                                                                          | 3.3.1.6.1 Linear equations around the operating point         | 154                                            |

|      | 3                                                                                                        | .3.1.7 Small signal transfers functions                       | 154                                            |

|      |                                                                                                          | Analysis of the AIDF-group                                    |                                                |

|      |                                                                                                          | .3.2.1 Previous simulations                                   |                                                |

|      | 3                                                                                                        | .3.2.3 Averaging                                              | 150<br>156                                     |

|      |                                                                                                          | .3.2.4 Additional variables calculation                       |                                                |

|      |                                                                                                          | .3.2.5 Operating point                                        |                                                |

|      |                                                                                                          | 3.3.2.5.1 Linear equations around the operating point         | 158                                            |

|      | 3                                                                                                        | .3.2.6 Small signal transfers functions                       | 159                                            |

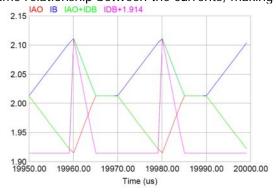

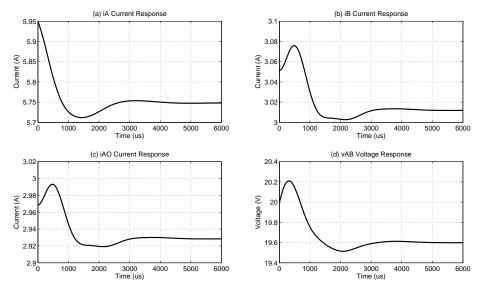

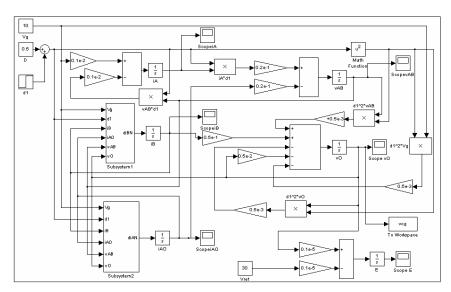

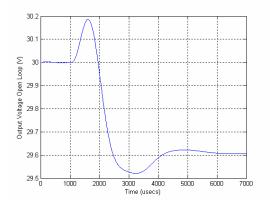

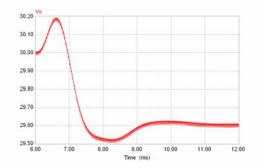

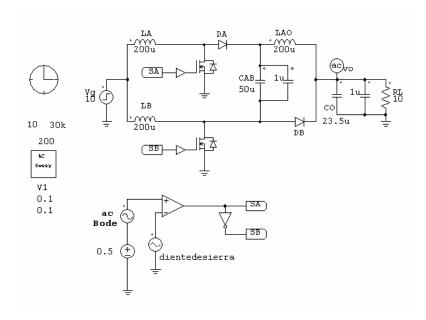

|      | 3.4                                                                                                      | IMULATION RESULTS OF THE AIDB IN TIME DOMAIN                  | 159                                            |

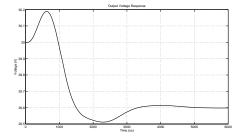

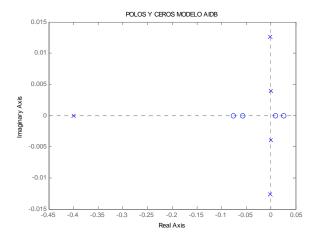

|      | 3.5 A                                                                                                    | IDB SIMULATION RESULTS IN FREQUENCY DOMAIN                    | 162                                            |

|      |                                                                                                          | PSIM simulations                                              |                                                |

|      |                                                                                                          | MATLAB simulations                                            |                                                |

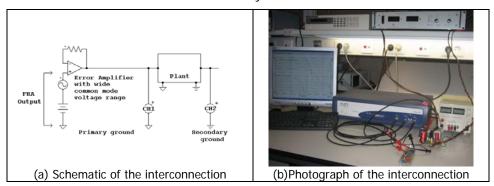

|      |                                                                                                          | XPERIMENTAL RESULTS IN FREQUENCY DOMAIN                       |                                                |

|      | 3.7                                                                                                      | CHAPTER CONCLUSIONS                                           | 165                                            |

|      | 3.8 F                                                                                                    | References                                                    | 166                                            |

| 4    | Δενμιμετ                                                                                                 | RICAL INTERLEAVED DUAL BOOST: CONTROL DESIGN AND APPLICATIONS | 167                                            |

| ••   |                                                                                                          | QUADRATIC OPTIMAL CONTROL                                     |                                                |

|      |                                                                                                          | Solving quadratic optimal control problems with MATLAB        |                                                |

|      | 4.2                                                                                                      | QUADRATIC OPTIMAL CONTROL DESIGN FOR THE AIDB                 | 169                                            |

|      | 4.2.1                                                                                                    | General assumptions                                           |                                                |

|      |                                                                                                          | e orror ar accumption to                                      | 169                                            |

|      | 4.2.2                                                                                                    | Controllability verification                                  | 170                                            |

|      | 4.2.3                                                                                                    | Controllability verification Last state equation              | 170<br>172                                     |

|      | 4.2.3                                                                                                    | Controllability verification                                  | 170<br>172                                     |

|      | 4.2.3<br>4.2.4<br><b>4.3</b> (                                                                           | Controllability verification                                  | 170<br>172<br>172<br><b> 174</b>               |

|      | 4.2.3<br>4.2.4<br><b>4.3</b> (                                                                           | Controllability verification                                  | 170<br>172<br>172<br><b> 174</b>               |

|      | 4.2.3<br>4.2.4<br><b>4.3 0</b><br>4.3.1<br>4.3.2                                                         | Controllability verification                                  | 170<br>172<br>172<br><b> 174</b><br>175        |

|      | 4.2.3<br>4.2.4<br><b>4.3 0</b><br>4.3.1<br>4.3.2                                                         | Controllability verification                                  | 170<br>172<br>172<br><b> 174</b><br>175        |

|      | 4.2.3<br>4.2.4<br><b>4.3 0</b><br>4.3.1<br>4.3.2<br>4.3.3                                                | Controllability verification                                  | 170<br>172<br>172<br><b> 174</b><br>175<br>177 |

|      | 4.2.4<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4.4<br>4.4.1                                              | Controllability verification                                  | 170<br>172<br>174<br>174<br>175<br>177<br>180  |

|      | 4.2.4<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.4.1<br>4.4.2                                       | Controllability verification                                  | 170 172 174 175 177 177 180 180                |

|      | 4.2.4<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.4.1<br>4.4.2                                       | Controllability verification                                  | 170 172 174 175 177 177 180 180                |

|      | 4.2.3<br>4.2.4<br>4.3 0<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4.1<br>4.4.1<br>4.4.2<br>4.4.3                   | Controllability verification                                  | 170 172 174 175 177 180 181                    |

|      | 4.2.4<br>4.3 (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4 (<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 (                   | Controllability verification                                  | 170 172 174 175 177 177 180 181                |

| Conc | 4.2.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4.1<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5<br>4.6                       | Controllability verification                                  | 170 172 174 175 177 180 181 183                |

|      | 4.2.3<br>4.2.4<br>4.3 (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4 4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 (<br>4.6 F | Controllability verification                                  | 170 172 174 175 177 180 181 183 184            |

# INTRODUCTION

A continuing objective in the field of power electronics is to generate new and improved structures of switching converter circuits.

The work presented here, as its title suggests, begins with the development of a new converter structure with interesting features in order to increase its range of possible applications.

The starting point of this development is a structure designed in a previous thesis that will be studied at the beginning of Chapter Two. Then, a new converter is developed using a methodology that will also be described in detail in that chapter.

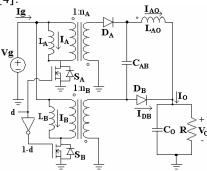

The converter is named the Asymmetrical Interleaved Dual Boost Converter (AIDB) for two reasons: the methodology used in its development and its operation features.

Other converter circuits with similar characteristics to the AIDB are developed by applying the same methodology to different basic converters. The advantages of the entire family of Asymmetrical Interleaved Converter Circuits are verified by simulation, as will be seen in Chapter Two.

The initial goal was to make a mathematical analysis of the new converter to further explore the characteristics of the plant and to obtain the model-based controller that would allow the output voltage to be regulated in the presence of disturbances. The first attempts to achieve this goal involved mathematical modelling using the traditional method of state space averaging; however, this did not provide suitable results.

After that, it was decided to focus this thesis on the issue of converters modelling and to begin a comprehensive study of the state of the art in this field. The initial aim was to find a method that would allow the converter modelling. However a second objective was achieved with this global review: enough information in this field that provides the basis for developing a new mathematical modelling approach.

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

2 Modelling and control of an asymmetric interleaved DC to DC switching converter

Therefore, the first chapter of this thesis will present a brief introduction into general aspects of converters followed by this exhaustive study of modelling methods in continuous conduction mode (CCM) and discontinuous conduction mode (DCM).

The first chapter will also include a review of methods for classifying and generating DC-to-DC converters in PWM because the original aim of this study was to generate a new converter structure. Some analytical approaches are described at the beginning because they are the basis of almost all the most popular DC-to-DC converters circuits used nowadays. After this, another approach to the generation of new converter structures is revised, this providing the starting point of the new converter developed in this study.

That chapter also presents a review of the conduction modes of converters because the new converter family generated shows an unusual combination of conduction modes, resulting in the interesting behaviour that gives the name to the family.

Specifically in the case of modelling methods in DCM, the review concludes with the study of the more recent work in this area. Its contributions were the inspiration for the changes introduced in the traditional averaging method that will be developed in the third chapter.

The second chapter of this thesis explores the method of generating the new converter structure and shows the results obtained by the simulations and by the measurements with the experimental prototype. The simulations were made for both the first new converter and the new family of converters that had been generated using the same methodology but starting from other basic circuits. These results are useful for determining the advantages of the new converter family.

This chapter also describes the first approximation of the steady state analysis and the comparison of the AIDB converter's open loop experimental results with those obtained in simulations.

The third chapter is the central chapter of this thesis and describes the procedure followed in obtaining the new modelling approach based on graphical methods. The chapter presents the mathematical calculations used to find the state space averaged model of the converter through the new modified approach. It will also describe the steady state analysis and the linearized small-signal model around an operating point.

Some comparisons are then made between the results obtained by each of the modelling methods in the time domain. The comparisons in the frequency domain include the experimental measurements made in open loop using the frequency response analyzer.

The new modelling approach is also used to find the small signal model of the new family of asymmetrical interleaved converters, the results being shown in the third chapter.

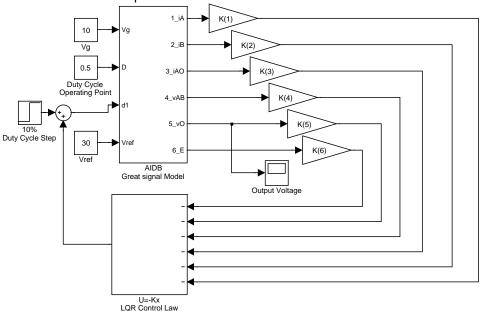

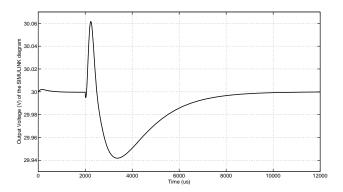

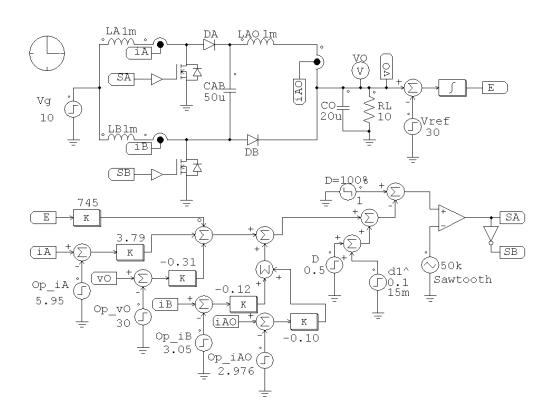

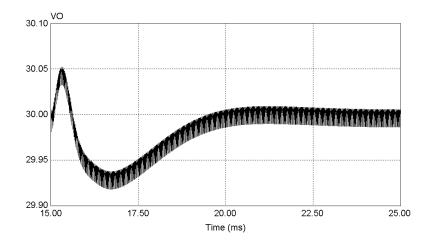

The fourth chapter makes use of the recently calculated small signal model of the AIDB converter for the controllability calculation and the Linear Quadratic Regulator (LQR) control design.

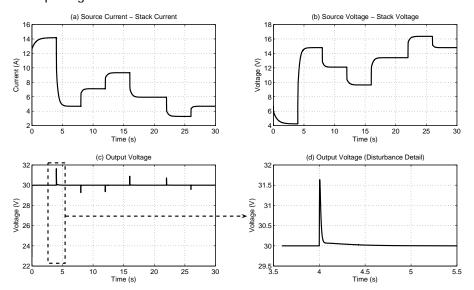

This chapter will also present the simulation results of the interconnection of the AIDB controlled converter with a Fuel Cell, an application that is possible because of certain features inherent in the AIDB converter. The simulation results will allow an initial verification to be made using the simulations of the converter operation with a model of a real source.

Finally, the conclusions of the thesis will be presented and will suggest possible areas for future research on the basis of the results obtained in this thesis.

## CHAPTER 1

### **STATE OF THE ART:**

# GENERATION AND MODELLING OF DC-TO-DC SWITCHING CONVERTERS

Power conversion emerged as an interdisciplinary field that requires a fundamental knowledge in several areas: power circuit configurations, mathematical modelling, control systems, electronic devices, and magnetic circuits. In its beginnings, there were two alternatives for the power delivery from a DC source to a load in a controllable manner: linear and switched mode power conversion. Usually, linear power conversion relies on the presence of a series linear element (resistor or transistor in linear mode) such that the total load current is passed through the series linear element. The main disadvantage of this conversion is the inefficiency, because even in its ideal form its efficiency ranges from 30 % to 60 %. On the contrary in the switched mode power conversion, where the controlling device is an ideal switch, the power flow to the load can be controlled in a very efficient way. Ideally its efficiency is almost 100 % even for a wide range of power being controlled [1].

Nowadays, the use of the switched mode power converters is widely generalized. It is the preferred way to provide power processing for different applications going from computing and communications to medical electronics, appliance control, transportation, renewable sources and high-power transmission. The associated power levels extend from milliwatts to megawatts in function of the application. Therefore, the design, analysis, modelling, and control of the switching power converters constantly present new and significant challenges to be achieved [2].

This chapter is mainly a bibliographic journey through two aspects of DC-to-DC switched mode power conversion: circuit structures generation and its mathematical modelling. The first section is an introduction to some elementary aspects of DC-to-DC switching converters, the second studies the new structures generation and classification, the third explains the operating modes and the final section is an overview in converters modelling and simulation.

Modelling and control of an asymmetric interleaved DC-to-DC switching converter

# 1.1 ELEMENTARY ASPECTS OF DC-TO-DC SWITCHING CONVERTERS

The power conversion and control function in switching converter circuits requires the use of semiconductor switches such as thyristors, MOSFETs and diodes, as its basic components. The need to generate a DC output voltage introduces passive storage elements such as inductors and capacitors whose role is to smooth out the inherent pulsating behaviour originated from the switching action. Sometimes, transformers are also used for isolation. Due to the many possibilities of combining these elements, a great variety of converter structures is possible, but taking into account that they have to form effectively a low pass filter in order to achieve the basic DC-to-DC conversion function [1].

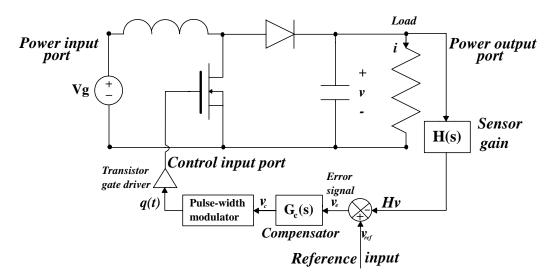

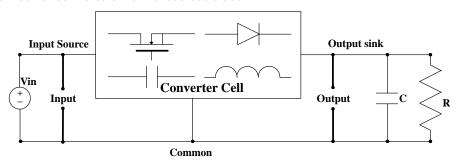

In general one converter has power input and control input ports, and a power output port as can be seen in Figure 1.1. The raw input power is processed as specified by the control input, yielding the conditioned output power. Specifically in a DC-to-DC converter, the DC input voltage is converted into a DC output voltage having a larger or smaller magnitude, possibly with opposite polarity or with isolation of the input and output ground references. Furthermore, an accurate control is undeniably required, since a well-regulated output voltage in the presence of variations of the input voltage and load current is desired. Moreover, high efficiency is one of the main goals in the designer's work [3].

In the next subsection, the boost converter will be studied in detail, in order to present the nomenclature.

### 1.1.1 THE PWM CONTROLLED BOOST CONVERTER

Figure 1.1: The boost converter with PWM control

The Figure 1.1 shows a basic step-up (boost) converter structure capable of producing a DC output voltage greater in magnitude than the DC input voltage. This structure utilizes only switches, inductors and capacitors. The switches are realized using power semiconductors devices, such as transistors and diodes. The transistors are controlled to turn on and off as required to perform the function of the ideal switch that can be seen in Figure 1.2. For simplicity, in the analysis to be performed the switches are supposed to be non dissipative and the switching frequency  $f_s$  (inverse of the switching period  $T_s$ ) to be a constant. That frequency generally lies in the range of  $f_s$  to  $f_s$  the fraction of time the switching speed of the semiconductor devices. The duty ratio  $f_s$  is the fraction of time the switch spends in position 1, and is a number between zero and one. The complement of the duty ratio  $f_s$  is defined as  $f_s$  in general, the duty ratio is a variable  $f_s$  that can change its value every  $f_s$  cycle to fit itself to the requirements of the control signal.

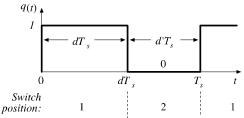

Figure 1.2: The function of the ideal switch

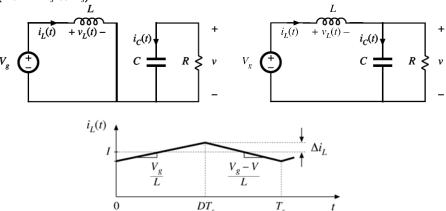

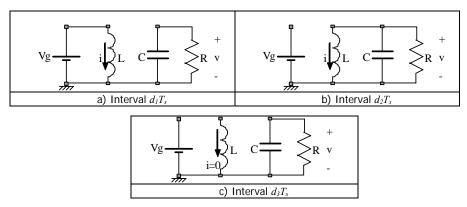

The boost converter in continuous conduction mode has two topologies of operation depending on the position of the switch, which can be observed in Figure 1.3. The inductor current waveform shows that the inductor L stores energy when the switch is in position "1" (from zero to  $DT_s$  seconds). This energy is transferred to the charge when the switch is in position "2" (from  $DT_s$  to  $T_s$ ).

Figure 1.3: Topologies and inductor current waveform of the boost converter

Thus, the inductor voltage and current relationship are defined:

$$v_L(t) = L \frac{di_L(t)}{dt} \tag{1}$$

Modelling and control of an asymmetric interleaved DC-to-DC switching converter

When the switch is in position 1 the inductor voltage is  $V_g$ , and in position 2 the inductor voltage is  $(V_g - V)$ , where V is almost constant if the output ripple is small.

According to the principle of inductor volt-second balance [1], in periodic steady state, the net change in inductor current is zero, hence, the total area (or volt-seconds) under the inductor voltage waveform is zero whenever the converter operates in steady state. An equivalent form of this principle is that the average inductor voltage is zero in steady state.

Applying this principle over one switching period to the boost converter, it can be obtained

$$\int_{0}^{T_{s}} v_{L}(t)dt = (V_{g})DT_{s} + (V_{g} - V)D'T_{s}$$

(2)

equating to zero, collecting terms and solving for V

$$V_{\sigma}(D+D')-VD'=0$$

$$V = \frac{V_g}{D'} \tag{3}$$

thus, the voltage conversion ratio is

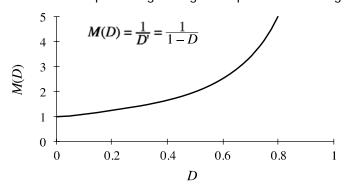

$$M(D) = \frac{V}{V_{\sigma}} = \frac{1}{D'} = \frac{1}{1 - D}$$

(4)

The equation (4) shows that the output voltage magnitude can be controlled through the variation of the duty ratio. In the Figure 1.4 it can be seen the control characteristic of the boost converter calculated using equation (4) that allows the duty ratio D to be adjusted in order to regulate the converter output voltage using a compensator as in Figure 1.1.

Figure 1.4: Boost converter control characteristic

The control of the duty ratio d, at constant switching frequency, is commonly called Pulse Width Modulation (PWM) control. As can be seen in the Figure 1.1, in order to obtain the control signal  $v_c(t)$ , the output voltage value is sensed  $(H_v)$  and compared with a reference input  $(v_{ref})$ . Then, the error signal  $v_e(t)$  is applied to the input of a compensator and its output signal  $v_c(t)$  is the modulation input of the PWM. Inside the PWM there is a comparator. The input to the "-" terminal of the comparator is a sawtooth waveform of period  $T_s$  that starts

ISBN:978-84-692-6903-9 / DL:T-1849-2009

from  $\theta$  at the beginning of every cycle, and ramps up linearly to F by the end of the cycle. At some instant  $t_k$  in the kth cycle, this ramp crosses the level of the modulating signal  $v_c(t)$  at the "+" terminal of the comparator. Hence, the output of the comparator is set to I every  $T_s$  seconds when the ramp restarts, and reset to  $\theta$  later in the cycle, at time  $t_k$ , when the ramp crosses  $v_c(t)$ . The duty ratio of the PWM output signal q(t) thus ends up being  $d_k = v_c(t)/F$  in the corresponding switching cycle. By varying the modulation signal  $v_c(t)$  from cycle to cycle, the duty ratio can be varied. The PWM's output signal shown in Figure 1.2 is connected to the gate transistor driver that establishes the portion of time in which the circuit is ON, controlling in this way the output voltage magnitude, because it depends directly on the time that the converter is in ON state. Note that the samples  $v_c(t_k)$  of  $v_c(t)$  are what determine the duty ratio signal q(t). In order to avoid the aliasing effect associated with sampling, the modulation signal is restricted to vary considerably more slowly than half the switching frequency. The modulating signal is usually generated by a feedback scheme as is shown by the input to the PWM in Figure 1.1.

Chapter 1. State of the art: generation and modelling of DC-to-DC switching converters

The low pass capacitive filter would have to smooth the inherent pulsating behaviour of the output voltage originated from the switching action, and therefore generate an ideal DC output voltage. However the output voltage is not ideal, in addition to its DC component, it consists of a small ripple voltage component at the switching frequency  $f_s$ . From the frequency point of view, the PWM voltage waveform at the input of the low pass filter is divided into its DC component, harmonics at the switching frequency  $f_s$ , and its integer multiples harmonics by using Fourier series. The DC component passes unattenuated through the filter to generate the desired DC output. Given that the filter corner frequency is significantly lower than the switching frequency (typically at least a decade below  $f_s$ ), the first and higher order harmonics are substantially attenuated by passing through the filter, resulting in an acceptably low switching ripple voltage at the output [1].

### 1.2 GENERATION AND CLASSIFICATION OF PWM DC-TO-DC CONVERTERS

One of the first studies on this subject was presented in [4] where the investigation of a variety of switching converters structures culminates in the establishment of the duality relationship, a general correlation law between the converter structures. The duality between converter structures can be observed in the dual nature of their components: inductors and capacitors, open and closed switches, input voltage and current sources, load resistance and load conductance. Starting from this law, new converter structures were generated by the application of the duality transformation to the existing converter configurations. In this way the duality between the buck and boost converters, and between the buck-boost and CUK converters is demonstrated as well. In addition to this duality other two topological properties were studied in that paper: inversion, in which the source and load interchange would result in an equally viable switching converter configuration, and symmetry, in which the source and load interchange results in the same configuration.

The study of more general approaches to the problem of the structure generation will be discussed in the next section

ISBN: 978-84-692-6903-9 / DL:T-1849-2009

8 Modelling and control of an asymmetric interleaved DC-to-DC switching converter

### 1.2.1 THE CONVERTER CELL

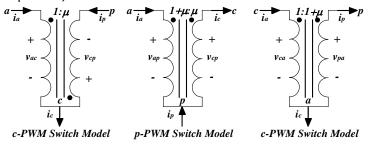

In the literature there are a lot of DC-to-DC converter structures performing similar power processing functions, seemingly without a unifying connection between them. In [5] a fundamental block known as converter cell, whose diagram is in Figure 1.5, was used to generate basic converter structures. Therefore a relationship between basic converters was established. This converter cell can be used to analyze them too.

As Figure 1.5 describes, the converter cell is defined as the remaining network when the input source and output voltage sink are removed. Then, the result is a topological combination of reactive elements (Ls and Cs), and switches (actives and passives), where the duty cycle has the control of the output voltage.

The Figure 1.5 also shows that the converter cell is a three terminal device. Their terminals can be connected to the input source, output sink or common terminal in six different possible ways that correspond to the number of permutations of three. Therefore a family of six converters may be derived from each converter cell, except in the cases of symmetric cells, where the numbers of family members reduces down to three.

The converters that have this structure are DC-to-DC voltage converters without isolation. The Use of other strategies as isolation or interleaving allows the derivation of an infinite number of converters from these basic set.

Figure 1.5: Converter Cell with ports indicated

A classification scheme of basic converters can be made in terms of converter-cell generated families. These converter cells were obtained without a formal synthesis procedure from known converters, and classified in four categories according to their order. The order indicates the number of storage elements and the number of switches used thus:

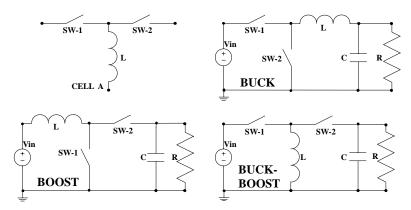

- 1) First-order, 2 switch: one type of converter cell as can be seen in Figure 1.6;

- 2) First-order, 4 switch: one possibility of converter cell.

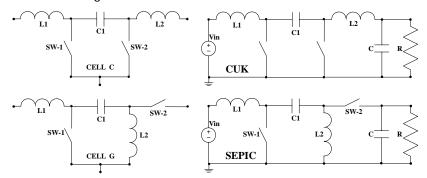

- 3) Third-order, 2 switch: five types of converters cells, two of them in Figure 1.7;

- 4) Third-order, 4 switch: seven types of converter cells.

For example, the "Cell A" of the first category is the basic converter cell of the buck, boost and buck-boost converters that are the most well-known structures and can be seen in Figure 1.6.

**Figure 1.6:** First order converters

Two examples of the third category are the "Cell C" and the "Cell G", which are the basic converter cells of other known structures: the Cuk and SEPIC converters respectively. These structures can be seen in Figure 1.7.

Figure 1.7: Third order converters

### 1.2.1.1 Another schemes of generation and classification

Based on a formal definition of PWM converters, the study of the general topological constraints and properties of PWM converter networks made in [6] derivates completely formalized synthesis procedures that, in contrast to earlier approaches, guarantees the generation of complete sets of converters with prescribed attributes.

In the Chapter Two of [7] there is another detailed study of the generation and classification of DC-to-DC converters based on the converter cell. However in this case the generation of structures are also based on a set of synthesis rules that enables the refining of the process. The generated converters are classified first according to the number of nodes, and second, after the static analysis, according to the conversion ratio.

In [8] there is a classification scheme of a large class of PWM DC-to-DC, non isolated, and voltage to voltage converters of second and fourth order, that use only one transistor and one diode. The criteria used in the classification is based on the analysis of the linearized zero dynamics of the converter, which allows the observation of structure corrections in order to obtain a better dynamic behaviour.

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

10 Modelling and control of an asymmetric interleaved DC-to-DC switching converter

In the Chapter Six of [3] was developed another scheme of DC-to-DC converters classification that includes converters with isolation and explores the properties that allowed the generation of the new converter structures.

### 1.2.1.2 CONVERTER ANALYSIS WITH CONVERTER CELLS

The concept of converters cells is more versatile when it is used for the analysis of the converters that it generates. Each converter cell can be treated as a three-terminal device, deriving the average models for each converter cell and obviating the need to derive again these models for each of the converters of a particular family. The cell model can then be substituted point-by-point for the cell in any of the converters derived by the cell to give the converter model which can then be solved.

This approach to converter analysis is analogous to ordinary transistor circuit analysis. A converter cell and a transistor are both nonlinear three-terminal devices. Operation of these devices for small excursions about a DC operating point allows deriving small-signal models. Once these models have been derived, the nonlinear device (the converter cell or the transistor) may be replaced point by-point by its linearized model. This allows the use of ordinary linear circuit analysis techniques in order to analyze the circuit in which the nonlinear device (converter or a transistor circuit) was embedded.

# 1.2.2 THE INTERLEAVING AS A STRATEGY OF CONVERTER GENERATION

A different approximation to the generation of new converter structures that improves the characteristics of the resulting circuit have been studied in [9]. This approximation begins from both basic converter structures and control techniques already known, and continues by performing a new combination of all of them. The first step applied by this technique consists in a structural change through a parallel interconnection of a determined number of identical converter cells (N canonical cells). The second step consists in the application, to each canonical cell, of the strategically phase shifted control signals in one switching period. The name of this technique is interleaving. It was initially presented in [10] as a method of incrementing the switching frequency of all the converter without increasing the switching frequency of the N canonical cells that conform it, at the time that divides the input power between the N canonical cells. The resulting converter improves some of the characteristics of the basics structures that conforms it, especially when it works at high power.

Some of the advantages of the use of interleaving are the following:

- The ripple reduction in the output voltage and the input current due to the increment in the switching frequency. This increment also diminishes the electromagnetic interferences (EMI) associated, making easier the observance of the standards about line current harmonics and conducted EMI.

- The decrease of switching losses as a result of the use of switching frequencies in the optimal range.

- The decrease in the converter size because of the filters reduction.

- The global decrease in the thermal dissipation due to the decrease of the losses.

- The converter fast dynamic response due to the smaller energy storage necessity.

- The improvement in the thermic management by the spreading of the hot spots.

### 1.2.2.1 COMPLEMENTARY INTERLEAVING

The technique of interleaving consists in the application of phase shifted control signals to each canonical cell in one switching period. If the phase shift of the signals is equal to the 50 % of the switching period, this is, the circuit switches are activated in a complementary way, the interleaving is called complementary. One of the characteristics of the 50 % phase shifted is that the circuit only works in configurations where the switches have different states and its analysis is easier.

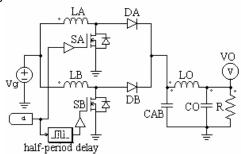

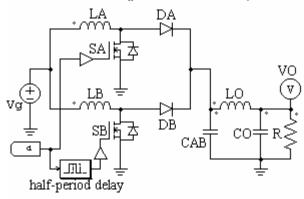

In the Chapter Two of [9] the complementary interleaving is applied to the interconnection of two boost converters with output filter in continuous conduction mode. The name of the new structure is Interleaved Dual Boost "IDB" shown in Figure 1.8. The analysis of this converter not only confirms the reduction in the global variables ripple but also finds the extremely sensibility to the losses and the possibility of using the circuit as a doubler with a 50% duty cycle.

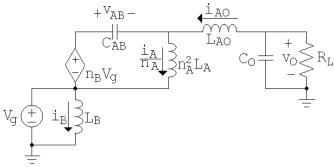

Figure 1.8: Interleaved Dual Boost (IDB) with Output Filter

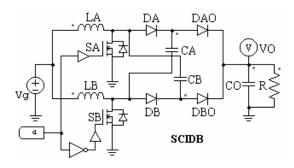

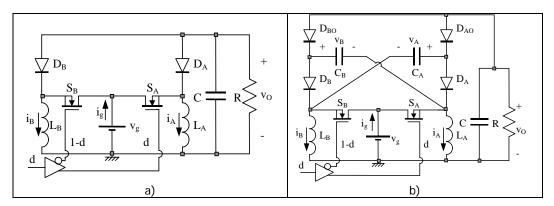

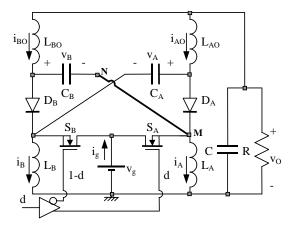

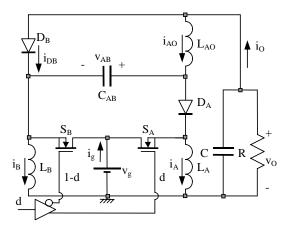

Searching for alternatives to the IDB circuit, the Chapter Six of [9] began making modifications into the original structure using another technique: the design of classical multipliers. The addition to the unidirectional structure of the IDB of two diodes, keeping the two original capacitors of the canonical boost cells, generates a new boost converter structure. This interconnection between capacitors and diodes remembers the classical voltage multiplying nets constituted precisely by these two elements and can be interpreted as a net of switched capacitors, originating therefore the denomination chosen for the new converter circuit: Switched Capacitor Interleaved Dual Boost "SCIDB" depicted in Figure 1.9.

The open loop analysis of the SCIDB shows the decrease of the sensibility problems in comparison with the previous structure (IDB). Consequently, the converter can operate in a very extensive range of duty cycles. The structure also exhibits a symmetrical operation for a 50 % duty cycle and basic conversion rate of a quadruplier.

Following the methodology presented in this subsection, it has been generated the family of converters that will be explained in the Chapter Two of this thesis.

ROVIRA I VIRGILI UNIVERSITY MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER Eliana Isabel Arango Zuluaga

ISBN: 978-84-692-6903-9 / DL:T-1849-2009

12 Modelling and control of an asymmetric interleaved DC-to-DC switching converter

Figure 1.9: Switched Capacitor Interleaved Dual Boost (SCIDB)

### 1.3 SWITCHING CONVERTERS OPERATION MODES

Two main modes of switching converter operation may be distinguished: the continuous conduction mode CCM, where the inductor current or capacitor voltage never fails to zero, and the discontinuous conduction mode DCM, where the inductor current or capacitor voltage becomes zero for one interval of the switching period.

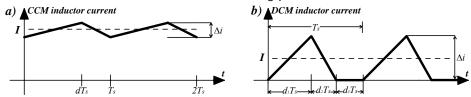

Figure 1.10: Inductor current waveform in a) CCM and b) DCM

### 1.3.1 Continuous conduction mode CCM

The operation in CCM is guaranteed under the small-ripple assumption that all the AC ripples of steady-state inductor currents and capacitor voltages are relatively small comparing to their DC quantities [11]. As can be seen in the Figure 1.10a, in CCM the waveform has two intervals of operation, corresponding to the duty cycle:  $dT_s$  and the complementary  $dT_s$ . Where d = (1-d).

### 1.3.2 Discontinuous conduction mode DCM

The DCM occurs in converters containing current or voltage unidirectional switches, when the inductor current or capacitor voltage ripple is large enough to cause the switch current or voltage to reverse its polarity. A typical example can be a DC-to-DC converter operating at light load (small load current). Although sometimes, for low power applications, it is also quite common to operate the converter in DCM even at full load in order to avoid the

13

reverse recovery problem of the diode [12]. In boost derived converters it can be found another use of this conduction mode with the aim to avoid the right half plane zero in the control-to-output transfer function [13].

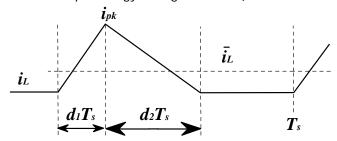

The DCM has been classified in two modes. If only the small-ripple assumption in inductor currents is not satisfied, the converter will operate in discontinuous inductor current mode DICM, and if only the small-ripple assumption in capacitor voltages is not satisfied, the converter will operate in discontinuous capacitor voltage mode DCVM, reported for the first time in [4].

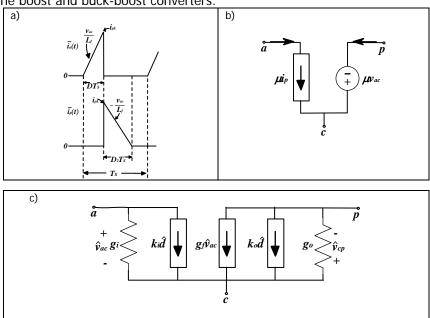

As it can be seen in Figure 1.10b, in DCM mode, the waveform has three intervals of operation. The energy stored in the inductor or capacitor during the first interval  $d_1T_s$  is completely released to the load during the second interval  $d_2T_s$ . Then, the inductor current or capacitor voltage becomes zero for the third interval  $d_3T_s$ .

Conditions for operation in the discontinuous conduction mode can be found by determining when the inductor current or capacitor voltage ripples and their DC components cause the switch on-state current or off-state voltage to reverse polarity. Some of these conditions are the increase of load R (therefore the averaged of DC current I or voltage V diminishes) or the decrease of the inductance L, capacitor C or switching frequency  $f_s$ . In any case, however, the operation in DCM mode results in an additional topology compared with the operation in CCM. Commonly the properties of converters change radically when DCM is entered: the conversion ratio M becomes load-dependent, output impedance is increased, dynamics are altered and control of output voltage may be lost when load is removed. Despite of these changes some circuits are purposely designed to operate in DCM over the entire line cycle in order to simplify the control [12].

### 1.3.3 DISCONTINUOUS QUASI-RESONANT MODE DORM

A systematic study of possible operating modes of PWM converters realized in [14] revealed that, in addition to the three known modes CCM, DICM and DCVM, when the small-ripple assumption in both inductor currents and capacitor voltages are not satisfied, the converter will operate in another mode: the discontinuous quasi-resonant mode DQRM. The name of this mode is because the inductor and the capacitor form a resonant circuit in one of the operating states. DQRM can be considered as a combination of DICM and DCVM.

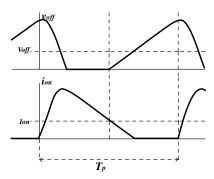

When a PWM converter operates in DQRM, the transistor turn-ON and the diode turn-OFF are at zero current, while the transistor turn-OFF and the diode turn-ON are at zero voltage, so that switching losses are reduced, as in various quasi-resonant converters. Unlike quasi-resonant converters, which require a variable frequency control, the PWM converter in DQRM can be controlled just as PWM converters in CCM: by varying the duty ratio of the active switch at constant switching frequency. In addition, the active switch does not need to be two-quadrant.

The operation in DCVM and DQRM is guaranteed under some specific conditions: the first is the order of the circuit topology that must be higher than two, and the second is that the transistor and diode must form a cut-set with a non-empty set of inductors for DICM operation or a loop with a set of capacitors (except output filter capacitor) and possibly voltage source for DCVM operation. Therefore, in a switching period there exists one time stage during which, both the transistor switch and the diode switch, can be in the same ON

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

14 Modelling and control of an asymmetric interleaved DC-to-DC switching converter

state for DCVM and DQRM operation, which means parallel or short connection of voltage source and/or capacitor for the basic two-order PWM switching converters, such as buck, boost, buck-boost circuits. So these basic converters can only operate in CCM and DICM [15].

### 1.3.4 OTHER DISCONTINUOUS MODES

The existence of new discontinuous modes in PWM DC-to-DC converters has been pointed out in [13]. Such modes have been named Multi-Discontinuous Modes (MDMs) as they are characterized by the presence of multiple current and voltage discontinuities within the switching period. This means that the discontinuity of the state current meets the discontinuity of the state voltage within the same state of the switch, which is the main difference with the DQRM mode described previously.

Multi-Discontinuous Modes (MDMs) were detected in fourth order PWM DC-to-DC converters with light load conditions. The authors use a Cuk-PWM converter in order to exemplify and characterize this mode of conduction. The experimental measuring of the control-to-output frequency responses have shown an order reduction due to the discontinuous behaviour of the converter, this is, the frequency response looks like a first order circuit although it is of fourth order. Another important observation reported by the authors is that the resonant stage lies on the output side instead of the input side, as it usually happens in QR converters; consequently, large output inductor current ripple can be involved, so that the demand for low ESR output capacitors increases. The experimental tests have also shown that a high feedback gain can lead sometimes to (instant) chaos in presence of MDMs.

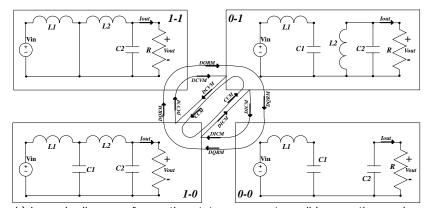

In Chapter Two it will be shown that in addition to these modes of conduction, when the interleaving technique is used for the generation of the circuit, another infrequent discontinuous mode could appear.

### 1.3.5 EXAMPLE

As an example, Figure 1.11a shows a buck converter with input filter and in Figure 1.11b the periodic sequence of states in all four possible modes of conduction can be observed. More exactly, the modes of conduction can be seen as follows. The loop of the CCM mode is described by the periodic sequence of states  $(I, 0) \rightarrow (0, I)$ , because in this mode the diode switching is synchronous with the transistor switching -when the transistor is ON, the diode is OFF and vice versa-. The operating states are denoted according to the position of the transistor and the diode switch (ON=I, OFF=0). Thus, two linear, time-invariant networks (operating states) are repeatedly switched in CCM.

b) Loops in diagram of operating states represent possible operating modes

**Figure 1.11:** Periodic sequence of states in all the possible modes of conduction

As was previously seen, the discontinuous conduction mode takes place when low rippled assumption is removed, either in the inductor or in the capacitor. The loop of three states,  $(1, 0) \rightarrow (0, 1) \rightarrow (0, 0)$ , of the discontinuous inductor current mode DICM, occurs when the ac ripple of the output inductor current is sufficiently large, because the diode will cease to conduct before the end of the transistor OFF-time. If the small-ripple assumption is removed from the capacitor, the discontinuous capacitor voltage mode DCVM appears, this is, the ac ripple in the capacitor voltage can be sufficiently large so that the diode starts to conduct before the end of the transistor ON-time. Their corresponding states are  $(1, 0) \rightarrow (1, 1) \rightarrow (0, 1)$ . It was shown that DCVM and DICM are dual operating modes.

The remaining possibility is to remove the small-ripple assumption from both the inductor and the capacitor. This option, which naturally follows from the preceding discussion, yields a previously neglected operating mode of PWM converters. The mode will be called the discontinuous quasi-resonant mode DQRM because the inductor and the capacitor form a resonant circuit in one of the operating states. The sequence of operating states in DQRM are then  $(I, 0) \rightarrow (I, 1) \rightarrow (0, 1) \rightarrow (0, 0)$ , where it is apparent that DQRM can be considered as a combination of DICM and DCVM. The waveforms shown in Figure 1.12, corresponding to the circuit in Figure 1.11a, can be used as a reference for qualitative description of the operation in DQRM.

Assume that initially the converter is in the (0-0) state, then both the transistor and the diode are OFF. At the beginning of a switching cycle, the transistor is turned ON and the resonant (1-0) state is entered. Note that the transistor current is equal to zero before and immediately after the turn-ON transition or, saying this in another way, the transistor is turned ON at zero current. In the (1-0) state, the capacitor voltage and inductor current evolve in a quasi-sinusoidal manner until the capacitor voltage reaches zero and the diode starts to conduct at zero voltage. The converter remains in the (1-1) state until the transistor is turned OFF at zero voltage, and the (0-1) state is entered. In the (0-1) state, the diode current decays linearly, while the transistor voltage ramps up linearly. The remaining (0-0) state is entered when the diode current drops to zero. The converter stays in the (0-0) state until the transistor is turned-ON again and the switching cycle is completed.

ROVIRA I VIRGILI UNIVERSITY MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER Eliana Isabel Arango Zuluaga

ISBN: 978-84-692-6903-9 / DL:T-1849-2009 16 Modelling and control of an asyr

Modelling and control of an asymmetric interleaved DC-to-DC switching converter

Figure 1.12: Waveforms of converter operating in DQRM mode

Then it can be concluded that when a PWM converter operates in DQRM, the transistor turn-ON and the diode turn-OFF are at zero current, while the transistor turn-OFF and the diode turn-ON are at zero voltage, so that switching losses are reduced, as in various quasiresonant converters. Unlike quasi-resonant converters, which require a variable frequency control, the PWM converter in DQRM can be controlled just as PWM converters in CCM: by varying the duty ratio of the active switch at constant switching frequency.

#### 1.4 AN OVERVIEW IN CONVERTERS MODELLING AND SIMULATION

Modelling and simulation are the essential ingredients of the analysis and design process in the power electronics area. They help a design engineer to gain an increased understanding of circuit operation. With this knowledge the designer can, for a given set of specifications, choose a structure, select appropriate circuit component types and values, estimate circuit performance, and complete the design by ensuring—using Monte Carlo simulation, worst case analysis, and other reliability and production yield analyses—that the circuit performance will meet specifications even with the anticipated variations in operating conditions and circuit component values. The combination of modelling, analysis, and simulation would provide better understanding of circuit operation and the basis for good design rather than working directly with a detailed schematic because simulation of a full production schematic still remains an elusive goal; some of its obstacles are for example the need for extensive model building, excessively long simulation times and the effects of layout, packaging, and parasitic losses. The combination of these insights with hardware prototyping and experiments constitutes a powerful and effective approach to design [2].

### 1.4.1 Initial analysis and simulation

The first step in the analysis of a converter circuit is to obtain the voltage and current waveforms that describe basic power-stage circuit operation. For this task it is necessary to ISBN:978-84-692-6903-9 / DL:T-1849-2009

eliminate some circuit elements that are secondary for the basic power processing function

Chapter 1. State of the art: generation and modelling of DC-to-DC switching converters

Moreover, the switch must be replaced by a simple switch model which is controlled by a duty cycle pulse derived from a modulating signal. This signal is compared with the sawtooth waveform at the input of a comparator IC in order to establish the duty ratio of the converter. This is a simple implementation of the so-called PWM.

Therefore, the basic steady-state analysis and circuit waveforms can be obtained using the simplified circuit by simulations in a general circuit simulator or by computations using straightforward circuit analysis and computational tools [2].

### 1.4.2 MATHEMATICAL AND CIRCUIT MODELLING

of the circuit, like the EMI filter, the bridge rectifier, the snubber net, etc.

In order to obtain the dynamic characteristics of the switching converter circuit in addition to the static ones, a modelling method is imperative. Its dynamic behaviour directly determines, or influences, four of the most important characteristics of a power converter: the stability of the feedback loop, the rejection of input voltage ripple and the closely-related transient response to input voltage perturbation, the output impedance and the closely-related transient response to load perturbation, and the compatibility with the input EMI filter [16].

It is important to note that each position of the switch results in one linear switched network. Consequently, for modelling purposes, the problem is well defined since it is completely described by the two (or more) linear networks. However, it is precisely this switching among several linear circuits that made the modelling problem nonlinear (piecewise linear) and difficult [1].

The complexity of modelling a switching converter circuit can also be observed when a small signal perturbation of a unique frequency is applying on a control signal because that signal generates an output which contains a multitude of frequencies: the fundamental signal and its harmonics. Even though the problem is not as severe as it looks because of the basic requirement of low output switching ripple compared with its DC value, this is the filter effect that highly accentuates the component of the output at the control fundamental frequency, and de-emphasizes its harmonics [1].

Due to the complexity characteristics of converter operation, the work of predicting its dynamic behaviour with the adequate precision is not easy but is very necessary. Because if one depends only on building the circuit and fixing it until the operation is satisfactory the engineering cost could escalate and it would be impossible to follow the chronograms. Therefore, the need of improving dynamic behaviour, that is no possible without an in-depth understanding of the operation of switching cells and easy-to-use and accurate models, explains the proliferation of papers related to switching cells analysis and modelling in the last years [16].

Since the objective is to solve for the transfer functions of a DC-to-DC converter, the requirement is for a small signal ac (dynamic) model linearized around a particular large-signal DC (steady-state) operating point, where the operating point is defined by certain values of steady state input voltage  $V_g$  and duty ratio D [1]. The small signal analysis can be used to predict accurately at all DC operating points: the stability margin of the converter

ROVIRA I VIRGILI UNIVERSITY

MODELLING AND CONTROL OF AN ASYMMETRIC INTERLEAVED DC TO DC SWITCHING CONVERTER

Eliana Isabel Arango Zuluaga

ISBN:978-84-692-6903-9 / DL:T-1849-2009

18 Modelling and control of an asymmetric interleaved DC-to-DC switching converter

against closed loop oscillation, and the frequency-domain and time-domain responses to perturbations in input voltage and/or output current [16].

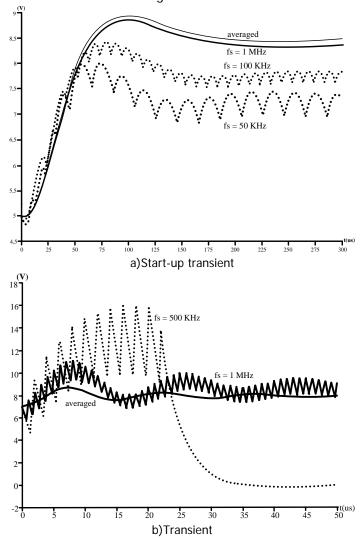

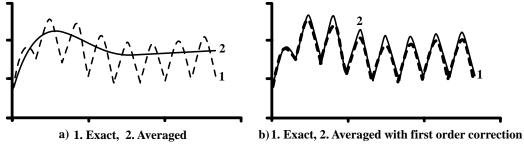

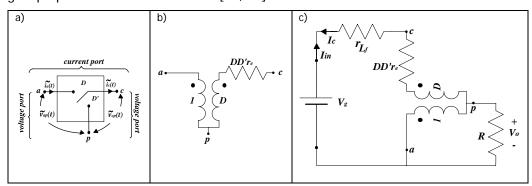

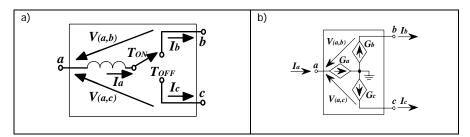

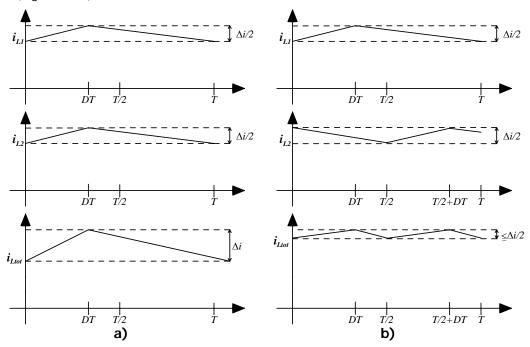

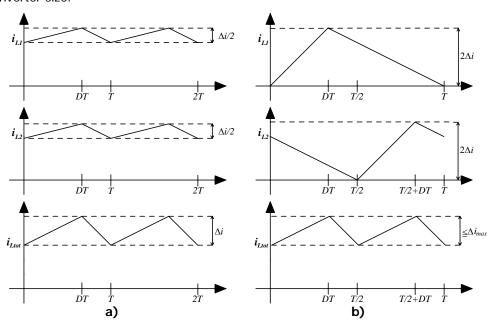

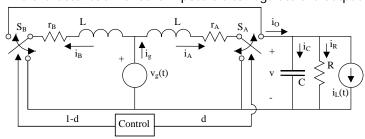

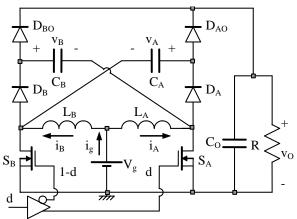

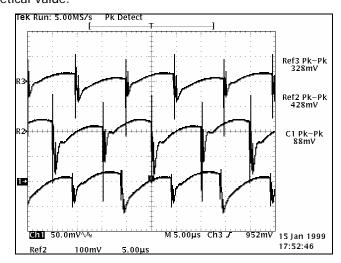

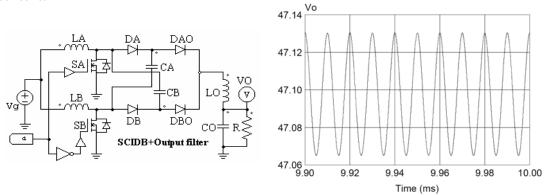

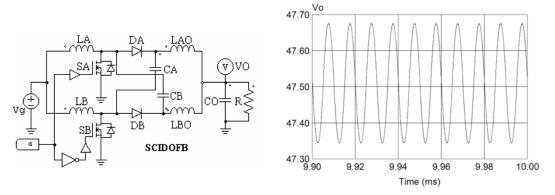

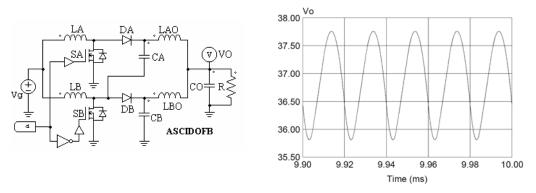

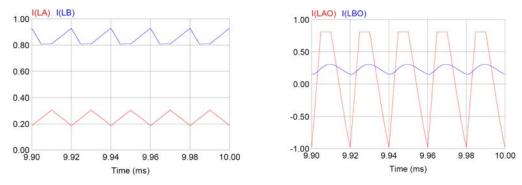

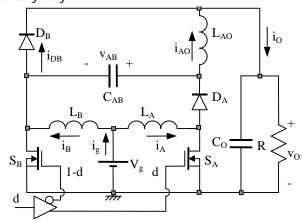

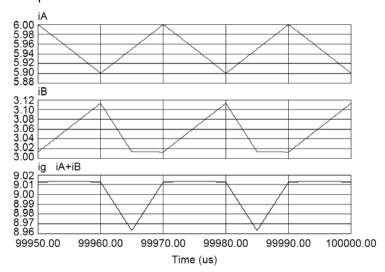

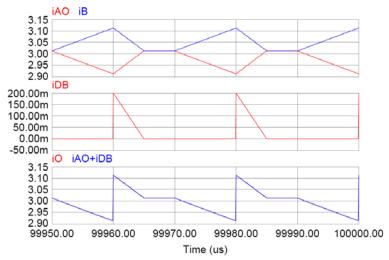

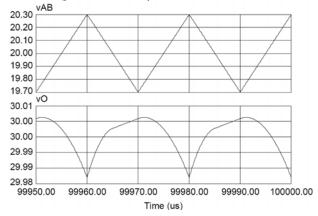

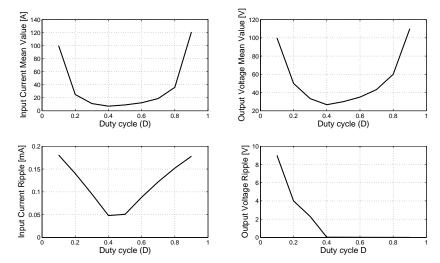

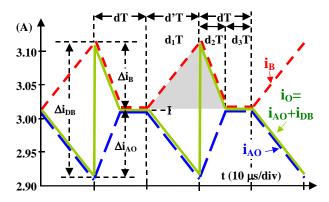

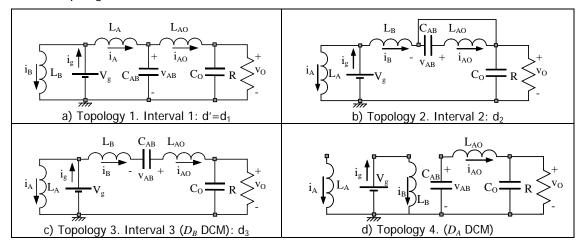

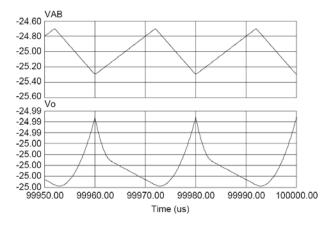

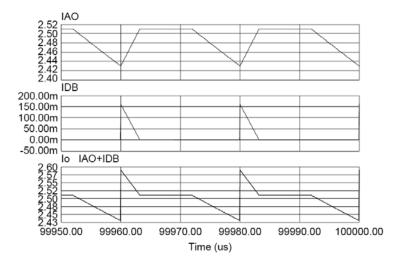

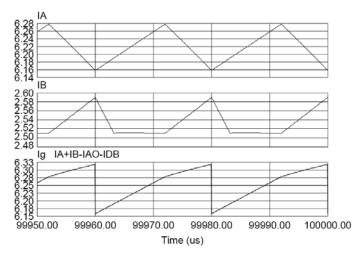

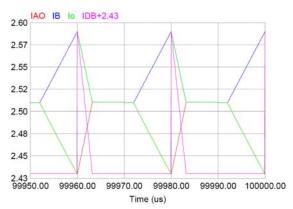

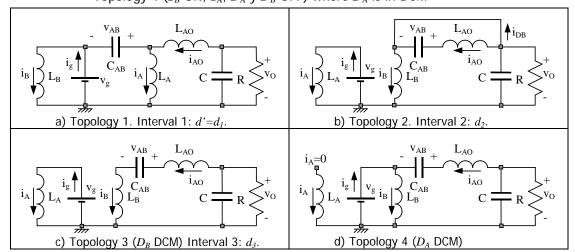

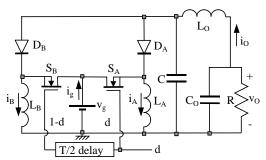

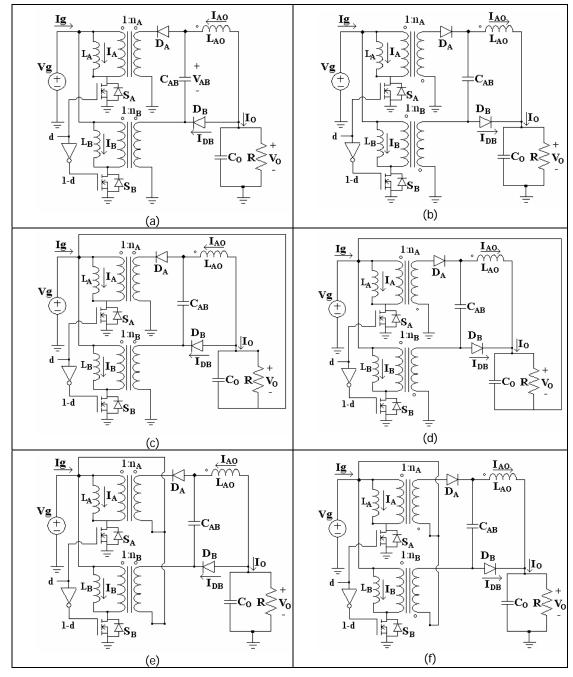

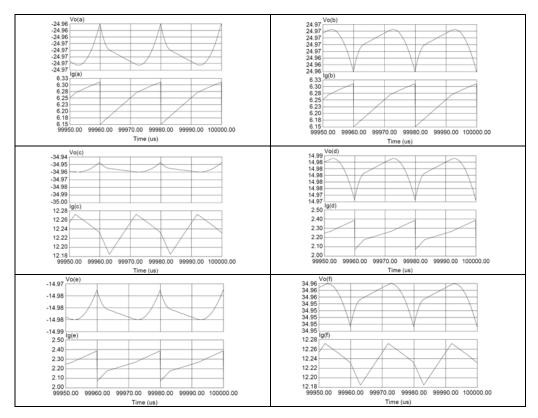

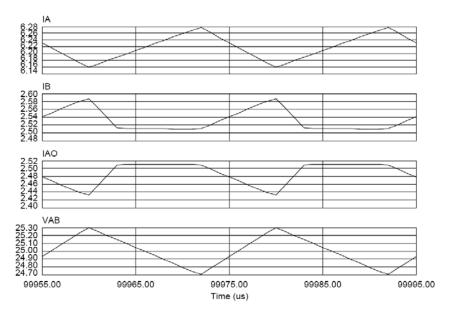

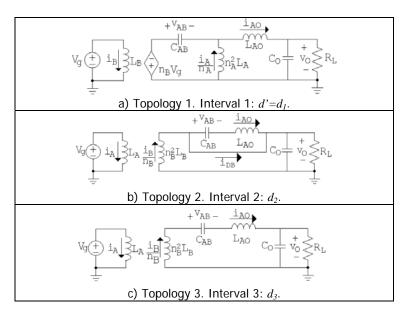

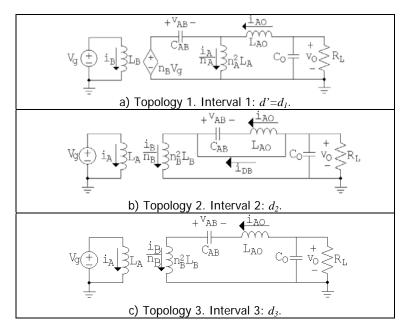

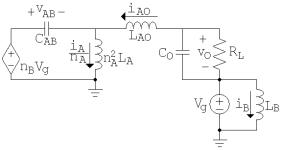

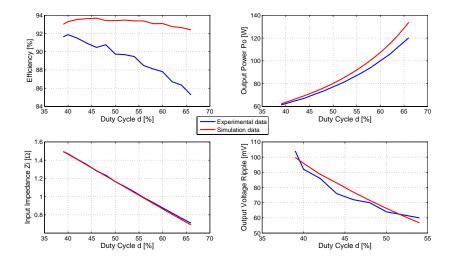

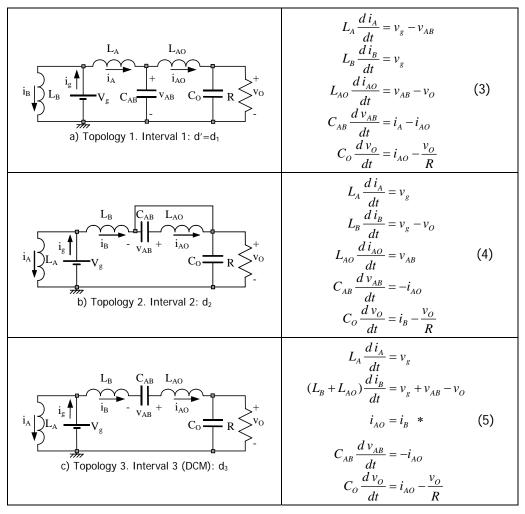

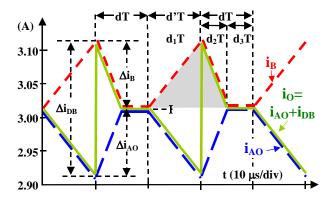

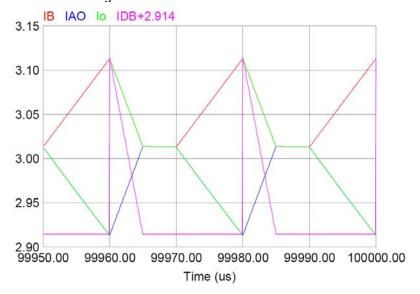

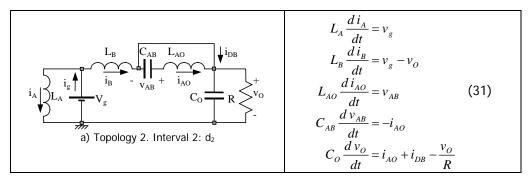

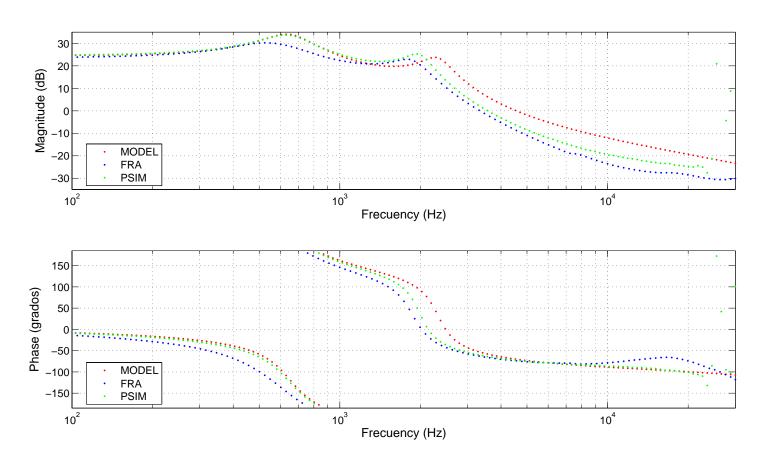

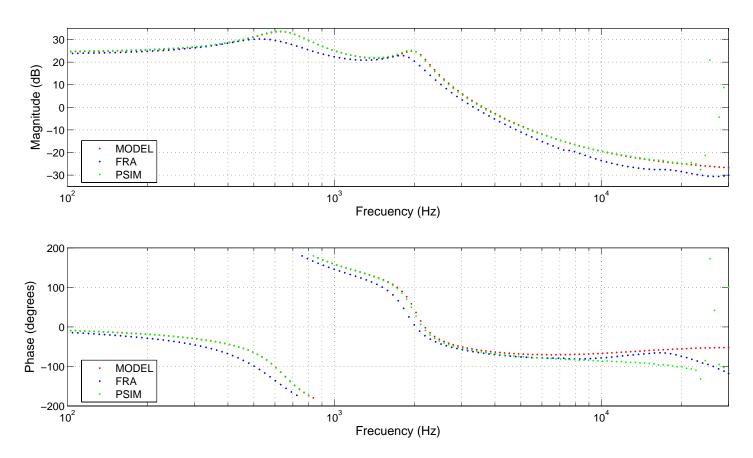

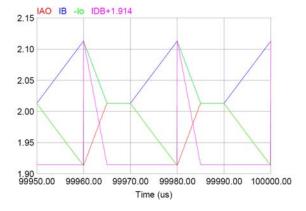

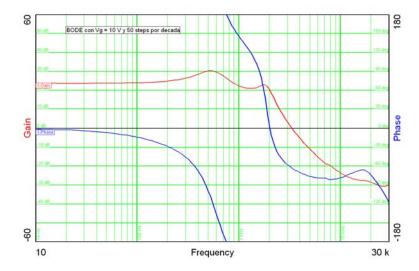

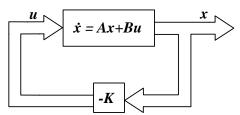

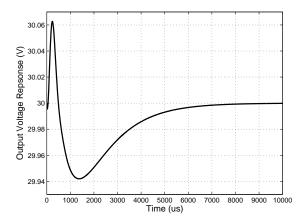

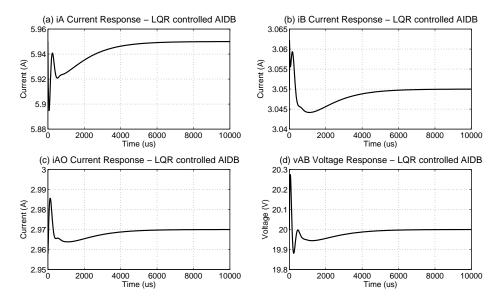

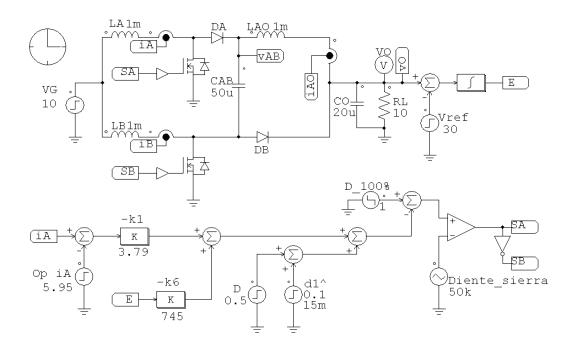

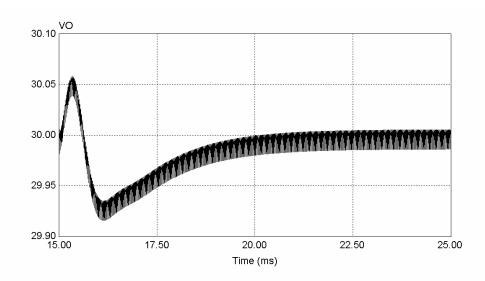

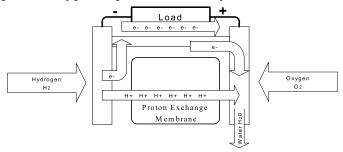

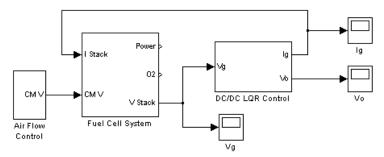

Elementary circuit modelling of a power converter typically produces detailed continuoustime nonlinear time-varying models in state-space form. These models have rather low order, provided one makes approximations that are reasonable from the viewpoint of control-oriented modelling, like neglecting dynamics that occur at higher frequencies than the switching frequency (for instance, dynamics due to snubber elements, whose time scales are typically shorter than the switching period), and focusing instead on components that are essential to the power processing and control functions of the converter [2].