### Escola d Enginyeria

### Departament d'Arquitectura de Computadors i Sistemes Operatius

## Improving Memory Hierarchy Performance on MapReduce Frameworks for Multi-Core Architectures

Submitted by **Tharso de Souza Ferreira** for the degree of Philosophiae Doctor by the Universitat Autònoma de Barcelona, under the supervision of Dr. Juan Carlos Moure and Dr. Antonio Espinosa, done at the Computer Architecture and Operating System Department, PhD. in High performance Computing

### Improving Memory Hierarchy Performance on MapReduce Frameworks for Multi-Core Architectures

| Submitted by Tharso de Souza Ferreira for the degree of Universitat Autònoma de Barcelona, under the supervis and Dr. Antonio Espinosa, at the Computer Architect Department, Ph.D in High-performance Computing. | ion of Dr. Juan Carlos Moure |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                                                                                                                                                                                                   | Barcelona, September 2013    |

| Supervisors:                                                                                                                                                                                                      | ${ m Author:}$               |

| Dr. Juan Carlos Moure                                                                                                                                                                                             | Tharso de Souza Ferreira     |

| Dr. Antonio Espinosa                                                                                                                                                                                              |                              |

### Abstract

The need of analyzing large data sets from many different application fields has fostered the use of simplified programming models like MapReduce. Its current popularity is justified by being a useful abstraction to express data parallel processing and also by effectively hiding synchronization, fault tolerance and load balancing management details from the application developer.

MapReduce frameworks have also been ported to multi-core and shared memory computer systems. These frameworks propose to dedicate a different computing CPU core for each map or reduce task to execute them concurrently. Also, Map and Reduce phases share a common data structure where main computations are applied.

In this work we describe some limitations of current multi-core MapReduce frameworks. First, we describe the relevance of the data structure used to keep all input and intermediate data in memory. Current multi-core MapReduce frameworks are designed to keep all intermediate data in memory. When executing applications with large data input, the available memory becomes too small to store all framework intermediate data and there is a severe performance loss.

We propose a memory management subsystem to allow intermediate data structures the processing of an unlimited amount of data by the use of a disk spilling mechanism. Also, we have implemented a way to manage concurrent access to disk of all threads participating in the computation.

Finally, we have studied the effective use of the memory hierarchy by the data structures of the MapReduce frameworks and proposed a new implementation of partial MapReduce tasks to the input data set. The objective is to make a better use of the cache and to eliminate references to data blocks that are no longer in use.

Our proposal was able to significantly reduce the main memory usage and improves the overall performance with the increasing of cache memory usage.

Keywords. MapReduce; Multi-core; Threads; Main Memory; Virtual Memory

## Resumen

La necesidad de analizar grandes conjuntos de datos de diferentes tipos de aplicaciones ha popularizado el uso de modelos de programación simplicados como MapReduce. La popularidad actual se justifica por ser una abstracción útil para expresar procesamiento paralelo de datos y también ocultar eficazmente la sincronización de datos, tolerancia a fallos y la gestión de balanceo de carga para el desarrollador de la aplicación.

Frameworks MapReduce también han sido adaptados a los sistema multi-core y de memoria compartida. Estos frameworks proponen que cada core de una CPU ejecute una tarea Map o Reduce de manera concurrente. Las fases Map y Reduce también comparten una estructura de datos común donde se aplica el procesamiento principal.

En este trabajo se describen algunas limitaciones de los actuales frameworks para arquitecturas multi-core. En primer lugar, se describe la estructura de datos que se utiliza para mantener todo el archivo de entrada y datos intermedios en la memoria. Los frameworks actuales para arquitecturas multi-core han estado disenado para mantener todos los datos intermedios en la memoria. Cuando se ejecutan aplicaciones con un gran conjunto de datos de entrada, la memoria disponible se convierte en demasiada pequena para almacenar todos los datos intermedios del framework, presentando así una grave pérdida de rendimiento.

Proponemos un subsistema de gestión de memoria que permite a las estructuras de datos procesar un número ilimitado de datos a través del uso de un mecanismo de spilling en el disco. También implementamos una forma de gestionar el acceso simultáneo al disco por todos los threads que realizan el procesamiento.

Por último, se estudia la utilización eficaz de la jerarquía de memoria de los frameworks MapReduce y se propone una nueva implementación de una tarea MapReduce parcial para conjuntos de datos de entrada. El objetivo es hacer un buen uso de la caché, eliminando las referencias a los bloques de datos que ya no están en uso.

Nuestra propuesta fue capaz de reducir significativamente el uso de la memoria principal y mejorar el rendimiento global con el aumento del uso de la memoria caché.

Palabras clave. MapReduce; Multi-core; Threads; Memoria Principal; Memoria Virtual.

### Resum

La necessitat d'analitzar grans conjunts de dades per part de diferents tipus d'aplicacions ha popularitzat la utilització d'entorns de programació simplificats com ara MapReduce. La seva popularitat actual es justifica pel fet de proporcionar una abstracció útil per expressar processament paral·lel de dades i per oferir una forma efectiva de fer transparent per al programador d'aplicacions detalls sobre la implementació de les tècniques de sincronització, tolerància a errors i balanceig de càrrega.

Els entorns d'execució MapReduce també han estat adaptats per als sistemes multi-core i de memòria compartida. Aquests entorns proponen dedicar un core de CPU diferent a cada tasca map i reduce i així executar-les de forma concurrent. Per una altra part, les etapes Map i Reduce comparteixen una estructura de dades comuna on s'aboquen la gran part de computacions realitzades.

En aquest treball descrivim les limitacions més importants dels entorns actuals de execució d'aplicacions MapReduce en entorns multi-core. Primer descrivim la rellevància de les estructures de dades utilitzades per mantenir les dades intermitges en memòria. Els entorns actuals estan dissenyats per mantenir tots els resultats intermitjos en memòria principal. Quan les aplicacions en execució han de tractar grans quantitats de dades d'entrada, la quantitat de memòria disponible no és capaç d'emmagatzemar la quantitat d'informació necessària i es produeix un greu problema de rendiment.

Proposem un nou subsistema de gestió de memòria per permetre que aquestes estructures de dades puguin processar una quantitat il·limitada de dades amb l ús d un mecanisme de spill al disc. També presentem un altre mecanisme per a gestionar els accessos a disc que generen tots els threads que participen al còmput.

Finalment, també hem estudiat l'ús efectiu de la jerarquia de memòria per part de les estructures de dades dels entorns MapReduce multi-core i proposem una nova implementació de l'execució parcial de tasques MapReduce a les dades d'entrada. L'objectiu és fer un millor ús de la memòria cau, així com eliminar les referències als blocs de dades que ja no es fan servir.

La nostra proposta ha estat capaç de reduir significativament la utilització de la

memòria principal, així com millorar el rendiment general de les aplicacions amb un increment en la utilització de la memòria cau.

Paraules claus. MapReduce; Multi-core; Threads; Memòria principal; Memòria virtual.

### Resumo

A necessidade de analizar largos conjuntos de dados desde distintos tipos de aplicações tem promovido o uso de simplicados modelos de programação como MapReduce. A atual popularidade é justificada por ser uma abstração útil para expressar processamento paralelo de dados e também por efetivamente esconder detalhes de sincronização, tolerancia a falhas, e gerenciamento de balanceio de carga do desenvolvedor da aplicação.

Frameworks MapReduce também foram portados para sistema multi-core e de memória compartilhada. Esses frameworks propoe dedicar os diferentes cores de uma CPU para cada tarefa Map ou Reduce a ser executada concorrentemente. As fases Map e Reduce também compartilham uma estrutura de dados comum onde o processamento principal é aplicado.

Em este trabalho nós descrevemos algumas limitações dos atuais frameworks para arquiteturas multi-core. Primeiro, nós descrevemos o relevante da estrutura de dados utilizada para manter todo o arquivo de entrada e dados intermédios em memória. Atuais frameworks para arquiteturas multi-core foram desenhados para manter todos os dados intermédios em memória. Quando se executam aplicações com grande conjunto de dados de entrada, a memória disponível torna-se muito pequena para armazenar todos os dados intermédios do framework apresentando assim uma séria perda de desempenho.

Nós propomos um subsistema de gestao de memória que permita as estruturas de dados processar um ilimitado conjunto de dados através do uso de um mecanismo de spilling no disco. Nós também implementamos uma maneira de gerenciar o acesso concorrente ao disco de todos os threads que estao participando do processamento.

Finalmente, nós estudamos o uso eficaz da hierarquia de memória dos frameworks MapReduce e propomos uma nova implementação de uma tarefa Mapreduce parcial para o conjunto de dados de entrada. O objetivo é fazer um bom uso da cache em elimiar as referencias para os blocos de dados que não estão mais em uso.

Nossa proposta foi capaz de significativamente reduzir a memória principal utilizada e melhorar o desempenho geral com o incrememento do uso da memória cache.

Palavras chave. MapReduce; Multi-core; Threads; Memória Principal; Memória Virtual.

## Acknowledgements

Four years ago i started this adventure across the ocean, away from home, with a whole new world ahead. First and foremost, i would not be here without the support of my parents and my sisters. For all the confidence, patience and faith deposited in me since the first moment. I would not be here without the support of you.

To Alexandre Strube, for introducing me to the world of research, for all the encouragement in the beginning of this journey, essential to be able to reach the end, i will be eternally grateful.

To Emilio and Lola, for receive me so well and make me feel safe so far from home, for all the help and advice, permitting believe and always continue. No thanks here would be enough to express my gratitude.

To Juan Carlos, Toni and Porfi, for all patience, guidance and productive discussions. I have learned so much from you, my whole way of looking at things has changed. Thank you for everything, especially for the patience with my immaturity in the research world.

To Carlos, who four years ago was the first to understand me, for advices, for long hours listening to me and helping solve any problems, thank you for the immense help throughout this journey. Thank you for becoming this great friend, i hope to have your friendship forever.

To Sandra, Andrea, Eduardo, Aprigio, César, Joao, Julio, Hugo, Marcela, Leo, Gemma, the best friends i could have here, were my family away from home. I will miss every minute by your side, thank you for making these past four years the best i could have.

To Sophie, for all the patience, always listening to me talk about work, care and worry about me. By always pushing me forward and believing in me.

To Bruno, the brother that life gave me. These last four years would never be complete without you always close.

To all my friends and partners at CAOS, for all i have learned of each of you. Thank you all!

# Contents

|          | Abst | tract                                                                | iv   |

|----------|------|----------------------------------------------------------------------|------|

|          | Resu | umen                                                                 | V    |

|          | Resu | um                                                                   | vi   |

|          | Resu | umo                                                                  | viii |

|          | Ack  | nowledgements                                                        | X    |

|          | List | of Figures                                                           | xvi  |

|          | List | of Tables                                                            | viii |

|          | List | of Algorithms                                                        | XX   |

|          | List | of Equations                                                         | xii  |

| -1       | T 4  | - Indian                                                             | -1   |

| 1        |      | roduction                                                            | 1    |

|          | 1.1  | Objectives                                                           | 6    |

|          | 1.2  | Work Organization                                                    | 7    |

| <b>2</b> | The  | esis Background                                                      | 9    |

|          | 2.1  | MapReduce Programming Model and Framework                            | 9    |

|          |      | 2.1.1 MapReduce Programming Model                                    | 11   |

|          |      | 2.1.2 Multi-core MapReduce Programming Model                         | 13   |

|          | 2.2  | Multi-core MapReduce frameworks                                      | 14   |

|          |      | 2.2.1 Phoenix                                                        | 15   |

|          |      | 2.2.2 Phoenix++                                                      | 17   |

|          |      | 2.2.3 Metis                                                          | 20   |

|          |      | 2.2.4 Comparing Multicore MapReduce Frameworks: Intermediate Data    |      |

|          |      | Structures                                                           | 21   |

|          |      | 2.2.5 Influence of Key Distribution                                  | 22   |

| 3        | Pro  | posal of Virtual Memory Management                                   | 25   |

| -        | 3.1  | Challenges of Managing Large Data Sets in Multicore MapReduce Frame- | -    |

|          | -    | works and Work Proposals                                             | 25   |

|          | 3.2  | •                                                                    | _    |

|   | 3.3 | Dynar  | nic Monitoring of Resource Utilization                             |

|---|-----|--------|--------------------------------------------------------------------|

|   | 3.4 | Mana   | ging the Use of Memory of the Intermediate Data Structure 30       |

|   | 3.5 | Synch  | ronizing Multiple Threads Spilling to Hard Disk                    |

| 4 | Pro | posal  | of Memory Hierarchy Management 35                                  |

|   | 4.1 | Optim  | nizing Cache Utilization on Shared-Memory MapReduce Frameworks 35  |

|   |     | 4.1.1  | Memory Access Behaviour on Current MapReduce Frameworks 36         |

|   |     | 4.1.2  | Memory Access Behaviour for Intermediate Data Structures 37        |

|   |     | 4.1.3  | Memory Access Behaviour When Scaling to a Higher Number of         |

|   |     |        | Threads                                                            |

|   |     | 4.1.4  | Memory Access Behaviour on the Merge Stage                         |

|   | 4.2 | Propo  | sal: Partial MapReduce Execution                                   |

|   | 4.3 | Propo  | sal: Partial MapReduce Implementation                              |

|   |     | 4.3.1  | Proposal: Map Phase                                                |

|   |     | 4.3.2  | Proposal: Reduce Phase                                             |

|   |     | 4.3.3  | Proposal: Merge Phase                                              |

| 5 | Eva | luatio | n 49                                                               |

|   | 5.1 | Exper  | imental Environment                                                |

|   | 5.2 | Bench  | mark Applications Description                                      |

|   |     | 5.2.1  | Word Count                                                         |

|   |     | 5.2.2  | Inverted Index                                                     |

|   | 5.3 | Workl  | oad $\dots$ 52                                                     |

|   | 5.4 | Memo   | bry Management Performance                                         |

|   |     | 5.4.1  | Buffering and Spill Execution Time                                 |

|   |     | 5.4.2  | Buffering and Spill Main Memory Usage                              |

|   |     | 5.4.3  | Buffering and Spill Major Page Faults                              |

|   |     | 5.4.4  | Thread Disk Acess Execution Time                                   |

|   | 5.5 | Partia | l MapReduce                                                        |

|   |     | 5.5.1  | Word Count Total Execution Time on Intel Xeon                      |

|   |     | 5.5.2  | Word Count Map Phase Total Execution Time on Intel Xeon 63         |

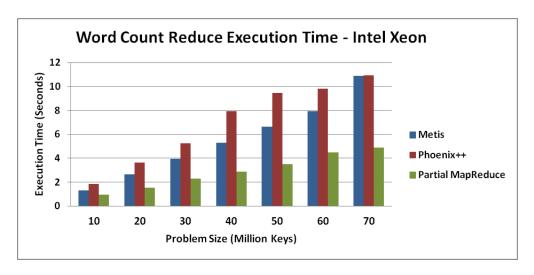

|   |     | 5.5.3  | Word Count Reduce Phase Total Execution Time on Intel Xeon 63      |

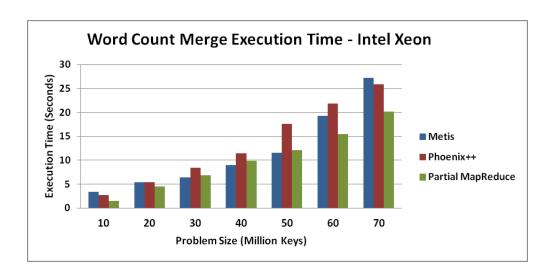

|   |     | 5.5.4  | Word Count Merge Phase Total Execution Time on Intel Xeon 65       |

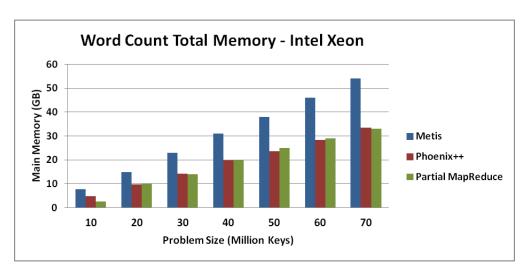

|   |     | 5.5.5  | Word Count Total Main Memory Usage on Intel Xeon 66                |

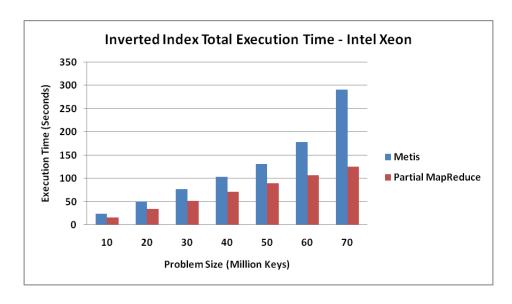

|   |     | 5.5.6  | Inverted Index Total Execution Time on Intel Xeon                  |

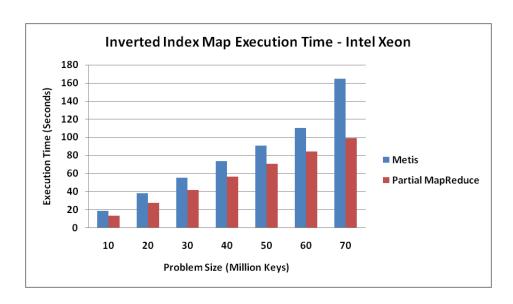

|   |     | 5.5.7  | Inverted Index Map Phase Total Execution Time on Intel Xeon 69     |

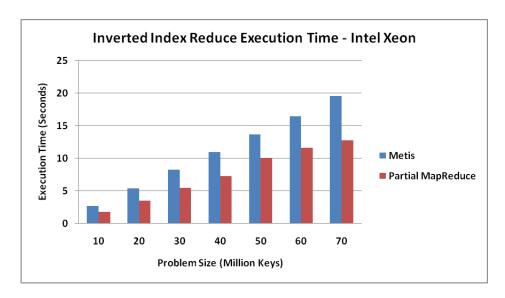

|   |     | 5.5.8  | Inverted Index Reduce Phase Total Execution Time on Intel Xeon. 70 |

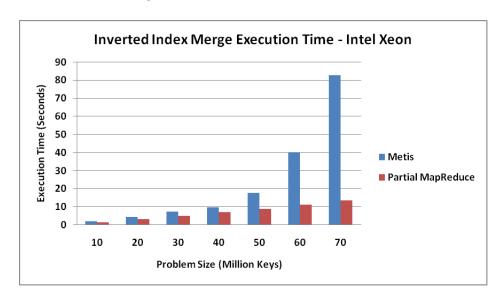

|   |        | 5.5.9   | Inverted Index Merge Phase Total Execution Time on Intel Xeon . | 72 |

|---|--------|---------|-----------------------------------------------------------------|----|

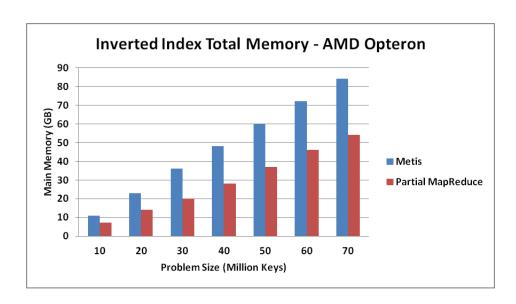

|   |        | 5.5.10  | Inverted Index Total Main Memory Usage on Intel Xeon            | 73 |

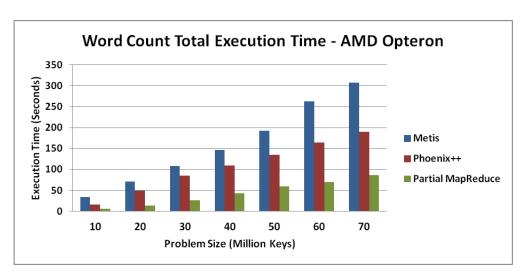

|   |        | 5.5.11  | Word Count Total Execution Time on AMD Opteron                  | 74 |

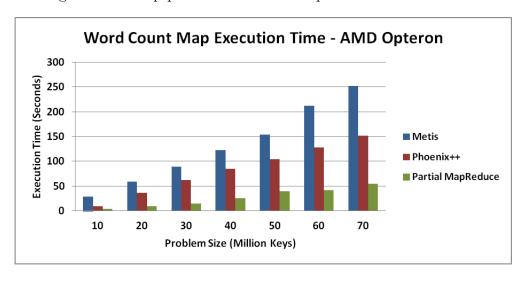

|   |        | 5.5.12  | Word Count Map Phase Total Execution Time on AMD Opteron $$ .   | 76 |

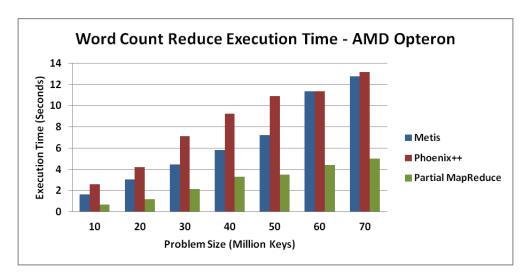

|   |        | 5.5.13  | Word Count Reduce Phase Total Execution Time on AMD Opteron     | 77 |

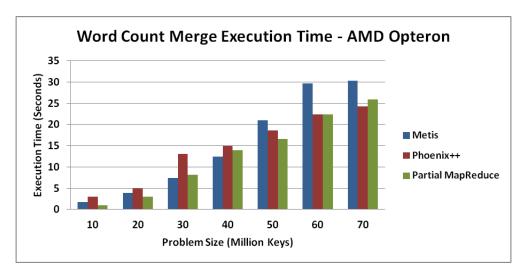

|   |        | 5.5.14  | Word Count Merge Phase Total Execution Time on AMD Opteron      | 78 |

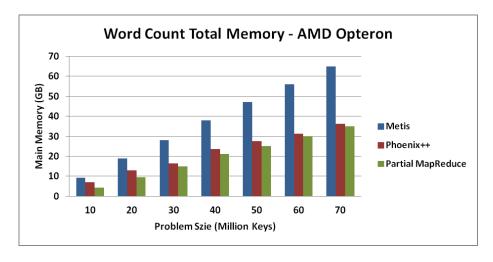

|   |        | 5.5.15  | Word Count Total Main Memory Usage on AMD Opteron               | 79 |

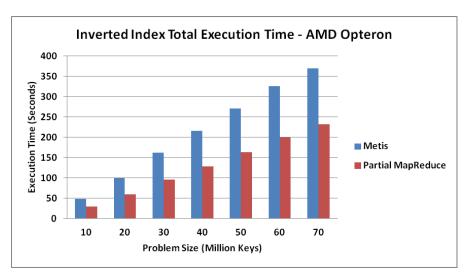

|   |        | 5.5.16  | Inverted Index Total Execution Time on AMD Opteron              | 80 |

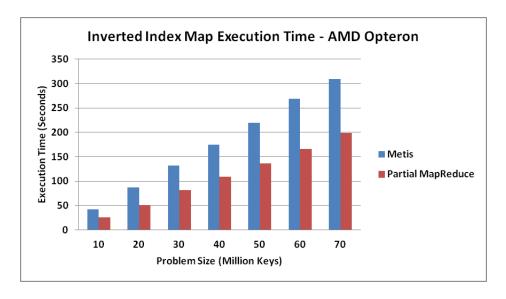

|   |        | 5.5.17  | Inverted Index Map Phase Total Execution Time on AMD Opteron    | 81 |

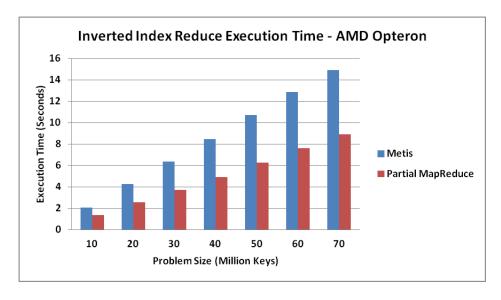

|   |        | 5.5.18  | Inverted Index Reduce Phase Total Execution Time on AMD Opteron | 82 |

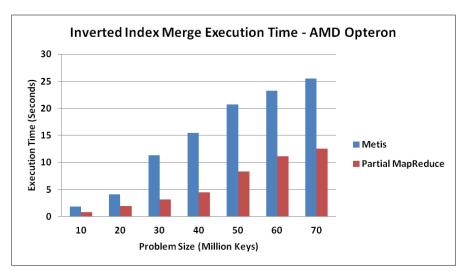

|   |        | 5.5.19  | Inverted Index Merge Phase Total Execution Time on AMD Opteron  | 83 |

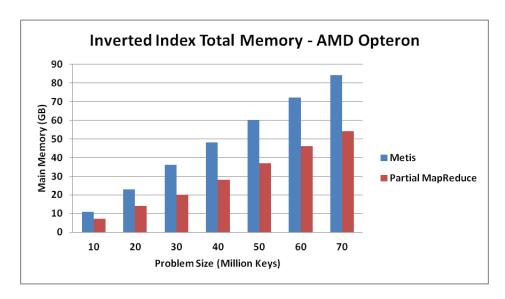

|   |        | 5.5.20  | Inverted Index Total Main Memory Usage on AMD Opteron           | 84 |

| 6 | Con    | clusio  | as                                                              | 87 |

|   | 6.1    | Final ( | Conclusions                                                     | 87 |

|   | 6.2    | Future  | Work and Open Lines                                             | 88 |

| B | iblioe | graphy  |                                                                 | 91 |

# List of Figures

| 1.1  | Basic data flow for MapReduce programming model                    | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Intermediate data structure organization                           | 4  |

| 2.1  | Full Programming Model Map Reduce Schema.                          | 12 |

| 2.2  | MapReduce Model With Combiner Functions                            | 13 |

| 2.3  | MapReduce Programming Model                                        | 14 |

| 2.4  | Multi Core MapReduce Framework                                     | 15 |

| 2.5  | Phoenix intermediate data structure Map Phase                      | 16 |

| 2.6  | Phoenix intermediate data structure Reduce Phase                   | 17 |

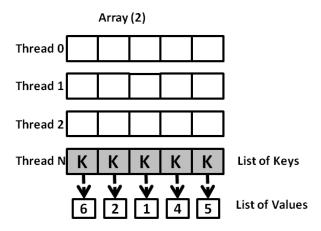

| 2.7  | Phoenix++ non-blocking shared array                                | 18 |

| 2.8  | Phoenix++ fixed-size thread-local array                            | 18 |

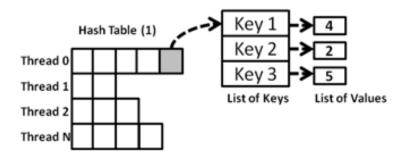

| 2.9  | Phoenix++ variable-width hash table                                | 19 |

| 2.10 | Metis intermediate data structure                                  | 20 |

| 2.11 | MapReduce Framework Key Distribution                               | 23 |

| 3.1  | Growth of intermediate data structure depending on the parallelism | 26 |

| 3.2  | Proposed scheme to improve memory hierarchy usage                  | 28 |

| 3.3  | MapReduce Framework Buffering and spill scheme                     | 30 |

| 3.4  | Buffering and spill scheme                                         | 31 |

| 4.1  | Intermediate data structures used by Metis                         | 40 |

| 4.2  | Two-level hierarchy for storing intermediate key/value pairs       | 40 |

| 4.3  | Partial MapReduce scheme                                           | 42 |

| 4.4  | Complete Partial MapReduce scheme                                  | 44 |

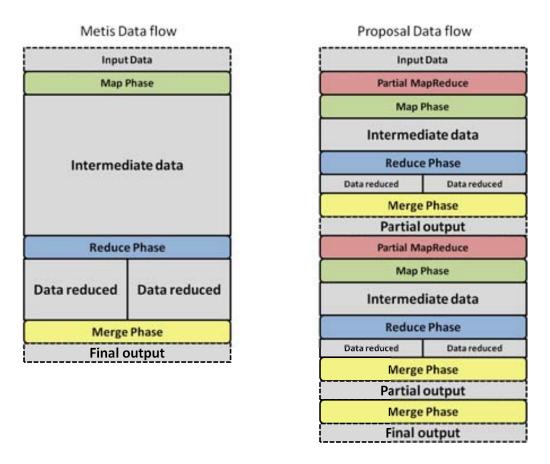

| 4.5  | Metis Data Flow versus Proposal Data Flow                          | 46 |

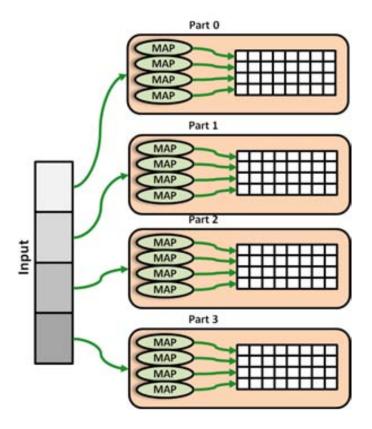

| 4.6  | Partial MapReduce Map phase scheme                                 | 47 |

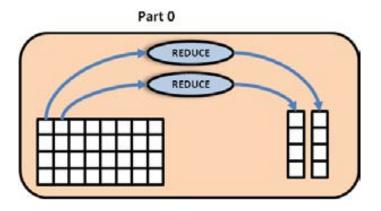

| 4.7  | Partial MapReduce Reduce phase scheme                              | 47 |

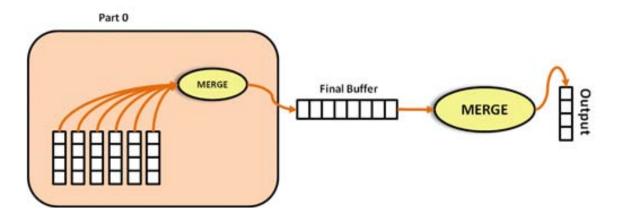

| 4.8  | Partial MapReduce Merge phase scheme                               | 48 |

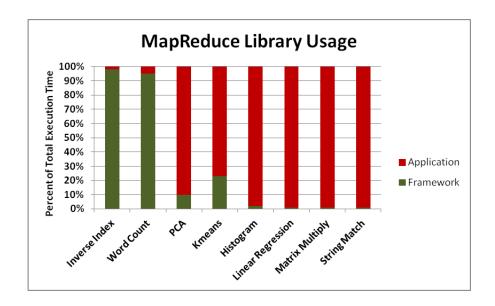

| 5.1  | MapReduce library usage                                            | 51 |

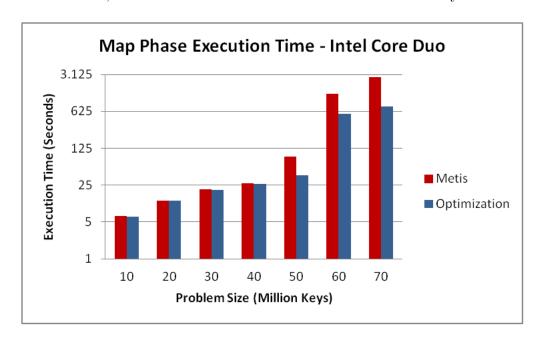

| 5.2  | Map phase Execution Time using Buffering/Spill mechanism           | 53 |

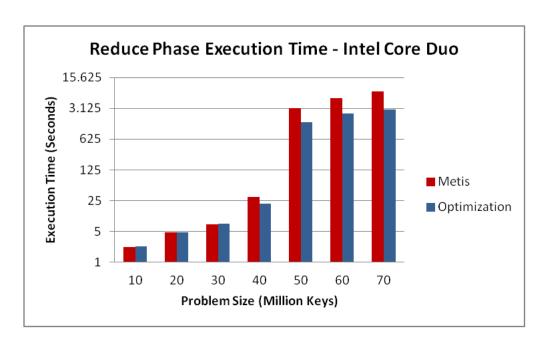

| 5.3  | Reduce phase Execution Time using Buffering/Spill mechanism                              | 54 |

|------|------------------------------------------------------------------------------------------|----|

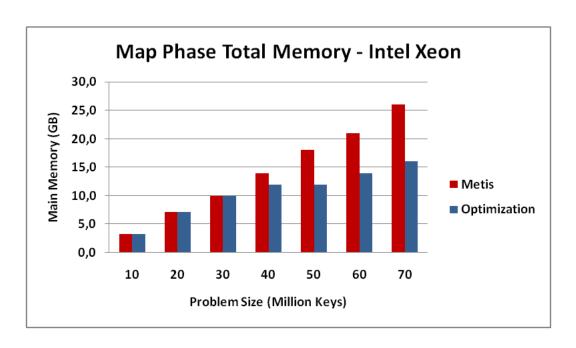

| 5.4  | Main memory usage on Map phase using Buffering/Spill mechanism                           | 55 |

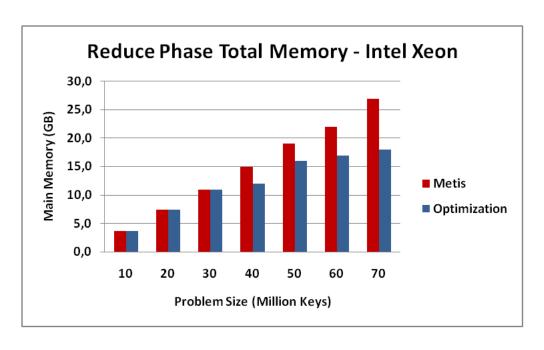

| 5.5  | Main memory usage on Reduce phase using Buffering/Spill mechanism                        | 56 |

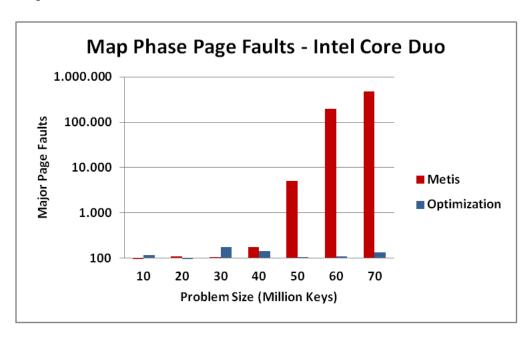

| 5.6  | Page faults Reduction on Map phase using spill/buffering mechanism                       | 57 |

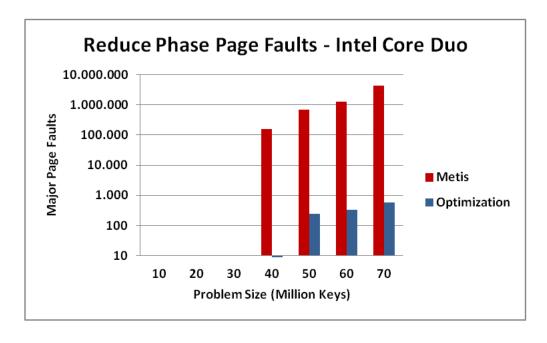

| 5.7  | Page faults Reduction on Reduce phase using spill/buffering mechanism. $$ .              | 57 |

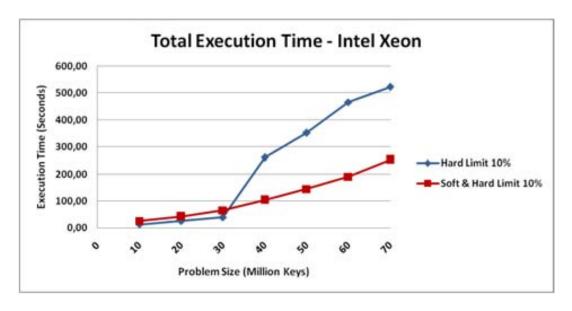

| 5.8  | Total execution time using hard and soft limit                                           | 58 |

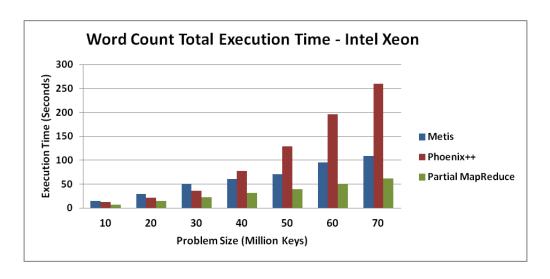

| 5.9  | Intel Xeon Total Time using Word Count Benchmark                                         | 60 |

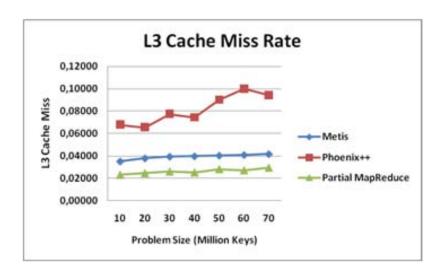

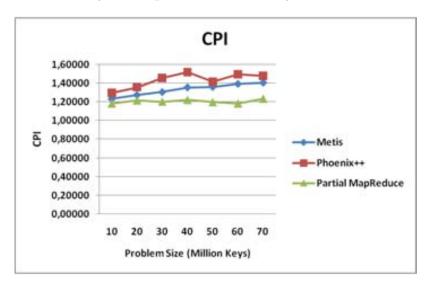

| 5.10 | Word Count L3 Cache Memory miss rate on Intel Xeon                                       | 61 |

| 5.11 | Word Count Benchmark CPI on Intel Xeon                                                   | 61 |

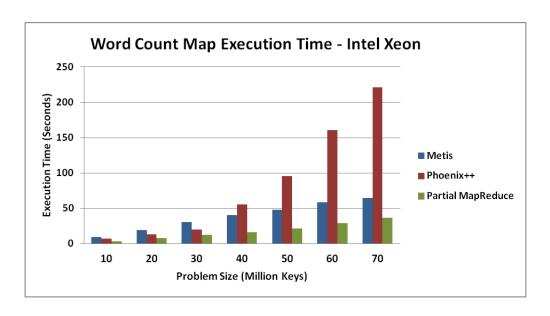

| 5.12 | Intel Xeon Map phase execution time using Word Count Benchmark                           | 63 |

| 5.13 | Intel Xeon Reduce phase execution time using Word Count Benchmark                        | 64 |

| 5.14 | Intel Xeon Merge phase execution time using Word Count Benchmark. $$                     | 66 |

| 5.15 | Intel Xeon main memory usage using Word Count Benchmark                                  | 67 |

| 5.16 | Intel Xeon Total Time using Inverted Index Benchmark                                     | 69 |

| 5.17 | Intel Xeon Map phase execution time using Inverted Index Benchmark                       | 70 |

| 5.18 | Intel Xeon Reduce Phase Execution Time using Inverted Index Benchmark.                   | 71 |

| 5.19 | Intel Xeon Merge Phase Execution Time using Inverted Index Benchmark.                    | 72 |

| 5.20 | Intel Xeon Main Memory Usage using Inverted Index Benchmark                              | 74 |

| 5.21 | AMD Opteron Total Time using Word Count Benchmark                                        | 75 |

| 5.22 | $\operatorname{AMD}$ Opteron Map phase execution time using Word Count Benchmark         | 76 |

| 5.23 | $\operatorname{AMD}$ Opteron Reduce Phase Execution Time using Word Count Benchmark.     | 77 |

| 5.24 | $\operatorname{AMD}$ Opteron Merge Phase Execution Time using Word Count Benchmark.      | 78 |

| 5.25 | AMD Opteron main memory usage using Word Count Benchmark                                 | 79 |

| 5.26 | AMD Opteron Total Time using Inverted Index Benchmark                                    | 80 |

| 5.27 | AMD Opteron Map phase execution time using Inverted Index Benchmark.                     | 81 |

| 5.28 | ${\bf AMD\ Opteron\ Reduce\ Phase\ Execution\ Time\ using\ Inverted\ Index\ Benchmark}.$ | 82 |

| 5.29 | $\operatorname{AMD}$ Opteron Merge Phase Execution Time using Inverted Index Benchmark.  | 83 |

| 5.30 | AMD Opteron Main Memory Usage using Inverted Index Benchmark                             | 84 |

# List of Tables

| 3.1  | Memory Limit                                                                                           | 34 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 5.1  | Benchmark applications that make higher use of the MapReduce library                                   | 50 |

| 5.2  | Benchmark applications that make lower use of MapReduce library                                        | 50 |

| 5.3  | Repeated Keys Workload                                                                                 | 52 |

| 5.4  | Total Execution Time Speedup on Intel Xeon using Word Count Benchmark.                                 | 60 |

| 5.5  | Map Phase Execution Time Speedup on Intel Xeon using Word Count                                        |    |

|      | Benchmark                                                                                              | 63 |

| 5.6  | Reduce Phase Execution Time Speedup on Intel Xeon using Word Count                                     |    |

|      | Benchmark                                                                                              | 65 |

| 5.7  | Merge Phase Execution Time Speedup on Intel Xeon using Word Count                                      |    |

|      | Benchmark                                                                                              | 66 |

| 5.8  | Reduction in main memory usage on Intel Xeon using Word Count Benchmark.                               | 68 |

| 5.9  | ${\it Total \ Execution \ Time \ Speedup \ on \ Intel \ Xeon \ using \ Inverted \ Index \ Benchmark}.$ | 69 |

| 5.10 | Map Phase Execution Time Speedup on Intel Xeon using Inverted Index                                    |    |

|      | Benchmark                                                                                              | 70 |

| 5.11 | Reduce Phase Execution Time Speedup on Intel Xeon using Inverted Index                                 |    |

|      | Benchmark                                                                                              | 71 |

| 5.12 | Merge Phase Execution Time Speedup on Intel Xeon using Inverted Index                                  |    |

|      | Benchmark                                                                                              | 73 |

| 5.13 | Reduction in Main Memory Usage on Intel Xeon using Inverted Index                                      |    |

|      | Benchmark                                                                                              | 74 |

| 5.14 | Total Execution Time Speedup on AMD Opteron using Word Count Bench-                                    |    |

|      | mark                                                                                                   | 76 |

| 5.15 | Map Phase Execution Time Speedup on AMD Opteron using Word Count                                       |    |

|      | Benchmark                                                                                              | 77 |

| 5.16 | Reduce Phase Execution Time Speedup on AMD Opteron using Word                                          |    |

|      | Count Benchmark                                                                                        | 78 |

| 5.17 | Merge Phase Execution Time Speedup on AMD Opteron using Word Count                                     |    |

|      | Benchmark                                                                                              | 79 |

| 5.18 | Reduction in Main Memory Usage on AMD Opteron using Word Count       |    |

|------|----------------------------------------------------------------------|----|

|      | Benchmark                                                            | 80 |

| 5.19 | Total Execution Time Speedup on AMD Opteron using Inverted Index     |    |

|      | Benchmark                                                            | 81 |

| 5.20 | Map Phase Execution Time Speedup on AMD Opteron using Inverted Index |    |

|      | Benchmark                                                            | 82 |

| 5.21 | Reduce Phase Execution Time Speedup on AMD Opteron using Inverted    |    |

|      | Index Benchmark                                                      | 83 |

| 5.22 | Merge Phase Execution Time Speedup on AMD Opteron using Inverted     |    |

|      | Index Benchmark                                                      | 84 |

| 5.23 | Reduction in Main Memory Usage on AMD Opteron using Inverted Index   |    |

|      | Benchmark                                                            | 85 |

# List of Algorithms

| 1 | Pseudo-code of the monitoring package | 29 |

|---|---------------------------------------|----|

| 2 | Partial MapReduce overview            | 45 |

# List of Equations

| 3.1 | Total memory of the environment         | 29 |

|-----|-----------------------------------------|----|

| 3.2 | Total of free memory of the environment | 29 |

| 3.3 | Soft Limit values                       | 34 |

## Chapter 1

### Introduction

In the early years of modern computing, when the first electronic computer was developed, the famous ENIAC in 1946 occupied a huge room at the University of Pennsylvania in the United States. At that time many of the most experienced technologists thought, except for advanced military applications, such as breaking encryption codes or calculate trajectories of projectiles, no one would want something as big as that. As technology has advanced, the machines invaded the civilian world. Today there are computers everywhere, it is hard to look at a side where there is not one. The evolution of technology has reduced the physical size of computers and increased performance on a single workstation, however the increased speed of the processors found growing barriers, as the physical limits were reached. Today it is not possible to increase the frequency of processors as was observed in the 90. The need for processing capacity is no longer achieved by faster processors and now being obtained by increasing the number of operations performed simultaneously, i.e. parallel processing.

Parallel systems are computer environments composed of a set of processing units that work together in a simultaneous way with the objective of solving a problem. Parallel environments are attractive because of their processing throughput, and their larger amount of main memory and storage capacity. Such systems have emerged as a solution to solve problems in totally different areas [12]. The set of typical applications of these systems include, physical systems simulations, and technical computations in the diverse areas of the chemistry, physics, biology, materials science, climatology, astrophysics and subsurface transport [5].

However, the use of parallel systems becomes useless if the necessary applications are not properly designed. In general, the idea of processing a data set consists of simple strategies, but becomes complicated when it is necessary to process large data sets in a distributed way.

MapReduce[11] is a programming model for expressing distributed computations and a distributed execution framework for processing large amounts of data [29]. In the MapReduce programming model, the user defines an algorithm using only two functions, Map and Reduce.

The Map function takes an input data set and produces a set of intermediate key/value pairs. The Reduce function receives an intermediate key K and a set of values for that key. It aggregates together these values to create an output for the problem. Typically just zero or one output value is produced per Reduce operation. In general, reductions must wait until all Map operations are completed.

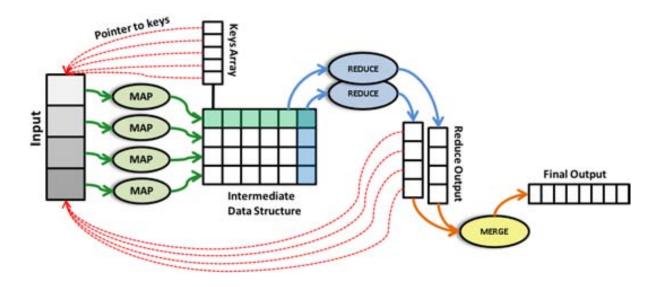

The MapReduce Model uses combiner functions to allow the local aggregation of values of each Map. The complete MapReduce model scheme can be seen in Figure 1.1.

Figure 1.1: Basic data flow for MapReduce programming model.

The main advantage of MapReduce is to provide a simple abstraction for the developer, transparently handling most of the internal implementation details in a scalable, robust, and efficient manner[29].

The goal of MapReduce was focused on hiding complex problems of parallel execution like fault tolerance, data distribution and load balancing [2][26]. The MapReduce usage allows programmers to exclusively search for solutions to specific problems, as opposed to how those computations are actually carried out or how to get the data to the processes

that need them.

MapReduce execution gets parallel speedup by running many Maps concurrently, each on a different part of the input file, and by running many Reduces concurrently on different keys. In short the charm of MapReduce is that the programming model hides all the concurrency management problems from the programmer[30].

In cluster-based MapReduce frameworks like Hadoop[44], the idea is to spread data across the local disks of nodes and run processes on nodes that hold the data. The complex issues of task managing storage in such environment are handled by using a distributed file system assembled over MapReduce. In most Hadoop executions, a distributed file system is used to store both the input to the Map phase and the output of the Reduce phase [10].

In Hadoop, each Map task is executed on the node that holds the input split, so that the Map will be processing local data. If it is not possible to run a Map task on local data, it becomes necessary to send input key/value pairs across the network.

Map and Reduce tasks run in isolation without any mechanism for direct communication. During the shuffle and sort phase, the intermediate key/value pairs are merged, sorted and then copied from the Map to the Reduce tasks nodes.

The need for faster processing required on a simple workstation in recent years, provided a growth of multi-core and multi-processor systems. The advances in technology, circuits integration and the limited performance of wide issue intruction execution, made multi-core and multi-processor shared memory architectures become the basic building block of parallel systems. They embeds multiple processing cores into a single system to exploit growing amounts of thread-level parallelism for achieving higher overall chip-level instruction-per-cycle rates.

By working over multi-core, cluster-based MapReduce frameworks exploit the parallelism offered by current parallel workstations by running multiple, independent MapReduce instances on the same node. The framework schedules tasks dynamically across the available processors in order to achieve parallelism, load balance and maximize task throughput.

Typical programming view of MapReduce frameworks can be divided into two set of functions, the user and system set. The Map user-defined function is applied in parallel over the input data, producing a list of intermediate key/value pairs. The Reduce user-defined function is applied in parallel to all intermediate pairs with the same key. The system set is composed of system-defined functions that are responsible for exploiting the available parallelism, data distribution and intermediate key/value management[24].

In shared-memory systems, the intermediate data produced by the Map phase and the Reduce phase output are stored in shared memory. Compared to cluster-based approaches, the multi-core has as main advantage its faster core-to-core communication through shared memory [7][34]. For multi-core MapReduce frameworks the most important aspect is that the Map and Reduce tasks handle with intermediate key/values through a shared memory. Unlike the cluster-based where the handling takes place through the distributed file system and network.

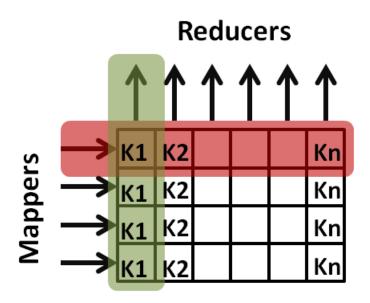

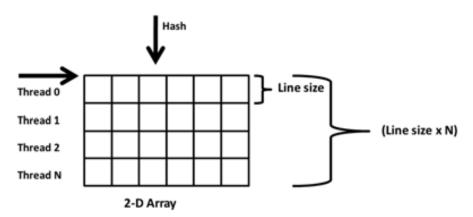

The use of a data structure organized in rows and columns makes Map and Reduce tasks independent. Each Map task has its own row in a hash table. Using a unique hash function, it finds the key position in the hash table. By processing the keys per column, each Reduce task has access to all the repeated keys produced from different Map tasks, as can be seen in Figure 1.2. Such a strategy avoids data copying, as reduce tasks reuse the data structure product of the Map phase.

Figure 1.2: Intermediate data structure organization.

Metis[30] and Phoenix++[42] were implemented to support multi-core MapReduce implementations,

In general, Phoenix++ and Metis work the same way, by using hash tables as a base, which allows quick key lookup with O(1) complexity. Reduce tasks have simple and fast access to all values of the same key by accessing columns of the data structure. Moreover, Phoenix and Metis add rows to the hash table to increase the parallelism achieved, making each worker has its own memory space.

In order to minimize the number of repeated keys in the intermediate data structure, Phoenix++ and Metis implement a combiner function, which aims to make a local thread reduction, saving main memory. After running the combiner function, the framework no longer stores a set of values and stores only a combined value of a given key.

The main differences between Phoenix++ and Metis is how they allocate the intermediate data structure and how they store the keys/value pair per hash entry.

In order to allocate the intermediate data structure, Metis tries to predict its size. First samples a part of the input and calculates the number of different keys, then allocates the hash table to have a specific amount of entries so that each entry contains a bounded number of keys. Phoenix++ on the other hand uses a resizable hash table, which can scale depending on the key distribution.

To store the keys/value pairs in hash entries, Phoenix++ uses a vector and Metis uses a B+tree index. The vector usage is more advantageous to store sets of keys from non repeated keys input, that do not require to be sorted. On the other hand, the use of trees is most advantageous for large sets of repeated keys.

Current MapReduce frameworks deal with some major performance problems. MapReduce frameworks are not designed to be efficient if the intermediate data do not fit in main memory.

Large input MapReduce applications provide a key distribution which causes the intermediate data structure to grow. On multi-core environments, such data structures can consume all the available main memory. When the available memory is not large enough to store the data structure, it creates a paging file on the hard disk, starting the use of virtual memory. Continuous hard disk access makes the framework have a severe performance loss.

Moreover, dealing with large datasets in main memory does not make scalable MapReduce frameworks. Such behavior is presented because MapReduce frameworks present a high contention when using threads across multiple chips. Due to non-uniform memory access effects, the cost are increased when more chips are used, obtaining a worse performance with increasing number of threads[45].

Another major problem of multi-core MapReduce frameworks, it is the low cache memory data-locality, when it is necessary to process large data sets. The large number of different keys produced and the growth of the intermediate data structure makes it difficult to keep all relevant data in cache memory.

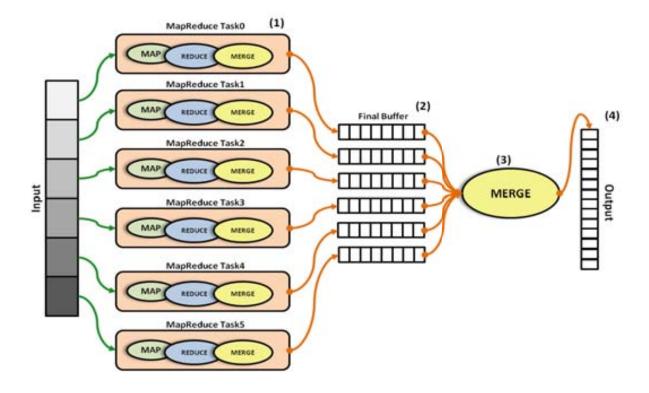

In order to solve the problems presented in multi-core MapReduce frameworks, we designed and implemented a solution that manages, handles and stores keys in a more efficient intermediate data structure.

In this work we describe an engineering technique for the MapReduce runtime library to minimize the memory footprint and execution-time overheads when it is necessary to manipulate large data sets. The proposed approach is divided into two major parts: a memory management system for the intermediate data structure with a set of parameters and limits to synchronize spilling of multiple threads to the hard disk, and a partial MapReduce system optimized for better cache memory data-locality.

The memory management system for the intermediate data structure prevents that the amount of intermediate data generated consumes the entire main memory. Our proposed approach monitors the main memory usage on runtime, until a pre-defined limit is met. Then it moves key/value pairs between main memory and hard disk until memory is available again. Furthermore, using a set of parameters and limits, our mechanism synchronizes the threads, thus avoiding any competition when spilling on the hard disk. Our memory management mechanism adapts to changes in the available memory in the execution environment, caused by sharing the system between different applications.

The proposed partial MapReduce system aims to increase the cache memory data cache locality. The mechanism groups execution of Map and Reduce phases such that the Reduce phase begins as soon as the number of keys generated in the Map phase reaches a pre-defined limit. Such a strategy assures that the most relevant data is maintained into cache memory. The main issues of this proposed mechanism are:

- Partially stop the production of keys by the Map phase when reaching a cache size-fit limit;

- Reduce the data produced partially so that the relevant data can fit in the last-level cache, and only then return to run the Map phase;

- By restricting the amount of keys produced by the Map phase and run the Reduce phase before the end of all Map operations it is possible to keep fewer keys repeated in memory;

- Perform a global reduction when all the input has already been processed.

#### 1.1 Objectives

The main objective of this work is to design, implement and evaluate a mechanism to improve the performance of multi-core MapReduce frameworks through efficient handling of intermediate data structures. The strategy to solve this problem focuses in improving the integration in memory hierarchy, hard disk, main memory and cache memory. The specific objectives of this work are numbered as follows:

- 1. Evaluate Metis and Phoenix++ performance using MapReduce applications that process large data sets and identify the potential bottlenecks in multi-core MapReduce frameworks;

- 2. Design and implement a memory management mechanism for multi-core MapReduce frameworks that deals with changes in the amount of available memory and reduce the main memory usage when the data do not fit in main memory;

- 3. Design and implement a mechanism to store and manipulate keys in a intermediate data structure on MapReduce frameworks, which achieves better performance by increasing data locality;

- 4. Propose a set of parameters that must be added to multi-core MapReduce frameworks to manage the use of cache memory, main memory and hard disk for each specific system;

- 5. Evaluate the performance improvement of the proposed solutions.

#### 1.2 Work Organization

Through the objectives previously proposed the outline of the work follows this organization.

- Chapter 2: Thesis Background. Presents the MapReduce programming model and the related work on multi-core architectures. Introduces a brief explanation of intermediate data structures and the influence of key distribution, in addition to the problem with the growth of intermediate structures.

- Chapter 3: Proposal of Virtual Memory Management. Presents the proposed mechanism to improve Virtual Memory Management, as well as details in the implementation of the proposal.

- Chapter 4: Proposal of Memory Hierarchy Management. Presents the proposed mechanism to improve the memory hierarchy integration, as well as details of the implementation, advantages and main points.

- **Chapter 5: Evaluation.** Describes the used scenario and provides an explanation of the results of our proposal as well as the types of applications and workloads.

- **Chapter 6: Conclusions.** Finally, we present a conclusion of this work, future work and open lines.

## Chapter 2

# Thesis Background

In this chapter we first introduce the MapReduce programming model describing its principles and some relevant details not visible to programmers. We start by introducing the MapReduce programming phases and the internal operations that frameworks must provide in between them. Then, we describe the existing multi-core MapReduce implementations attending their architectural differences, focusing our description in the specific details of the intermediate data structures they use. Of special importance are key distribution and how current data structures tolerate data growth and variations of key distributions. Finally, we discuss the influence of the memory hierarchy in multi-core MapReduce frameworks

#### 2.1 MapReduce Programming Model and Framework

MapReduce[11] is a programming model originally developed by Google for expressing distributed computations on massive amounts of data. It is also a private framework for large-scale data processing on clusters of commodity servers [29][33][46]. Its main objective is to facilitate the task of parallel programming. It proposes a way of abstracting the details related with data distribution, load balancing and fault tolerance through a clear and simplified API of a distributed framework. The work of the programmers is to design a solution to their problems by applying the MapReduce model. Then, the framework is in charge of parallelizing the computation among the computing resources [14][15].

Since its introduction of MapReduce, apart from its intensive use by Google for tasks involving large datasets each day, it has gained popularity by the widely use of Hadoop [44], an Apache project MapReduce implementation. Hadoop has been used regularly by public and private institutions like Yahoo, eBay, Facebook, Twitter, Amazon and IBM [19].

All MapReduce computations are arranged along a set of operations that take advantage of a set of distributed computing resources in a cluster[35][31]. In Google and Hadoop implementations, there are two main subsystems inside the framework:

- Task management environment: in charge of forking, synchronization and elimination of computation worker tasks;

- Distributed file system: MapReduce frameworks use their own file systems like GFS [18][27] or HDFS [44] to store datasets. They provide read, write operations on a distributed data repository and allow the replication of blocks as a fault tolerance method.

Once a problem is specified in terms of the MapReduce programming model, we can also use that design to execute applications on any shared memory, multicore CPU computer [9]. Then, the programming model becomes our point in common with the cluster original implementations. This model is based on the following concepts [25]:

- 1. Iteration over the input.

- 2. Computation of key/value pairs from each piece of input.

- 3. Grouping of all intermediate values by key.

- 4. Iteration over the resulting groups.

- 5. Reduction of each group.

The terms *Map* and *Reduce* come from Lisp operations with the same name. In practice, Reduce here can be significantly different from the Lisp s in that the output does not need to be smaller than the input, and may in fact be higher [9].

The most viable approach to efficiently tackling large-data problems today is to divide and conquer, which is a fundamental concept in computer science that is introduced very early in typical undergraduate curricula. The basic idea is to partition a large problem into smaller sub-problems. To the extent that the sub-problems are independent [1], they can be tackled in parallel by different workers, represented by threads in a processor core, cores in a multi-core processor, multiple processors in a machine, or many machines in a cluster.

MapReduce frameworks perform parallel processing first by distributing the data among a group of nodes. Then, each worker applies the same computation to a different local input data block [36].

The MapReduce programming model has been effective in solving some problems because it easily fits many solutions to large data analysis. Expressing computation in terms of Map and Reduce operations exhibits the inherent parallelism of an application, allowing the efficient exploitation of distributed machines by executing many tasks in parallel [4]. The importance of MapReduce is providing an effective tool to tackle the problem of large-scale data processing. It represents an effective new way of organizing the computations needed at a very large scale [29].

#### 2.1.1 MapReduce Programming Model

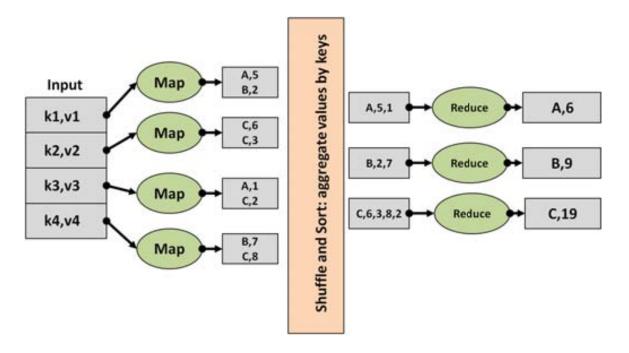

As previously mentioned, the MapReduce programming model is simple. The input data format is application-specific, and must be specified by the user [22][37][28]. In principle, programmers must design a solution using Map and Reduce operations. From the point of view of the programmer, the model can be expressed in the following stages that are shown in Figure 2.1.

- Input is split in blocks and each map task receives one block as its input;

- Map tasks receive a key/value pair (a record) from each entry of its input block. For text inputs, the key is the input file line number while the value is the text of the line;

- Map tasks apply some computation to each key/value input pair and generate zero, one, or several different key/value outputs;

- Reduce tasks input is a unsorted set of all values generated by all map tasks associated with a specific key;

- Reduce tasks apply some computation, usually some kind of reduction operation such as summation, to the set of values and generate an output as a solution to the problem;

- The disjoint set of keys and values received by each reduce task is sorted by key.

Some relevant consequences are derived from this model.

- Map tasks are executed on local blocks of data without any interdependency;

- At the end of the execution of the map tasks, they generate a set of data called intermediate key/value pairs. This set of values is automatically shuffled (merged) and sorted by the framework before providing input to reduce tasks;

Reduce tasks cannot generate a solution until all map tasks have finished their execution;

Reduce tasks do not have any interdependency.

Figure 2.1: Full Programming Model Map Reduce Schema.

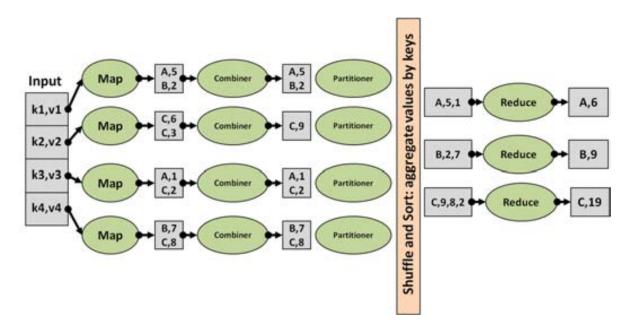

In addition to the Map and Reduce operations, there are helper functions to increase efficiency: combiner and partitioners, as shown in figure 2.2. The combiner functions allow the aggregation of values for the same key at the end of the map execution. The partitioner functions allow us to define the distribution of keys among the reducers.

Figure 2.2: MapReduce Model With Combiner Functions.

### 2.1.2 Multi-core MapReduce Programming Model

There are different implementations of MapReduce for parallelizing computing heterogeneous and multi-core environments, for FPGA chips as the FPMR [40], GPU[4], [20], [21], [41], [13], [32], [6], [3] and especially for multi-core architectures and multi-processor shared memory as Phoenix[38][45], Phoenix++[42] and Metis[30], where we are focusing our work.

As for cluster systems, multi-core MapReduce implementations require the programmers to design their algorithms using two functions: map and reduce. Multi-core MapReduce frameworks are available for programmers in the form of libraries, while Hadoop implementations provide an API via a Java runtime system in the form of a set of classes and objects.

Typically, the library partitions the input into fixed size blocks and calls the specific user map implementation on each block. The framework usually executes one thread per CPU core for running map tasks.

Each map task generates a list of intermediate key/values as its output. When all input blocks are processed by map tasks, the library starts creating reduce tasks, again one per core, to call the specific user reduce implementation. This time, the library calls reduce once for each distinct key produced by the map tasks. Each reduce generates a set of output key/value pairs. Finally, there is a merge step where the framework sorts all

reduce outputs by key.

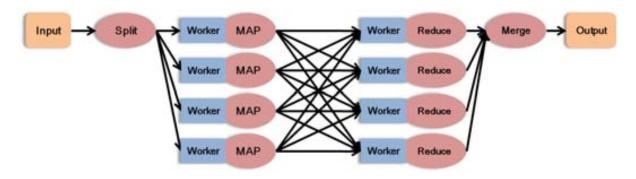

Figure 2.3: MapReduce Programming Model.

The main benefit of this model is simplicity. The programmer provides a simple description of the algorithm that focuses on functionality and not on parallelization [38]. Frameworks make use of multi-core resources by running many map tasks concurrently, each on a different input block, and by executing many reduce tasks on different keys.

# 2.2 Multi-core MapReduce frameworks

The performance of MapReduce frameworks such as Hadoop is managed by the configuration of a large number of parameters. System managers are responsible of modifying default values to increase the efficiency of the platform for running a specific set of applications.

It is very important to have a good implementation of the sort-merge algorithm that must join all intermediate key/values generated by map tasks, sort them and send the joined values to each reduce task. This operation depends on the actual bandwidth of both disk and network systems [11].

The multi-core MapReduce frameworks can be understood as interleaved models of parallel and serial computation operating in steps. At each step, the user-defined serial functions are executed independently in parallel. Each step consists of the consecutive execution of the main phases, Map and Reduce [19].

The multi-core MapReduce frameworks have been designed to use the shared main memory of the system. All map and reduce tasks operate in a shared data structure that must be stored in main memory. This approach takes advantage of the rapid communication between tasks through shared memory [7]. Therefore, the design and performance of the data structures used to store and retrieve intermediate data are crucial in overall system performance [45].

MapReduce frameworks for multi-core architectures typically make extensive use of pointers. All the framework main functions provide pointers to the input/output data buffers. The use of pointers allows the data manipulation through all the phases without the need for copying large amounts of data [38]. For instance, keys are not copied to intermediate data structures. Instead, pointers to keys in the original input are used as seen in Figure 2.4. An additional benefit is to simplify the implementation for any key data type and size.

Figure 2.4: Multi Core MapReduce Framework.

#### 2.2.1 Phoenix

Phoenix implements MapReduce for shared-memory systems [38][45]. It presents an API to the programmer through a framework that deals with the issues of parallelization. It consists of a set of functions that allows the programmer to initialize the framework and link it with the application to be executed. The Phoenix runtime system spawns multiple processes or threads that apply Map and Reduce functions concurrently across the elements of the input dataset [45]. The API guarantees that within a partition of the intermediate output, reducers will process the input pairs in key order, making it easy to produce a sorted final output that is often desired. The Map and Reduce functions are declared as void pointers wherever possible, providing flexibility in their declaration and fast use without conversion overhead.

To start the Map stage, the framework uses the Splitter function to divide input into

equally sized units to be processed by the Map tasks. The Splitter function is called once per Map task and returns a pointer to the input data that will be processed. When a MapReduce application starts a job, it spawns multiple workers and binds them to different CPU cores. The Map tasks are allocated dynamically to workers and each one emits intermediate key/value pairs, which are stored in an intermediate data structure.

Figure 2.5: Phoenix intermediate data structure Map Phase.

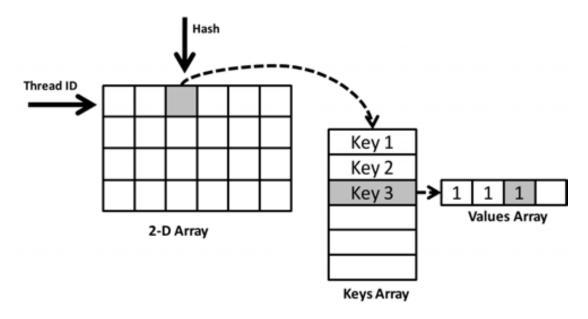

Phoenix uses a matrix as intermediate data structure as shown in Figure 2.5. Each worker responsible of a map task accesses a different row of the matrix.

When the Map worker emits a key, it uses a hash function to determine a position in its own row. This position contains a pointer to a keys array where the emitted key is searched. The keys in the keys array are kept sorted to accelerate this search process. For each key contained in this keys array there is another array where values are stored. When a key already exists in the array of keys, the new value is just appended to the array of values. If the emitted key is not found, (a pointer to) the actual key is stored in the keys array. When a keys array is full, it is dynamically doubled. The same happens with the values array.

In summary, each map worker uses a hash function shared by all map workers. It accesses a row of pointers as a fixed-sized hash table. For each hash element, there is a hash bucket containing keys. Each array of keys is implemented as a contiguous buffer. The framework must wait for all Map tasks to complete before initiating the Reduce phase.

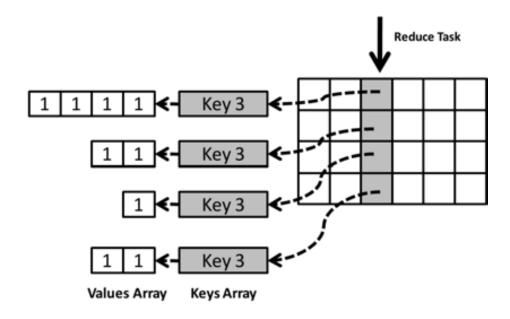

In the Reduce phase, aiming to quickly join all the equal keys and their values, each

Figure 2.6: Phoenix intermediate data structure Reduce Phase.

reduce worker retrieves all the keys and values of a column of the matrix as shown in Figure 2.6. By assigning different workers to different columns all keys and its associated values are merged. When a reduce worker finishes reduction in one designated column, the framework is responsible of assigning another column to be processed.

The input of each reduce task is a set of arrays already sorted by key and at the end of the reduce phase, each key has only one value associated with it. In the last step the final output from all reduce tasks is merged into a single buffer, then sorted by keys. To Phoenix, this Merge phase is considered optional.

#### 2.2.2 Phoenix++

As a complete revision of the original Phoenix, Phoenix++[42] was developed to improve execution speed through modularity in critical sections. First, it provides a flexible intermediate key/value storage abstraction that permits to adapt the specific implementation to the features of the workload. And second, it includes a more effective combiner implementation that can minimize memory usage.

As an improvement from the first implementation, Phoenix++ considers different types of key distributions and basic execution parameters, which directly influence the use of shared memory.

Phoenix++ classifies MapReduce applications by the number of keys that the map tasks will emit:

- 1:1 each task outputs a single, unique key;

- \*:k any map task can emit any of a fixed number of keys, k;

- \*:\* any map task can emit any key, where the number of keys is not known before execution.

The idea of knowing the type of key distribution is to allow the user to choose a type of intermediate data structure to be used from a list of options. Phoenix++ provides three types of intermediate data structure to choose from

Figure 2.7: Phoenix++ non-blocking shared array.

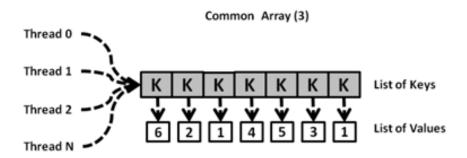

Common Array (1:1): a non-blocking array structure shared across all threads, as it is shown in Figure 2.7. The common array leverages the fact that each emitted key is unique and all threads can write into the same array without any synchronization.

Figure 2.8: Phoenix++ fixed-size thread-local array.

Array (\*:k): a fixed-size thread-local array implementation, as it is shown in Figure 2.8, which requires the keys to be integers within an a priori known range. For tasks with a known, small key cardinality, insertion into a fixed size array avoids the cost of hashing keys and repeatedly checking if the hash table should be resized. Provides an increase in performance in cases where there is a small computation per task.

Figure 2.9: Phoenix++ variable-width hash table.

Hash table (\*:\*):This is the main improvement from the previous Phoenix version with the objective to improve the search in large keys arrays. It is a variable-width hash table implementation where each map thread can resize its own hash table, as it is described in Figure 2.9. This ensures that insertion complexity is kept in the order of O(1) even in the presence of an unexpectedly large number of keys. With this structure, Phoenix must prevent the loss of correspondence between the number of keys of each row, which would make it difficult to group values of the same key, through the different threads. At the end of the Map phase all keys and values are copied to a fixed-size hash table, where the number of columns is the same as the number of reduce tasks to launch.

The use of distinct data structures to adjust the framework to each workload key distribution improves the efficiency of handling specific known applications. In those cases, the volume of data to be processed may not be necessarily large.

In addition to using different intermediate data structures Phoenix++ also has a combiner function that performs a local reduction per thread, after each key/value pair is emitted by the map function. The combiner function reduces the amount of memory required when having multiple values for the same key inside each Map task.

#### 2.2.3 Metis

Using Phoenix as a base, Metis[30] is an improved multi-core MapReduce framework. To increase the performance with most types of workloads, Metis makes use of three main strategies

The use of combiner function;

A new data structure to store intermediate key/values;

A key/value distribution prediction phase.

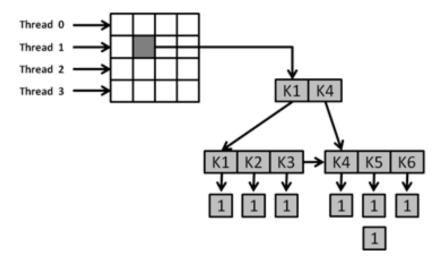

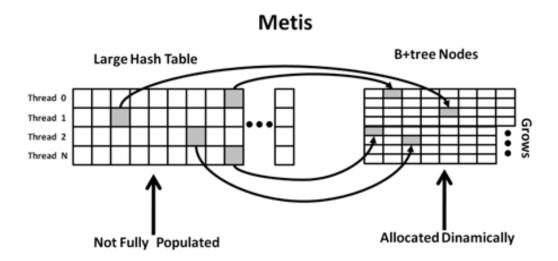

All Map workers have a hash table to store keys and values and use the same hash function to ensure a good distribution of keys throughout the hash table. To avoid competition between different threads on the same memory region, each thread has its own Hash-tree, which is represented by each row of the matrix shown in Figure 2.10.

Each hash table entry points to a B+tree to store keys and values. The idea is to achieve a theoretical O(1) search complexity accessing the hash table. Then, assuming N keys stored in each hash bucket, traversing the tree to find the key position has O(logN) complexity. If the key already exists, the worker adds a new value to the key list. If the key does not exist, then the new key is inserted into the tree.

Figure 2.10: Metis intermediate data structure.

Some types of workload, exhibit a homogeneous key distribution in the Map output. This predictability helps obtaining an approximate sizing of the intermediate data structure, providing an equal distribution of keys across the hash table. Metis uses a prediction phase to define the amount of entries in the hash table. The idea is to predict the total number

of distinct keys that a Map task can generate. Metis makes this prediction counting the total number of distinct keys issued over the first 10% of the input file, and extrapolating these results to the total execution.

Then, Metis allocates a hash table that is big enough to contain a certain average number of keys per hash entry. In this way, search and insert complexity remains bounded. By default, Metis tries to keep 10 distinct keys per hash entry.

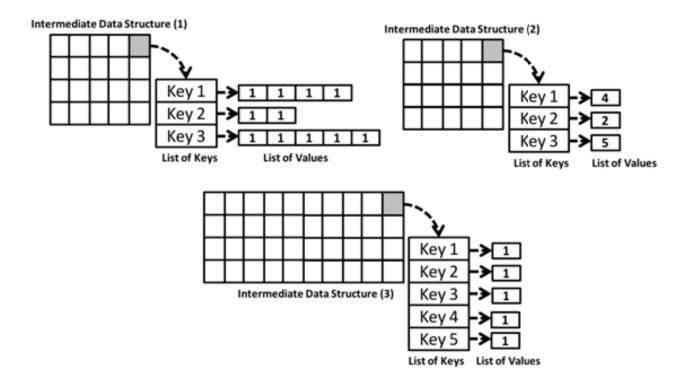

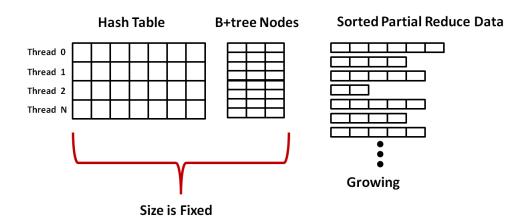

# 2.2.4 Comparing Multicore MapReduce Frameworks: Intermediate Data Structures

Generally, the different implementations of MapReduce work in the same way, following an execution timeline divided between Map and Reduce phases. In large collections of computers that form the clusters, the entire operation of communication between different phases is dominated by network performance. However, in multi-core MapReduce frameworks there is no actual communication between different phases as map and reduce tasks share the same intermediate data structure.

The big difference between distinct multi-core MapReduce frameworks is the data structure they implement and the way that they manage it. The management process needs to consider multiple factors in order to obtain acceptable performance on multi-core architectures.

Each Map task must avoid accessing the same positions when inserting keys and values, saving as much locking and cache contention costs as possible. An intermediate data structure must be able to maintain the keys sorted, allowing quick search and insertion, and accelerating the combination of equal keys. Different MapReduce applications pressure in different ways intermediate data structure. In this context the Map phase represents most of the insertion work on the intermediate data structure for processing the input data, producing and organizing keys. Also, Map tasks usually emit repeated keys in their own output, which makes it relatively important to the intermediate data structure the ability to perform a fast search for already existing keys.

The Reduce phase must consider all instances of a given key at the same time, grouping the output of different Map tasks. The Reduce tasks should generate an output organized with the objective of minimizing the cost of the Merge phase [30].

Comparing the current main implementations of MapReduce for multi-core architecture, Phoenix++ and Metis exhibit significant differences in the intermediate data structure used. Phoenix++ promotes the use of three adaptations of intermediate data structure on the same framework. The user becomes responsible for deciding what type of intermediate

data structure should be used. This procedure makes it necessary to know about the type of workload of the application.

The use of a hash table is attractive for workloads with many repeated keys. Phoenix++ chooses to use a resizable hash table to store map outputs. The use of this strategy requires Phoenix++ to make an extra copy between map and reduce phases, to retrieve the indices that allow reduce tasks process equal keys. Variable-width hash table allows the framework to avoid waste of main memory, since usually different Map workers may emit different sets of keys, ranging from many repeated keys to many different keys.

Metis uses in a different data structure, freeing the user from the responsibility to know the workload characteristics. Metis uses a hash table as well as Phoenix++. After the end of the prediction phase, Metis defines the hash table size that is shared by all workers. Instead of arrays, Metis uses B+ trees for each hash entry. The objective is to take advantage from the sorting of keys that the B+ tree provides, in addition to O(logN) complexity for insertion and search. Although the use of B+ trees is more attractive for workloads where there are many repeated keys, they can also store a certain number of distinct keys without sacrificing performance. The sorting of the keys in the B+ tree reduces the Merge phase execution time to make the final global sorting.

In summary, the Phoenix++ resize strategy adds some extra work to the framework, thereby increasing execution time. Metis gets better performance by using a more general intermediate data structure. However, the use of a prediction phase may end up compromising the use of resources, by generating a waste of memory.

## 2.2.5 Influence of Key Distribution

Understanding factors that affect positively or negatively MapReduce frameworks, provides an opportunity to optimize current strategies. In current multi-core MapReduce frameworks, a factor that affects performance is the key distribution.

Shared memory MapReduce performance is highly affected by the number of intermediate output key/value pairs relative to the number of distinct keys [43]. As can be seen in Figure 2.11 item 1 in accordance with a distribution key X, for each key in the key list, it was kept in memory a list of values. In this case the shared memory is affected by the number of keys, independently of the repetition of the keys. Using the combiner, which makes the reduction of keys per thread, repeated keys no longer cause major impact on the use of shared memory, as shown in Figure 2.11 item 2. However, in a key distribution which is predominately high the number of unique keys, shared memory performance is directly affected. Such a situation is caused because the combiner becomes useless, making the key list grow thus increasing the size of the intermediate data structure, as shown in

Figure 2.11 item 3.

Figure 2.11: MapReduce Framework Key Distribution.

On the other hand, the number of keys per hash entry is also an important factor in the performance of multi-core MapReduce frameworks. By the way that frameworks works, sharing main memory between different *Map* and *Reduce* tasks, all space allocated in main memory is important. When an area of main memory allocated does not have the amount of keys needed to cover the allocation cost, the framework is penalized in unnecessary memory usage, reduced spatial locality, and increasing the work of all the MapReduce framework phases.

Using as an example Metis[30], which by default tries to keep 10 keys trees in each hash entry, although the proximity of this value depends on the distribution through the hash table. The amount of keys per hash entry is an important parameter for Metis in the decision of the hash table size. If Metis[30] makes a prediction that a given input file contains 10 million of distinct keys, the number of columns required would be 1 million. In short, for a prediction of 10 million distinct keys in a environment with 2 threads running, it would create a table of 2 rows per 1 million columns. For the same input file with 10 million distinct keys, but in an environment with 24 threads it would be necessary a table of 24 rows per 1 million columns. This situation creates a waste of memory space, since

that the creation of a large table to ensure a memory space for each thread, allow the increase of empty hash entries. The increase in the number of empty hash entries also reflected in unnecessary work to the *Reduce* tasks, that must go through all the column reducing keys.

# Chapter 3

# Proposal of Virtual Memory Management

# 3.1 Challenges of Managing Large Data Sets in Multicore MapReduce Frameworks and Work Proposals

MapReduce is a paradigm that was designed to facilitate data parallel computing. Initially developed for cluster environments, MapReduce applications can also be executed in multi-core architectures by the use of specialized frameworks. One of the main proposals of MapReduce implementations is the storage of the intermediate data in a specific data structure

In cluster environments, the Map and Reduce tasks are usually executed in different machines and data communications between tasks are sent through the network. But compared to multi-core shared memory environments, the major performance bottlenecks processing for large MapReduce applications is the large memory requirements of shared data structures and its management.

We have already described how the current implementation strategy is to keep all input and intermediate data into memory during the entire execution. This makes necessary the use of a large amount of main memory of the system [7]. Large data sets usually have difficult to predict key-value distributions that generate very large intermediate data structures. In environments with limited amount of main memory, the whole performance of the application is affected by the unmanaged use of virtual memory and disk.

The intermediate data structures used by multi-core MapReduce frameworks are hash tables. Each of their entries points to a second data structure, where keys and values are

actually stored. The size of the hash table is normally set at the beginning of execution, while key-value buffers must grow to allocate map key and value outputs. There is an ideal hash table where each entry contains a similar number of keys and values so that search cost is evenly distributed. Structures where some entries are empty and others store many values should be avoided as they waste memory space.

The main reason to use a MapReduce framework in a multi-core environment is the possibility of executing concurrent map and reduce tasks using the available CPU cores. This promise of parallelism is compromised by the limitations of the data structure needed to store all intermediate data of all concurrent tasks. As each Map task will have its own hash table to insert its keys values without any task dependence the space needed grows linearly with the number of tasks.

For example, if a computing environment has just one thread per map task, the MapReduce framework would allocate space for a hash table with only one row, with a fixed number of N columns. If, for example, each map task generates a key-value set of 200 megabytes in main memory, now let's suppose that the same execution be done in an environment with 32 threads for 32 map tasks. The framework must distribute 32 main memory spaces, one for each thread in use. That means a hash table with 32 rows for the same fixed amount of N columns. In summary, memory needed makes a total of 6.4 gigabytes of main memory just to allocate space for the same workload used in the execution with just one thread as shown in Figure 3.1.

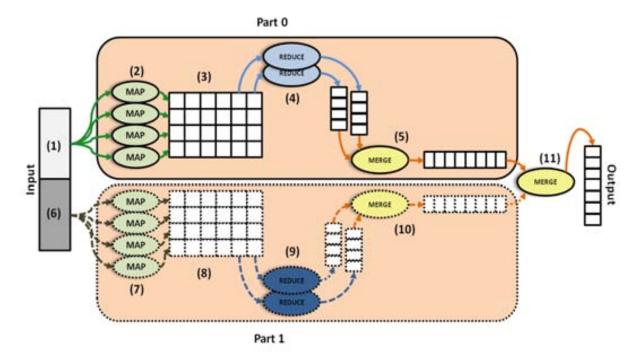

Figure 3.1: Growth of intermediate data structure depending on the parallelism.

In conclusion, current designs of MapReduce frameworks data structures do not scale well when dealing with large data set applications using a large number of threads.

When a Map task, in its key-value insertion process, runs out of main memory the framework relies on the operating system to create a paging file in the hard disk, starting

the use of virtual memory. Framework disk usage through virtual memory is not different from main memory. That is, Map tasks request scattered memory references to different hash entries actually mapped in the disk. As the disk latency can be a hundred times slower than main memory, the performance is dramatically decreased.

## 3.2 Memory Management Proposals

In this section we present the main objectives of our proposal to improve the performance multi-core MapReduce frameworks. During the execution time, the frameworks control the flow of the application. Then, they are responsible of managing the use of resources. Any improvement in the performance of the frameworks affects directly the whole application execution times.

Initially multi-core MapReduce frameworks have been developed for applications which data fits in main memory[23]. When data sets grow bigger than the available memory available, frameworks should consider strategies to manage the extra space needed. Dealing with large data sets requires framework environments to be prepared to manage their needs. Multi-core environments deal with a limited static amount of resources and more demanding memory needs are not easily solved by adding more nodes to the system.

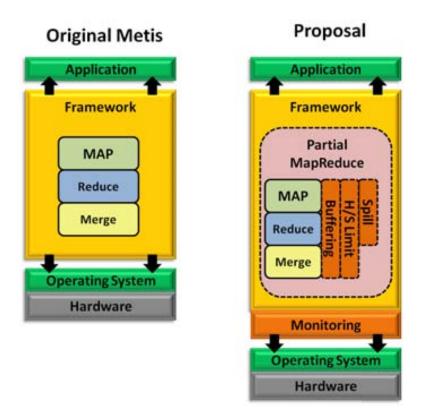

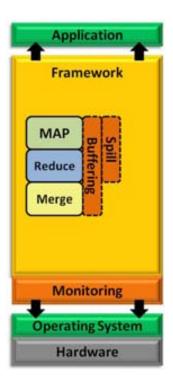

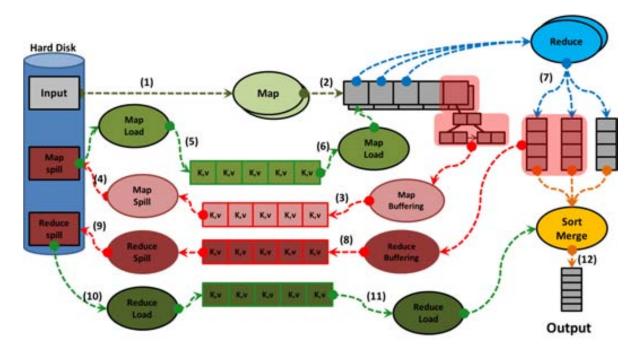

In order to solve the problems presented in multi-core MapReduce frameworks, we designed and implemented a solution that manages, handles and stores keys and values in a more efficient intermediate data structure.

Our proposal objective is to improve the intermediate data structure memory management to be able to accept an indeterminate large number of key-values. We propose to use a mechanism to monitor the memory needs of the MapReduce application. We present a spilling subsystem to save the memory data structure to disk without affecting the performance of the application. Finally, we also add a mechanism to manage the concurrent access to disk by several concurrent threads.