# Evaluating techniques for parallelization tuning in MPI, OmpSs and MPI/OmpSs

Author: Vladimir Suвотіć Advisors:

Prof. Jesús Labarta

Prof. Mateo Valero

Prof. Eduard Ayguadé

A THESIS SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF **Doctor per la Universitat Politècnica de Catalunya** Departament d'Arquitectura de Computadors Barcelona, 2013

### **Abstract**

Parallel programming is used to partition a computational problem among multiple processing units and to define how they interact (communicate and synchronize) in order to guarantee the correct result. The performance that is achieved when executing the parallel program on a parallel architecture is usually far from the optimal: computation unbalance and excessive interaction among processing units often cause lost cycles, reducing the efficiency of parallel computation.

In this thesis we propose techniques oriented to better exploit parallelism in parallel applications, with especial emphasis in techniques that increase asynchronism. Theoretically, this type of parallelization tuning promises multiple benefits. First, it should mitigate communication and synchronization delays, thus increasing the overall performance. Furthermore, parallelization tuning should expose additional parallelism and therefore increase the scalability of execution. Finally, increased asynchronism would allow more flexible communication mechanisms, providing higher tolerance to slower networks and external noise.

In the first part of this thesis, we study the potential for tuning MPI parallelism. More specifically, we explore automatic techniques to overlap communication and computation. We propose a speculative messaging technique that increases the overlap and requires no changes of the original MPI application. Our technique automatically identifies the application's MPI activity and reinterprets that activity using optimally placed non-blocking MPI requests. We demonstrate that this overlapping technique increases the asynchronism of MPI messages, maximizing the overlap, and consequently leading to execution speedup and higher tolerance to bandwidth reduction. However, in the case of realistic scientific workloads, we show that the overlapping potential is significantly limited by the pattern by which each MPI process locally operates on MPI messages.

In the second part of this thesis, we study the potential for tuning hybrid MPI/OmpSs applications. We try to gain a better understanding of the parallelism of hybrid MPI/OmpSs applications in order to evaluate how these applications would execute on future machines and to predict the execution bottlenecks that are likely to emerge. We explore how MPI/OmpSs

applications could scale on the parallel machine with hundreds of cores per node. Furthermore, we investigate how this high parallelism within each node would reflect on the constraints of the interconnect. We especially focus on identifying critical code sections in MPI/OmpSs. We devised a technique that quickly evaluates, for a given MPI/OmpSs application and the selected target machine, which code section should be optimized in order to gain the highest performance benefits.

Also, this thesis studies techniques to quickly explore the potential OmpSs parallelism inherent in applications. We provide mechanisms for the programmer to easily evaluate potential parallelism of any task decomposition. Furthermore, we describe an iterative trial-and-error approach to search for a task decomposition that will expose sufficient parallelism for a given target machine. Finally, we explore potential of automating the iterative approach by capturing the programmers' experience into an expert system that can autonomously lead the process of finding efficient task decompositions.

Also, throughout the work on this thesis, we designed development tools that can be useful to other researchers in the field. The most advanced of these tools is Tareador – a tool to help porting MPI applications to MPI/OmpSs programming model. Tareador provides a simple interface to propose some decomposition of a code into OmpSs tasks. Then, based on the proposed decomposition, Tareador dynamically calculates data dependencies among the annotated tasks, and automatically estimates the potential OmpSs parallelization. Furthermore, Tareador gives additional hints on how to complete the process of porting the application to OmpSs. Tareador already proved itself useful, by being included in the academic classes on parallel programming at UPC.

## Acknowledgement

On January 12<sup>th</sup> 2007, I started my Ph.D. studies at the UPC. In the first two hours of "sitting in front of computer", I managed to format my Linux partition. Today, I'm about to defend my doctorate in computer science. I'm not the same guy from my first day, both personally and professionally. Many people helped me on my way. I owe them many thanks.

I'm very thankful to Jesus, who taught me to be methodological and direct – I would say a brutal engineer.

I'm thankful to Mateo, whose encouragement and support I knew to recognize and appreciate fully always with a significant delay.

I must thank Edu for "adopting" me close to the end of my studies and helping me finish my Ph.D. in a surprisingly good mood.

I'm thankful to Jose Carlos, who enormously helped me writing papers.

Also, I wish to thank my numerous colleagues from Barcelona Supercomputing Center who shared with me their working and non-working hours and made my Ph.D. time both more productive and enjoyable. I must pick out Saša and Srdjan, who showed me many tricks of the trade. And, I would like to specially mention Uri Prat, a big guy who had amazing patience with me, even in the days when I was a technical idiot.

Finally, this thesis would not be possible without my girlfriend Jelena. She has stuck with me through thick and thin.

### Errata

My graduate work has been financially supported by the following projects:

- Computacion de altas prestaciones V (TIN2007-60625).

- TEXT Towards EXaflop applicaTions. EU Commission, Information Society Technologies, IST-2007-261580.

- BSC-IBM MareIncognito project. IBM Research.

- Intel-BSC Exascale Lab. Intel Corporation.

Also, throughout my Ph.D. studies, I was receiving a grant from Barcelona Supercomputing Center.

# Contents

| A  | cknov   | vledgem       | ient                               | IV  |

|----|---------|---------------|------------------------------------|-----|

| C  | onten   | ts            |                                    | vi  |

| Li | st of l | Figures       |                                    | X   |

| Li | st of ' | <b>Fables</b> |                                    | xiv |

| 1  | Intr    | oductio       | o <b>n</b>                         | 1   |

|    | 1.1     | Goals         |                                    | 2   |

|    | 1.2     | Appro         | ach                                | 3   |

|    | 1.3     | Contri        | butions                            | 4   |

|    | 1.4     | Docum         | ment structure                     | 6   |

| 2  | Bac     | kground       | d                                  | 8   |

|    | 2.1     | Paralle       | el machines                        | 9   |

|    |         | 2.1.1         | Processor architecture trends      | 9   |

|    |         | 2.1.2         | Memory Organization                | 11  |

|    |         | 2.1.3         | Message Passing Cost               | 14  |

|    | 2.2     | Paralle       | el programming models              | 15  |

|    |         | 2.2.1         | MPI                                | 16  |

|    |         | 2.2.2         | OpenMP                             | 22  |

|    |         | 2.2.3         | OmpSs                              | 27  |

|    |         | 2.2.4         | Example - MPI/OmpSs vs. MPI/OpenMP | 33  |

|    | 2.3     | Tools .       |                                    | 35  |

|   |       | 2.3.1    | mpitrace                                                        | 36         |

|---|-------|----------|-----------------------------------------------------------------|------------|

|   |       | 2.3.2    | Valgrind                                                        | 36         |

|   |       | 2.3.3    | Paraver                                                         | 37         |

|   |       | 2.3.4    | Dimemas                                                         | 37         |

| 3 | Mot   | ivation  |                                                                 | 39         |

|   | 3.1   | MPI p    | rogramming                                                      | 39         |

|   |       | 3.1.1    | Bulk-synchronous programming                                    | 40         |

|   |       | 3.1.2    | Communication Computation Overlap                               | 41         |

|   | 3.2   | Our ef   | fort in tuning MPI parallelism                                  | 42         |

|   |       | 3.2.1    | Automatic overlap                                               | 43         |

|   | 3.3   | MPI/C    | OmpSs programming                                               | 45         |

|   |       | 3.3.1    | Hiding communication delays                                     | 45         |

|   |       | 3.3.2    | Additional parallelism within an MPI process                    | 47         |

|   | 3.4   | Our ef   | fort in tuning MPI/OmpSs parallelism                            | 48         |

|   |       | 3.4.1    | Identifying parallelization bottlenecks                         | 49         |

|   |       | 3.4.2    | Searching for the optimal task decomposition                    | 50         |

| 4 | Infr  | astructi | ure                                                             | 51         |

|   | 4.1   | Simula   | ation aware tracing                                             | 52         |

|   |       | 4.1.1    | Illustration of the methodology                                 | 53         |

|   | 4.2   | Frame    | work to identify potential overlap                              | 54         |

|   |       | 4.2.1    | Implementation details                                          | 56         |

|   | 4.3   | Frame    | work to replay MPI/OmpSs execution                              | 59         |

|   |       | 4.3.1    | Implementation details                                          | 61         |

|   | 4.4   | Taread   | or – Framework to identify potential dataflow parallelism       | 64         |

|   |       | 4.4.1    | Implementation details                                          | 65         |

|   |       | 4.4.2    | Usage of Tareador                                               | 69         |

| 5 | Ove   | rlappin  | g communication and computation in MPI scientific applica-      |            |

|   | tions |          | -                                                               | <b>7</b> 0 |

|   | 5.1   | Charac   | eteristic application behaviors                                 | 71         |

|   | 5.2   | Autom    | natic Communication-Computation Overlap at the MPI Level        | 73         |

|   |       | 521      | Automatic overlan applied on the three characteristic behaviors | 75         |

|   | 5.3  | Specu   | lative Dataflow – A proposal to achieve automatic overlap        | 77     |

|---|------|---------|------------------------------------------------------------------|--------|

|   |      | 5.3.1   | Protocol of speculative dataflow                                 | 77     |

|   |      | 5.3.2   | Emulation                                                        | 78     |

|   |      | 5.3.3   | Hardware support                                                 | 83     |

|   |      | 5.3.4   | Conclusions and future research directions                       | 83     |

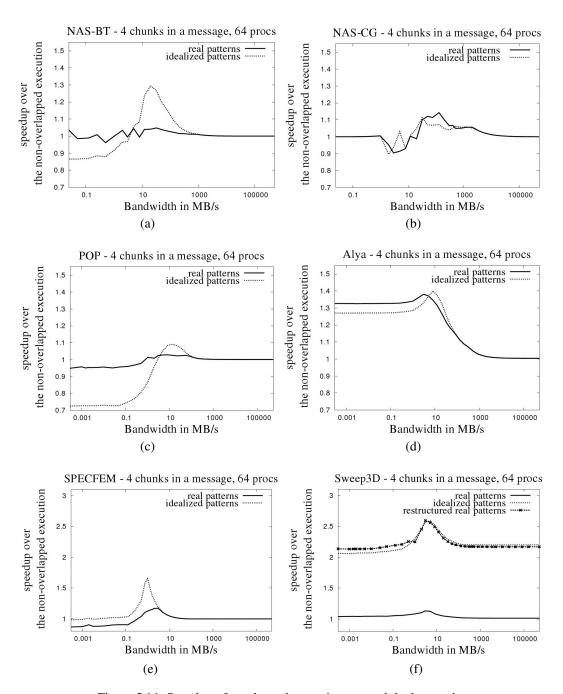

|   | 5.4  | Quant   | ifying the potential benefits of automatic overlap               | 84     |

|   |      | 5.4.1   | Experimental Setup                                               | 85     |

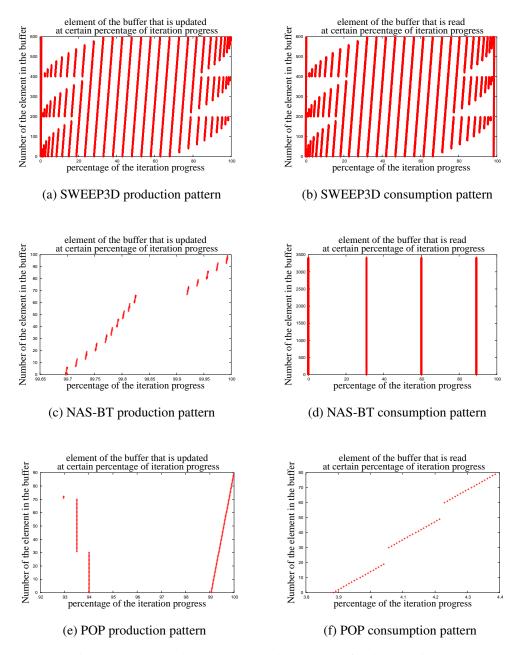

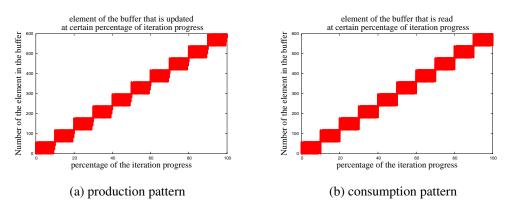

|   |      | 5.4.2   | Patterns of production and consumption                           | 85     |

|   |      | 5.4.3   | Simulating potential overlap                                     | 91     |

|   |      | 5.4.4   | Conclusions and future research directions                       | 102    |

| 6 | Tasl | k-based | dataflow parallelism                                             | 104    |

|   | 6.1  | Identii | fying critical code sections in dataflow parallel execution      | 105    |

|   |      | 6.1.1   | Motivation                                                       | 106    |

|   |      | 6.1.2   | Motivation example interpreted by the state-of-the-art technique | es 108 |

|   |      | 6.1.3   | Experiments                                                      | 110    |

|   |      | 6.1.4   | Conclusion and future research directions                        | 118    |

|   | 6.2  | Tareac  | lor: exploring parallelism inherit in applications               | 119    |

|   |      | 6.2.1   | Motivating example                                               | 120    |

|   |      | 6.2.2   | Experiments                                                      | 121    |

|   |      | 6.2.3   | Conclusion and future research directions                        | 129    |

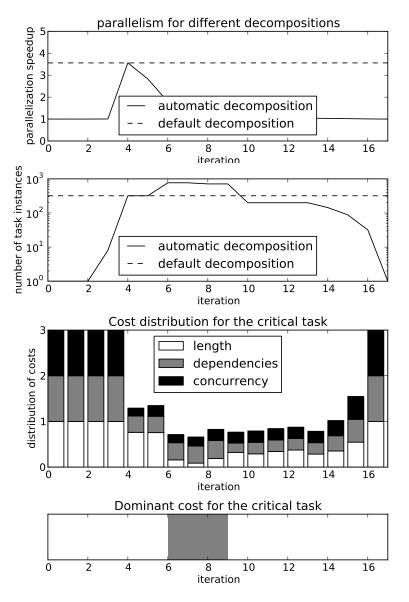

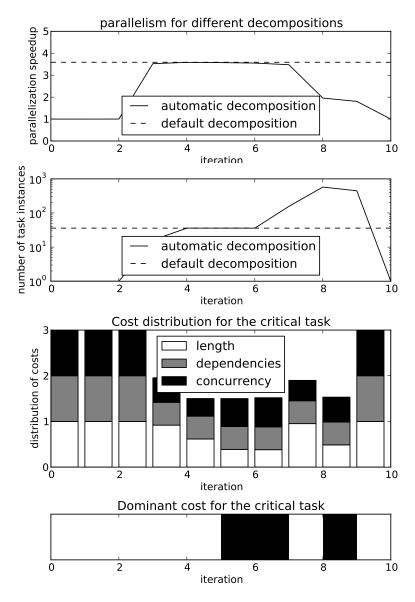

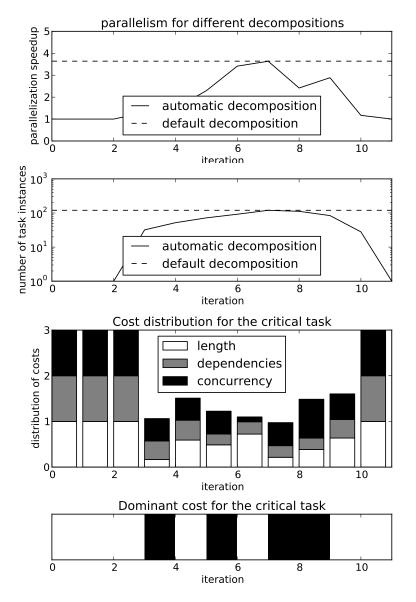

|   | 6.3  | Auton   | natic exploration of potential parallelism                       | 130    |

|   |      | 6.3.1   | The search algorithm                                             | 131    |

|   |      | 6.3.2   | Heuristic 2: When to stop refining the decomposition             | 135    |

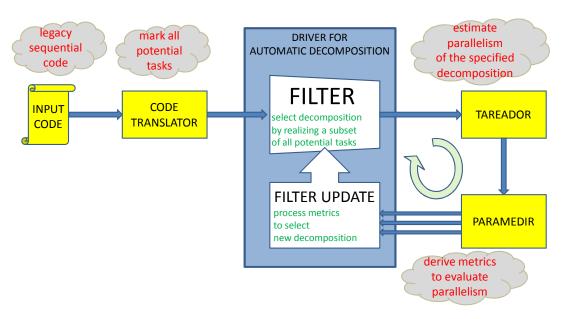

|   |      | 6.3.3   | Working environment                                              | 136    |

|   |      | 6.3.4   | Experiments                                                      | 138    |

|   |      | 6.3.5   | Conclusion                                                       | 146    |

| 7 | Rela | ated Wo | ork                                                              | 147    |

|   | 7.1  | Simul   | ation methodologies for parallel computing                       | 147    |

|   | 7.2  | Overla  | apping communication and computation                             | 149    |

|   | 7.3  | Identif | fying parallelization bottlenecks                                | 150    |

|   | 74   | Paralle | elization development tools                                      | 152    |

### **CONTENTS**

| 8  | Con   | clusion  |                                   | 155 |

|----|-------|----------|-----------------------------------|-----|

|    | 8.1   | Future   | work                              | 157 |

|    |       | 8.1.1    | Parallelism for everyone: my view | 158 |

| 9  | Pub   | lication | s                                 | 161 |

| Bi | bliog | raphy    |                                   | 164 |

# List of Figures

| 2.1  | The evolution of computing platforms. Chart originally from SPIRAL  |    |

|------|---------------------------------------------------------------------|----|

|      | project website [72]                                                | 10 |

| 2.2  | Example MPI code                                                    | 18 |

| 2.3  | Execution of the example MPI code                                   | 19 |

| 2.4  | simple OpenMP code                                                  | 24 |

| 2.5  | simple OpenMP code                                                  | 24 |

| 2.6  | Pointer chasing application parallelized with OpenMP                | 26 |

| 2.7  | Porting sequential C to OmpSs                                       | 28 |

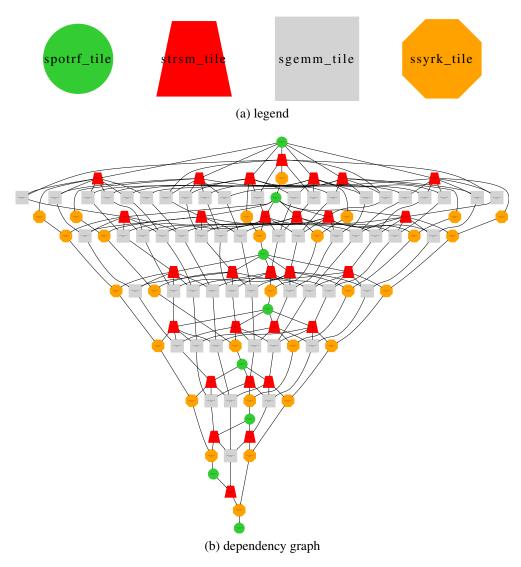

| 2.8  | OmpSs implementation of Cholesky                                    | 31 |

| 2.9  | Dependency graph of Cholesky                                        | 32 |

| 2.10 | Simple MPI code to study potential lookahead                        | 34 |

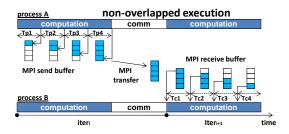

| 3.1  | The case of nonoverlapped MPI                                       | 42 |

| 3.2  | The case of overlapped MPI                                          | 42 |

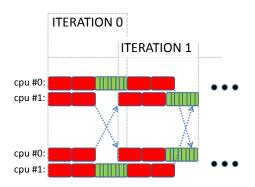

| 3.3  | Overlap with chunks                                                 | 43 |

| 3.4  | Example of nonoverlapped MPI                                        | 46 |

| 3.5  | Example of overlapped MPI/OmpSs                                     | 46 |

| 3.6  | MPI/OmpSs execution with multiple cores per MPI process             | 48 |

| 4.1  | Simulating different implementations of broadcast                   | 53 |

| 4.2  | The framework for studying overlap integrates Valgrind, Dimemas,    |    |

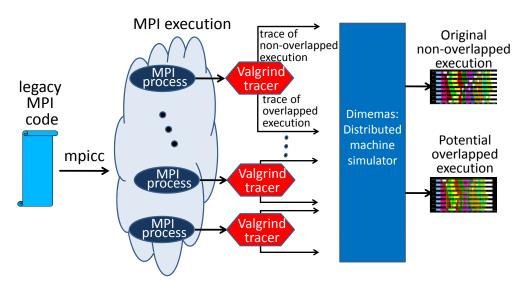

|      | and Paraver.                                                        | 56 |

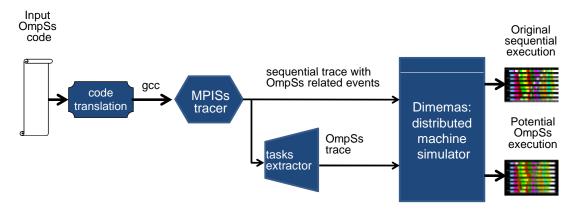

| 4.3  | The environment integrates Mercurium code translator, MPISS tracer, |    |

|      | tasks extractor, Dimemas simulator and Paraver visualization tool   | 61 |

| 4.4  | The code translation inserts functions that signal OmpSs pragma an-    |     |

|------|------------------------------------------------------------------------|-----|

|      | notations                                                              | 62  |

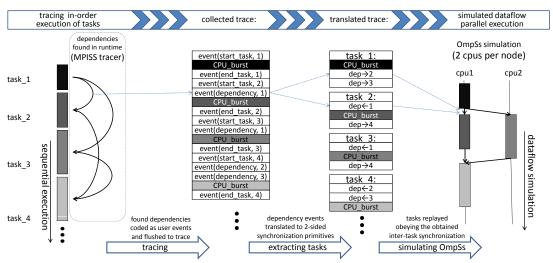

| 4.5  | Environment methodology                                                | 64  |

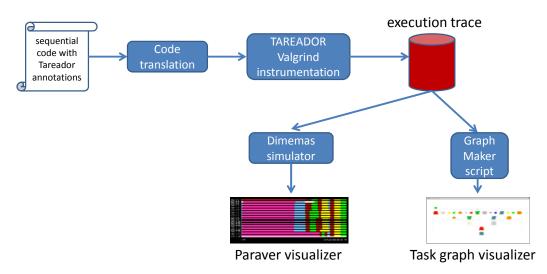

| 4.6  | The Tareador framework integrates Mercurium code translator, Val-      |     |

|      | grind tracer, Dimemas simulator, Paraver and dependency graph visu-    |     |

|      | alization tool                                                         | 65  |

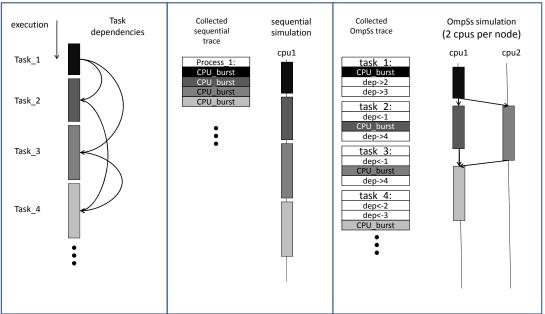

| 4.7  | Translation of the input code required by the framework                | 67  |

| 4.8  | Collecting trace of the original sequential and the potential OmpSs    |     |

|      | execution                                                              | 68  |

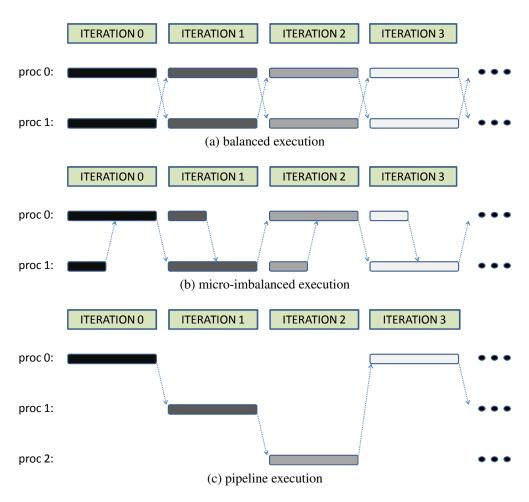

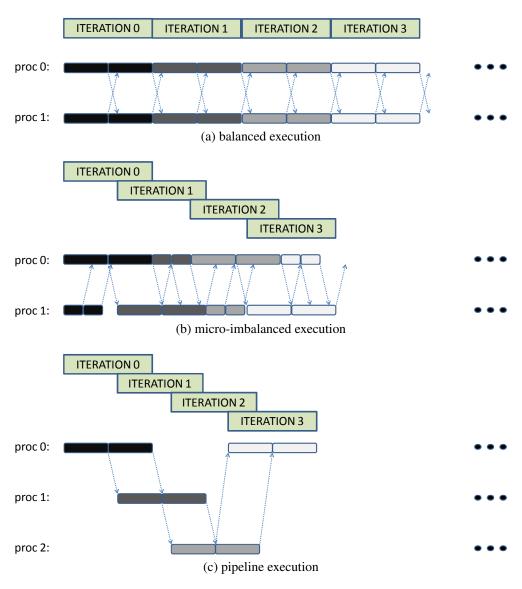

| 5.1  | Three characteristic MPI behaviors that suffer from lack of overlap    | 72  |

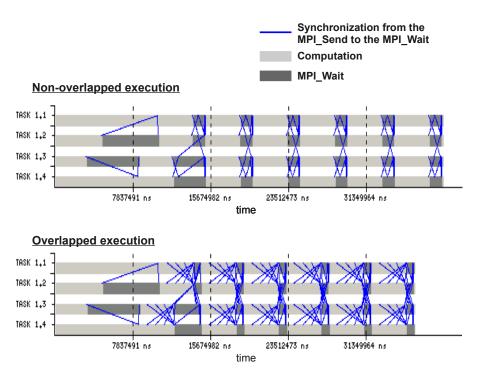

| 5.2  | Non-overlapped execution                                               | 74  |

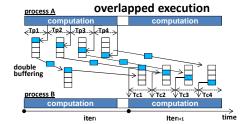

| 5.3  | Overlapped execution                                                   | 74  |

| 5.4  | Three characteristic behaviors with chunked overlap                    | 75  |

| 5.5  | Software mock-up for the evaluation                                    | 79  |

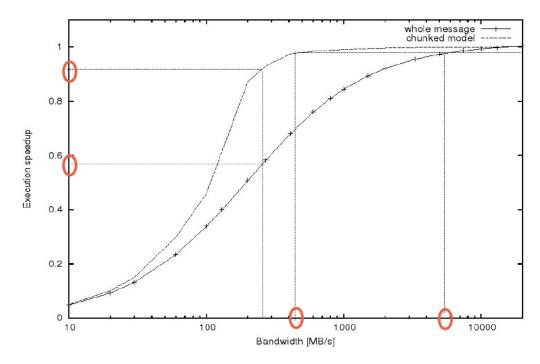

| 5.6  | Influence of the network bandwidth on execution time                   | 80  |

| 5.7  | Bandwidth usage for the link bandwidth of 2.5GB/s                      | 81  |

| 5.8  | Bandwidth usage for the link bandwidth of 250MB/s                      | 81  |

| 5.9  | Trace of a micro-imbalanced application                                | 82  |

| 5.10 | Overlapping in pipeline executions                                     | 82  |

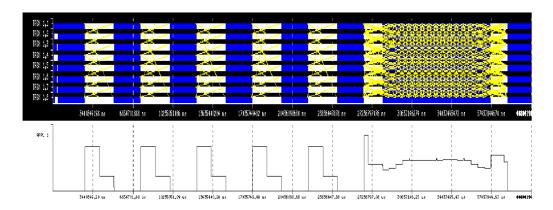

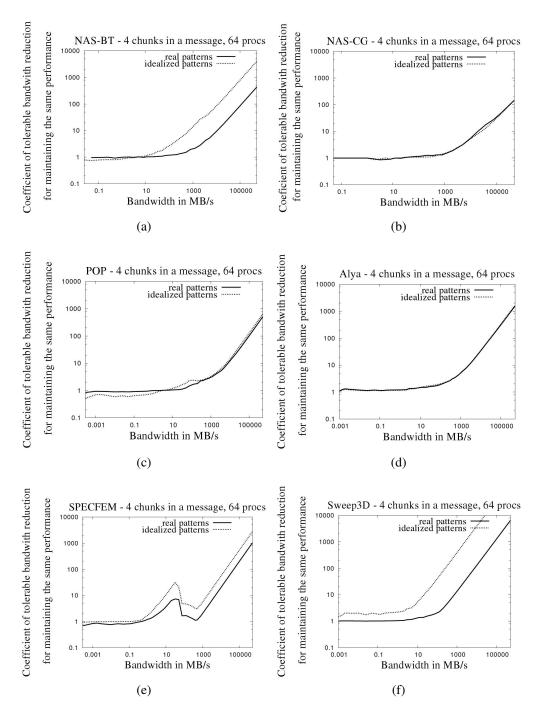

| 5.11 | Production and consumption patterns of various applications            | 87  |

| 5.12 | Production and consumption patterns of the restructured Sweep3D        | 91  |

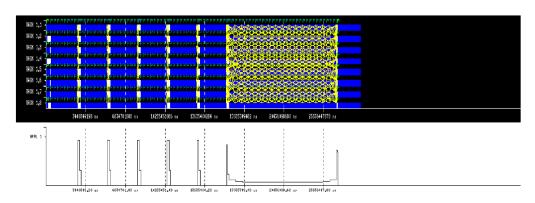

| 5.13 | Paraver visualization for the non-overlapped and overlapped execu-     |     |

|      | tions of NAS-CG                                                        | 93  |

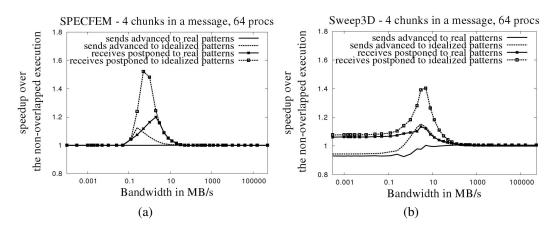

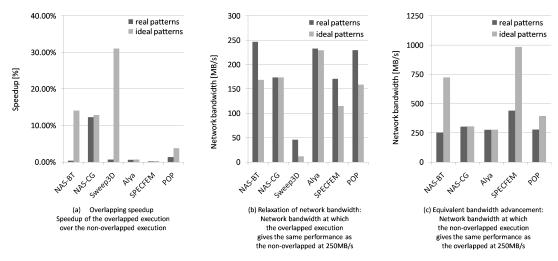

| 5.14 | Speedup of overlapped execution over original execution                | 94  |

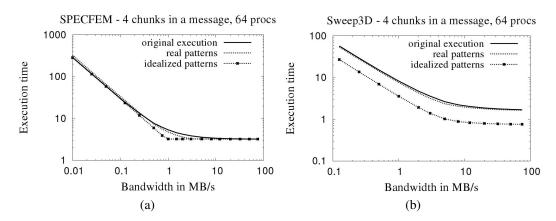

| 5.15 | Execution time for original and overlapped (real and ideal patterns)   |     |

|      | execution                                                              | 97  |

| 5.16 | Factor of bandwidth reduction for which the overlapped execution main- |     |

|      | tains the performance of the original execution on full bandwidth      | 98  |

| 5.17 | Benefit of only advancing sends or only postponing receives            | 100 |

| 5.18 | Simulation of the overlapped executions on the real and ideal produc-  |     |

|      | tion/consumption patterns                                              | 101 |

| 6.1  | Code of the motivating example                                         | 107 |

| 6.2  | Data-dependency graph of the motivating example                          | 108 |

|------|--------------------------------------------------------------------------|-----|

| 6.3  | The resulting speedup when accelerating different tasks                  | 109 |

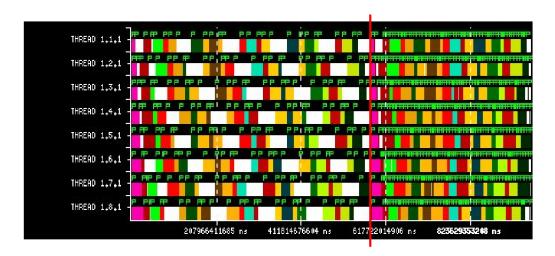

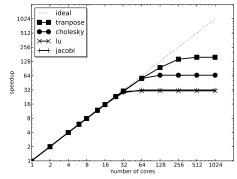

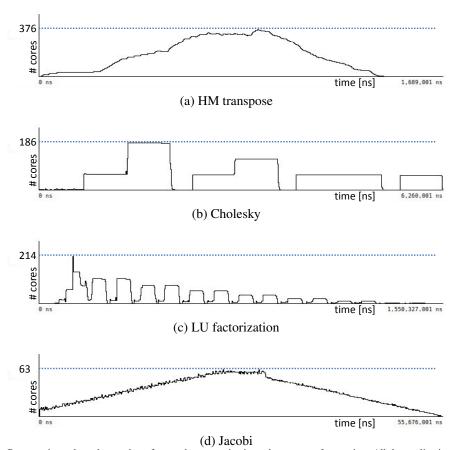

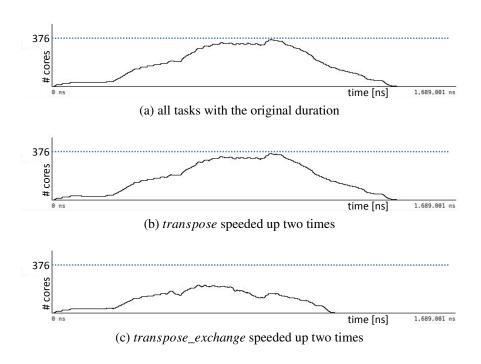

| 6.4  | Parallelism of OmpSs applications                                        | 111 |

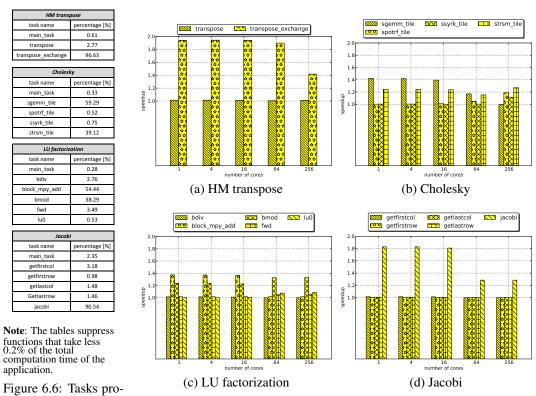

| 6.5  | Number of cores active during execution                                  | 112 |

| 6.6  | Tasks profile                                                            | 113 |

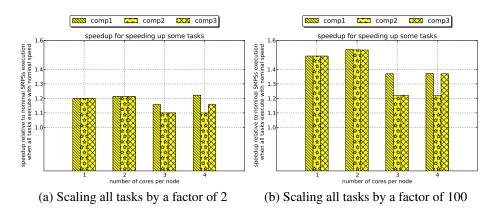

| 6.7  | Speedup when one task is speeded up by 2x (OmpSs codes)                  | 113 |

| 6.8  | HM transpose: number of active cores                                     | 114 |

| 6.9  | LU factorization: number of active cores                                 | 114 |

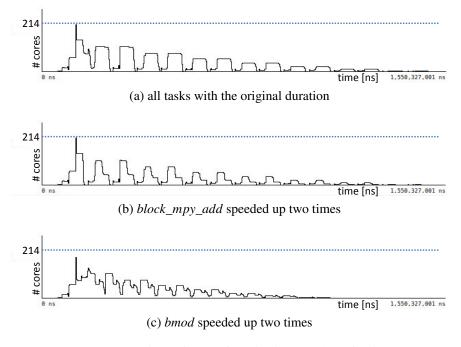

| 6.10 | Parallelism of MPI/OmpSs applications                                    | 116 |

| 6.11 | Tasks profile                                                            | 117 |

| 6.12 | Speedup when one task is speeded up by 2x (MPI/OmpSs codes)              | 117 |

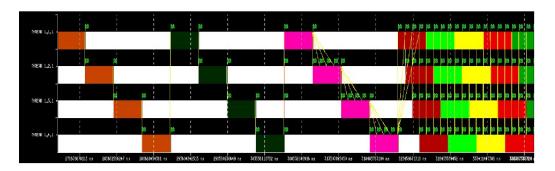

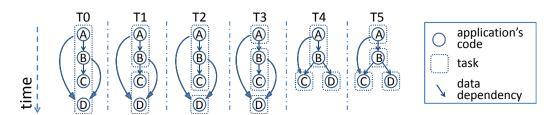

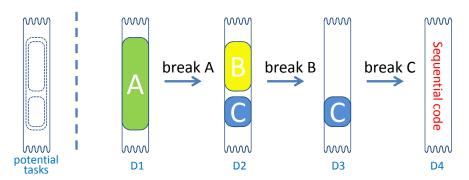

| 6.13 | Execution of different possible taskifications for a code composed of    |     |

|      | four parts                                                               | 120 |

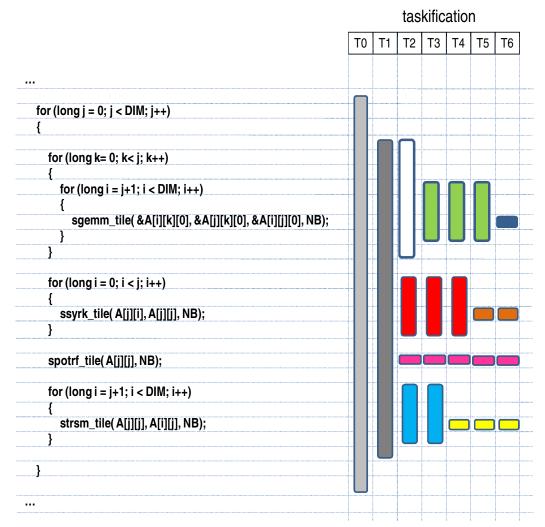

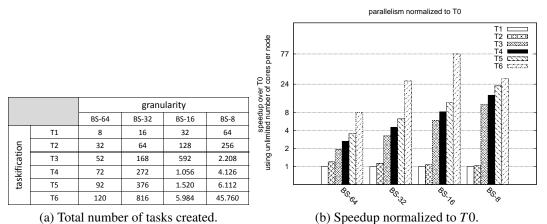

| 6.14 | Exploring potential decomposition of Cholesky code                       | 123 |

| 6.15 | Number of task instances and the potential parallelism for various task- |     |

|      | ifications of Cholesky                                                   | 124 |

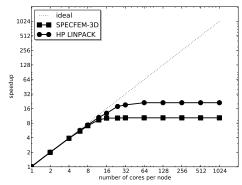

| 6.16 | Speedup and parallel efficiency for $T6$ for various number of cores     | 125 |

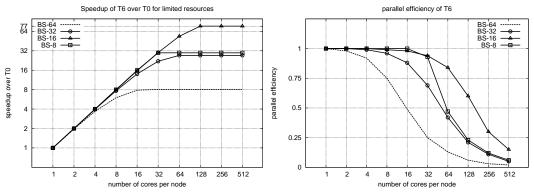

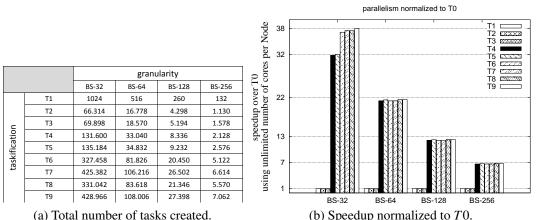

| 6.17 | Exploring task decompositions of HP Linpack                              | 126 |

| 6.18 | Number of task instances and the potential parallelism of each taskifi-  |     |

|      | cation                                                                   | 127 |

| 6.19 | Paraver visualization of the first 63 tasks and the dependencies among   |     |

|      | them (taskification T4, BS=256)                                          | 128 |

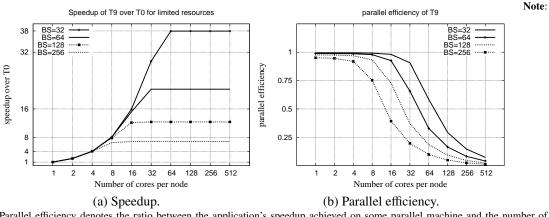

| 6.20 | Speedup and parallel efficiency for T9 for various number of cores       | 129 |

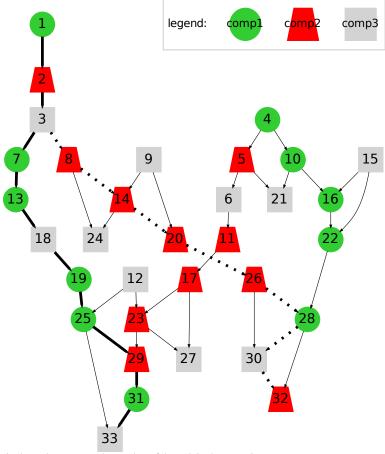

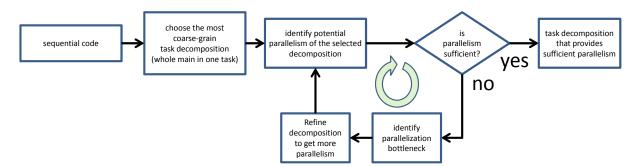

| 6.21 | Algorithm for exploring possible task decompositions                     | 131 |

| 6.22 | Iterative refinement of decompositions                                   | 132 |

| 6.23 | The environment that automatically explores possible task decomposi-     |     |

|      | tionss                                                                   | 136 |

| 6.24 | Code translation for automatic task decomposition                        | 137 |

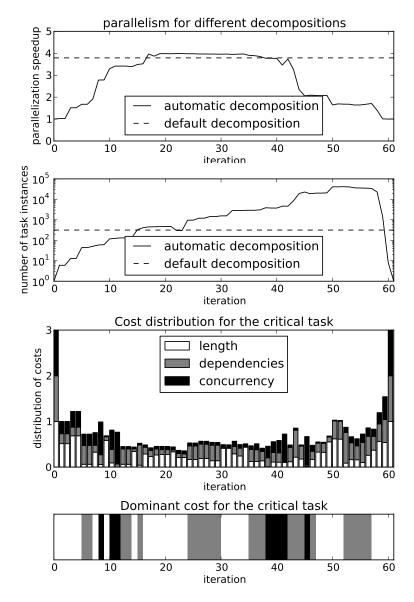

| 6.25 | Jacobi on 4 cores                                                        | 140 |

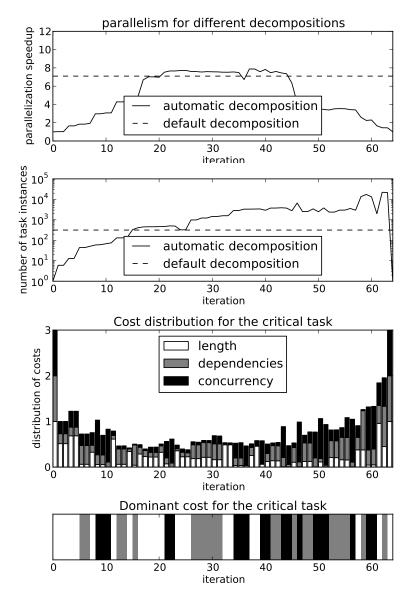

| 6.26 | HM transpose on 4 cores                                                  | 141 |

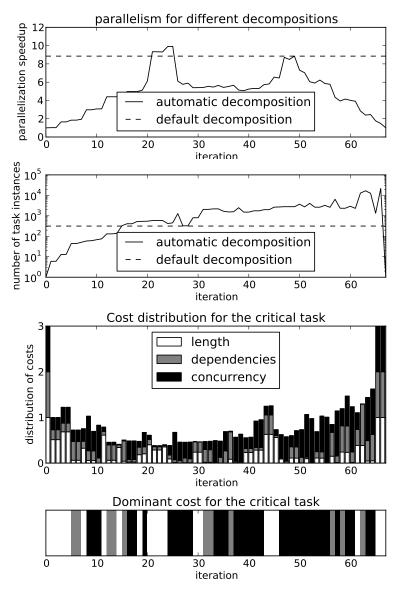

| 6.27 | Cholesky on 4 cores                                                      | 142 |

| 6.28 | Sparse LU on 4 cores                                                     | 143 |

| 6.29 | Sparse LU on 8 cores                                                     | 144 |

|   | -            |    |   | _ | -   |   | _ |   | _ |

|---|--------------|----|---|---|-----|---|---|---|---|

|   | <b>1 3 1</b> | ГО | _ | ы | 112 |   | u | - | 4 |

| _ |              | _  |   |   | u   | u |   | _ |   |

| 6 30 | Sparse LU on 16 cores |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 14 | 15 |

|------|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|---|---|---|---|---|----|----|

| 0.50 | Sparse Lo on 10 cores | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | <br> | • | • | • | • | • | 1- | T. |

# List of Tables

| 5.1 | Average patterns of production and consumption               | 89  |

|-----|--------------------------------------------------------------|-----|

| 5.2 | Number of network buses used in Dimemas for each application | 101 |

| 6.1 | Speedup for different number of cores                        | 108 |

# Introduction

Technological evolution demands increasing amounts of computational power and causes appearance of brand new large-scale parallel machines. Today, virtually all science and engineering is based on high-accuracy numerical simulations. These simulations are extremely computation-intensive programs. In order to finish the computation in limited time, these programs must execute in parallel. Therefore, parallel processing is becoming an indispensable part of modern science.

However, it is very hard to make a parallel machine work efficiently. As the number of processors in a system grows to hundreds and beyond, organizing inter-processor communication becomes a very important issue. In such large systems, inefficient communication and synchronization can introduce long execution stalls. These stalls prevent the processors from computing useful work and seriously harm performance.

In order to eliminate processor stalls, the computer architect's community tries to accelerate communication and synchronization mechanisms by investing more in interconnects. Hardware vendors constantly deliver more powerful networks. These networks constantly advance technological parameters, providing higher bandwidth

and lower latency. As a result of this trend, the cost of the interconnect is becoming a significant share in the total cost of these parallel machines [32]. Moreover, the trend of the Top 500 list [87] forecasts that the share of the interconnect in both power and cost of the whole system will be increasing.

Therefore, the trend of simply improving technological parameters of interconnects, and paying for those improvements, becomes economically unsustainable. Many recent studies show that, in High Performance Computing (HPC), interconnection networks are over-designed and yet underutilized [35]. Also, despite their increasing cost, new high-end interconnects deliver just a slight improvement in the overall performance. Thus, the community must optimize the utilization of network resources. Rather than trying to create new, faster and lately very expensive cycles in the network, the community must learn how to profit more from the already existing cycles.

To tackle the issue of under-utilization of parallel systems, in this thesis we explore techniques for parallelization tuning. We especially target techniques that increase asynchronism in parallel execution. Theoretically, this type of parallelization tuning promises multiple benefits. First, it should mitigate communication and synchronization delays, thus increasing the overall performance. Furthermore, parallelization tuning should expose additional parallelism and therefore increase the scalability of execution. Finally, increased asynchronism would allow more flexible communication mechanisms, providing higher tolerance to slower networks, as well as to external noise.

### 1.1 Goals

The major goal of this thesis is to explore techniques for parallelization tuning in MPI and MPI/OmpSs. In studying MPI execution, we evaluate automatic techniques for hiding communication delays. We explore techniques that can automatically overlap communication and computation, without the need to refactor the original legacy MPI code. Furthermore, we explore techniques for optimizing MPI/OmpSs execution. We specially focus on pinpointing bottlenecks of MPI/OmpSs execution. Also, we explore how MPI/OmpSs execution can be improved by changing the task decomposition of the code.

Also, throughout the work on this thesis, we strove to produce a useful development

infrastructure that can be used by both research and industry. Nowadays, very few people can efficiently program in parallel [38, 49]. However, as the existing hardware becomes increasingly parallel, parallel programming will inevitably become mainstream. Therefore, this thesis also aims to produce new development environments that can further increase the overall understanding of parallelism. We hope that our development environments can facilitate the adoption of parallel programming, especially the MPI/OmpSs programming model.

### 1.2 Approach

The experimental part of this thesis is based on trace-driven simulation. Initially, our study targets parallelization tuning of MPI execution. However, simulating MPI execution is a very hard problem. The simulation must process high number of separate MPI processes that among themselves communicate, synchronize and share resources (e.g. interconnection network). Thus, simulators of MPI execution are very computation-intensive and hard to parallelize. Our experience tells us that the mainstream solution for simulating MPI execution is a trace-driven simulation at a high level of abstraction.

We customize the conventional trace-driven methodology, by migrating the feature modeling effort from the simulation phase to the tracing phase. In the conventional trace-driven simulation, modeling a new feature is done in the simulation phase. The tracer instruments the application and collects the trace of the run. Then, the simulator replays the collected trace to reconstruct the time-behavior of the studied application on a parallel machine. When testing a new feature, the developer must extend the simulator in order to incorporate the effects of the inspected feature into the resulting time-behavior. On the other hand, in this thesis, we design a novel simulation methodology in which modeling a new feature is done in the tracing phase. In our simulation approach, we extend the tracer in order to introduce the effects of the inspected feature already into the collected trace. Then, the unchanged simulator can replay the collected trace and propagate the effect of the modeled feature throughout the simulated parallel execution.

Our methodology allowed us to simulate effects of low-level features in large-scale systems. Our approach stresses the tracing part of the simulation, by moving the feature modeling effort into this phase. Since each MPI process is traced concurrently,

the intensive computation for feature modeling is naturally parallelized across all MPI processes. This parallelization of feature modeling computation allowed us to build very powerful environments. In many developed tools, we implement tracers based on binary translation environments. These tracers instrument execution at the level of a single instruction and model very low-level features. On the other hand, an unchanged MPI simulator propagates the effects of the modeled feature throughout a very large-scale parallel machine.

Based on the presented methodology, we created new useful development environments. More specifically, we designed three development environments. The first environment automatically evaluates the potential of communication/computation overlap in MPI applications. The second environment extends the legacy MPI replaying toolchain (mpitrace, Dimemas) into a new MPI/OmpSs replaying toolchain (mpisstrace, Dimemas). Finally, the last environment is Tareador – a tool that guides parallelization of sequential applications. Tareador showed to be especially useful for teaching parallel programming, so it was included in the academic program of UPC.

### 1.3 Contributions

The first contribution of the thesis consists of exploring techniques for parallelization tuning. The goal of these techniques is to hide communication delays and increase parallelism in scientific parallel applications:

1. In our study of techniques for tuning parallelism in MPI execution, we focus on exploring the potential of communication-computation overlap. We introduce *speculative dataflow* – a technique that automatically overlaps communication and computation in MPI applications, without the need to restructure the target legacy code. We describe the protocol of speculative dataflow, prove its feasibility and demonstrate its potential benefits in characteristic MPI applications. Furthermore, we show that in real scientific applications, overlap can achieve significant execution speedup, as well as higher tolerance to bandwidth reduction. However, we point out that the potential overlap is often seriously limited by the applications intrinsic computation pattern. In the case of one application, we illustrate how that computation pattern can be changed by refactoring the ap-

plication. However, we conclude that it is impractical to do such manual refactoring in each application. In a search for a dynamic technique for restructuring computation patterns, we start our study of task-based dataflow programming models (OmpSs and MPI/OmpSs).

- 2. In our study of techniques for tuning parallelism in MPI/OmpSs execution, we first identify parallelization bottlenecks in existing unmodified MPI/OmpSs applications. The years of practice in optimizing applications points that the major issue is focus – identifying the code section whose optimization would yield the highest overall applications speedup. We illustrate that, due to the irregular parallelism of MPI/OmpSs, the programmer can hardly identify the critical code section. Furthermore, we demonstrate that in many applications, the choice of the critical section decisively depends on the configuration of the target machine. For instance, in HP Linpack, optimizing a task that takes 0.49% of the total computation time yields the overall speedup of less than 0.25% on one machine and at the same time yields the overall speedup of more than 24% on a different machine. To tackle this issue, we devised an automatic approach that, for a given target parallel machines, identifies the critical code sections of an MPI/OmpSs application. Compared to the state-of-the-art research, our approach accounts for more influences, and estimates the potential benefits of the optimization in advance, before incurring into any coding efforts.

- 3. We further explore techniques to introduce OmpSs parallelism into existing MPI applications. OmpSs potentially extracts very irregular parallelism, parallelism that the programmer cannot identify himself. Thus, for a programmer without any development support, it is very hard to anticipate whether some task decomposition exposes parallelism or not. To that end, we provide mechanisms for the programmer to evaluate quickly the potential parallelism of any OmpSs task decomposition. Furthermore, we describe an iterative trial-and-error approach to search for a task decomposition that will expose sufficient parallelism for a given target machine. Finally, we explore the potential of automating the iterative approach by capturing the programmers' experience into an expert system that can autonomously lead the process of finding efficient task decompositions.

The second contribution of the thesis consists in creating an infrastructure that can be used for future research, as well as for educating programmers about parallel programming. To that end, we developed two environments:

- mpisstrace an environment for replaying MPI/OmpSs parallel execution. Already existing BSC tools allow tracing MPI execution with mpitrace and replaying that execution with Dimemas. Based on this infrastructure, we extended MPI tracing library in order to instrument MPI/OmpSs codes and Dimemas in order to support task-based dataflow execution. As the result, we obtained a framework that is fully compatible with the legacy BSC tool-chain, but also supports simulating MPI/OmpSs execution.

- 2. **Tareador** a tool to assist porting MPI applications to MPI/OmpSs. Having an MPI application, the programmer can very simply propose some decomposition of the code into tasks. Then, Tareador dynamically identifies data-dependencies among the annotated tasks and reconstructs potential parallel time-behavior. If the programmer is satisfied with the obtained parallelization, Tareador can further assist the process of porting the application by identifying input and output parameters of each task. Tareador already proved to be so useful in exploring parallelism, that it was included in the academic program of UPC.

### 1.4 Document structure

The document is organized as follows. Chapter 2 presents the state-of-the-art technology related to the topic of this thesis. It provides a survey on the hardware architecture, programming models and development tools related to this thesis. Chapter 3 illustrates the performance issues in parallel computing and introduces the techniques for parallelization tuning addressed in this thesis. In Chapter 4, we describe the development environments designed during the work on this thesis. Furthermore, Chapter 5 presents our work in the field of tuning MPI parallelism. More specifically, it describes our work in the field of overlapping communication and computation in MPI applications. Furthermore, Chapter 6 presents our work in the field of tuning MPI/OmpSs parallelism. Namely, it describes our techniques for identifying parallelization bottlenecks

in MPI/OmpSs and exploring potential MPI/OmpSs parallelism inherent in applications. Chapter 7 presents the previous work related to the research covered in this thesis while Chapter 8 draws the conclusion of this thesis and presents the direction of the future research in this field. Finally, Chapter 9 lists the papers that we published throughout the work on this thesis.

# 2 Background

This Chapter presents the background and state-of-the-art relevant to this thesis Section 2.1 presents background on the architecture of parallel machines. It focuses on the classification of parallel machines on shared-memory and distributed-memory, especially analyzing the cost of communication among separate processing units. Section 2.2 describes the mainstream parallel programming models. It revisits the most widely used programming models for distributed-memory parallel machines (MPI) and shared-memory parallel machines (OpenMP). Also, we describe the OmpSs programming model that extends OpenMP providing semantics for expressing dataflow parallelism. Finally, in Section 2.3 we present the legacy tools that are used throughout this thesis. These tools are the starting point of the thesis – our initial extensions finally graduated into fully independent tools.

### 2.1 Parallel machines

The constant need for higher performance caused the appearance of machines with parallel architecture. A conventional sequential computer consists of the processor connected to the memory via a datapath. Intensive computation makes each of these three parts a bottleneck. As the direct acceleration on these parts showed unfeasible, the solution was found in multiplying resources. However, in order to take advantage of this multiplicity, the execution must exhibit parallelism. The parallelism can be implicit (hidden from the programmer) or explicit (directly expressed by the programmer). In the rest of this Section, we present architectural concepts related to parallel processing.

### 2.1.1 Processor architecture trends

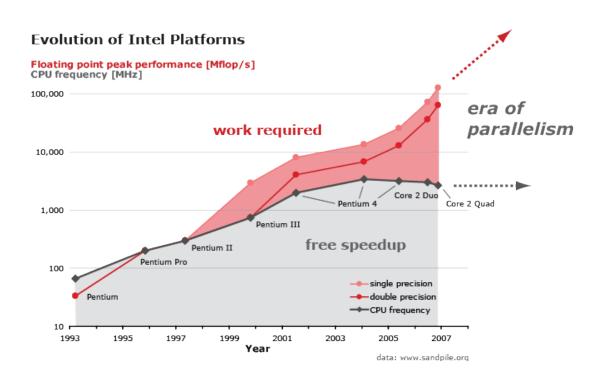

The initial trend in manufacturing more powerful computers was building processors with higher clock frequency. Processor chips are the key components of computers. The most straight-forward approach for making faster computers is making a computer that operates on a higher clock frequency. For a long time, the vendors provided computers with increased frequency, making that property the selling point for all processor chips. Frequency scaling provides an automatic (free) speedup for any software – due to frequency scaling, an unchanged software automatically achieves the speedup proportional to the frequency improvement (gray region in Figure 2.1). However, increased frequency dramatically increases chip's power consumption. Therefore, computing platforms have hit the so called "power wall"[68], with frequency scaling no longer appealing over the 3 GHz.

As the trend of increasing clock frequency became unsustainable, the vendors started investing more effort in designing architectural improvements on the chip. In 1965, Gordon Moore made an empirical observation that the number of transistors on a processor chip doubles every 18-24 months. This observation, called Moore's law [77], still holds. The increased number of transistors in the chip is used for architectural improvements, such as additional functional units, additional registers, wider paths ... This resource abundance increases chip's floating point peak performance (light-red region in Figure 2.1). However, unlike frequency scaling, the resource abundance pro-

Figure 2.1: The evolution of computing platforms. Chart originally from SPIRAL project website [72]

vides no automatic speedup of execution. Therefore, in order to achieve execution speedup, either hardware or software must include additional logic that leverages the additional resources.

Increased number of transistors in the cores lead to architectural improvements that increase the internal processors use of parallelism. This type of parallelism is extracted in the hardware and entirely hidden from the programmer. There are two types of internal processor's parallelism:

1. **Pipelining [47]:** The hardware breaks each instruction into pipeline stages, so different stages of different instructions can execute concurrently. Typically, an instruction is broken into stages of fetch, decode, execute and write-back. The hardware itself checks for data-dependencies among different pipelines, and allows the independent pipeline stages to executed concurrently. This type of parallelism is called instruction-level parallelism (ILP). Available degree of parallelism theoretically increases with the number of pipeline stages. Current processes have between 2 and 26 pipeline stages.

2. Superscalar execution [47]: The hardware consists of multiple independent functional units. The processor is multi-issue – it issues multiple instructions at the same time in order to utilize multiple ALUs, FPUs, load/store units ... These multiplied resources can be utilized in parallel execution of different instructions, as long as data-dependencies are satisfied. Depending on how are the data-dependencies among instructions calculated, these processors can be classified into superscalar processors and very long instruction word (VLIW) processors. In superscalar processors, the hardware dynamically detects data-dependencies, which significantly increases the architectural complexity of the chip. On the other hand, in VLIW processors, the compiler resolves dependencies, generating long instructions that explicitly specify which operations can execute concurrently.

However, since the techniques of implicit parallelism showed only limited potential, new computer architectures targeted higher performance by allowing the programmer to explicitly expose parallelism. The presented two techniques exposed parallelism without any involvement of the programmer – the user programmed a sequential control flow but the underlying system automatically extracted parallelism. However, the implicit parallelism showed to be insufficient. An alternative approach puts multiple independent cores in one chip and allows the programmer to have a different control flow in each of the cores. These parallel architectures provided more flexibility in using the computation resources, but also increased the complexity of programming.

### 2.1.2 Memory Organization

Parallel computers can have shared or distributed-memory organization. Here, a clear distinction should be made between how the memory is physically organized in hardware and how the memory is perceived by the programmer. In respect to the physical organization of the memory, a parallel machine can have shared memory or distributed memory. Moreover, the machine can also have a hybrid organization where at the level of one node the machine has shared memory, while different nodes among themselves operate on distributed memory. However, all these physical systems, from the programmers point of view can be systems with shared or distributed address space. Further text in this Section describes the differences between shared-memory and

distributed-memory systems.

### **Ditributed-Memory Organization**

Distributed-memory machines (DMM) are computers with physically distributed memory. Each node is an independent unit that consists of a processor and a local memory. An interconnection network connects all the nodes and allows communication among them. Each node can only access its local memory. If a node needs data that is not in its local memory, the data needs to be transferred by sending messages through the network.

Distributed-memory machines improve efficiency by investing in faster and more intelligent networks. In DMMs, the nodes are usually connected by point-to-point interconnection links. Each node connects to a finite number of neighboring nodes. The network topology is regular, often a hypercube or a tree. Since each node can send the message only to its neighboring nodes, limited connectivity significantly restricts programming. Initially, communication between nodes that have no direct connection had to be controlled by software of the intermediate nodes. However, new intelligent network adapters enabled data transfers to or from the local memory without participation of the host processor. This allowed that the host processor can be efficiently computing while, in background, there is a transfer to/from it. Furthermore, the state-of-the-art networks optimize communications by dedicating special links for executing multicast transfers.

A distributed-memory machine consists of loosely coupled processing units, making it easy to assemble but difficult to program. DMMs can be assembled using off-the-shelf desktop computers. However, to achieve high performance, the nodes must be interconnected using a fast network. On the other hand, DMMs are very difficult to program. The programmer must explicitly specify the data decomposition of the problem across processing units with separate address spaces. Also, the programmer must explicitly organize inter-processor communication, making both the sender and the receiver aware of the transfer. Moreover, the programmer must take special care about data partitioning among the nodes, because delivering some data from one node to another may be very expensive. Thus, the data layout must be selected carefully to minimize the amount of the exchanged data.

### **Shared-Memory Organization**

Shared-memory machines (SMM) are computers with a physically shared memory. A SMM consists of more processors, a shared physical memory (global memory), and the network that connects the processors and the memory. The processors communicate by reading and writing shared variables. The global memory usually provides a common address space over a set of memory modules. The programming model allows coordination of processors through the accesses to the common address space. However, concurrent accesses to the shared data must be coordinated in order to avoid race conditions with unpredictable effects.

The users perception of shared memory facilitates programming, at the cost of difficult implementation of the machine. Communication through shared variables allows easy parallelization. The programmer is less concerned about data locality, expecting from the machine to serve all his requests for data. However, providing a fast global memory access to multiple processors makes the technical realization of a SMM a serious effort. Increasing the number of processors in the system further stresses performance of the global memory. Thus, a shared resource of global memory is an impediment for high scalability of these machines. Scaling of these machines beyond tens of cores is very hard.

The most common parallel programming model for SMMs is threaded execution. Multiple threads have separate control flows but can access shared global memory. A programmer expresses parallelism using parallel constructs offered by the programming model. The programming model maps user threads on system kernel threads, while the operating system maps kernel threads to processors. These mapping algorithms are partly or entirely hidden from the programmer. Also, the operating system can take advantage of hardware parallelism by starting concurrent execution of different sequential programs on different processors.

Initial implementations of SMMs usually relied on uniform memory access (UMA) architectures. UMA architecture provides a uniform access time from any processor to the single shared memory. Thus, UMA platforms are often called symmetric multiprocessors (SMP). The interconnect is typically a central bus that connects small number of processors to the global memory. In this architecture, the interconnect becomes a bottleneck that limits the number of processors in the system. Besides caches, there is

no other memory private to the processors. Caches allow faster access time, and avoid that all the data requests go to the interconnect.

Today many implementations of SMMs rely on NUMA (non-uniform memory access) architecture. NUMA architectures offer to the programmer perception of a shared address space, although the underlying architecture is based on physically distributed memory. Thus, NUMA platforms are often called distributed shared-memory (DSM) machines. Perception of shared address space is achieved using the cache coherence protocol. The coherence protocol guarantees that the memory access goes to the last version of the variable, independent of where the variable is physically stored. However, coherence causes the access time to memory to depend on the physical location of the accessed data. An access to the data that is locally stored is faster than an access to the data that is stored in the local memory of some other node.

### 2.1.3 Message Passing Cost

This thesis focuses on achieving more efficient inter-processor communication. The efficiency of communication can significantly determine the overall performance of the parallel system. In this subsection, we explore in more details the factors that determine the cost of message passing among nodes. Also, we explore the possible techniques to reduce the transfer time for messages.

The message transfer time is a sum of the time needed to prepare the message for transmitting, and the time needed for the message to traverse the network to its destination. The system parameters that determine the transfer time are:

- Startup time: Startup time is the processing time local to the node that is needed before sending and after reception of the message. This time accounts for the time needed to pack the data into the message (adding message header, tail and error correction information). Also, this time accounts for executing routing algorithms and interfacing of the processor with the router.

- Latency: On its way to the destination, the message has to do a finite number of hops via links that directly connect routers. Latency time is the multiply of the latency of the router and the length of the routing path (number of hops to reach the destination).

• **Bandwidth:** Bandwidth determines the speed by which the data traverses the network. Bandwidth of the network depends of the clock rate and the width of the links as well as of the speed of the routing and buffering within the routers.

One way of improving message passing among nodes is to reduce the transfer time. Network vendors constantly deliver more expensive networks that have more resources. First, networks with faster clock rate can provide higher bandwidth and lower latency. Latency can further be improved by the increased connectivity among nodes. Furthermore, new network interfaces can offload message processing from the node, thus reducing the startup time. Also, message transfer time can be significantly reduced by the programmer. Organizing a good data layout, the programmers can reduce the total amount of data that needs to be communicated. Moreover, the programmer can amortize the startup overhead by communicating in bulk – accumulating more data and communicating in larger messages.

However, this thesis focuses on different techniques that improve message passing – instead of reducing time of the transfer, our goal is to hide the transfer time by overlapping it with useful computation. As already mentioned, state-of-the-art parallel machines can transfer messages without direct involvement of the processors. Thus, while the message is in transfer, the processor can be busy doing some useful computation. This approach potentially allows to execute long transfers, without consequently stalling the involved processors.

### 2.2 Parallel programming models

The search for the "holy grail" of parallel computing has failed – there is no efficient and highly applicable automatic parallelization. The biggest idea in the field of parallel computation was to find techniques that would automatically expose parallelism in the applications. However, despite decades of work [78], automatic parallelization showed very limited potential. Today, the only viable solution is to rely on the programmer to expose parallelism.

For distributed-memory machines, the mainstream programming models are message passing (MP) and partitioned global address space (PGAS). The most popular implementation of MP model is message passing interface (MPI) [81]. In MPI, the pro-

grammer must partition the workload among processes with separate address spaces. Also, the programmer must explicitly define how the processes communicate and synchronize in order to solve the problem. Conversely, PGAS model is implemented in languages such as UPC [20], X10 [25] and Chapel [24]. PGAS model provides a global view for expressing both data structures and the control flow. Thus, as opposed to message passing, the programmer writes the code as if a single process is running across many processors.

On the other hand, OpenMP [31] is a de-facto standard for programming shared-memory machines. OpenMP extends the sequential programming model with a set of directives to express shared-memory parallelism. These directive allow exposing fork-join parallelism, often targeting independent loop iterations. Nevertheless, OmpSs programming model [37] extends OpenMP offering semantics to express dataflow parallelism. Compared to fork-join parallelism exposed by OpenMP, the parallelism of OmpSs can be much more irregular. Throughout this thesis, we focus mainly on OmpSs as a programming model for shared-memory machines. We also explore the potential of MPI/OmpSs, a hybrid programming model that integrates OmpSs and MPI.

### 2.2.1 **MPI**

Message Passing Interface (MPI) [81] is the most widely used programming model for programming distributed parallel machines. To facilitate writing message-passing programs, MPI standard defines the syntax and semantics of useful library routines. Today, MPI is the dominant programming model in high-performance computing.

In the MPI programming model, multiple MPI processes compute in parallel and communicate by calling MPI library routines. At the initialization of the program, a fixed set of processes is created. Typically, the optimal performance is achieved when each MPI process is mapped on a separate core. For easier coordination among processes, MPI interface provides functionality for communication, synchronization and virtual topology.

The most essential functionality of MPI is point-to-point communication. The most popular library routines are: MPI\_Send to send a message to some specified process; and MPI\_Recv to receive a message from some specified process. Point-

to-point operations are especially useful for implementing irregular communication patterns. A point-to-point operation can be in synchronous, asynchronous, buffered, and ready form, providing stronger and weaker synchronization among communicating processes. The ability to probe for messages allows MPI to support asynchronous communication. In asynchronous mode, the programmer can issue many outstanding MPI operations.

Collective operations allow communication of all processes in a process group. The process group may consist of the entire process pool, or it may be user defined subset of the entire pool. A typical operation is MPI\_Bcast (broadcast), in which the specified root process sends the same message to all the processes in the specified group. A reverse operation is MPI\_Gather, in which the specified root process receives one message from all the processes in the specified group. Other collective operations implement more sophisticated communication patterns.

Throughout its evolution, MPI standard has introduced new features to facilitate easier and more efficient parallel programming. The initial MPI-1 specification focused on message passing within a static runtime environment. Additionally, MPI-2 includes new features such as parallel I/O, dynamic process management, one-sided communication, etc. Furthermore, recent research studies [50] motivated MPI community to include non-blocking collective operations [50] as a part of MPI-3 standard.

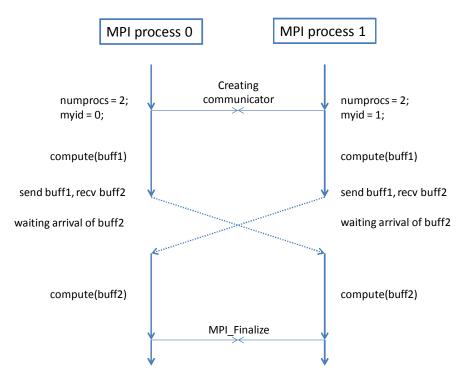

### A simple program

In this Section, we present a simple program and explain the runtime properties of MPI execution. The example shows a simple code with only two sections of useful work (function compute) and one Section that exchanges data (function  $MPI\_Sendrecv$ ). Each MPI process executes function compute on local buffer buff1, then sends the calculated buffer buff1 to its neighbor. At the same time, each process receives buffer buff2 from another neighbor, and again executes function compute on the received buffer. The processes communicate in a one-sided ring pattern – each process receives the buffer from the process with rank for 1 lower, and sends the calculated buffer to the process with rank for 1 higher.

All the processes start independently, learning about the parallel environment by calling MPI\_Init. MPI execution starts by calling the MPI agent (mpirun-nx./binary.exe)

17

```

1 #include <mpi.h>

2 #include <stdio.h>

3 #include <string.h>

5 int main(int argc, char *argv[])

6 {

float buff1[BUFSIZE], buff2[BUFSIZE];

7

8

int numprocs;

9

int myid;

10

int tag = 1;

11

12

MPI_Status stat;

13

MPI_Init(&argc,&argv);

14

15

/* find out how big the SPMD world is */

16

MPI_Comm_size(MPI_COMM_WORLD,&numprocs);

17

18

/* and this processes' rank is */

19

MPI_Comm_rank(MPI_COMM_WORLD,&myid);

20

21

/* At this point, all programs are running equivalently,

the rank distinguishes the roles of the programs in the SPMD model */

22

23

/* compute on the local data (buff1) */

24

25

compute(buff1);

26

/* exchange data (send buff1 and receive buff2 )*/

27

28

my_dest = (myid + 1) % numprocs;

29

my_src = (myid + numprocs - 1) % numprocs;

MPI_Sendrecv( /* sending buffer */ buff1, BUFSIZE, MPI_FLOAT,

30

/* destination MPI process */ my_dest, tag,

31

/* receiving buffer */ buff2, BUFSIZE, MPI_FLOAT,

32

/* source MPI process */ my_src, tag,

33

34

MPI_COMM_WORLD, &stat);

35

36

/* compute on the received data (buff2) */

37

compute(buff2);

38

39

/* MPI programs end with MPI Finalize; this is a weak synchronization point */

40

MPI_Finalize();

41

42

return 0;

43 }

44

```

Figure 2.2: Example MPI code

that spawns the specified number (x) of MPI processes. In the studied case (Figure 2.3), the MPI execution starts with 2 independent MPI processes. By calling MPI\_Init, each process learns about the MPI parallel environment. All the MPI processes are grouped into the universal communicator (MPI\_COMM\_WORLD). Using the universal com-

Figure 2.3: Execution of the example MPI code

municator, each process identifies the total number of MPI processes in the system (MPI\_comm\_size) and gets the unique rank of the process (MPI\_comm\_rank).

Each MPI process, knowing its rank and the size of the universal communicator, identifies its role in the execution of the parallel program. Each process identifies the part of the total workload that is assigned to it. Also, each process identifies the ranks of the neighboring processes with which it should communicate in order to get the job done. In the presented example, based on *myid* and *numprocs*, each process calculates ranks of its neighboring processes (*my\_dest* and *my\_src*) to generate the one-sided ring communication pattern.

When the computation on the local data finishes, the processes communicate to exchange the data and start the next phase of computing on the local data. Each process calculates the buffer buff1 in the function compute. Then, the process sends the processed buff1 to the neighboring process. At the same time, the process receives a message from some other neighboring process and stores the content of that message into local buffer buff2. Then, the process locally computes on buff2 in another instantiation of function compute. Thus, MPI process 0 calculated on its local buff1,

and then after the  $MPI\_S$  endrecv call, it calculated on its local buff2 (that was buff1 local to MPI process 1).

When the useful work finishes, all the processes call *MPI\_Finalize* to announce the end of the parallel section. *MPI\_Finalize* implicitly calls a barrier, waiting for all the MPI processes from *MPI\_COMM\_WORLD* to come to this point. When all the processes reach the barrier, the joint work is guaranteed to be finished, and all the processes can exit the parallel execution independently. The parallel execution finishes.

This simple example also illustrates one of the main topics of this thesis – communication delays that are characteristic for MPI execution. When both processes finish executing compute(buff1), they initiate their transfers in the same moment. While the messages are in transit, both processes are stalled without doing any useful work. Chapter 3 further illustrates this problem and presents some of the possible solutions.

#### **Different MPI implementations**

MPI standard defines a high-level user interface, while low-level protocols may vary significantly depending of the implementation. MPI provides a simple-to-use portable interface for a basic user, setting a standard for hardware vendors of what they need to provide. This opens space for various MPI implementations that have different features and performances.

Depending on the implementation, MPI messaging may use different messaging protocols. An MPI message passing protocol describes the internal methods and policies employed to accomplish message delivery. Two common protocols are

- eager an asynchronous protocol in which a send operation can execute without an acknowledgement from the matching receive; and

- **rendezvous** a synchronous protocol in which a send operation can execute only upon the acknowledgement from the matching receive.

Eager protocol is faster, as it requires no "handshaking" synchronization. However, this relaxation of synchronization comes at the cost of the increased memory usage for message buffering. Thus, a common implementation uses eager protocol only for messages that are shorter than the specified threshold value. On the other hand, messages larger than the threshold are transferred using rendezvous protocol. Also, it is common

that a very long message is partitioned into chunks, with each chunk being transferred using separate rendezvous protocol.

Also, MPI implementations provide different interpretation of independent progress of transfers. Independent progress defines whether the network interface is responsible for assuring progress on communications, independent of making MPI library calls. This feature is especially important for the messages that use rendezvous protocol. For example, rank 0 sends a non-blocking transfer to rank 1 using rendezvous protocol. If rank 0 comes to its MPI\_Isend before rank 1 comes to the matching receive, rank 0 issues handshaking request and leaves the non-blocking send routine. Later, when rank 1 enters its corresponding MPI Recv, it acknowledges the handshake, allowing rank 0 to send the message. The strict interpretation of the independent progress mandates that rank 0 sends the actual message as soon as it receives the acknowledgement from rank 1. Conversely, the weak interpretation mandates that rank 0 must enter some MPI routine in order to process the acknowledgement and prepare for the actual message transfer. Here, the weak interpretation of independent progress will be very performance degrading if after the non-blocking send, rank 0 enters a very long computation with no MPI routine calls. Most of the state-of-the-art networks provide the strict implementation of progress by introducing interrupt-driven functionality in the network interface.

Depending on the computation power of the network interface, an MPI implementation can provide different ability for communication/computation overlap. MPI standard specifies semantic for asynchronous communication that offers significant performance opportunities. However, in some machines, the processors are entirely responsible for assuring that the message reaches its destination. On the other hand, many state-of-the-art networks provide intelligent network adapters that take care of delivering the message, allowing the processor to dedicate to useful computation. This way it is possible to achieve overlap of communication and computation – a feature that is considered of a major importance for high parallel performance.

Also, an MPI implementation can provide different interpretation for offload. Offload is the feature that enables the processor to pass the overhead of MPI routines to the network interface. Offload avoids the host processor involvement in progressing on a non-blocking send on the sender side and storing the received message into the local memory of the receiver side. An implementation that supports offload allows

both overlap and independent progress to be achieved without host processor overhead. In applications with frequent calls to MPI library, offload can significantly boost the performance [19].

## 2.2.2 OpenMP

OpenMP (Open Multi-Processing) [31] is the mainstream programming model for programming shared-memory parallel systems. OpenMP is an application programming interface (API) that supports multi-platform shared-memory programming in C, C++, and Fortran. It uses a portable model that provides to programmers a simple and flexible interface for developing parallel applications for platforms ranging from the standard desktop computer to the supercomputer. OpenMP allows integration with MPI, providing a hybrid MPI/OpenMP model for parallel programming at large scale.

OpenMP is a programming model based on fork-join parallelism. On reaching a parallel section, a master thread forks a specified number of slave threads. All the threads run concurrently, with the runtime environment mapping threads to different processors. When the parallel section finishes, the slave threads join back into the master. Finally, the master continues through the sequential section of the program.

OpenMP provides a set of programming language extensions that the programmer can use to expose parallelism in the program. OpenMP extends the sequential programming model with a set of directives (pragmas in C/C++) to express shared-memory parallelism. Also, it provides a set of runtime library routines and environment variables that allow the programmer to dynamically modify parallel execution. The OpenMP language extensions can be classified into: 1) control structures for expressing parallelism; 2) data environment constructs for communicating among threads; and 3) synchronization constructs for coordinating threads. In the following paragraphs, we further explain these three types of extension.

Control structures alter the flow of execution. There are two kinds of constructs for expressing parallelism. The *parallel* directive encapsulates a block of code and creates a set of threads that concurrently execute that block. The multiple concurrent threads execute different execution instances of that block of code. The second control structure is the *do* directive that allows to divide the work among an existing set of threads.

Data environment constructs enable communication among threads. When the master thread reaches a parallel construct, it creates new slave threads with private execution contexts. This enables a new thread to execute without interfering with stack frames of other threads. Data environment constructs allow the programmer to choose whether some variable will be shared among threads. Each variable has one of the three sharing attributes:

- *shared*: A variable with shared scope clause has a single storage location in memory during the parallel construct. Using this unique memory location, the threads can communicate through read/write operations.

- *private*: A variable with private scope clause has a separate storage location for each thread during the parallel construct. All read/write operations on this location are protected from the accesses of other threads.

- *reduction*: The reduction clause is used for variables that are target of reduction operations. This sharing attribute mixes the properties of shared and private attribute, allowing the compiler to optimize accesses to it.

Synchronization constructs coordinate the execution of threads. OpenMP threads communicate via read/write operations to the shared variables. However, without any thread synchronization, concurrent accesses to shared variables may induce race conditions. Two common OpenMP synchronization mechanisms are mutual exclusion and event synchronization. Mutual exclusion guarantees that a shared variable is accessed exclusively by one thread. Exclusivity is achieved with the *critical* directive that encapsulates a block of code that can be accesses by one thread at the time. Event synchronization signals the occurrence of some event across multiple threads. The most common event synchronization construct is the *barrier* directive that defines a point where each thread waits for all the other threads to catch up. Besides *critical* and *barrier*, OpenMP provides other directives that can model more complicated synchronization patterns.

#### A simple OpenMP example

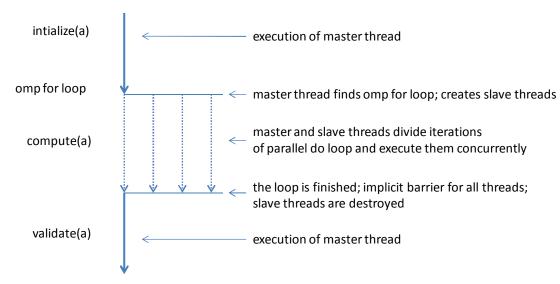

This Section analyzes a simple loop parallelization using OpenMP. Figure 2.4 shows a simple OpenMP code. The code consists of one loop that calls function *compute*

in each iteration. Before the loop, the buffer is initialized (function *initialize*), and after the loop, the buffer is validated (function *validate*). In each iteration of the loop, function *compute* executes on a different element of array *a*, making all the iterations of the loop independent. Thus, the appropriate OpenMP parallelization of this code would be using the *parallel* construct to make all the iterations of the loop execute concurrently. The original sequential code is parallelized by adding only one line of code.

Figure 2.5 illustrates OpenMP parallel execution of the presented code. The program initializes with only one thread active – the main thread. After finishing function

```

1 int main(int argc, char *argv[]) {

const int N = 100000;

3

int i, a[N];

4

5

initialize(a);

6

7

#pragma omp parallel

for (i = 0; i < N; i++)

8

9

compute(a[i]);

10

validate(a):

11

12

13

return 0;

14 }

```

Figure 2.4: simple OpenMP code

Figure 2.5: simple OpenMP code

*initialize*, the main thread reaches the parallelized loop and spawns the specified number of slave threads (3 in this case). The four threads partition among themselves the iterations of the loop and start computing concurrently. The parallel for loop ends with an implicit barrier that waits for each thread to finish executing iterations that are assigned to it. When all the threads finish their portion of work, the barrier condition is fulfilled. The main thread destroys all the slave threads and proceeds with the sequential section of the program (function *validate*).

It is important to note that an OpenMP programmer just specifies how to divide the work between threads, but not how to execute that work on the underlying machine. For the programmer, the thread is a separate control flow that operates on the same memory as the main thread. Having that abstraction, the programmer does not care whether OpenMP thread is implemented as an OS thread or a Pthread. Also, the programmer leaves to the compiler (or runtime) to decide how to partition the iterations across the threads. However, to achieve higher data locality, OpenMP provides to the programmer special semantics to specify how the iterations should be distributed across threads.

In the presented simple code, the scope of each variable is determined by the default OpenMP rules. By default, all the variables are shared if not declared differently. Thus, array a is shared. Each iteration of the parallelized loop accessed a different element in the array, avoiding any conflict of concurrent accesses to a shared variable. Especially, loop index i is an exception in the default OpenMP rules. Within a parallel construct, loop index is automatically declared as private variable. Thus, the conflicts are avoided by making a private copy of the loop index for each thread. After the parallel loop finishes, these private copies are destroyed, and the value of i is assumed to be undefined.

Again, our simple example requires no explicit synchronization. Synchronization is primarily used to coordinate accesses to shared variables. Since each iteration of the loop computes on a different element of array a, there is no need for explicit synchronization inside parallel loop. However, in order to do the validation of the array (function *validate*), all the threads must finish their computation of loop iterations. Again, explicit synchronization constructs are avoided, because parallel loop implicitly ends with a barrier. The barrier assures that all the concurrent threads finished their work, so the main thread can proceed to *validate*.

```

#pragma omp parallel

#pragma omp single

p = listhead;

num elements = 0;

p = listhead;

while(p) {

while (p) {

listitem[num elements++] = p;

#pragma omp task

p = next(p);

p = listhead;

process(p);

while (p) {

p = next(p);

#pragma omp parallel for

process (p)

for (int i=0; i<num elements; i++)</pre>

}

p=next (p);

process( listitem[i] );

}

(a) sequential code.

(b) OpenMP without tasks.

(c) OpenMP with tasks.

```

Figure 2.6: Pointer chasing application parallelized with OpenMP

#### **OpenMP** tasks

Although the parallelization of the presented code appears easy and elegant, it remains a question whether OpenMP loop parallelization could be widely applicable. OpenMP is tailored for applications with array-based computation. These application have very regular parallelism and regular control structures. Thus, OpenMP can identify all work units in the compile time and statically assign them to multiple threads. However, irregular parallelism is inherent in many applications such as tree data structure traversal, adaptive mesh refinement and dense linear algebra. These applications would be very hard to parallelize using only basic OpenMP syntax.

Let us consider possible OpenMP parallelization of the sequential code from Figure 2.6a. The program consists of a while loop that updates each element of the list. The code cannot be parallelized just by adding a parallel loop construct, because the list traversal would be incorrect. Thus, in order to use a parallel loop construct, the list first has to be translated into an array (Figure 2.6b). However, this translation causes an inadmissible overhead.

In order to tackle this issue, OpenMP introduces support for tasks. Tasks are code segments that may be deferred to a later time. Compared to the already introduced work units, tasks are much more independent from the execution threads. First, a task is not bound to a specific thread – it can be dynamically scheduled on any of the active threads. Also, a task has its own data environment, instead of inheriting the data environment from the thread. Moreover, tasks may be synchronized among

themselves, rather than synchronizing only separate threads. This implementation of OpenMP tasks allows much higher expressibility of irregular parallelism.

Figure 2.6c illustrates the possible parallelization of the studied code using OpenMP tasks. The master thread runs and dynamically spawns a task for each instantiation of the function *process*. On each instantiation, the content of pointer *p* is copied into the separate data environment of the task. Since the inputs to the task are saved, the task can execute later in time. Thus, the master thread sequentially traverses the list and dynamically spawns tasks. The spawned tasks are executed by the pool of worker threads. When the main thread finishes spawning all tasks, it joins the workers pool. Therefore, despite of irregular control structures, OpenMP tasks allow elegant parallelization.

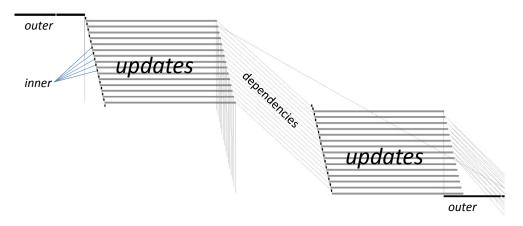

Since tasks showed to be very powerful in exposing irregular parallelism, OpenMP community concentrates on developing new tasking constructs that could further facilitate programming. Thus, soon to appear OpenMP API version 4.0 introduces data-dependencies between tasks. Namely, the 4.0 standard introduces a new task clause:

depend(dependence-type: list),