**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

Thesis submitted to the Universitat Politècnica de Catalunya for the Degree of Doctor of Philosophy, November 2011.

# MODULATION STRATEGIES FOR THE NEUTRAL-POINT-CLAMPED CONVERTER AND CONTROL OF A WIND TURBINE SYSTEM

by

Jordi Zaragoza i Bertomeu

Supervised by

Dr. Josep Pou i Fèlix

#### ACTA DE QUALIFICACIÓ DE LA TESI DOCTORAL

Reunit el tribunal integrat pels sota signants per jutjar la tesi doctoral:

Títol de la tesi: MODULATION STRATEGIES FOR THE NEUTRAL-POINT

CLAMPED CONVERTER AND CONTROL OF A WIND TURBINE

SYSTEM

| Autor  | de la tesi: Jordi Zarago | oza i Bertomeu  |                 |

|--------|--------------------------|-----------------|-----------------|

| Acord  | a atorgar la qualificaci | ó de:           |                 |

|        | No apte                  |                 |                 |

|        | Aprovat                  |                 |                 |

|        | Notable                  |                 |                 |

|        | Excel·lent               |                 |                 |

|        | Excel·lent Cum Laude     | е               |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

| Terras | ssa, de/d'               | de              |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

| FI Pre | esident                  | El Secretari    | El vocal        |

|        | Joident                  | Li occician     | Livodai         |

|        |                          |                 |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

|        |                          |                 |                 |

| (nom   | i cognoms)               | (nom i cognoms) | (nom i cognoms) |

Als meu pares, que ho són tot per mi i que tant suport i afecte m'han donat.

A Natàlia, per estar sempre al meu costat i compartir la seva vida amb mi.

| i conincai oniversity or cataloni | Technical | Universit | v of | Catal | lonia |

|-----------------------------------|-----------|-----------|------|-------|-------|

|-----------------------------------|-----------|-----------|------|-------|-------|

### **ACKNOWLEDGMENTS**

First of all, I would like to thank my supervisor, Dr. Josep Pou, for his guidance, support in this work and for always demanding the best from me. His friendship and dedication have made the realization of this thesis possible. During the development of this work, we spent several years researching together. His knowledge, humility and work have instilled in me great admiration.

I would like to thank Dr. Salvador Ceballos (Salva, to his friends) for the good and fun times we spent together researching. His support and collaboration made several results in this thesis possible. I hope to return the favor someday.

I would like to thank Dr. Pedro Ibáñez for giving me the opportunity to stay at the Energy Unit of the Robotiker-Tecnalia research center. My research in Robotiker was a pleasant experience thanks to the staff. They helped me integrate myself and enjoy the experience during my stay. For this reason I would like to thank all my colleagues in Robotiker. I would especially like to thank Dr. Eider Robles for the moments that we shared inside and outside the technological center.

I would also like to thank Dr. Cyril Spiteri for giving me the opportunity to stay at the Industrial Electrical Power Conversion Department in the Faculty of Engineering at the University of Malta. I am grateful for his guidance during my stay.

I would like to thank all my colleagues from the Technical University of Catalonia, especially those in the Department of Electronic Engineering in Terrassa, for sharing so many coffees and meals during these years. Particularly, I would like to thank my friends Juan and Nestor for all the joyful moments we shared and adversities we overcame. I am especially grateful to Dr. Antoni Arias for his technical advice and suggestions.

Finally, I would like to dedicate this dissertation to my parents Salvador and Teresa, my brother Juan Salvador, my grandparents and the rest of my family for their support and love. I would also like dedicate this dissertation to my love Natàlia for sharing her life with me.

## MODULATION STRATEGIES FOR THE NEUTRAL-POINT-CLAMPED CONVERTER AND CONTROL OF A WIND TURBINE SYSTEM

#### **RESUM**

Els convertidors multinivell són topologies de convertidors d'electrònica de potència que poden generar tres o més nivells de voltatge en cadascuna de les fases de sortida. Com a resultat, els voltatges i corrents generats per aquestes topologies presenten una distorsió harmònica baixa. Hi ha diferents configuracions de convertidors multinivell, les quals es basen en connectar dispositius de potència o convertidors en sèrie. El resultat d'aquestes connexions permet obtenir voltatges alts, tant en la part de corrent continu com en la de corrent altern del convertidor. A més, cada dispositiu sols ha de suportar una fracció del voltatge total del bus de corrent continu. Per aquestes raons, els convertidors multinivell són generalment utilitzats en aplicacions d'alta potència.

El convertidor de tres nivells amb connexió a punt neutre (neutral-point-clamped) és el més utilitzat. La recerca d'aquesta tesis doctoral està focalitzada en aquesta topologia de convertidor, i el principal objectiu és l'aportació de noves tècniques de modulació. Aquestes tenen en compte diferents aspectes: la velocitat computacional dels algorismes, l'equilibrat de les tensions dels condensadors del bus de contínua, les pèrdues de commutació i les oscil·lacions de baixa freqüència en el punt neutre del convertidor.

Totes les estratègies de modulació proposades en aquesta tesis són modulacions d'amplada de polses basades en portadora. En la primera modulació que es presenta, s'injecta un senyal comú (seqüència zero) a totes les moduladores, que es basa en els patrons de la modulació vectorial que utilitza tres vectors dels més propers al de referència (nearest-three-vector modulation). S'estudien i es comparen els resultats d'aquesta modulació amb la seva homòloga, basada en

perspectiva vectorial. Una segona proposta és l'anomenada modulació d'amplada de polses de doble senyal (double-signal pulse-width modulation). Aquesta modulació és capaç d'eliminar completament les oscil·lacions de voltatge en el punt neutre del convertidor. No obstant això, es produeix un increment de les pèrdues de commutació en els dispositius de potència i, a més, no hi ha un equilibrat natural de les tensions en els condensadors del bus. Una última estratègia de modulació, anomenada modulació híbrida (hybrid pulse-width modulation), es basa en la combinació de la modulació sinusoïdal (sinusoidal pulse-width modulation) i la de doble senyal. Aquesta presenta una solució de compromís entre reduir les pèrdues de commutació, en detriment d'un augment de l'amplitud de les oscil·lacions de voltatge en el punt neutre.

Una segona part d'aquesta tesis es centra en les aplicacions a generació eòlica, ja que els convertidors multinivell estan començant a ser utilitzats en aquest camp. Això es produeix fonamentalment per l'augment continu de les dimensions de les turbines eòliques. En aquesta part de la recerca s'ha considerat la configuració de dos convertidors multinivell connectats a un mateix bus de contínua (back-to-back), tot i que els convertidors han estat estudiats independentment. Inicialment s'ha estudiat el convertidor que va connectat a la xarxa elèctrica i s'ha aplicat l'estratègia de control coneguda com a control orientat a tensió (voltage-oriented control). S'han utilitzat controladors estàndard (proporcional-integral), als quals s'ha afegit un control difús que supervisa i modifica els valors de les constants dels controladors. Aquest supervisor difús millora la dinàmica de la tensió del bus de contínua davant canvis de càrrega quan el convertidor treballa com a rectificador. Per una altra part, s'ha estudiat el control d'una turbina eòlica basada en un generador d'imants permanents. En aquest cas, s'ha aplicat l'estratègia de control coneguda com a control orientat a camp (field-oriented control). S'han avaluat i comparat els avantatges i inconvenients de diferents formes de sintonitzar els controladors.

## MODULATION STRATEGIES FOR THE NEUTRAL-POINT-CLAMPED CONVERTER AND CONTROL OF A WIND TURBINE SYSTEM

#### **ABSTRACT**

Multilevel converters are power electronic topologies that can generate three or more voltage levels in each output phase. As a result, the voltage and current waveforms generated have lower total harmonic distortion. Multilevel topologies are based on connecting power devices or converters in a series. Consequently, high voltages can be handled on the dc and ac sides of the converter, while each device stands only a fraction of the total dc-link voltage. For these reasons multilevel converters are generally applied to high-power applications.

The three-level neutral-point-clamped converter is the most extensively used multilevel topology. This topology is the main focus of research in this dissertation. The main objective is to propose new modulation strategies that are able to meet a compromise solution while considering computational algorithm speed, voltage balance in the dc-link capacitors, switching losses and low frequency voltage oscillations at the neutral point.

All the modulation strategies proposed here are based on carrier-based pulse-width modulation. A new modulation strategy has been implemented using a proper zero-sequence signal injected into the modulation signals. The zero sequence is determined from a space-vector modulation standpoint, particularly the nearest-three-vector modulation strategy. The proposed carrier-based technique is compared with its space-vector modulation counterpart. It shows some advantages, such as easier implementation and reduced switching events; however, it still produces oscillations in the neutral-point voltage for some operating conditions. A new modulation strategy able to completely remove such voltage oscillations is also presented. It is called double-signal pulse-width modulation. The main drawback of this strategy is that it

increases the switching frequency of the power devices and has no natural capacitor voltage balance. Some balancing strategies are proposed in this dissertation for this specific modulation. Furthermore, a hybrid pulse-width modulation approach is presented which is able to combine sinusoidal pulse-width modulation with double-signal pulse-width modulation; this represents a compromise solution between switching losses and neutral-point voltage oscillation amplitudes.

The second part of this thesis is focused on wind generation applications. Multilevel converters are starting to be used in such a field nowadays, and are expected to be further applied in the near future as the sizes of wind turbines grow. Two back-to-back-connected power converters are considered in this application, although they are analyzed independently. First of all, the control of the grid-connected converter is studied. A voltage-oriented control is used with standard proportional-integral controllers. The originality of the method is that a fuzzy supervisor is designed and included in the structure; the fuzzy supervisor is able to modify the proportional-integral parameters online. It is shown how the control of the total dc-link voltage improves significantly under load changes when the converter is working as a rectifier. On the other hand, a control study is performed on the wind turbine side. The variable speed wind turbine is based on a permanent magnet synchronous generator. A field-oriented control strategy is applied. The controllers are evaluated and compared using different tuning strategies which highlight the advantages and drawbacks of each.

## **Contents**

| ACKNOWLEDGMEN 15                   | VII   |

|------------------------------------|-------|

| RESUM                              | ix    |

| ABSTRACT                           | xi    |

| List of Figures                    | xix   |

| List of Tables                     | xxvii |

| List of Abbreviations and Acronyms | xxix  |

|                                    |       |

| CHAPTER 1.                         | 1     |

| INTRODUCTION                       | 1     |

| 1.1.Context of the Research        | 2     |

| 1.2.Introduction of this Thesis    | 2     |

| 1.3.Objectives                     | 5     |

| 1.4. Structure of the Document     | 6     |

| 1.5. Chapter References            | 8     |

| CHAPTER 2.                                                             | 11 |

|------------------------------------------------------------------------|----|

| MULTILEVEL TOPOLOGIES. PROTOTYPE DESCRIPTION AND MODULATION TECHNIQUES | 11 |

| 2.1. Multilevel Converter Topologies                                   | 12 |

| 2.1.1. Diode-Clamped Converter                                         | 13 |

| 2.1.2. Floating-Capacitor Converter                                    | 17 |

| 2.1.3. Cascaded H-bridge Converter                                     | 21 |

| 2.1.4. General Data for Basic Multilevel Topologies                    | 22 |

| 2.2. Prototype Description                                             | 24 |

| 2.2.1. NPC Converter Description                                       | 24 |

| 2.2.2. Digital Control Hardware                                        | 26 |

| 2.2.2.1. Digital Signal Processor                                      | 27 |

| 2.2.2. PLD Board                                                       | 27 |

| 2.3. Modulation Techniques                                             | 28 |

| 2.3.1. Space-Vector Modulation (SVM)                                   | 28 |

| 2.3.2. Limiting Area                                                   | 31 |

| 2.3.3. Calculation of Duty Cycles                                      | 33 |

| 2.3.4. Calculation of Duty Cycles by Projections                       | 34 |

| 2.3.5. Three-Level Converter                                           | 35 |

| 2.3.5.1. SVM under Voltage-Balanced Conditions                         | 35 |

| 2.3.5.1.1. Simplified Calculation of Duty Cycles                       | 37 |

| 2.3.5.2. NTV Modulation                                                | 39 |

| 2.3.5.3. Symmetric Modulation                                          | 42 |

| 2.3.5.4. Virtual-Vector Modulation                       | 44 |

|----------------------------------------------------------|----|

| 2.3.5.5 SPWM                                             | 45 |

| 2.3.5.6 Modified SPWM                                    | 48 |

| 2.4. Chapter References                                  | 49 |

|                                                          |    |

| CHAPTER 3.                                               | 53 |

| A CARRIER-BASED PWM STRATEGY WITH ZERO-SEQUENCE          |    |

| VOLTAGE INJECTION                                        | 53 |

| 3.1. Proposed CB-PWM Strategy                            | 56 |

| 3.2. Simulation Results                                  | 65 |

| 3.3. Experimental Results                                | 70 |

| 3.4. Conclusions of the Chapter                          | 72 |

| 3.5. Chapter References                                  | 72 |

|                                                          |    |

| CHAPTER 4.                                               | 75 |

| CARRIER-BASED PWM USING TWO MODULATION SIGNALS PER       |    |

| PHASE                                                    | 75 |

| 4.1. Double-Signal PWM (DSPWM)                           | 77 |

| 4.1.1. Introduction                                      | 77 |

| 4.1.2. Basis of the Method                               | 78 |

| 4.1.3. Compensation for Imbalances                       | 83 |

| 4.1.4. Control Signals for the Transistors               | 84 |

| 4.1.5. Simulation Results                                | 85 |

| 4.1.6. Experimental Results                              | 90 |

| 4.2. Optimal Compensator and Control Limitation in DSPWM | 92 |

| 4.2.1. Control Strategy                                  | 93 |

| 4.2.2. Maximum Offset and Control Limits                                    | 97  |

|-----------------------------------------------------------------------------|-----|

| 4.1.3. Simulation Results                                                   | 100 |

| 4.1.4. Experimental Results                                                 | 103 |

| 4.3. Chapter Conclusions                                                    | 106 |

| 4.4. Chapter References                                                     | 107 |

| CHAPTER 5.                                                                  | 111 |

| CARRIER-BASED HYBRID PWM                                                    | 111 |

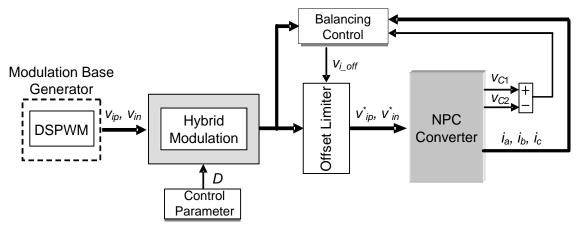

| 5.1. Hybrid PWM Based on SPWM and DSPWM                                     | 113 |

| 5.1.1. Basis of the Method                                                  | 113 |

| 5.1.2. Simulation Results                                                   | 116 |

| 5.1.3. Experimental Results                                                 | 124 |

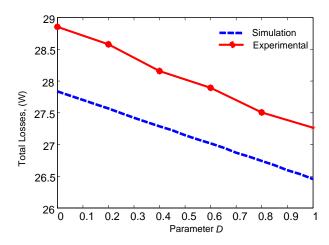

| 5.2. Tracking Method in the Hybrid Modulation                               | 127 |

| 5.2.1. Tracking Method for NP Voltage Oscillation Minimization              | 127 |

| 5.2.2. Simulation Results                                                   | 130 |

| 5.3. Control Loop for the NP Voltage Oscillation Amplitude                  | 132 |

| 5.3.1. Amplitude Control Strategy of the Neutral-Point Voltage oscillations | 133 |

| 5.3.2. Simulation Results                                                   | 133 |

| 5.4. Chapter Conclusions                                                    | 136 |

| 5.5. Chapter References                                                     | 136 |

| CHAPTER 6.                                                                  | 139 |

| MODELING AND CONTROL OF A GRID-CONNECTED NPC                                | 139 |

| CONVERTER                                                                   |     |

| 6.1. Model of a Grid-Connected Multilevel Converter                         | 141 |

| 6.1.1. Large-Signal Model of the System                                     | 141 |

| 6.1.2. Averaged-Signal Model of the System                                                                                                                                                                                                                   | 143                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6.2. Control of the Grid-Connected Converter Working as a Rectifier                                                                                                                                                                                          | 145                      |

| <ul> <li>6.2.1. Control of the Multilevel Converter Using Standard Pl's</li> <li>6.2.1.1 Tuning of the PI Controllers</li> <li>6.2.2. Control of the Multilevel Converter Using a Fuzzy Supervisor</li> <li>6.2.2.1 The Fuzzy Supervisor Strategy</li> </ul> | 145<br>147<br>151<br>152 |

| 6.3. Simulation and Experimental Results                                                                                                                                                                                                                     | 155                      |

| 6.4. Chapter Conclusions                                                                                                                                                                                                                                     | 156                      |

| 6.5. Chapter References                                                                                                                                                                                                                                      | 157                      |

| CHAPTER 7.                                                                                                                                                                                                                                                   | 159                      |

| WIND-TURBINE CONTROL APPLICATION                                                                                                                                                                                                                             | 159                      |

| 7.1. Wind Generation                                                                                                                                                                                                                                         | 160                      |

| <ul><li>7.1.1 Wind Turbine Configurations</li><li>7.1.2 Ac-dc-ac Power Electronic Topologies</li><li>7.1.3 Control Strategies</li></ul>                                                                                                                      | 160<br>161<br>163        |

| 7.2. Wind Energy Conversion System Modeling                                                                                                                                                                                                                  | 164                      |

| 7.2.1 Wind Turbine Modeling                                                                                                                                                                                                                                  | 164                      |

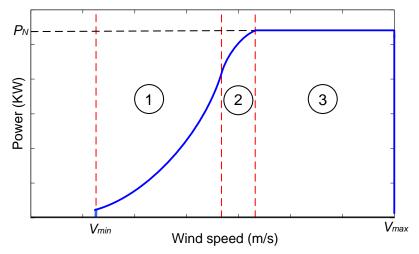

| 7.3. Variable-Speed Wind Turbine Systems                                                                                                                                                                                                                     | 166                      |

| <ul><li>7.3.1. Variable Speed Control Reference</li><li>7.3.2. PMSG Modeling</li></ul>                                                                                                                                                                       | 166<br>167               |

| 7.4. Field-Oriented Control Strategy                                                                                                                                                                                                                         | 169                      |

| 7.4.1. Tuning the PIs 7.4.2. Experimental Results 7.4.2.1 System Description 7.4.2.2 Experimental Results                                                                                                                                                    | 170<br>175<br>175<br>176 |

| 7.5. Chapter Conclusions                              | 180 |

|-------------------------------------------------------|-----|

| 7.6. Chapter References                               | 180 |

|                                                       |     |

| CHAPTER 8.                                            | 185 |

| CONCLUSIONS AND FUTURE RESEARCH                       | 185 |

| 8.1. Conclusions                                      | 186 |

| 8.2. Main Contributions                               | 188 |

| 8.3. Publications and Patents Derived from the Thesis | 190 |

| 8.4. Future Research                                  | 194 |

|                                                       |     |

| APPENDICES A, B, C, D, E and F                        | 197 |

| APPENDIX A                                            | 298 |

| A.1. Switch Status in an NPC Converter                | 298 |

| APPENDIX B                                            | 202 |

| B.1. Switching Model of an NPC Converter              | 202 |

| APPENDIX C                                            | 203 |

| C.1. Power Losses                                     | 203 |

| APPENDIX D                                            | 206 |

| D.1. Harmonic Distortion                              | 206 |

| APPENDIX E                                            | 206 |

| E.1. Normalized NP Voltage Ripple                     | 206 |

| APPENDIX F                                            | 207 |

| F.1. Parameters of the PMSG and Controllers           | 207 |

# **List of Figures**

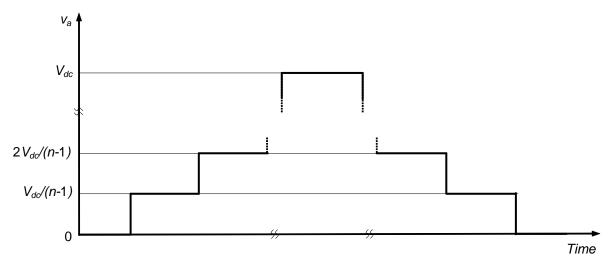

| Fig.2.1. Example of voltage waveform generated by an n-level converter.                                                                                | 13 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

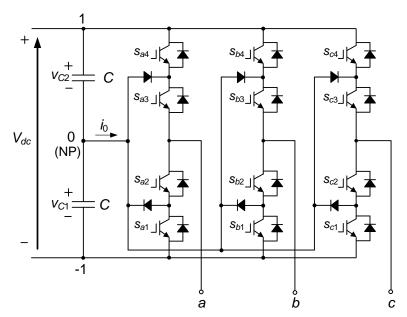

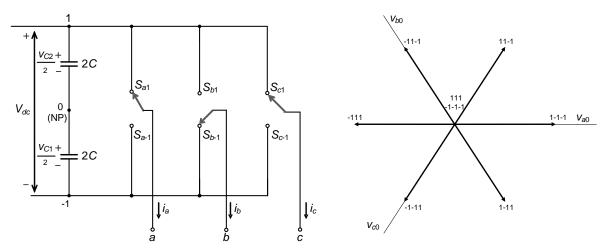

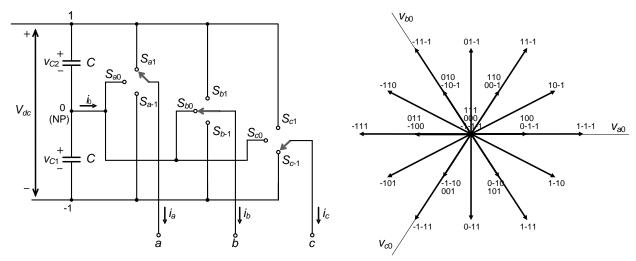

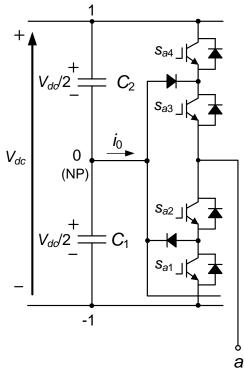

| Fig.2.2. Three-level diode-clamped converter.                                                                                                          | 14 |

| Fig.2.3. Diode-clamped multilevel converters (one phase leg): (a) four-, and (b) five-level topologies.                                                | 15 |

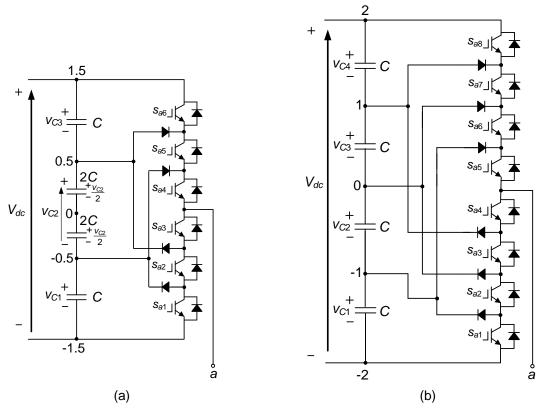

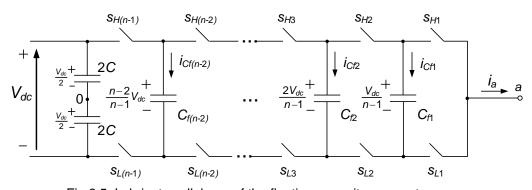

| Fig.2.4. (a) Three-level and (b) four-level floating-capacitor converters.                                                                             | 18 |

| Fig.2.5. Imbricate cell, base of the floating-capacitor converter.                                                                                     | 18 |

| Fig.2.6. Transitions between consecutive voltage levels.                                                                                               | 20 |

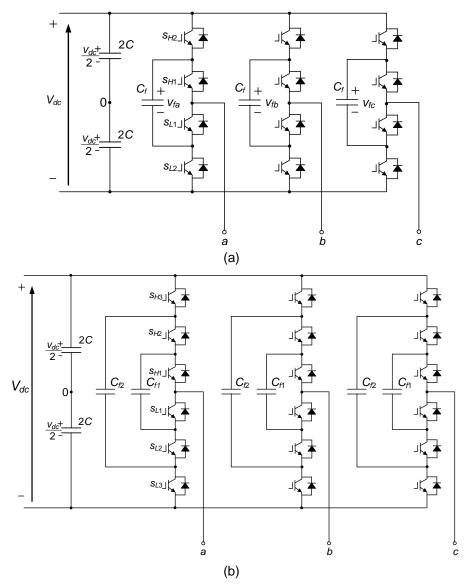

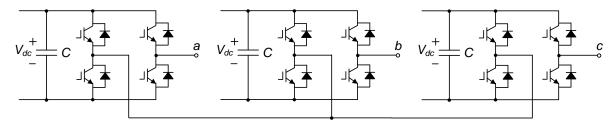

| Fig.2.7. Three-level converter.                                                                                                                        | 21 |

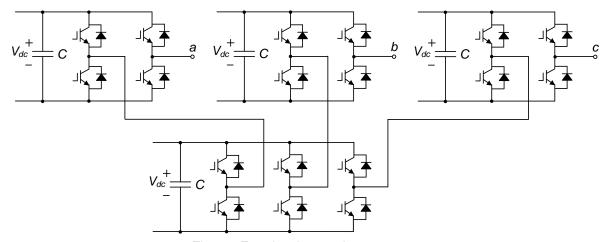

| Fig.2.8. Multilevel cascade converter.                                                                                                                 | 21 |

| Fig.2.9. Four-level cascade converter.                                                                                                                 | 22 |

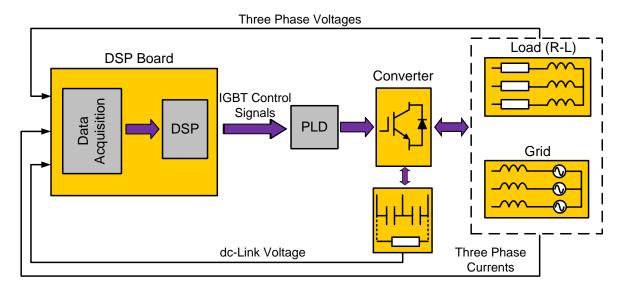

| Fig.2.10. General diagram of the experimental platform.                                                                                                | 24 |

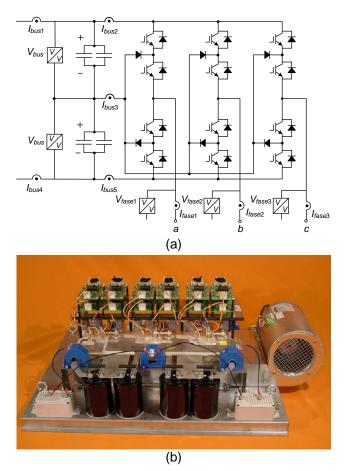

| Fig.2.11. NPC converter: (a) general diagram, and (b) converter set up.                                                                                | 25 |

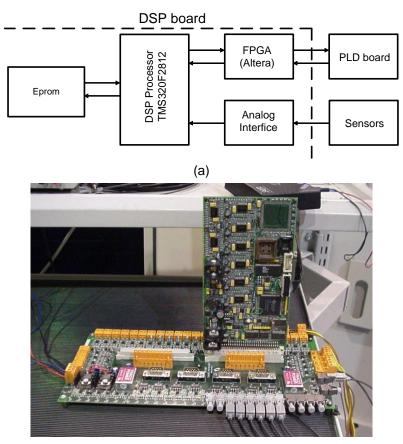

| Fig.2.12. Control hardware: (a) architecture and (b) DSP board.                                                                                        | 26 |

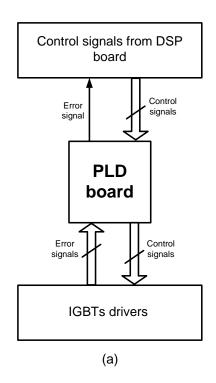

| Fig.2.13. PLD board and IGBTs drivers: bloc diagram and, b) building.                                                                                  | 27 |

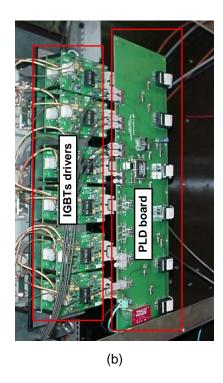

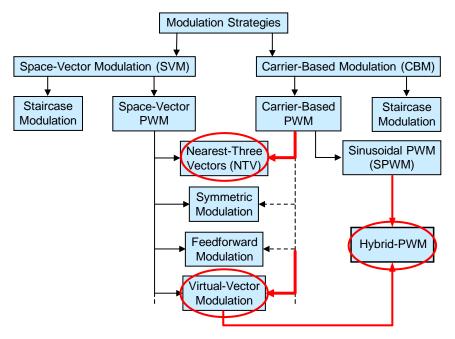

| Fig.2.14. Classification of modulation strategies.                                                                                                     | 28 |

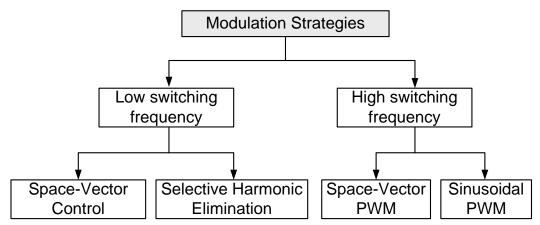

| Fig.2.15. Clarke's Transformation: (a) director vectors, and (b) example of spatial vector for $v_{a0}$ =200 V, $v_{b0}$ =300 V, and $v_{c0}$ =-100 V. | 30 |

| Fig.2.16. SV diagram of the two-level converter.                                                                                                       | 30 |

| Fig.2.17. SV diagram of the three-level converter.                                                                                                     | 31 |

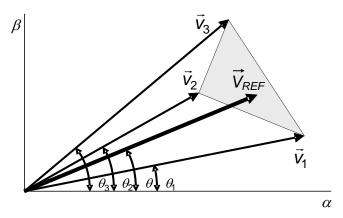

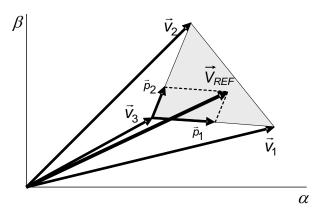

| Fig.2.18. Limiting area to generate the reference vector ( $V_{\!\scriptscriptstyle REF}$ ) by using three vectors.                                                          | 32 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.2.19. Boundary of the area, determined when $d_3=0$ .                                                                                                                    | 33 |

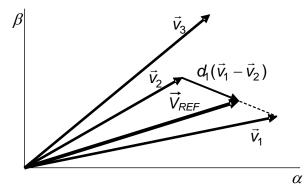

| Fig.2.20. Projections of the reference vector $\vec{V}_{REF}$ ( $\vec{p}_1$ and $\vec{p}_2$ ).                                                                               | 34 |

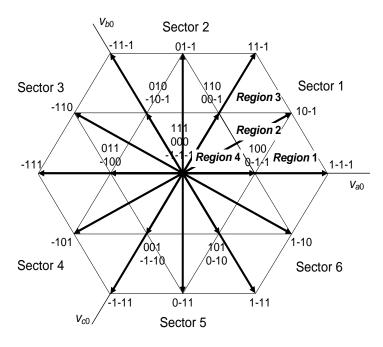

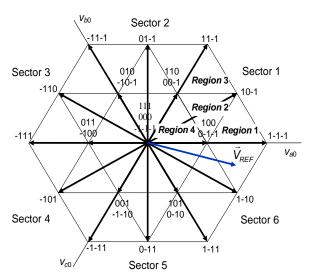

| Fig.2.21. Three-level vector diagram divided into sectors and regions.                                                                                                       | 36 |

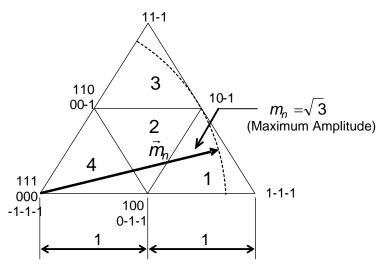

| Fig.2.22. Maximum length of the normalized reference vector in steady-state conditions.                                                                                      | 37 |

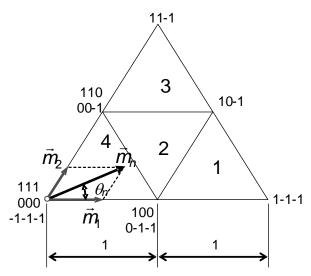

| Fig.2.23. Projections of the normalized reference vector in the first sector.                                                                                                | 38 |

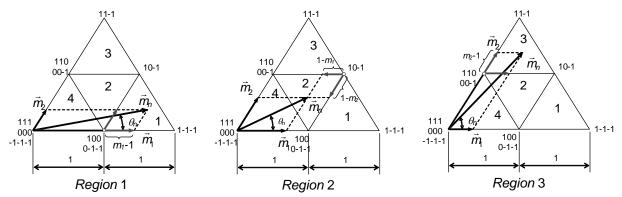

| Fig.2.24. Projections for Regions 1, 2 and 3.                                                                                                                                | 39 |

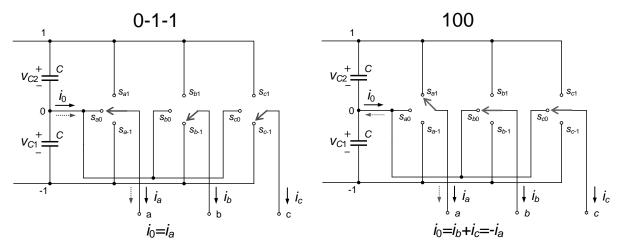

| Fig.2.25. Example of control of the NP current by proper selection of the double vectors. Vector 0-1-1 produces $i_0=i_a$ , whereas vector 100 produces $i_0=i_b+i_c=-i_a$ . | 40 |

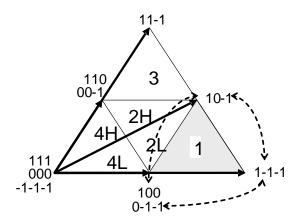

| Fig.2.26. New regions for symmetric modulation. Example of vector sequence for Region 1.                                                                                     | 43 |

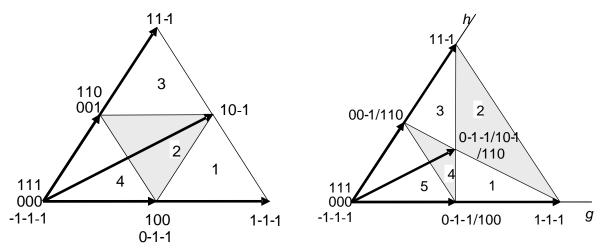

| Fig.2.27. Triangular regions in the first sector of the space-vector diagram for: (a) standard modulation techniques and (b) the modulation based on virtual vectors.        | 44 |

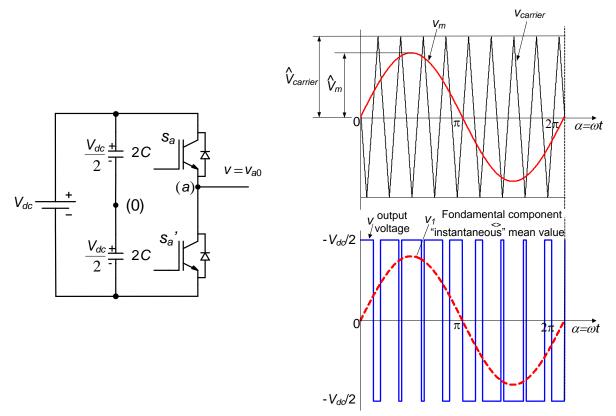

| Fig.2.28. Output voltage representation using SPWM.                                                                                                                          | 46 |

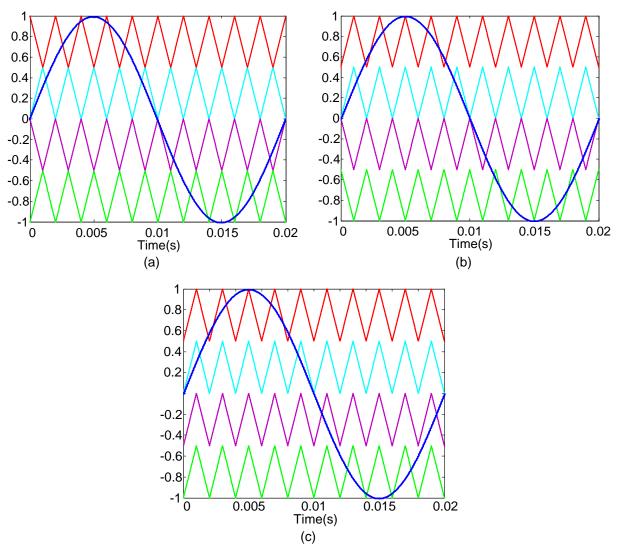

| Fig.2.29. Examples of the three techniques. (a) APO, (b) PO and (c) PH.                                                                                                      | 47 |

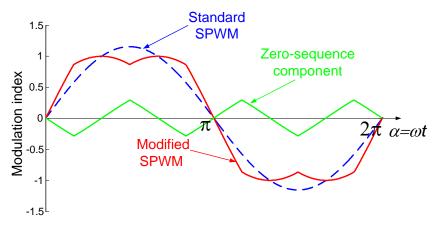

| Fig.2.30. Modified SPWM.                                                                                                                                                     | 48 |

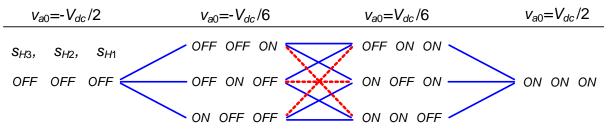

| Fig. 2.4. NDC acquirertor                                                                                                                                                    | 50 |

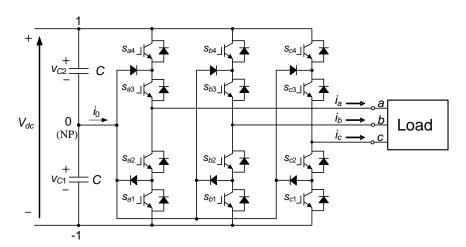

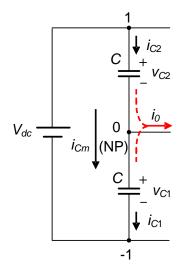

| Fig. 3.1. NPC converter.                                                                                                                                                     | 56 |

| Fig.3.2. SV diagram of the NPC converter.                                                                                                                                    | 56 |

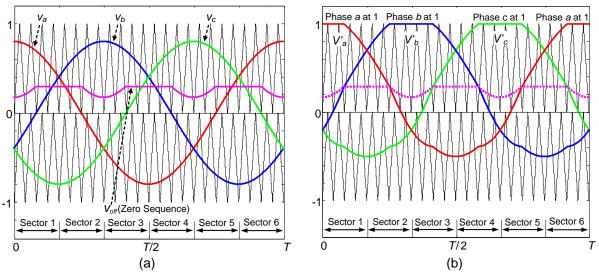

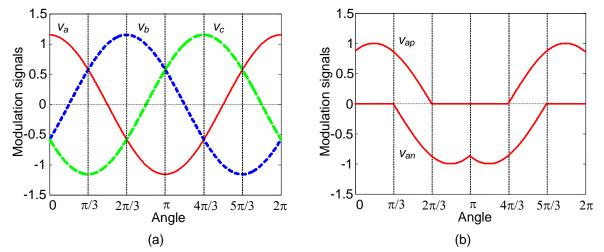

| Fig.3.3. Modulation signals: (a) sinusoidal references, and (b) addition of a positive zero-sequence signal.                                                                 | 59 |

| Fig.3.4. Co-relation between the CB-PWM and NTV-SVM strategy when phase <i>a</i> is clamped to +1: (a) CB-PWM switching sequence, and (b) NTV-SVM strategy.                  | 60 |

| Fig.3.5. Co-relation between the CB-PWM and NTV-SVM strategy when phase <i>b</i> is clamped to 0: (a) CB-PWM switching sequence, and (b) NTV-SVM strategy.                   | 61 |

| Fig.3.6. Co-relation between the CB-PWM and NTV-SVM strategy when phase $c$ is clamped to -1: (a) CB-PWM switching sequence, and (b) NTV-SVM strategy.                       | 61 |

| Fig.3.7. Modification of the modulation signals by adding the proposed zero-sequence signal to balance the voltage.                                                          | 65 |

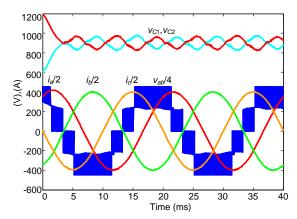

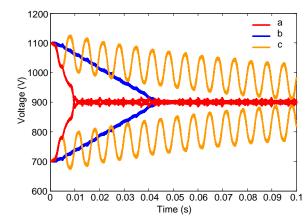

| Fig. 3.8. Simulation results of the proposed CB-PWM: (a) $m=1$ : (b) $m=0.8$ : (c) $m=0.6$ : (d)                                                                             |    |

| m=0.4.                                                                                                                                        | 66                |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Fig.3.9. Dynamics of the voltage compensator operating on a linear load ( <i>m</i> =0.9).                                                     | 67                |

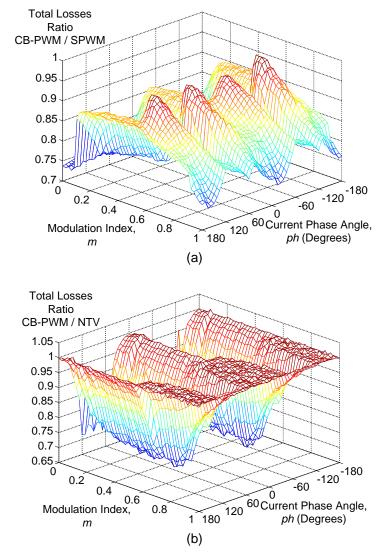

| Fig.3.10. Total losses ratio of the proposed CB-PWM to those of (a) the SPWM strate (b) the NTV-SVM strategy.                                 | gy, and<br>68     |

| Fig.3.11. Normalized amplitude of the low-frequency NP voltage oscillations produced the SPWM strategy, and (b) the proposed CB-PWM strategy. | d by: (a)<br>69   |

| Fig.3.12. Experimental results for the proposed CB-PWM: (a) $m=1$ , (b) $m=0.7$ , and (c)                                                     | <i>m</i> =0.4. 71 |

| Fig.3.13. Dynamics of the voltage compensator operating over a linear load ( <i>m f</i> =50Hz).                                               | ⊫1 and<br>71      |

| Fig.4.1. Three-level diode-clamped converter (or NPC converter).                                                                              | 77                |

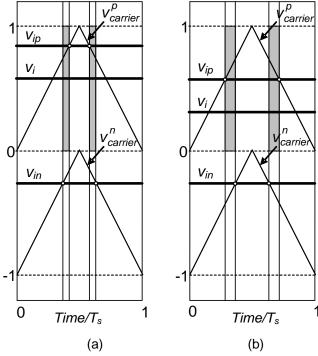

| Fig.4.2. Two possible situations for the calculation of the duty cycle $d_{i0}$ : (a) $v_{in}^{+1} < v_{ip}$ ,                                | and (b)           |

| $V_{in}^{+1} > V_{ip}$ , for $V_{in}^{+1} = V_{in} + 1$ .                                                                                     | 80                |

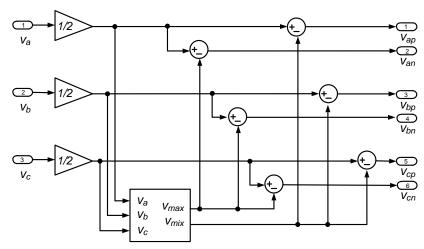

| Fig.4.3. Scheme for the generation of $v_{ip}$ and $v_{in}$ from $v_i$ ( $i = \{a,b,c.$ ).                                                    | 82                |

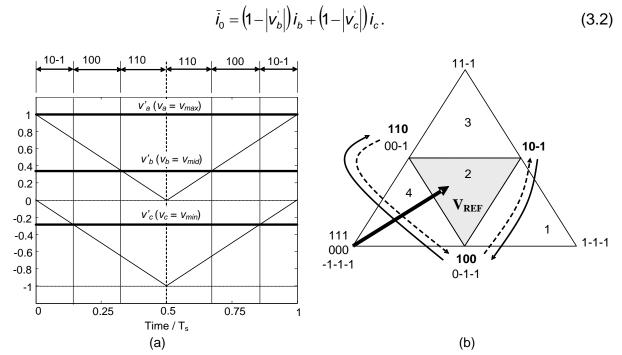

| Fig.4.4. Example of sinusoidal modulation signals: (a) original signals and (b) modified for phase <i>a</i> .                                 | d signal<br>83    |

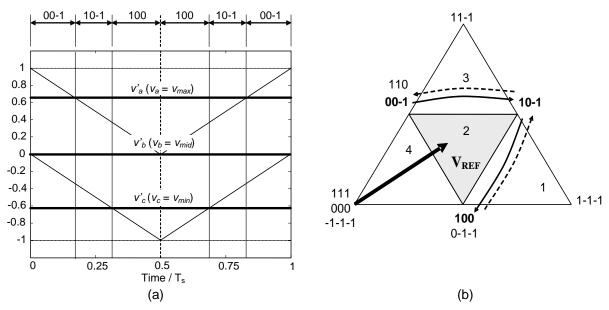

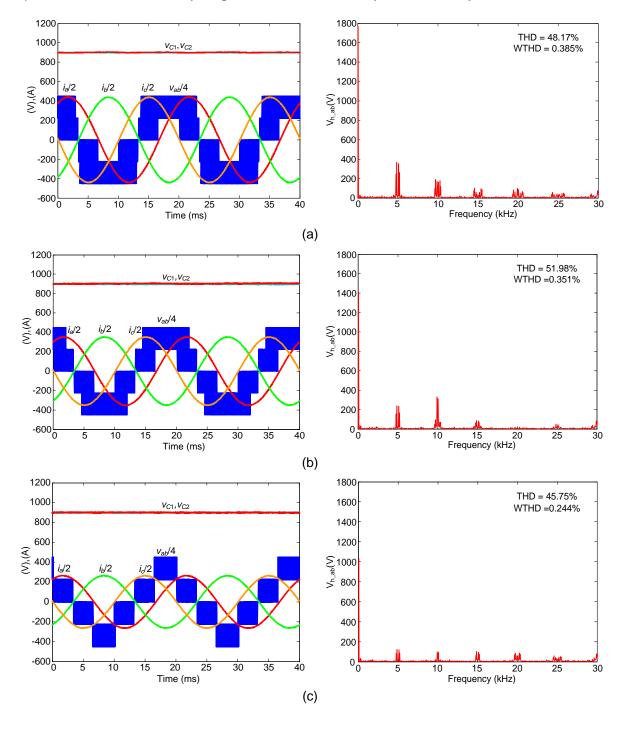

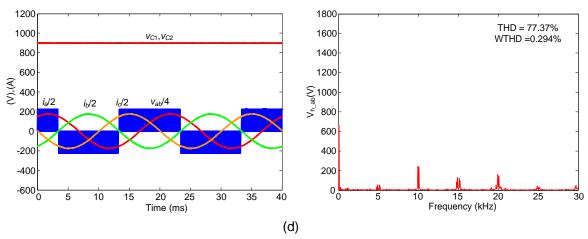

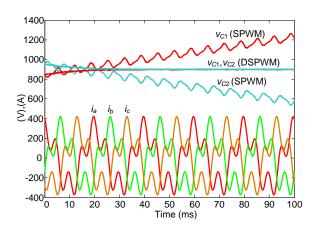

| Fig.4.5. Simulation results of DSPWM: (a) $m=1$ ; (b) $m=0.8$ ; (c) $m=0.6$ ; (d) $m=0.4$ .                                                   | 87                |

| Fig.4.6. Dynamics of the SPWM and DSPWM operating over a nonlinear load.                                                                      | 87                |

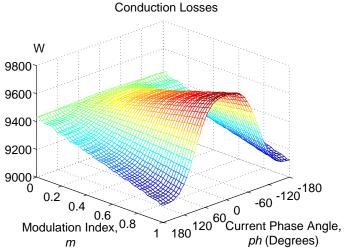

| Fig.4.7. Conduction losses obtained using SPWM and DSPWM.                                                                                     | 88                |

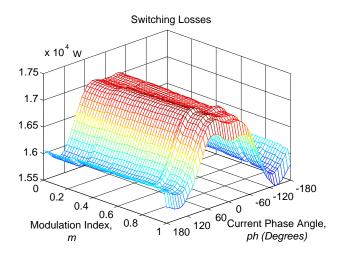

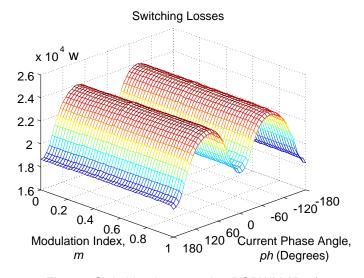

| Fig.4.8. Switching losses using SPWM.                                                                                                         | 88                |

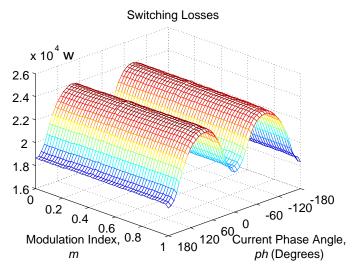

| Fig.4.9. Switching losses using DSPWM.                                                                                                        | 89                |

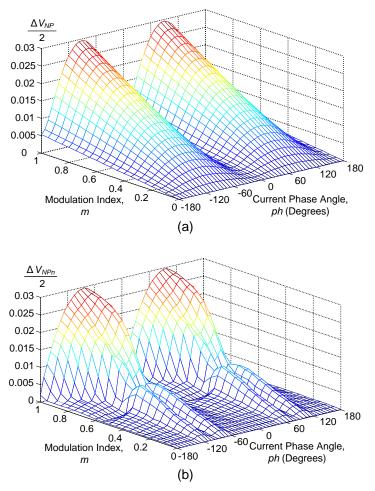

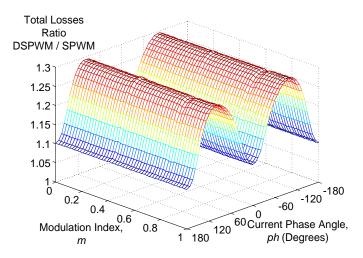

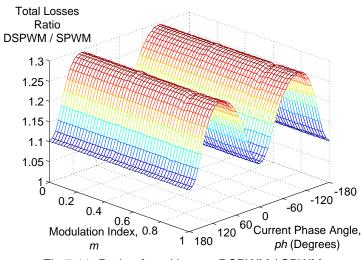

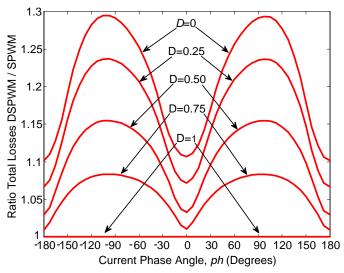

| Fig.4.10. Ratio of total losses DSPWM / SPWM.                                                                                                 | 89                |

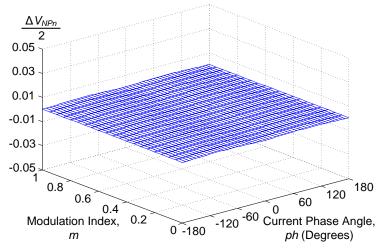

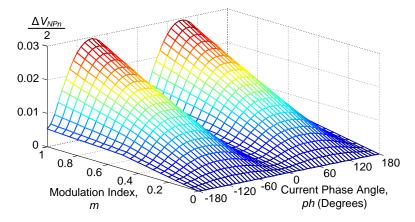

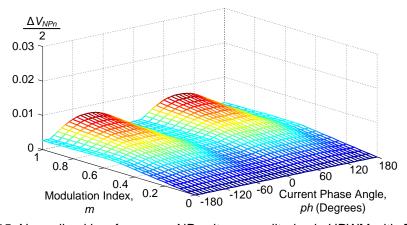

| Fig.4.11. Normalized low-frequency NP voltage amplitudes in DSPWM.                                                                            | 90                |

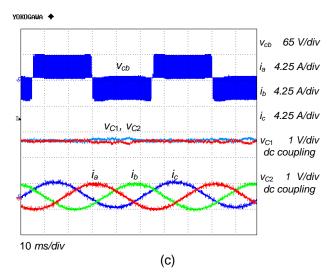

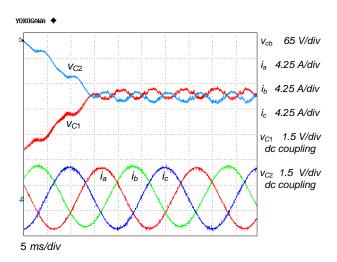

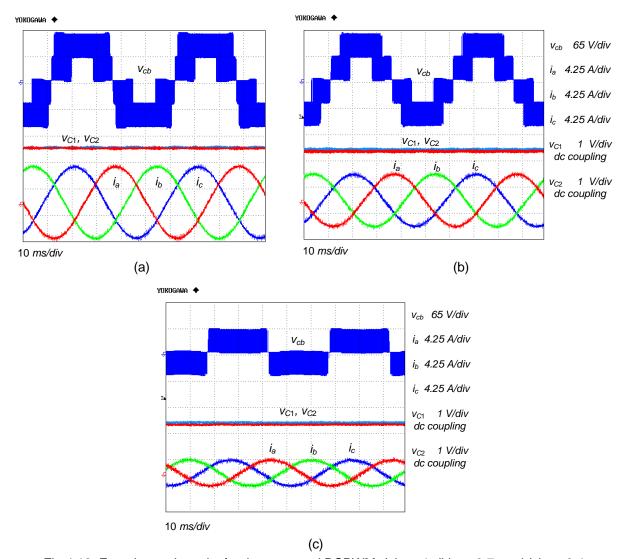

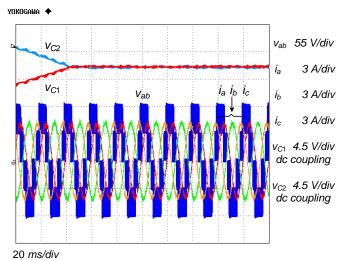

| Fig.4.12. Experimental results for the proposed DSPWM: (a) $m=1$ , (b) $m=0.7$ , and (c) $m=0.7$                                              | <i>m</i> =0.4. 91 |

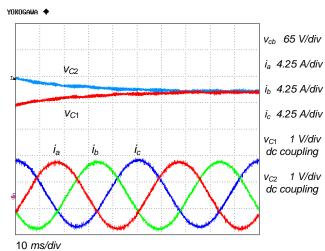

| Fig.4.13. Dynamics of the voltage compensator operating on a linear load ( <i>m</i> =0.9).                                                    | 91                |

| Fig.4.14. Current in the capacitors.                                                                                                          | 94                |

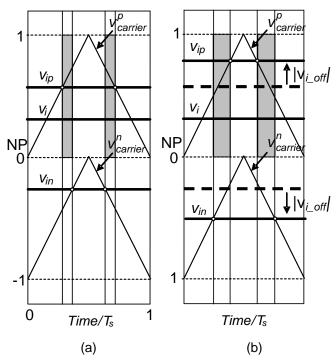

| Fig.4.15. Modulation and carrier signals. (a) No compensation offset added and (b) ex offset added.                                           | cessive<br>98     |

| Fig.4.16. Upper and lower limiting areas for the compensation offset.                                                                         | 99                |

| Fig.4.17. Maximum compensating NP current for sinusoidal output currents.                                                                                            | 100 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

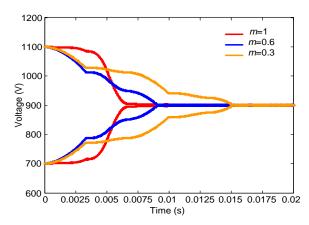

| Fig.4.18. Voltage in the dc-link capacitors using the optimal (Case 'a') and the nonoptimal (Cases 'b' and 'c') compensators.                                        | 102 |

| Fig.4.19. Voltage in the dc-link capacitors under different modulation indices using the optimal compensator.                                                        | 102 |

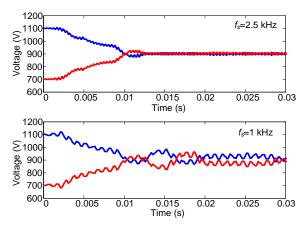

| Fig.4.20. Voltage in the dc-link capacitors using the optimal compensator for a low-switching frequency operation.                                                   | 103 |

| Fig.4.21. Comparison of voltage balancing dynamics operating with zero power factor for DSPWM with the optimal compensator and NTV.                                  | 103 |

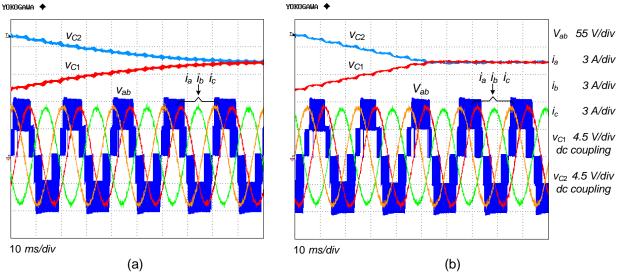

| Fig.4.22. Nonoptimal compensator: (a) with a limiter of ±1, and (b) with a limiter of ±0.03.                                                                         | 104 |

| Fig.4.23. Optimal compensator.                                                                                                                                       | 104 |

| Fig.4.24. Experimental results with the dynamic limiter and a modulation index $m$ =0.8: (a) nonoptimal voltage-balancing compensator, and (b) proposed compensator. | 105 |

| Fig.4.25. Experimental results with the dynamic limiter and a modulation index m=0.4: (a) nonoptimal voltage-balancing compensator, and (b) proposed compensator.    | 105 |

| Fig.5.1. Scheme of HPWM.                                                                                                                                             | 113 |

| Fig.5.2. Modulation signals for the DSPWM and SPWM techniques.                                                                                                       | 115 |

| Fig.5.3. Modulation signals for the HPWM.                                                                                                                            | 115 |

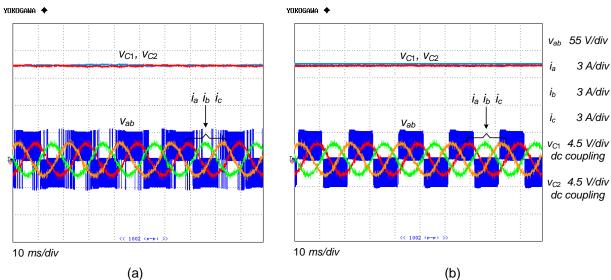

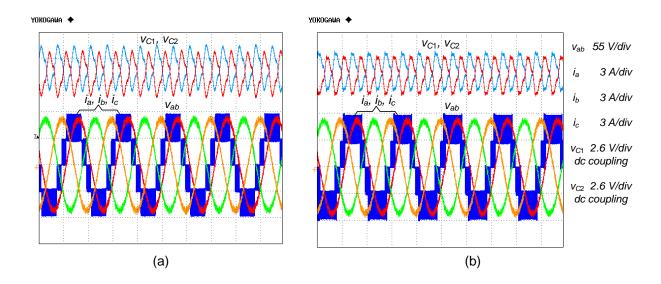

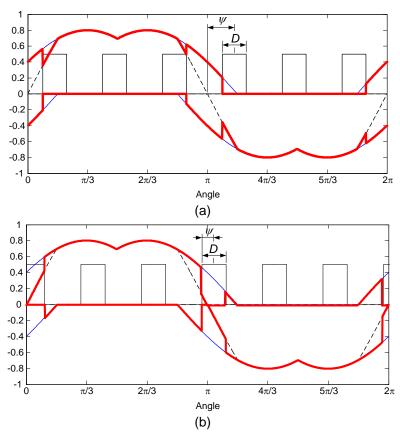

| Fig.5.4. Simulation results of HPWM: (a) <i>D</i> =1; (b) <i>D</i> =0.75; (c) <i>D</i> =0.5; (d) <i>D</i> =0.25; (e) <i>D</i> =0.                                    | 118 |

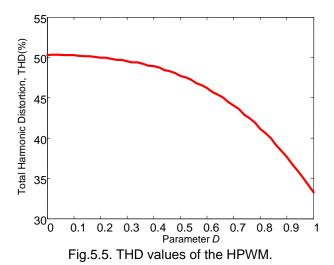

| Fig.5.5. THD values of the HPWM.                                                                                                                                     | 118 |

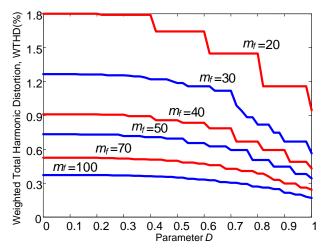

| Fig.5.6. WTHD values of the HPWM.                                                                                                                                    | 119 |

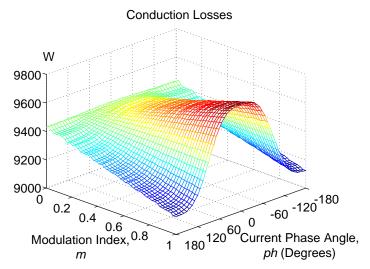

| Fig.5.7. Conduction losses obtained using SPWM, DSPWM, and HPWM with <i>D</i> =0.5.                                                                                  | 120 |

| Fig. 5.8. Switching losses using SPWM ( <i>D</i> =1).                                                                                                                | 120 |

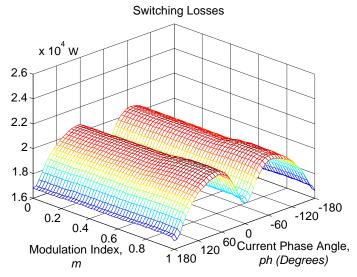

| Fig. 5.9. Switching losses using DSPWM ( <i>D</i> =0).                                                                                                               | 120 |

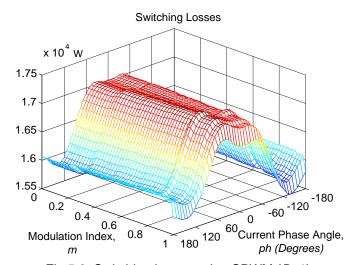

| Fig.5.10. Switching losses using HPWM for <i>D</i> =0.5.                                                                                                             | 121 |

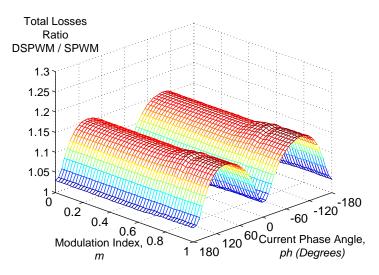

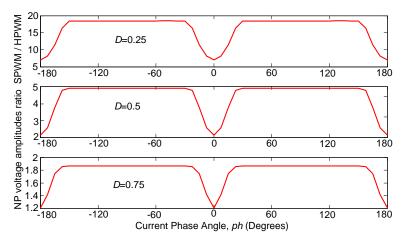

| Fig.5.11. Ratio of total losses DSPWM / SPWM.                                                                                                                        | 121 |

| Fig.5.12. Ratio of total losses HPWM / SPWM for <i>D</i> =0.5.                                                                                                       | 122 |

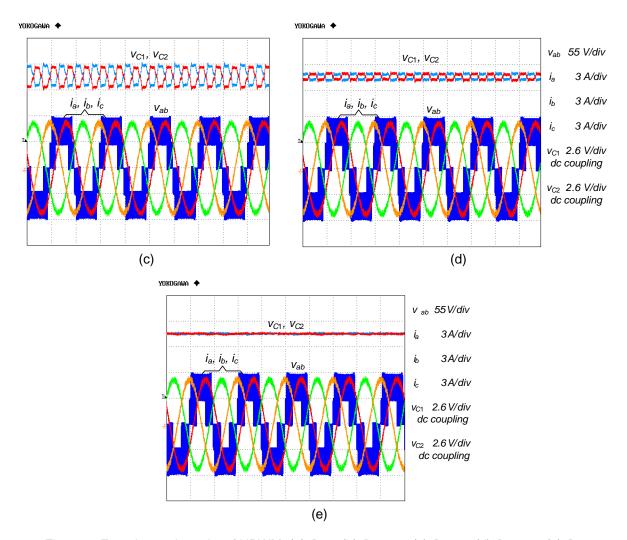

| Fig.5.13. Ratio of total losses HPWM / SPWM for different <i>D</i> values.                                                                                           | 122 |

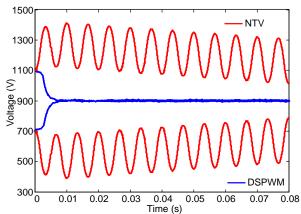

| Fig.5.14. Normalized low-frequency NP voltage amplitudes in SPWM.                                                                    | 123 |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig.5.15. Normalized low-frequency NP voltage amplitudes in HPWM with <i>D</i> =0.5.                                                 | 123 |

| Fig.5.16. Normalized low-frequency NP voltage amplitudes in SPWM.                                                                    | 124 |

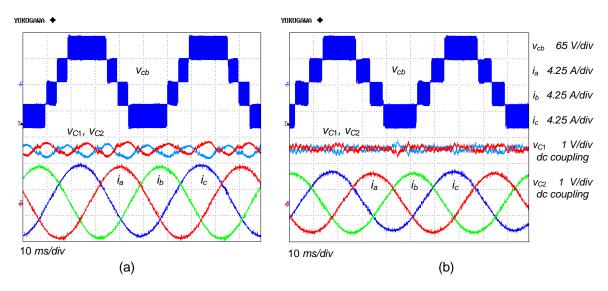

| Fig.5.17. Experimental results of HPWM: (a) <i>D</i> =1; (b) <i>D</i> =0.75; (c) <i>D</i> =0.5; (d) <i>D</i> =0.25; (e) <i>D</i> =0. | 126 |

| Fig.5.18. Power losses from the low-power prototype.                                                                                 | 127 |

| Fig.5.19. Clamping intervals defined from the parameters $D$ and $\psi$ .                                                            | 128 |

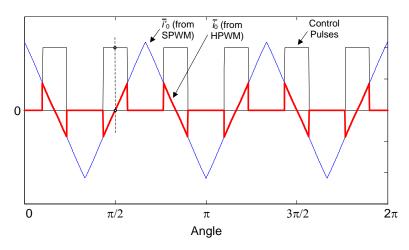

| Fig.5.20. Tracking example.                                                                                                          | 129 |

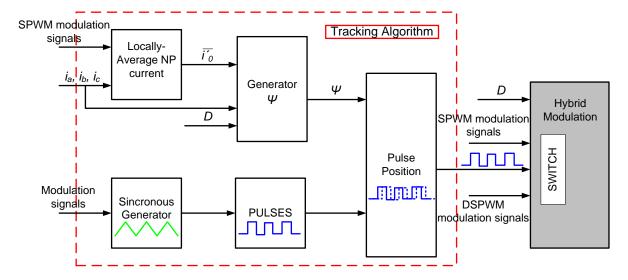

| Fig.5.21.Tracking algorithm.                                                                                                         | 130 |

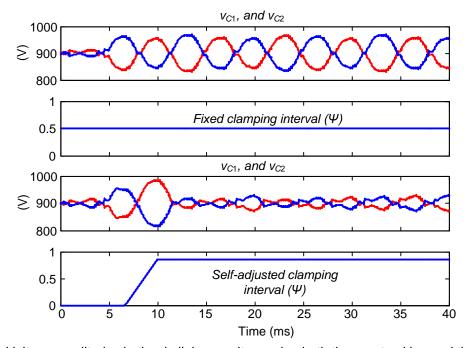

| Fig.5.22. Voltage amplitudes in the dc-link capacitors using both the non-tracking and the tracking.                                 | 131 |

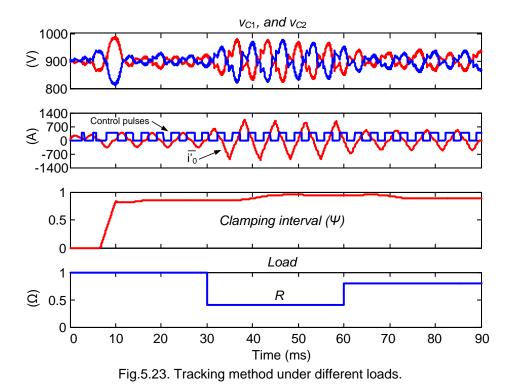

| Fig.5.23. Tracking method under different loads.                                                                                     | 131 |

| Fig.5.24. System Structure.                                                                                                          | 132 |

| Fig.5.25. Control strategy.                                                                                                          | 134 |

| Fig.5.26. Simulation results for different NP voltage amplitude reference values.                                                    | 135 |

| Fig.5.27. Protection algorithm verification.                                                                                         | 135 |

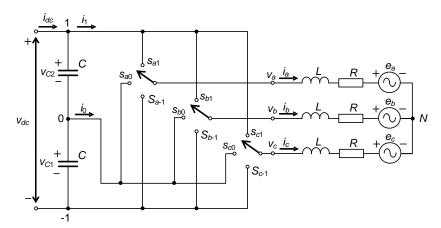

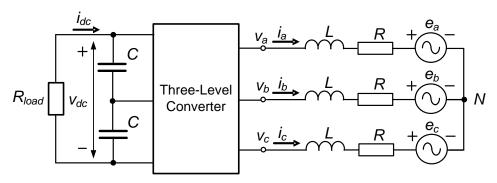

| Fig.6.1. Grid-connected NPC converter.                                                                                               | 141 |

| Fig.6.2. Grid-connected converter operating as a rectifier.                                                                          | 145 |

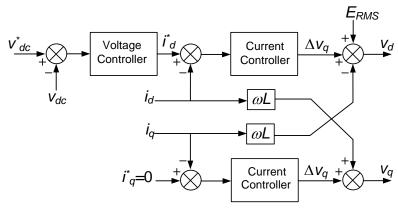

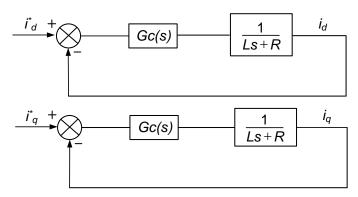

| Fig.6.3. Decoupled PI controller.                                                                                                    | 146 |

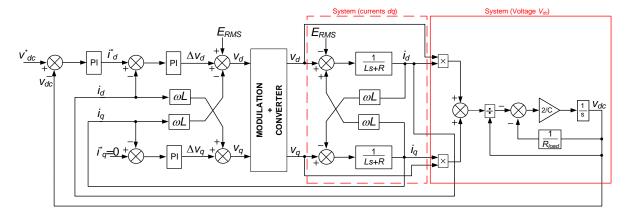

| Fig.6.4. Model and control of the grid-connected converter.                                                                          | 148 |

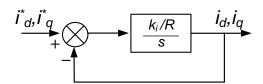

| Fig.6.5. Current control loop.                                                                                                       | 148 |

| Fig.6.6. Current control loop with zero-pole cancelation.                                                                            | 148 |

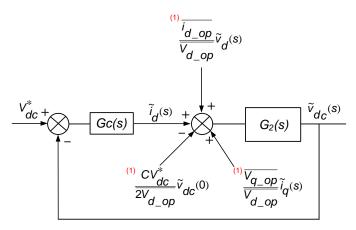

| Fig.6.7. Voltage control loop.                                                                                                       | 150 |

| Fig.6.8. Control structure.                                                                                                          | 151 |

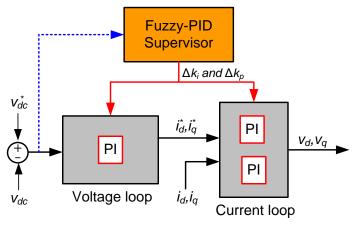

| Fig.6.9. Control Structure based with Fuzzy-PID.                                                                                     | 153 |

| Fig.6.10. Example of the strategy pole-zero cancelation.                                                                             | 154 |

| Fig.6.11. Membership functions for <i>e</i> and <i>ce</i> .                                                                          | 154 |

| Fig.6.12. Resulting input-output supervisor surface.                                                                                 | 154 |

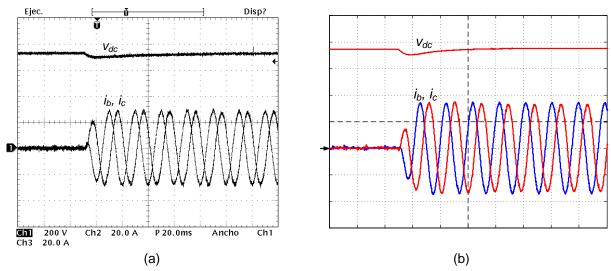

| Fig.6.13. Dynamics of the dc voltage and two currents using VOC: (a) experimental results, and (b) simulation results.                         | 155 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig.6.14. Dynamics of the dc voltage and two currents using VOC with a Fuzzy supervisor: (a) experimental results, and (b) simulation results. | 156 |

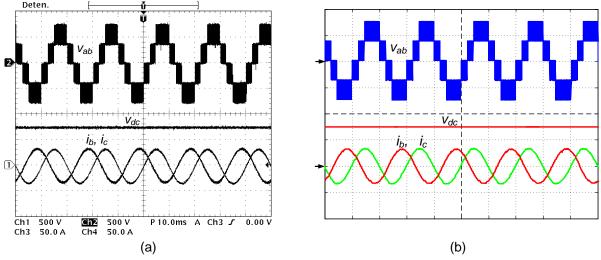

| Fig.6.15. Results under steady-state conditions: (a) experimental results, and (b) simulation results.                                         | 156 |

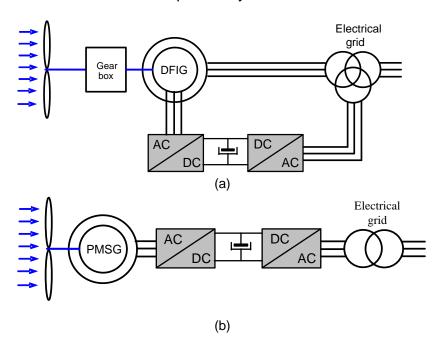

| Fig.7.1. Variable-speed WT systems: (a) double-fed induction generator and (b) permanent-magnet synchronous generator.                         | 160 |

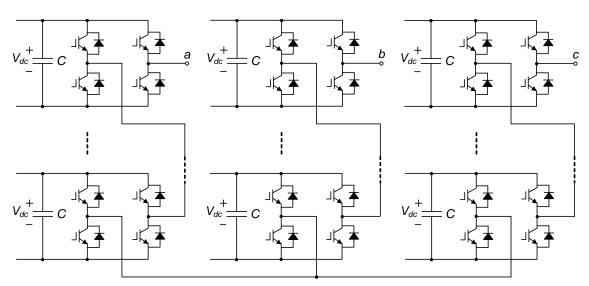

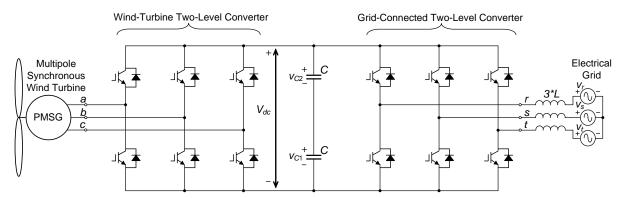

| Fig.7.2. Back-to-back-connected conventional two-level converters.                                                                             | 161 |

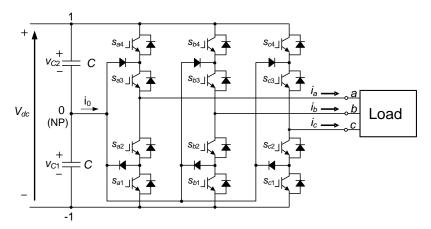

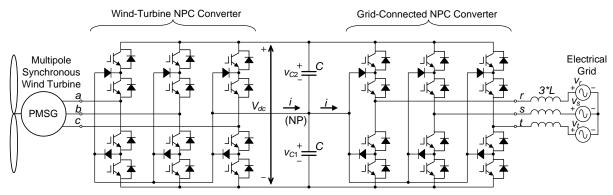

| Fig.7.3. Back-to-back-connected NPC converters.                                                                                                | 162 |

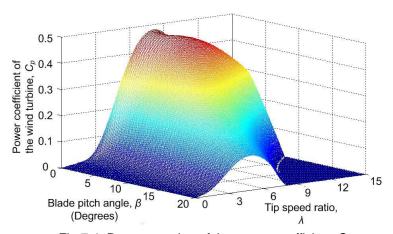

| Fig.7.4. Representation of the power coefficient $C_p$ .                                                                                       | 165 |

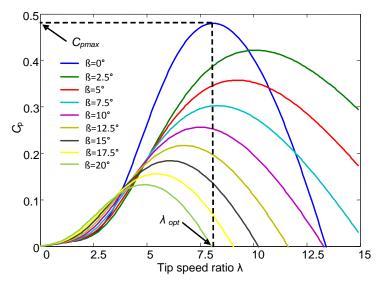

| Fig.7.5. Power coefficient $C_p$ for constant values of $\beta$ .                                                                              | 166 |

| Fig.7.6. Control regions for the WT.                                                                                                           | 167 |

| Fig.7.7 Electrical and mechanical model of the PMSG.                                                                                           | 168 |

| Fig.7.8. Model and control of the wind turbine system.                                                                                         | 169 |

| Fig.7.9. Current and speed control loops after compensating the known terms                                                                    | 170 |

| Fig.7.10. Simplified FOC scheme applied to the WT system.                                                                                      | 170 |

| Fig.7.11. Control configuration.                                                                                                               | 171 |

| Fig.7.12. Root-locus of the speed controller: (a) IDF ( $D_f = 0.707$ ) and (b) ZPC tuning strategies.                                         | 172 |

| Fig.7.13. Step response with a settling time of $T_r = 0.5$ s: (a) IDF strategy with and without pre-filter and (b) ZPC strategy.              | 173 |

| Fig.7.14. Disturbance load effect.                                                                                                             | 174 |

| Fig.7.15. Energy increment ratio (%): (a) average wind of 8 m/s and (b) 6 m/s.                                                                 | 174 |

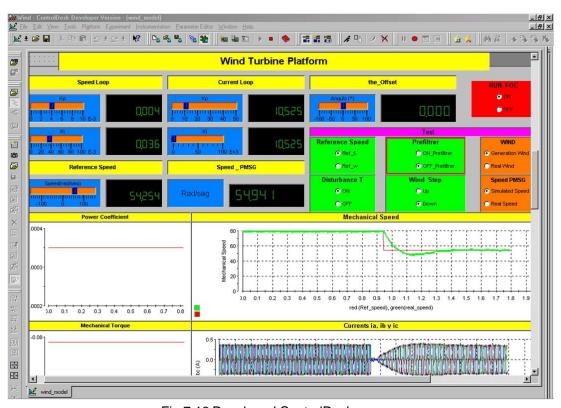

| Fig.7.16 Developed ControlDesk screen.                                                                                                         | 175 |

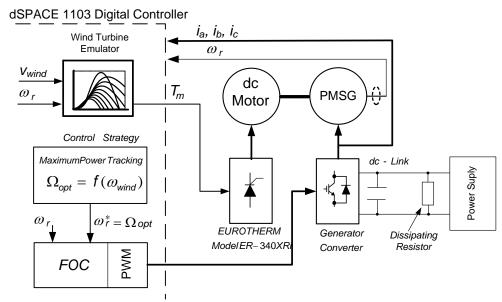

| Fig.7.17. Block diagram of the experimental platform.                                                                                          | 176 |

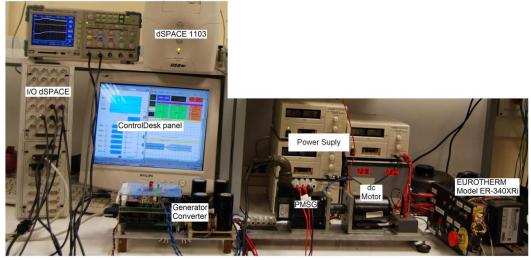

| Fig.7.18. View of the experimental setup.                                                                                                      | 176 |

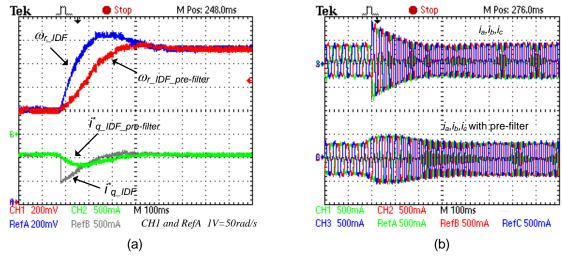

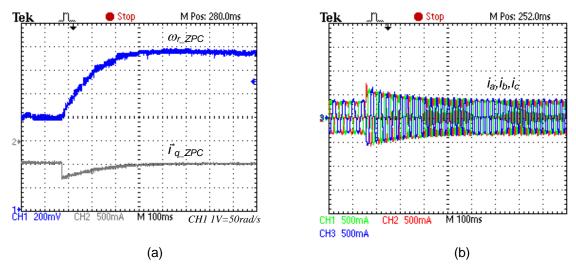

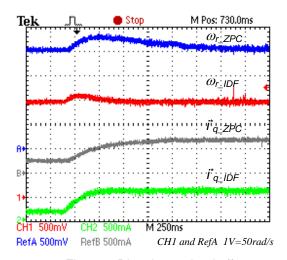

| Fig.7.19. Step response with and without a pre-filter using the IDF: (a) mechanical speed and                                                  |     |

| reference current and (b) PMSG currents.                                                                                                             | 177 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig.7.20. Step response using the ZPC strategy: (a) mechanical speed and reference current, and (b) PMSG currents.                                   | 178 |

| Fig.7.21. Disturbance load effect.                                                                                                                   | 178 |

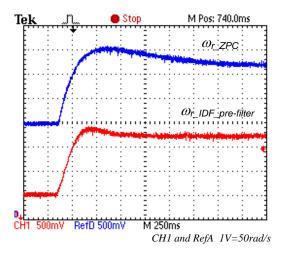

| Fig.7.22. PMSG speed response when a wind step is applied.                                                                                           | 179 |

| Fig.7.23. Experimental results shown in the ControlDesk panel.                                                                                       | 179 |

|                                                                                                                                                      | 400 |

| Fig.8.1. Space vector modulation strategies.                                                                                                         | 186 |

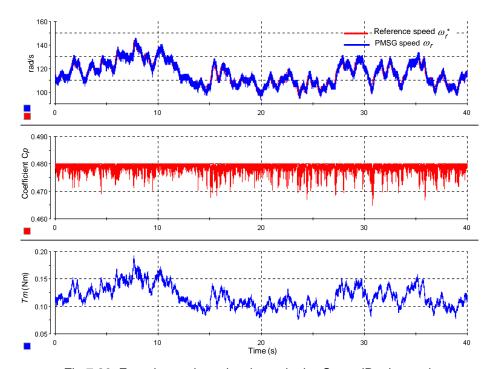

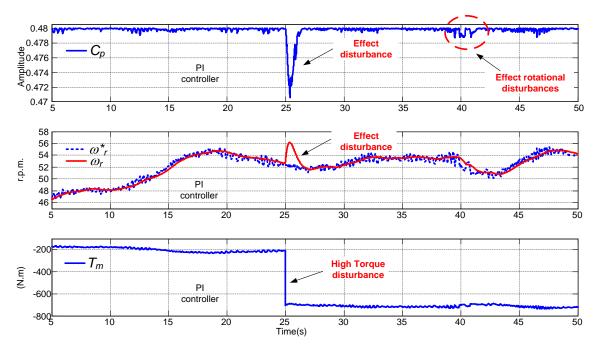

| Fig.8.2. PI controller performance. (a) Power Coefficient, $C_p$ ; (b) rotor speed, $\omega_r$ ; and (c) Mechanical torque, $T_m$ .                  | 196 |

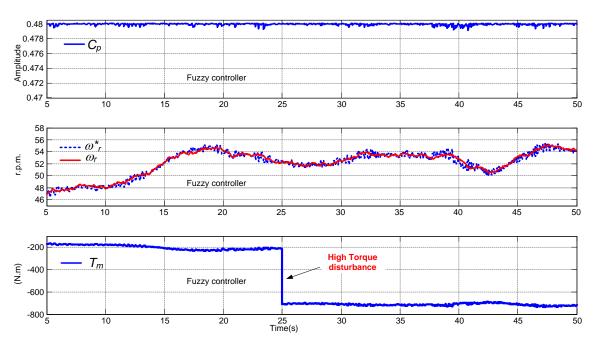

| Fig.8.3. Fuzzy controller performance. (a) Power Coefficient, $C_p$ ; (b) rotor speed, $\omega_r$ ; and (c) Mechanical torque, $T_m$ .               | 196 |

| Fig.A.1. An NPC converter leg.                                                                                                                       | 198 |

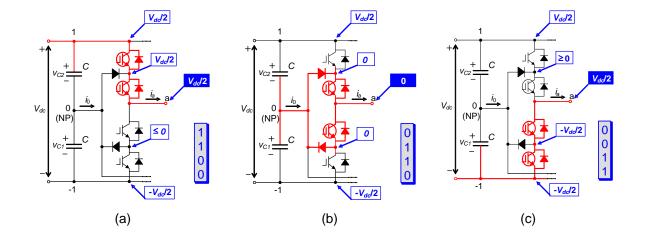

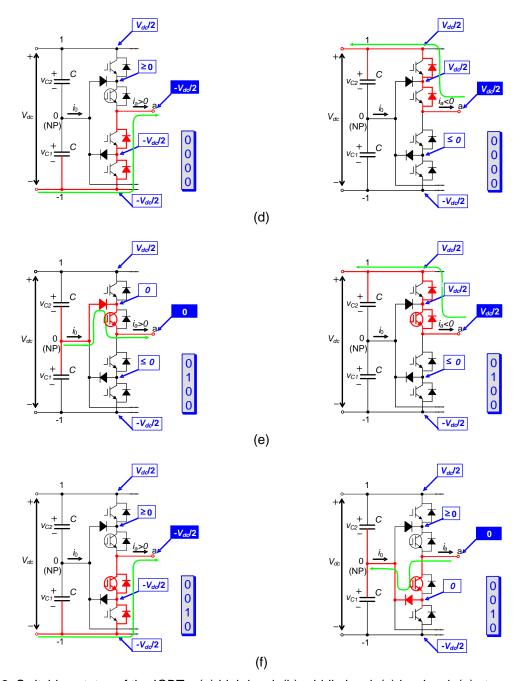

| Fig.A.2. Switching states of the IGBTs: (a) High level, (b) Middle level, (c) Low level, (e) Stopped level and (f) Available for transitions levels. | 200 |

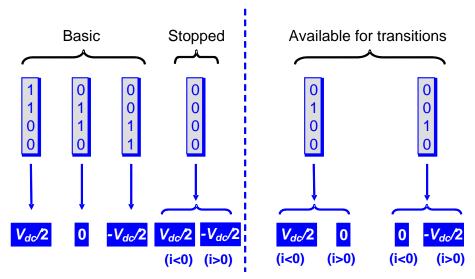

| Fig.A.3. Summary of feasible states.                                                                                                                 | 201 |

| Fig.A.4. Feasible states and transitions.                                                                                                            | 201 |

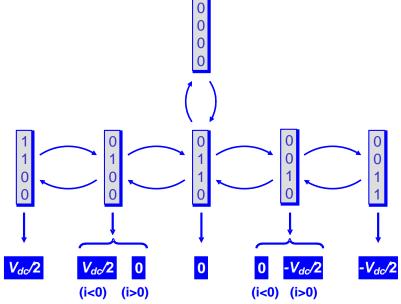

| Fig.A.5. Sequence in both directions.                                                                                                                | 201 |

| Fig.B.1.Grid-connected NPC converter.                                                                                                                | 202 |

| Technical University of Catalonia |

|-----------------------------------|

|-----------------------------------|

## **List of Tables**

| Table 2.1. Switching states of an NPC converter.                                                                                                                            | 14       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 2.2. Switching states and output voltages: (a) four-, and (b) five-level topologies.                                                                                  | 15       |

| Table 2.3. Possible states of the switches in (a) the three-level, and (b) the four-level floating capacitor converters.                                                    | g-<br>19 |

| Table 2.4. Summarizes the general characteristics of basic multilevel topologies.                                                                                           | 23       |

| Table 2.5. Summary of information for the SVM.                                                                                                                              | 39       |

| Table 2.6. (a) Criteria for selection between vectors 0-1-1 and 100, and vectors 00-1 and 110 and (b) equivalences of currents to process calculations in the first sector. | 0;<br>40 |

| Table 2.7. Sequences of vectors in the first sector by NTV modulation.                                                                                                      | 41       |

| Table 2.8. Sequences of vectors in the first sector by symmetric modulation.                                                                                                | 43       |

|                                                                                                                                                                             |          |

| Table 3.1. Vector Sequences in Sector 1.                                                                                                                                    | 59       |

| Table 3.2. Actions to Help Balance the Voltage.                                                                                                                             | 63       |

| Table 3.3. Determination of the Sector.                                                                                                                                     | 64       |

|                                                                                                                                                                             |          |

| Table 4.1. Possible cases for simplification.                                                                                                                               | 96       |

| Table 4.2. Possible cases per phase.                                                                                                                                        | 97       |

| Table 4.3. Calculated values for the simulation conditions in Fig.4.19.                                                                                                     | 102      |

|                                                                                                                                                                             |          |

| Table 6.1. Rule table of the fuzzy supervisor.                                                                                                                              | 154      |

| Table 6.2. Parameters of the Fuzzy Controller.                       | 155 |

|----------------------------------------------------------------------|-----|

| Table 6.3. Parameters of the PI's Controller.                        | 155 |

|                                                                      |     |

| Table A1.Possible states of the switches.                            | 199 |

| Table C1. Parameters of the IGBTs for calculating conduction losses. | 205 |

| Table C2. Parameters of the IGBTs for calculating switching losses.  | 206 |

| Table F1. Parameters of the machine.                                 | 207 |

| Table F2. Parameters of the controllers.                             | 207 |

### List of Abbreviations and Acronyms

A/D: analog-to-digital (converter)

ac: alternating current

AVG: average

CB: carrier-based

D/A: digital-to-analog (converter)

dc: direct current

DFIG: double-fed induction generation

DEE: Department of Electronic Engineering

DTC: direct torque control

DSPWM: double-signal pulsewidth modulation

DSP: digital signal processor

EMI: electromagnetic interference

EPE: European conference on Power Electronics and applications

FOC: field-oriented control

HPWM: hybrid pulse-width modulation

PLD: digital logic programmable

IDF: imposed damping factor

IEEE: Institute of Electrical and Electronics Engineers

IGBT: insulated gate bipolar transistor

LQR: linear quadratic regulator

max: maximum min: minimum

NP: neutral point

NPC: neutral-point-clamped (converter)

NTV: nearest-three-vector (modulation)

PESC: Power Electronics Specialists Conference

PF: power factor

ph: phase

PD: proportional derivative

PI: proportional integral

PID: proportional integral derivative

PMSG: permanent-magnet synchronous generator

PWM: pulse-width modulation

RMS: root mean square

SHE: selective harmonic eleminatuion

SPWM: sinusoidal pulse-width modulation

SV: space vector

SVM: space-vector modulation

SV-PWM: space-vector pulse-width modulation

THD: total harmonic distortion

UPC: Universitat Politècnica de Catalunya

VA: volt-ampere

VAR: volt-ampere reactive VOC: voltage oriented control VSI: voltage-source inverter

WECS: wind energy conversion system

WT: wind turbine

WTHD: weighted total harmonic distortion

ZPC: zero-pole cancelation

#### **Terminology**

$$\vec{a} = e^{j\frac{2\pi}{3}}$$

B: rotational friction

C: capacitor

*C<sub>f</sub>*: floating capacitor

$C_p$ : power coefficient

d: duty cycles

D: control variable of the hybrid modulation that takes values within the interval [0, 1] (D=0 and D=1 means applying DSPWM and SPWM, respectively)

D<sub>f</sub>: damping factor

dx: duty cycle

$e_a$ ,  $e_b$  and  $e_c$ : grid phase voltages

$\mathbf{e}_{\mathbf{d}},\,\mathbf{e}_{\mathbf{q}}$  and  $\mathbf{e}_{\mathbf{o}}$ : dq transformed utility phase voltages

$E_{RMS}$ : RMS line-to-line utility voltage

f: line frequency

f<sub>m</sub>: modulation frequency

fs: sample frequency or switching frequency

$\bar{i}_0$ : locally-average NP current

$i_a$ ,  $i_b$  and  $i_c$ : phase currents in the dc side of a converter

$i_{ao}$ ,  $i_{bo}$  and  $i_{co}$ : zero sequence of currents

i<sub>Cx</sub>: current thought a capacitor

$i_d$ ,  $i_a$  and  $i_o$ : dq transformed phase currents

$Im(\vec{x})$ : imaginary part of  $\vec{x}$

$$\mathbf{i}_{ph} = \begin{bmatrix} i_a & i_b & i_c \end{bmatrix}^\mathsf{T}$$

$$\mathbf{i}_{LL} = \begin{bmatrix} i_{ab} & i_{bc} & i_{ca} \end{bmatrix}^\mathsf{T} = \begin{bmatrix} i_a - i_b & i_b - i_c & i_c - i_a \end{bmatrix}^\mathsf{T}$$

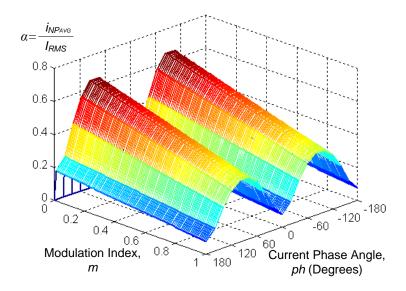

$\bar{i}_{0 ext{min}}$ : minimum local-averaged NP current

$\overline{i}_{0avg}$ : average NP current over a line period

$\hat{l}$ : current amplitude (fundamental)

$I_{RMS}$ : RMS value of the phase currents of the converter (fundamentals)

J: rotational inertia

L: inductance

m: modulation index for the SVM (under linear modulation mode  $0 \le m \le 1$ )

$$m_a = \hat{V}_m / \hat{V}_{camier}$$

: modulation index for SPWM

$$m_a = \frac{2}{\sqrt{3}}m$$

; relationship between modulation indices

$(m_1, m_2)$ : normalized components of the equivalent reference vector in the first sector (given in the non-orthogonal limiting axes of this sector).

$$m_{12} = 2 - m_1 - m_2$$

$\vec{m}$ : reference vector

$m_f = \frac{f_s}{f_m}$ ; frequency-modulation ratio

$\vec{m}_n$ : normalized reference vector

$m_n = \frac{\sqrt{3}}{2}(n-1)m$ ; amplitude of the normalized reference vector

n: number of available voltage levels in each leg of a multilevel converter. This number typifies an n-level converter

$p_{ac}$ : instantaneous power at the ac side

$p_{dc}$ : instantaneous power at the dc side

p: pole pairs

$P_m$ : mechanical power

$\vec{p}_x$ : vector projection

R: electrical resistance

$R_b$ : blade radius

$Re(\vec{x})$ : real part of  $\vec{x}$

R<sub>s</sub>: stator resistance

$s_{ij}$ : switch control variable,  $s_{ij} \in \{0, 1\} = \begin{cases} 1 \text{ the switch is ON, and} \\ 0 \text{ the switch is OFF;} \end{cases}$  where  $i = \{a, b, c\}$  is the

output phases, and  $j=\{1,0,-1\}$  is the dc-link level

t: time

T: line period

$$t_{B} = \frac{2C\Delta V_{C}}{\alpha I_{RMS}}$$

where  $\alpha = \frac{I_{NP_{AVG}}}{I_{RMS}}$ ; capacitor voltage balancing time for DSPWM

$T_s$ : sampling period

$T_m$ : mechanical torque

$T_r$ : rise time

$\mathbf{T}_{dq}$ : dq transformation or park transformation

$v_a$ ,  $v_b$ , and  $v_c$ : modulation signals

$v_{ip}$  and  $v_{in}$ : positive and negative modulation signals.  $v_{ip}$  will only cross the upper carrier, and  $v_{in}$  will only cross the lower carrier

$v_{a0}$ ,  $v_{b0}$  and  $v_{c0}$ : output voltages of a multilevel converter refereed to the NP dc-link voltage

$\hat{V}_{carrier}$ : carrier amplitude of the SPWM

$v_{Cx}$ : voltage of a dc-link capacitor ( $x=\{1, 2, 3, ..., n-1\}$ )

$v_{dc}$ : dc-link voltage regulated by a controller

$v_{dc}^*$ : dc-link voltage control reference

$V_{dc}$ : dc-link voltage provided by a voltage source

$v_{c1}$ : voltage in the lower dc-link capacitor

$v_{c2}$ : voltage in the upper dc-link capacitor

v<sub>off</sub>: common offset (or zero sequence) added to the three-phase modulation signals in carrier-based NTV modulation

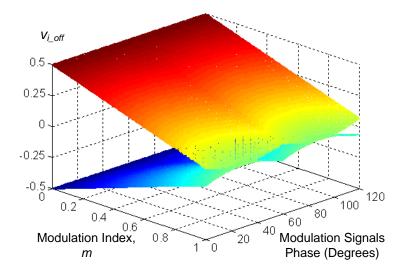

$v_{i\_off}$ : offset applied to two modulation signals of phase i ( $i = \{a, b, c\}$ ) in DSPWM

$v_{i\_off\_HPWM}$ : offset applied to two modulation signals of phase i (  $i = \{a, b, c\}$ ) to generate HPWM

$v_m$ : modulation signal

$\hat{V_m}$ . amplitude of the modulation signal for the SPWM

v<sub>N0</sub>: neutral voltage of a star-connected load refereed to the NP dc-link level

$\vec{V}_{REF}$  : reference vector

*v<sub>wind</sub>*: wind speed

$v_0 = \frac{\max(v_a, v_b, v_c) + \min(v_a, v_b, v_c)}{2}$ : common offset (or zero sequence) added to the three-phase modulation signals to achieve maximum modulation range (modified SPWM)

$\vec{x}$ : generic vector

$\overline{x}$ : local-averaged variable

$\tilde{x}$ : small-signal variable

X\*: reference value

$\hat{X}$ : amplitude of a sinusoidal variable

$x_{op}$ : operation point value of a variable

$X_{RMS}$ : RMS value of a periodic waveform

$x_{(k)}$ : sampled variable at period k

X(t): time-dependent variable

**x**: state vector in the state-space representation

y: output vector in the state-space representation

$\alpha$ ,  $\beta$ : orthogonal axes in a two-dimensional representation

$$\Delta O_{NP} = \frac{V_{C1} - V_{C2}}{2}$$

; instantaneous oscillations around the NP

$$\Delta V_C = V_C - \frac{V_{dc}}{n-1}$$

; voltage error in a dc-link capacitor

$\Delta V_{NP}$ : low-frequency peak-to-peak NP voltage ripple

$$\Delta v_{NPn} = \frac{\Delta v_{NP}}{I_{RMS}/fC}$$

; normalized low-frequency peak-to-peak NP-voltage ripple

$\theta$ : angle

$\theta_n$ : angle of the normalized reference vector (first sextant)

$\theta_o$ : initial angle

$\theta_r$ : rotating coordinated angle of the dq transformation

$\eta$ : efficiency

$\omega = 2\pi f$ ; angular frequency

$\omega_e$ : electrical speed

$\omega_r$ : rotational speed

$\rho$ : air density

$\Psi$ : parameter for the position of the camping interval using HPWM

$\Psi_m$ : magnetic flux

ε: error

$\Omega_{opt}$ : optimal speed

$\beta$ : pitch angle

$$\lambda = \frac{\Omega R_b}{V_{wind}}$$

; tip speed ratio

Chapter 1.

## Introduction

his chapter presents the context of this research work and makes an introduction of this thesis. There is a brief overview of multilevel converter topologies, modulation strategies, and applications are employed. The chapter also includes the main objectives of this thesis and presents the structure of this document.

## 1.1. Context of the Research

The present thesis has been developed in the Department of Electronic Engineering of the Universitat Politècnica de Catalunya (UPC), within the research group called Terrassa Industrial Electronic Group (TIEG). The main research interests of this group are power electronics, renewable energy, multilevel converters, motion control, power quality, and electromagnetic compatibility.

This research has been carried out with the collaboration of two other institutions; the Energy Unit of the Robotiker-Tecnalia research center, Basque Country, Spain; and the Industrial Electrical Power Conversion Department in the Faculty of Engineering at the University of Malta, Malta. Several research stays have been made in both institutions in order to share knowledge and develop some parts of this work.

This research is also part of the activities of three administration supported competitive projects:

-RECENER (ENE2004-07881-C03-03), entitled Advanced power converter topologies to improve efficiency and power quality in the integration of wind energy in the electrical network, funded by the Ministerio de Educación y Ciencia of Spain.

-CEBATE (ENE2007-67033-C03-01), entitled *Study of low-voltage energy* converters for cost reduction and reliability improvement in wind energy systems, funded by the Ministerio de Ciencia e Innovación of Spain.

-CONSOLIDER RUE (CD2009-00046), entitled Advanced wide band gap semiconductor devices for rational use of energy, funded by the Ministerio de Ciencia e Innovación of Spain.

# 1.2. Introduction of this Thesis

Multilevel converters are widely used in high-power applications. These topologies are based on connecting power devices or converters in series. Consequently, high voltages can be handled on the dc and ac sides of the converter, while each device stands only a fraction of the total dc-link voltage.

This thesis focuses on the neutral-point-clamped (NPC) converter (Baker May 13, 1980). Since its introduction in 1981 (Nabae et al. 1981), the NPC and other multilevel topologies have been widely studied. Some of these topologies are the floating or flying capacitor multilevel converter, which include some capacitors to provide the output voltages and to clamp the voltages of the switches. This topology has been of great interest since its introduction in the early 1990s (Meynard and Foch 1992a, b). Another multilevel topology is based on cascading H-bridge inverters. One of the earliest applications of this topology was for plasma stabilizations (Marchesoni et al. 1990); and later it was extended to three-phase applications (Fang Zheng et al. 1996).

Nowadays, the NPC topology is largely used in practical applications. One of the main concerns in this topology is how to keep the neutral point (NP) at one-half of the dc-link voltage. This is necessary to take full benefit of the converter.

Several modulation strategies can be used in multilevel converters. When dealing with a carrier-based modulation, the number of carriers needed is *n*-1, *n* being the number of levels that each phase of the converter can provide (Rodriguez et al. 2007). The standard carrier-based pulse-width modulation (PWM) is sinusoidal PWM (SPWM), in which the modulation signals are sinusoidal waveforms in the steady state. However, in multiphase systems, the modulation signals can be modified by the addition of a proper zero-sequence, which allows extending the range of the modulation index in the linear mode (Bowes and Yen-Shin 1997, van der Broeck et al. 1988). On the other hand, in three-phase systems, the most extended modulation technique is space-vector modulation (SVM), based on PWM (SV-PWM) (Ogasawara and Akagi 1991). These strategies can directly achieve large amplitudes of the output voltages in the linear operation mode, and low switching frequencies in power devices (Kaku et al. 1997). However, processing the algorithms used in SV-PWM may take a long time for its implementation. A summary of the main modulation strategies is shown in (Rodriguez et al. 2002).

In the NPC converter, the NP potential variation is analyzed in (Ogasawara and Akagi 1993) for ac motor drives and static volt-ampere reactive (VAR) compensators. In general terms, introducing a zero-sequence to the reference voltages can control

the NP voltage. In SPWM, this is equivalent to shifting up or down the phase signals of the modulator within a limited interval (Newton and Sumner 1997).

Although the NP voltage of the NPC converter can be generally controlled, a low-frequency voltage oscillation may appear at the NP under some operating conditions (Celanovic and Boroyevich 2000, Ogasawara and Akagi 1993, Pou et al. 2004, 2005a). Therefore, the power devices of the converter and the dc-link capacitors must be oversized in order to stand this voltage. Some recent modulation strategies are able to solve this problem (Busquets-Monge et al. 2004, Pou et al. 2005b). However, these modulation strategies increase the number of transistor switching events and, subsequently their switching losses. Furthermore, they do not naturally balance the voltages in the capacitors. Therefore, this thesis is focused on improving these voltage balancing issues.

Multilevel converters are especially interesting for high power applications. In this sense, the NPC topology is being used in wind energy conversion systems (WECS), since such systems have increased their rated power in recent years. For this reason, the NPC converter is becoming a preferred alternative to the standard two-level converter.

The back-to-back configuration of inverter topologies (Baroudi et al. 2007, Zhe et al. 2009) is used in variable-speed windmills. They require the use of ac-dc-ac converters to make the rotational speed of the blades independent of the utility frequency. Some advantages of this indirect connection are efficiency improvement, reduction of mechanical stresses, voltage control of the local grid, improvement in power quality, and better integration of wind energy into the electrical grid. Furthermore, in many European countries specific regulations make decisive the use of power electronics converters for the integration of wind energy to the grid.

Permanent-magnet synchronous generators (PMSG) are expected to be the standard generators in the future wind turbines. When designed as multipole machines, they may avoid the use of a gearbox and give rise to the so-called direct drive configurations. Unlike in the double-fed induction generator (DFIG), power electronic converters have to process 100% of the energy generated in a PMSG-

based system. Avoiding the use of a gearbox implies both an increase in system efficiency as well as fewer maintenance requirements. In addition, the PMSG configuration has more control over the currents injected into the electrical grid and thus over the reactive power. This is an important advantage for fulfilling grid-connection regulations.

Different control strategies can be implemented in an ac-dc-ac configuration for both the converter that drives the wind turbine and the grid-connected converter. Some standard control schemes are direct torque control (DTC) (Casadei et al. 2002, Zhong et al. 1999) and field-oriented control (FOC) (Casadei et al. 2002, Murray et al. 2008) in the case of the converter driving the wind turbine (WT). Similarly, the counterparts are direct power control (DPC) (Kazmierkowski and Malesani 1998) and voltage-oriented control (VOC) (Noguchi et al. 1998)] in the case of the grid-connected converter. In a WT system, the electrical and mechanical parts are mostly linear; however, the aerodynamics of the blades are highly nonlinear (the system behaves globally as a nonlinear system). Also, the dc-link voltage is defined by a nonlinear equation and therefore the controller of the grid-connected converter should be designed with this nonlinear feature in mind.

The use of linear or nonlinear controllers and a method to tune standard controllers such as proportional-integrative (PI) is performed in Chapter 6 and 7 of this thesis. The research focuses on using an NPC converter connected to the grid (Chapter 6) and on a converter driving the WT (Chapter 7).

# 1.3. Objectives

This thesis focuses on new modulation strategies and control techniques for the NPC converter. The primary objectives are to find new modulation strategies that improve the main problems with the NPC converter, such as: (1) removing the low-frequency voltage oscillation that appears at the NP under some operating conditions, (2) improving balancing dynamic of the voltages in the dc-link capacitors, and (3) finding a compromise solution between switching losses and NP voltage

oscillation amplitudes. Also this thesis is devoted to studying and developing control strategies for the NPC converter in wind turbine energy applications.

For these purposes, the following objectives are defined in this thesis:

- Analyze the current modulation strategies and propose new alternatives in order to improve the main drawbacks commented upon previously.

- Evaluate and compare standard modulation strategies with those proposed under some aspects: conduction and switching losses, harmonic distortion, low-frequency oscillations at the NP of the NPC converter, and the balancing dynamic of the dc-link capacitor voltages.

- Propose control techniques for a grid-connected NPC converter.

- Analyze and propose tuning strategies to improve the control of a converter driving a PMSG in a wind turbine application.

#### 1.4. Structure of the Document

This document is composed of eight chapters and one appendix. The following summary indicates the main contents of each of them.

Chapter 2 starts with a revision of the main multilevel converter topologies. It also describes the NPC converter prototype used for the experimental results presented in this dissertation. Furthermore, it introduces some general modulation strategies used in both two-level and multilevel inverters. This helps in understanding the novel modulation strategies presented in the following chapters.

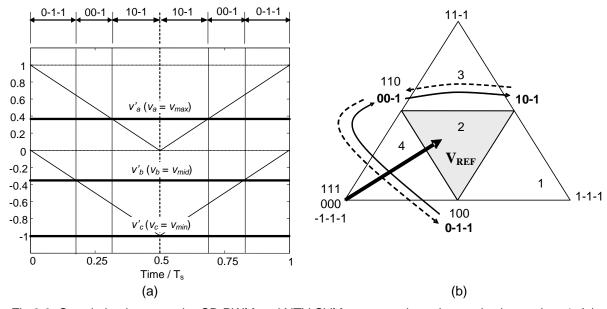

Chapter 3 describes and analyzes a CB-PWM strategy for the three-level NPC converter with a zero-sequence voltage injection. The proposed strategy explores and exploits the duality between the nearest-three-vector (NTV)-SVM strategy and the CB-PWM strategy with a zero-sequence voltage injection in order to (i) balance the voltage, (ii) reduce the switching frequency and consequently switching losses, and (iii) mitigate the voltage oscillations of the NP. A theoretical basis for the proposed CB-PWM strategy is developed based on the analysis of the NTV-SVM strategy.

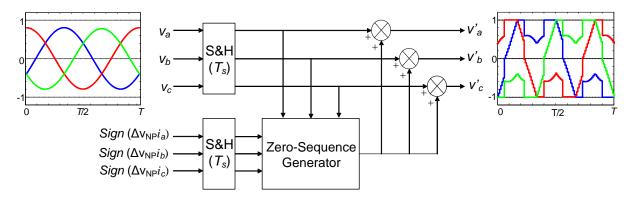

Chapter 4 proposes another modulation strategy that overcomes the problem of low-frequency NP voltage oscillation in the NPC converter. This modulation strategy is characterized by the use of two modulation signals per phase, and it is the so-called double-signal PWM (DSPWM). One of the main drawbacks of this modulation strategy is that it does not provide natural voltage balancing; therefore, an optimal compensator is also presented in this chapter.

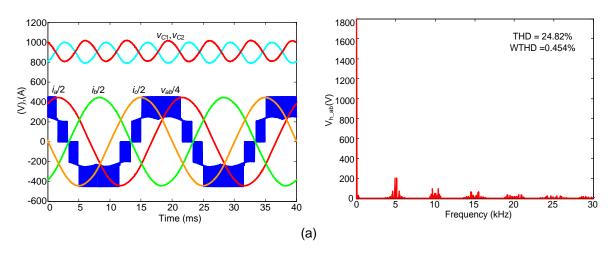

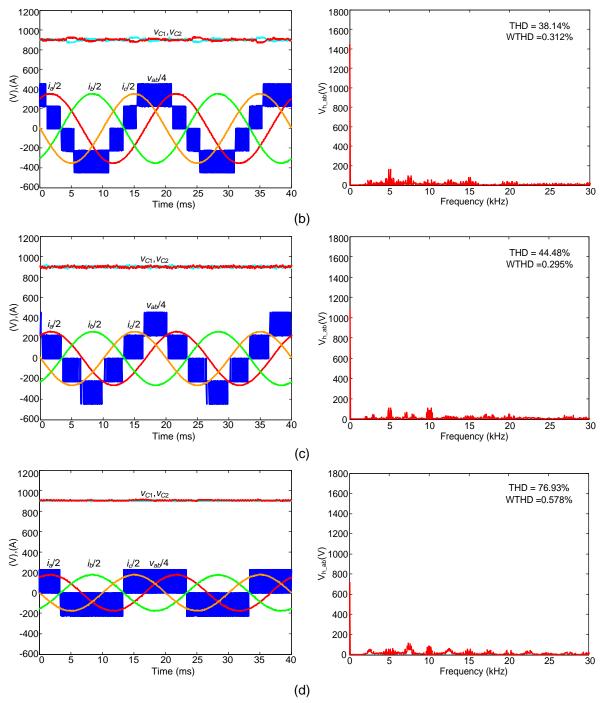

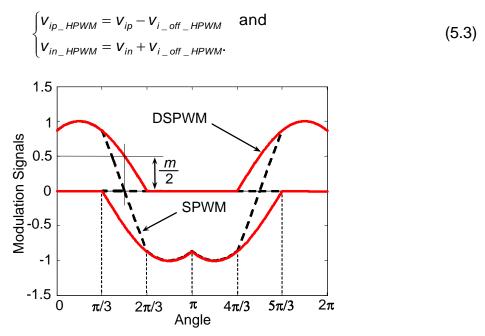

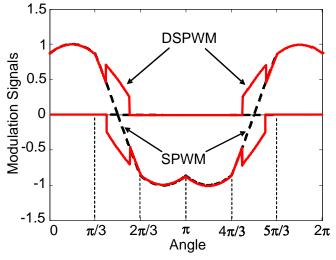

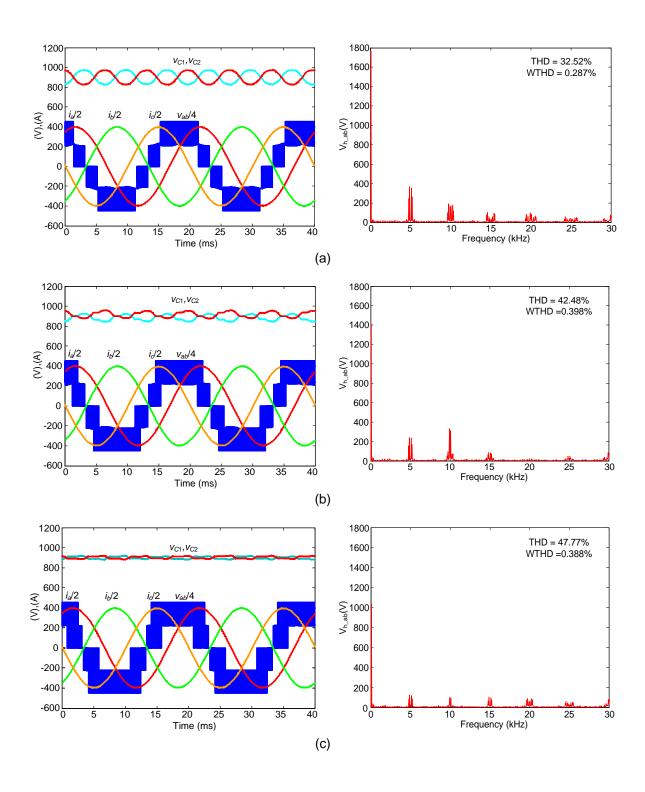

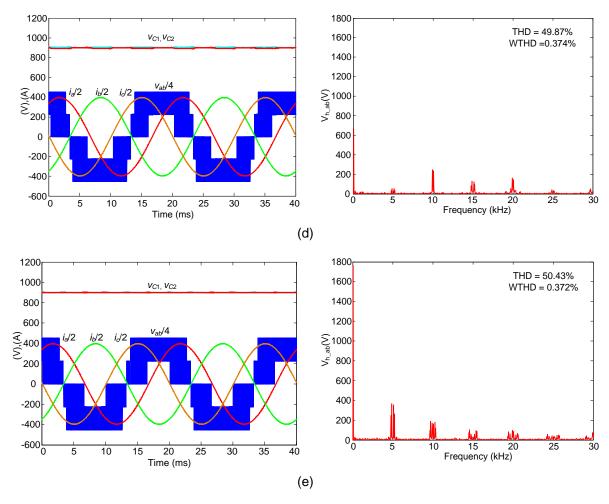

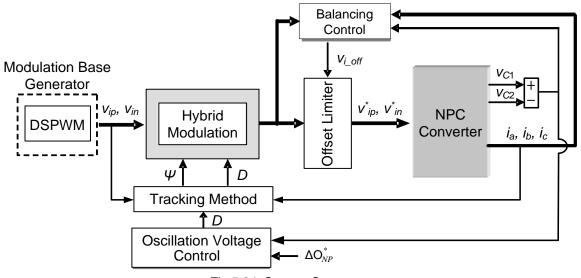

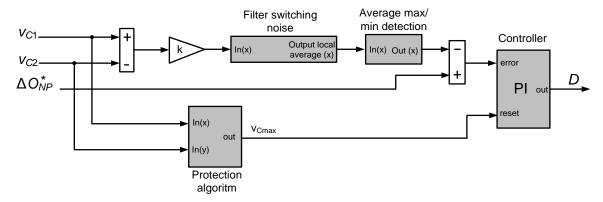

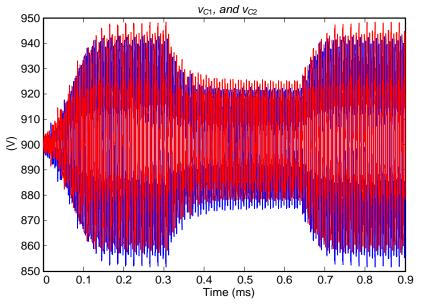

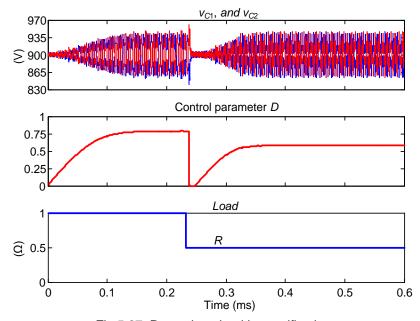

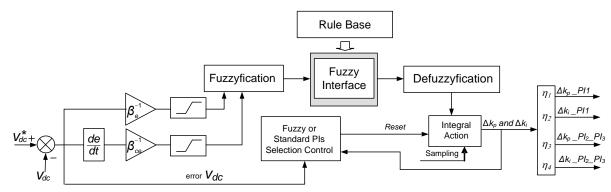

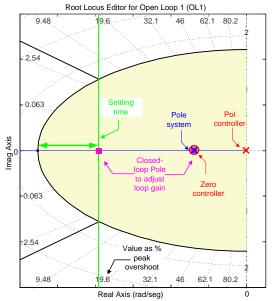

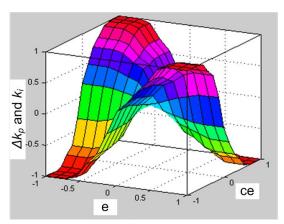

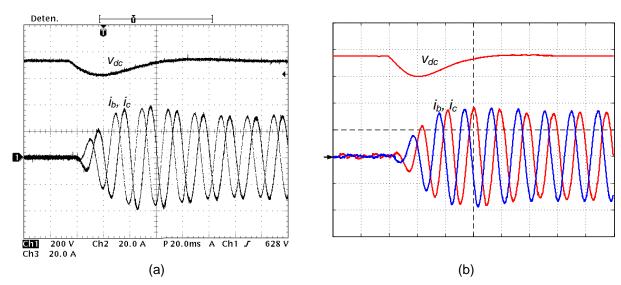

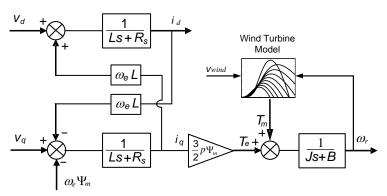

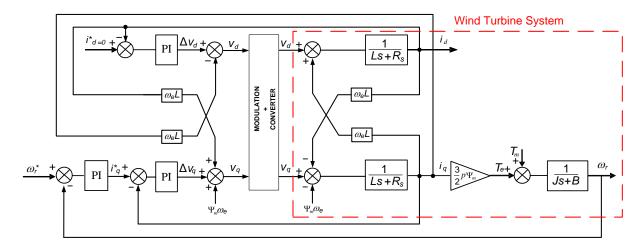

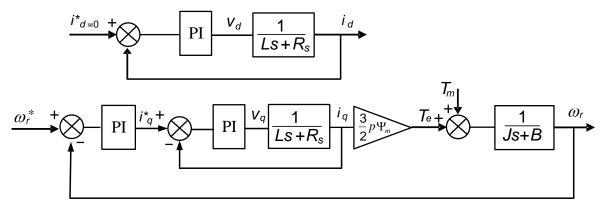

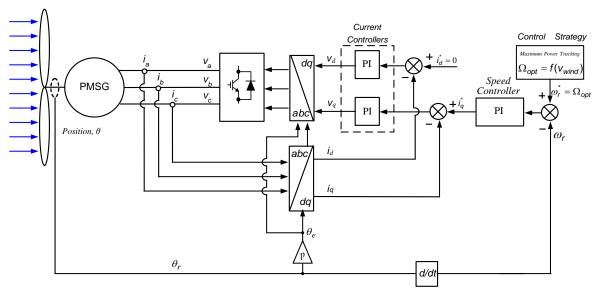

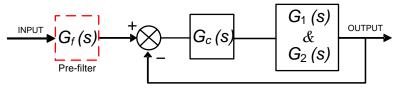

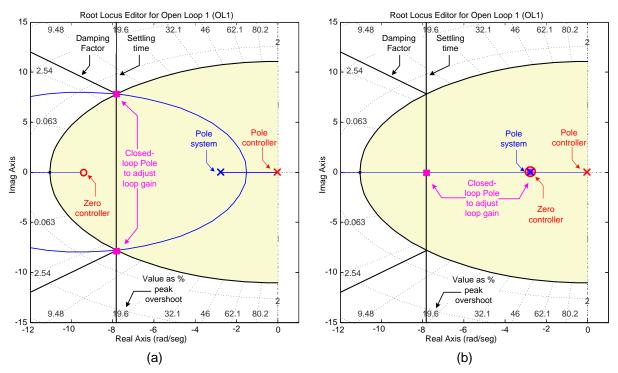

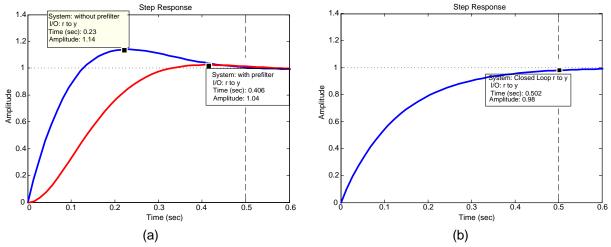

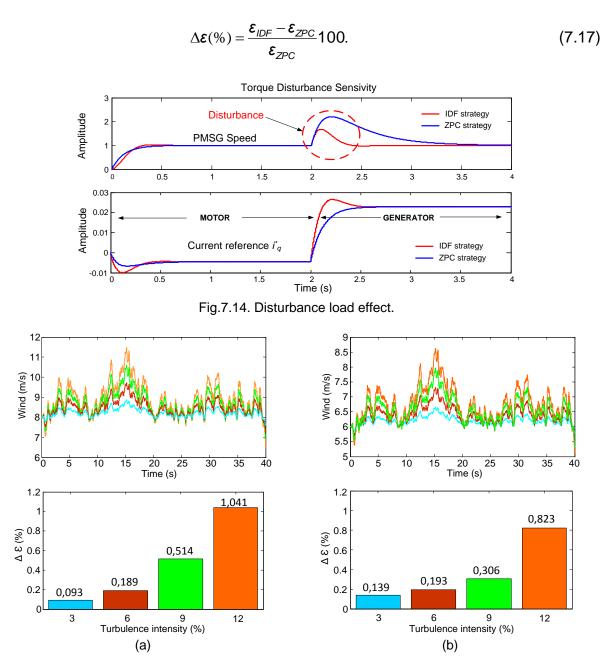

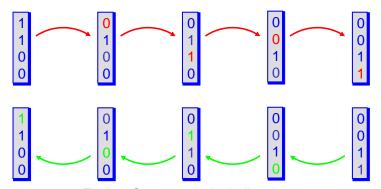

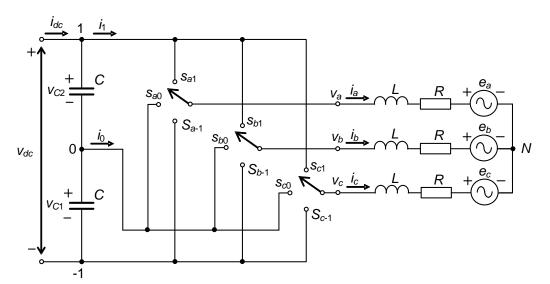

Chapter 5 proposes a hybrid modulation strategy (HPWM), based on the modulation strategy presented previously in Chapter 4. This new modulation combines the DSPWM with the SPWM in order to minimize the switching losses. The main characteristic of this HPWM is the reduction of the switching losses at the cost of some low-frequency voltage oscillations at the NP. Furthermore, a tracking method and an amplitude control of the NP voltage are also proposed in this chapter in order to achieve the maximum reduction of the voltage oscillation amplitudes in HPWM and to control the maximum amplitude of the NP voltage oscillations