# UNIVERSITAT AUTONOMA DE BARCELONA

## FACULTAT DE CIENCIES DEPARTAMENT D'INFORMATICA

ADAPTACION DE LA ARQUITECTURA EN TIEMPO DE EJECUCION

MEMORIA PRESENTADA POR JOAN SORRIBES GOMIS PARA OPTAR AL GRADO DE DOCTOR EN CIENCIAS (INFORMATICA)

BARCELONA ABRIL 1987

#### ADAPTACION DE LA ARQUITECTURA EN TIEMPO DE EJECUCION

Memoria presentada por JOAN SORRIBES GOMIS para optar al grado de Doctor en Ciencias (Informâtica) por la Universidad Autônoma de Barcelona. Trabajo realizado en el departamento de Informâtica de la Facultad de Ciencias de la Universidad Autônoma de Barcelona, bajo la dirección del Dr. Emilio Luque Fadôn.

Bellaterra, Abril de 1987.

Vo. Bo. Director Tesis

Fdo. Emilio Luque

A Georgina

a Joan

i als pares

Deseo hacer constar mi agradecimiento màs expresivo al Prof. Dr. Emilio Luque Fadòn que con su valiosa dirección, asesoramiento y ayuda ha hecho posible la realización de esta memoria.

A la Dra. Ana Ripoll por sus acertadas sugerencias y apoyo constantes.

A Porfidio Hernandez por sus comentarios alentadores y apoyo.

A Lola Isabel Rexachs por sus sugerencias y estímulo.

A Carles Siscart por el apoyo tècnico proporcionado.

A los miembros de la Unidad de Control Digital por sus oportunos consejos.

Muy especialmente a mi esposa, Georgina sin cuya infinita paciencia y apoyo incondicional no hubiera sido posible este trabajo.

### INDICE

| PROLOGO                                                       | i∨ |

|---------------------------------------------------------------|----|

| CAPITULO I ADAPTACION DE LA ARQUITECTURA                      | 1  |

| I.1 INTRODUCCION                                              | 1  |

| I.1.1 ADAPTACION FUNCIONAL DE LA ARQUITECTURA                 | 4  |

| 1.1.a Sistemas Operativos                                     | 4  |

| 1.1.b Procesadores Definidos por un Lenguaje de Alto Nivel    | 6  |

| I.1.2 ADAPTACION DE LA ARQUITECTURA ORIENTADA<br>AL PROBLEMA  | 8  |

| 1.2.a Estudio Heurístico                                      | 9  |

| 1.2.b Estudio Analitico                                       | 13 |

| I.1.3 ADAPTACION DE LA ARQUITECTURA<br>EN TIEMPO DE EJECUCION | 19 |

| I.2 PLANTEAMIENTO DEL TRABAJO                                 | 24 |

| I.3 ESTRUCTURA DEL SISTEMA                                    | 32 |

| I.4 FUNCIONAMIENTO DEL SISTEMA                                | 36 |

| I.5 PARAMETROS DE DISEÑO                                      | 38 |

| I.6 COMPORTAMIENTO DEL SISTEMA                                | 40 |

| CAPITULO II ESTRUCTURA Y FUNCIONAMIENTO DEL SISTEMA           | 44 |

| II.1 ORGANIZACION Y MODO DE OPERACION DEL COPROCESADOR        | 44 |

| II.1.1 FUNCIONAMIENTO DEL SISTEMA                             | 46 |

| II.1.2 MEMORIA DE INTERCONEXION (M. I.)                       | 51 |

| II.1.3 UNIDAD DE GESTION DE LA MEMORIA DE                     | 45 |

|     | 4      | .3.1 ACCESO A LA MEMORIA DE INTERCO-                                               |     |

|-----|--------|------------------------------------------------------------------------------------|-----|

|     | 7.     | NEXION                                                                             | 63  |

|     |        | 1.3.1.a Acceso en lectura                                                          | 63  |

|     |        | 1.3.1.b Acceso en escritura                                                        | 65  |

|     | 1.     | .3.2 ALGORITMO DE REEMPLAZAMIENTO                                                  | 70  |

|     |        | 1.3.2.a Algoritmo L.R.U                                                            | 71  |

|     |        | 1.3.2.b Algoritmo de Distancia Māxima                                              | 74  |

|     | II.1.  | 4 UNIDAD DE CONTROL DEL COPROCESADOR (U.C.C.)                                      | 78  |

| CAF | PITULO | III SIMULACION Y EXPERIMENTACION                                                   | 81  |

| III | .1     | VALORACION DE LA GANANCIA DEL METODO PROPUESTO CON RESPECTO A LOS METODOS CLASICOS | 81  |

| III | 1.2    | SIMULACION DEL COPROCESADOR                                                        | 94  |

| III | .3     | PROGRAMA SIMULADOR                                                                 | 101 |

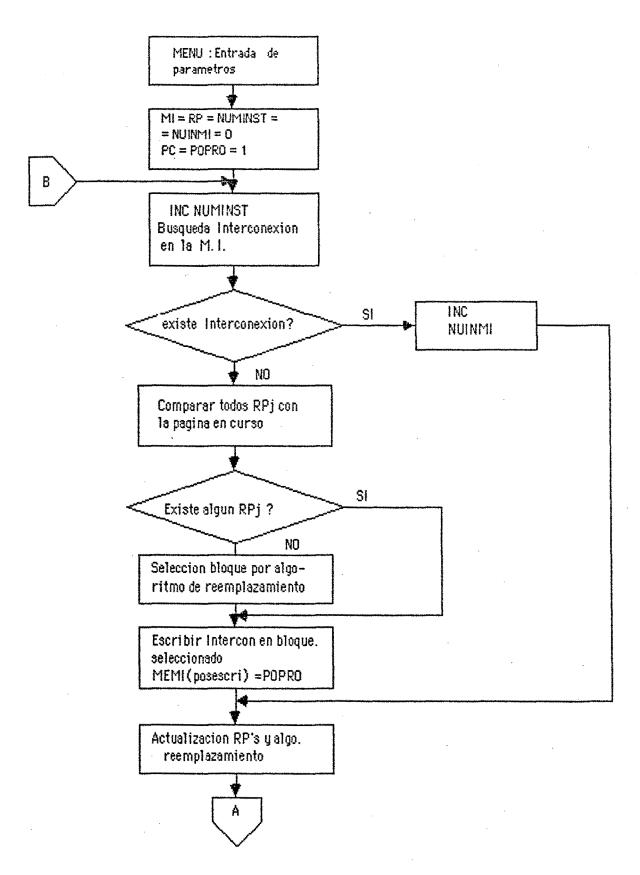

|     | 3.1    | Entrada de paràmetros                                                              | 104 |

|     | 3.2    | Inicialización                                                                     | 108 |

|     | 3.3    | Ejecuciòn simulada                                                                 | 109 |

|     | 3.4    | Fallo de pàgina                                                                    | 110 |

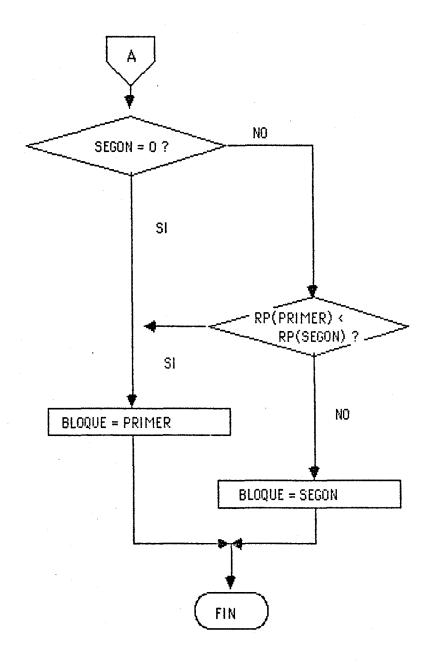

|     | 3.5    | Algoritmo de reemplazamiento                                                       | 111 |

|     | 3.6    | Creación de la interconexión                                                       | 114 |

|     | 3.7    | Actualización del algoritmo                                                        | 115 |

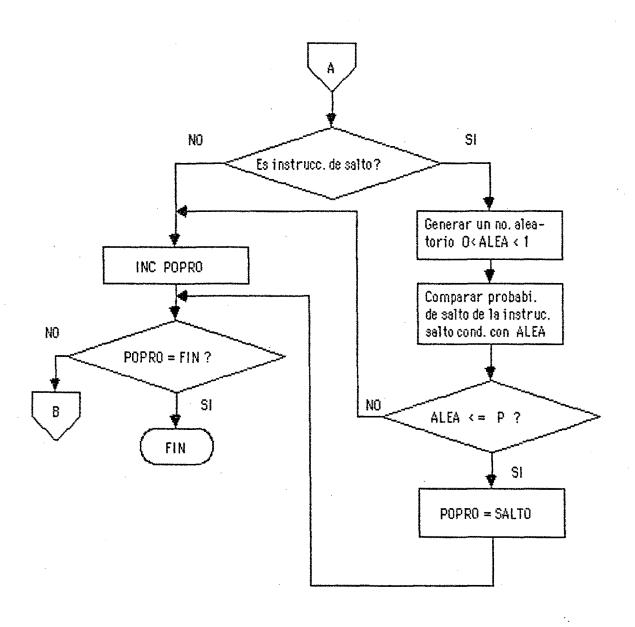

|     | 3.8    | El secuenciamiento                                                                 | 116 |

|     | 3.9    | Visualización de resultados                                                        | 116 |

|     | 3.10   | Simulación sistemàtica                                                             | 118 |

|     | 3.11   | Simulacion probabilistica                                                          | 119 |

| III | 1.4    | INCIDENCIA DE LOS ALGORITMOS DE REEM-<br>PLAZAMIENTO EN EL COMPORTAMIENTO DEL      |     |

|     |        | SISTEMA                                                                            | 125 |

|     | 4.1    | Algoritmo de Mapping Directo                                                       | 125 |

| 4.2      | Algor          | itmo Las                     | t Rece | ≘ntly | / Used | 1 (L      | RU)   | •          | -  | • | • | • | 128 |

|----------|----------------|------------------------------|--------|-------|--------|-----------|-------|------------|----|---|---|---|-----|

| 4.3      |                | o de la<br>comporta          | •      |       |        | la<br>• • | M.I.  | •          |    | • |   | ě | 133 |

| 4.4      | Algor          | itmo de 1                    | Distar | ncia  | Maxid  | na        | •     |            | •  | • |   | • | 139 |

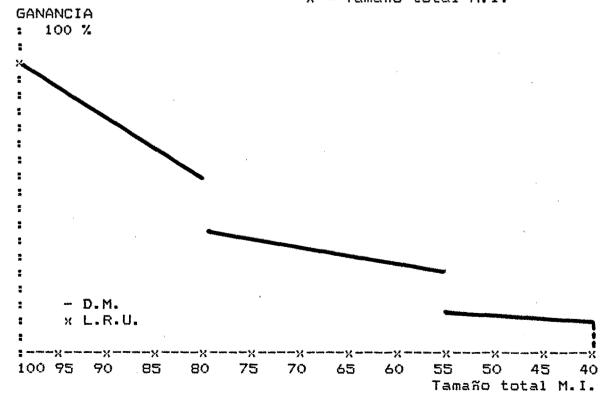

| 4.5      | Compa          | ración d                     | e los  | _     |        | )s<br>• • | L.R.  | .U.        |    |   | • | • | 144 |

| 111.5    | EJEMF<br>METOD | PLO PARA<br>OS CLASIO        | LA CO  |       |        |           |       | _os<br>•   |    | • | • | • | 146 |

| 111.6    |                | CION DE<br>RTAMIENTO         |        | DELO  |        | RITM      |       | DE<br>•    | •  |   |   |   | 151 |

| 6.1      | Reduc          | ciòn al                      | lazo : | simpl | le     |           |       |            |    | • | • |   | 151 |

| 6.2      | -              | ortamient<br>Itmico          | o del  | sist  | tema.  | E1        | mode  | elo<br>• • | •  |   | • | • | 155 |

| CAPITULO | יז כ           | UTILIZA<br>TACION<br>MICROPR | DE I   | LA A  | ARQUI  |           |       |            |    |   | • | • | 179 |

| IV.1     |                | RIPCION<br>PROGRAMA          |        | "R65  | 02" E  | N V       | ERS   |            |    |   |   | • | 180 |

| IV.2     | INCOF          | RPORACION                    | DEL    | COPR  | OCESA  | DOR       | •     |            | •  |   |   |   | 186 |

| IV.3     | EJEMF<br>PROPU | LO DESAR<br>JESTA            | ROLLA: |       | DBRE I | LA M      | iAQU: | INA<br>• • | •  | • | # | • | 190 |

| CONCLUS  | IONES          | Y LINEAS                     | ABIE   | RTAS  | •      |           |       |            | •  | • | • |   | 195 |

| APENDIC  | ΕA             | LISTADO<br>DETERPRI          |        | ADOR  | DETE   | RMIN      | 11ST  | ICO        |    |   |   |   |     |

| APENDIC  | E B            | LISTADO<br>DETSISTM          |        | ADOR  | SIST   | EMAT      | ICO   |            |    |   |   |   |     |

| APENDIC  | EC             | LISTADO<br>BRANCLRU          |        | ADOR  | PROB   | ABIL      | _IST  | ICO        |    |   |   |   |     |

| APENDIC  | E D            | LISTADO                      | MICRO  | PROGI | RAMAS  | PAF       | RA E  | L Rá       | 50 | 2 |   |   |     |

| APENDIC  | EE             | LISTADO<br>PRETE "J          |        |       |        |           |       | NTEF       | ₹  |   |   |   |     |

REFERENCIAS

#### PROLOGO

La presente memoria describe el trabajo desarrollado en el diseño y evaluación de un coprocesador para la

migración vertical dinàmica en tiempo de ejecución, para

sistemas microprogramados. Esta memoria ha sido estructurada

en cuatro capítulos cuyos contenidos resumimos a

continuación.

CAPITULO I Se presenta una introducción sobre el tema de la migración vertical, primero desde su vertiente clàsica de implementación "off-line", y más tarde desde el punto de vista on-line (en tiempo de ejecución). En este capítulo, se expone en lineas generales el trabajo que ha sido desarrollado, describiendo las características básicas de la estrategia presentada, la estructura del sistema y su modo de funcionamiento, así como su simulación y aplicación a un ejemplo concreto.

CAPITULO II Este capitulo ha sido dedicado a la descripción detallada de la estructura del sistema, así como de su modo de funcionamiento, analizando cada una de las partes del coprocesador por separado, y su papel en el funcionamiento del mismo. El funcionamiento del sistema es analizado en las dos situaciones que se pueden presentar al

ejecutar una instrucción: a- que deba realizarse su migración. b- que esta ya se encuentre migrada (versión en lenguaje intermedio o "J+1/2". Esto permite estudiar posteriormente los parametros que influyen en la aceleración de la ejecución de un programa.

CAPITULO III Se realiza un estudio comparativo de los mètodos clàsicos (off-line) con el mètodo propuesto en este trabajo (on-line). El desarrollo de un programa simulador, para un sistema que incorpore el coprocesador para la migración vertical en tiempo de ejecución, nos ha permitido analizar el comportamiento de dicho sistema y la incidencia de los parametros fundamentales, tales como el tamaño de la Memoria de Interconexión, su partición, algoritmos de reemplazamiento, etc.. Por último, a partir de los resultados obtenidos con el programa simulador, ha sido posible elaborar un modelo algorítmico que permite la evaluación de la ganancia que se puede obtener en un sistema con el coprocesador, para una configuración de parametros dada y un programa determinado.

CAPITULO IV La estrategia de adaptación propuesta, coprocesador para migración en tiempo de ejecución, ha sido aplicada a un ejemplo concreto, el microprocesador "R6502". Inicialmente se ha procedido a una emulación del R6502 sobre una simulación de un sistema microprogramado, para posteriormente incluir el coprocesador propuesto y generar el intérprete del lenguaje intermedio definido.

#### CAPITULO I

#### ADAPTACION DE LA ARQUITECTURA

#### I.1 INTRODUCCION

La eficiencia con que se puede resolver un problema con la ayuda de un ordenador, depende de la medida en que la arquitectura de dicho ordenador, soporte las primitivas que precisa el algoritmo utilizado para la resolución del problema. Dado que es imposible que la arquitectura original de una màquina de propòsito general, pueda adaptarse forma òptima a cualquier problema especifico, la resolución màs eficaz de cada problema implica la necesidad de una maquina de propòsito especial, con una arquitectura orientada al problema a resolver. Este objetivo no se puede atacar evidentemente construyendo fisicamente dicha maquina para cada problema, puesto que el coste casi nunca se podría justificar. Sin embargo, podemos abordar el problema desarrollando un mètodo capaz de adaptar (Tuning) la arquitectura de la maquina de la forma mas adecuada posible, es decir, creando la maquina virtual capaz de soportar de forma optima las primitivas necesarias para una tarea concreta. (Ri80)

La Adaptación de la arquitectura de un ordenador està (B185) basado en la idea general de que cualquier organismo, vivo o no, que realice alguna tarea de forma repetitiva, tiene en si mismo el germen del aprendizaje. Esta capacidad puede ser explotada al màximo con un "tuning en tiempo real", (B183) (B184) donde el ordenador aumenta su velocidad de ejecución gradualmente, como resultado de la "experiencia" que adquiere al ir encontrando lazos y estructuras repetitivas durante la ejecución de un programa.

Un mecanismo de Tuning, es un medio a travès del cual la arquitectura de un sistema sigue (se adapta) constantemente las variaciones del perfil de ejecución de un programa, mejorando sus tiempos de ejecución, como consecuencia de la experiencia adquirida durante la misma.

Una primera aproximación para realizar el Tuning de la arquitectura de un ordenador a una aplicación, es a través de la Migración Vertical (Am83a) (Am83b). La Migración Vertical es una técnica muy conocida para mejorar las prestaciones de un ordenador. Con esta técnica las primitivas seleccionadas (secuencias de instrucciones o funciones) son trasladadas de un nivel a otro inferior dentro de la jerarquía de los diferentes niveles software de un ordenador, bajo la idea de aumentar la velocidad de ejecución de un sistema monoprocesador. La Migración Vertical es vista

como el modo de acelerar la ejecución de un programa, convirtiendo las primitivas seleccionadas del programa original, escrito en un lenguaje de nivel "k", en nuevas instrucciones del repertorio del lenguaje "k", creando en un nivel "j" inferior (j < k) las rutinas de interpretación necesarias para su ejecución. Esta técnica ha sido normalmente aplicada cuando "k" es el nivel máquina y "j" el de microprogramación.

Esta migración lo es en el sentido de que se crean las rutinas en el lenguaje de nivel "j" capaces de interpretar un conjunto de nuevas instrucciones o primitivas en el lenguaje de nivel "k", las cuales pueden incluir a otras de su mismo repertorio. De esta forma una primitiva (conjunto de segmentos o funciones) de un programa de usuario (nivel "k"), puede ser substituida por una nueva instrucción (nivel "k"), que será interpretada en el nivel "j".

El objetivo que se persigue con la Migración Vertical es, en definitiva, la síntesis de la arquitectura para su adaptación a un problema. Esta síntesis de la arquitectura puede ser realizada de dos formas : (Lu81a) (Lu83) (Ho84)

- 1 Sintesis Funcional.

- 2 Sintesis Orientada al Problema.

#### I.1.1 ADAPTACION FUNCIONAL DE LA ARQUITECTURA

En la adaptación funcional se migran aquellas funciones software que son utilizadas intensivamente en determinadas àreas de aplicación. Esta alternativa ha sido utilizada con èxito en dos àreas : Sistemas operativos y procesadores definidos por un lenguaje de alto nivel (Ch75) (Mi85), en las cuales la migración se lleva a cabo entre el lenguaje màquina y la microprogramación.

#### 1.1.a Sistemas Operativos.

La migración puede ser utilizada de formas distintas para proporcionar soporte óptimo a los sistemas operativos (De84):

- creando primitivas que seran utilizadas por un sistema operativo en microprogramación.

- creando una máquina virtual en la cual puedan ser ejecutadas las primitivas.

- microproprogramando porciones del sistema operativo, parcial o enteramente.

Puesto que en una màquina microprogramable la Memoria de Control Escribible (Writable Control Store) es de tamaño limitado, no es posible migrar todas las primitivas, por lo que es necesario hacer una selección de cuales han de ser migradas. Las primitivas que son candidatas para ser microprogramadas, son aquellas demasiado específicas para su realización hardware, con muy poca probabilidad de cambiar con el tiempo y que acaparen el mayor tiempo de ejecución

del còdigo. En (Wi69) Wirth sugerfa el uso de la microprogramación para la creación de instrucciones màquina especiales requeridas por los sistemas operativos, tales como las primitivas de sincronización de procesos de Dijkstra "p" y "v". La mejora de las primitivas "p" y "v" mediante la microprogramación ha sido descrita por Anceau en (An72). En (Br76) Brown enumera catorce funciones que podrían ser implementadas como primitivas mediante la microprogramación. Estas incluyen, entre otras, las siguientes:

- Primitivas de sincronización de programas.

- Mecanismos de manejo de colas.

- Conmutación de estados.

En (Br77) se describe como seleccionar las primitivas más apropiadas para su implementación así como analizar las características diferenciales entre software, hardware y firmware. Existe un modelo analítico para determinar la estrategia óptima para la implementación firmware.

Como se indica en (St78) los sistemas operativos estructurados jerarquicamente tienen una desventaja, el impacto sobre el comportamiento del sistema causado por el "overhead" de los sucesivos niveles de interpretación. La reducción de este "overhead" mediante la migración vertical se consigue alterando selectivamente dicha jerarquía de interpretación, y reimplementando las primitivas (o funciones) que la CPU usa de forma más intensiva en niveles

inferiores. Una función que ha sido migrada a un nivel inferior de la jerarquia, es ejecutada de forma más rápida y eficiente, pero también más elemental. Recientemente esta metodologia ha sido aplicada al sistema operativo "UNIX" por Holtkamp (Ho85).

#### 1.1.b Procesadores Definidos por un Lenguaje de Alto Nivel.

La ejecución de programas escritos en un lenguaje de alto nivel mediante la microprogramación, està relacionada con el soporte y gestión de las estructuras de datos incorporadas y/o definidas sobre el Lenguaje de Alto Nivel y de las estructuras de control utilizadas en programas expresados en un lenguaje particular.

El uso de la microprogramación para ejecutar programas desarrollados en un lenguaje de alto nivel puede ser visto de formas distintas :

- a Los programas pueden ser traducidos directamente a microprogramas.

- b Los programas en lenguaje de alto nivel pueden ser interpretados directamente por microprogramas.

- c Los programas pueden ser traducidos (via software o firmware) a un lenguaje intermedio, y êste a su vez ser interpretado directamente por los microprogramas.

La primera utilización conocida de la migración vertical a microprogramación, para la implementación de

procesadores de lenguajes de alto nivel, fue la realización microprogramada de Weber para EULER, sobre un sistema 360 modelo 30 de IBM (We67). Esta realización consistía de tres partes:

- Un traductor, escrito en microcòdigo Modelo 30.

- Un intérprete, escrito en microcòdigo Modelo 30.

- Un programa de control de entrada/salida, escrito en lenguaje maquina en el sistema 360.

Posteriormente se desarrollò una implementación microprogramada de APL para el sistema IBM 360 Modelo 25 (Ha73). En este sistema APL, el emulador APL se carga en la memoria de control. Un supervisor y un traductor se cargan en la memoria principal.

Una contribución importante en este campo lo constituyen los ordenadores Burroughs B1700 (Wi72). Estos sistemas incorporan una gran variedad de lenguajes de alto nivel, traduciendo los programas a lenguajes intermedio (lenguajes S). Existe un lenguaje S para cada lenguaje de alto nivel, y los programas en estos lenguajes S son interpretados directamente por microprogramas.

En (Lu77) se describe un sistema microprogramable a dos niveles, capaz de ejecutar directamente cualquier lenguaje de alto nivel. En este sistema, cualquiera de los lenguajes de alto nivel puede ser soportado directamente como si se tratara de lenguaje màquina. Las principales

características del lenguaje de alto nivel se soportan sobre una mezcla de hardware y firmware.

Finalmente debemos hablar del Intel iAPX 432 (In80) (My81), una màquina cuya unidad central de procesos està formada por dos chips (circuitos). El primero funciona como una unidad de decodificación de la instrucción y el segundo corresponde a una unidad de microejecución. El microcódigo sobre la arquitectura bàsica ejecuta un lenguaje màquina equivalente al lenguaje ADA, el cual constituye el "assembler" del iAPX 432. La traslación de las sentencias ADA a instrucciones màquina es esencialmente un proceso uno a uno.

#### I.1.2 ADAPTACION DE LA ARQUITECTURA ORIENTADA AL PROBLEMA

Con la adaptación orientada al problema, se pretende el reemplazamiento automàtico del còdigo por microcòdigo funcionalmente equivalente para programas específicos, analizados individualmente. En cuanto a la metodología a seguir para elegir cuales de las secuencias del progama del usuario deben ser migradas a microcòdigo, podemos enfocarla de dos formas:

- Estudio heuristico.

- Estudio analitico.

#### 1.2.a Estudio Heuristico.

Un primer intento de conseguir de manera automâtica el reemplazamiento del còdigo, por microcòdigo funcionalmente equivalente se describe en (Ab74). Este proceso heuristico puede ser subdividido en varias fases incluyendo la partición del entorno, o clasificando los problemas de acuerdo a su función, haciendo la traza de la ejecución de un programa con un "overhead" minimo, sintesis de la arquitectura, verificación del microcòdigo generado y proporcionando los cambios de la arquitectura al traductor del sistema. La mayor parte del trabajo realizado por Abd-Alla está dedicado a la fase de síntesis de la arquitectura mientras que las otras permanecen como problemas en la realización de arquitecturas de ordenadores heurísticamente adaptables.

La arquitectura especializada es sintetizada de modo iterativo, una instrucción cada vez, hasta conformar un conjunto de instrucciones con un minimo tiempo de ejecución esperado. Cuando la mejora resultante de una iteración es menor que el "tuning overhead", la arquitectura obtenida puede considerarse óptima, y la fase de sintesis finalizada. El algoritmo de sintesis puede resumirse así (Ri80):

- 1 Determinación de los limites de los lazos con mayor frecuencia de ejecución en el programa.

- 2 Asignación de los datos referenciados con mayor frecuencia en el lazo a los registros de trabajo.

- 3 Creación de las microoperaciones de precarga de los registros de trabajo.

- 4 Conversión del flujo de instrucciones del lazo a un flujo equivalente registro a registro.

- 5 Traducción del flujo de instrucciones a microinstrucciones

- 6 Optimización del flujo de microinstrucciones.

- 7 Creación de microoperaciones de restauración de la memoria principal.

- 8 Eliminación de las precargas y restauraciones innecesarias.

- 9 Parar si existe convergencia (mejora), en caso contrario regresar al primer paso.

Fara demostrar la viabilidad del proceso de tuning heuristico, se utilizò sobre una rutina de mover datos y un generador de números de Fibonacci sobre una arquitectura Hewlett Packard 2100. Las mejoras en velocidad que se obtuvieron de las versiones firmware sobre las software fueron de 7.9 y 4.4 respectivamente.

El-Ayat (Ay77b) desarrollo un mètodo heuristico que extendía la idea anterior y que consistía en los siguientes pasos :

- 1 Traza de la ejecución y monitorización de los programas de aplicación.

- 2 Anàlisis estadistico de la traza e identificación de los segmentos del còdigo que ofrezcan una mejora significativa del comportamiento del sistema al ser migrados.

3 - Sintesis del microcòdigo optimizado para migrar los segmentos identificados en el paso anterior.

El programa así migrado (adaptado), es ejecutado bajo la nueva arquitectura para comparar los resultados del programa con los obtenidos con la anterior arquitectura. Se abre un periodo de tiempo durante el cual la nueva arquitectura es analizada, y se decide si esta es definitiva, o requiere nuevos cambios hasta obtener una solución satisfactoria al problema de aplicación atacado.

En (Ay77a) se presentan dos algoritmos para automatizar el proceso de tuning; el algoritmo de anàlisis y el de sintesis. La función del algoritmo de anàlisis es la de identificar y delimitar todos los segmentos candidatos a la migración. Esto es realizado a través de un anàlisis del programa de aplicación y de su perfil de ejecución. En cuanto a la sintesis, se emplearon dos algoritmos diferentes, dependiendo del tipo de segmento a ser migrado, uno para los lazos y otro para los demás casos. el algoritmo, es decir para "no lazos", realiza un test para los segmentos de tamaño excesivo, con el fin de hacer una primera selección entre los posibles candidatos. Si el tamaño del segmento es adecuado, es decir, està dentro de los limites permitidos, el segmento es llevado a un "buffer" de trabajo y la primera instrucción reemplazada por una instrucciòn extendida. Los siguientes pasos del algoritmo, manejan expansiones individuales de instrucciones en microcòdigo y sintesis de microcòdigo final optimizado. El algoritmo de sintesis para lazos difiere del anterior, en que utiliza registros locales de trabajo para las referencias a operandos y almacenamiento temporal de resultados intermedios en lugar de la memoria principal. Los resultados experimentales obtenidos, muestran que la ganacia en velocidad conseguida es del 35 al 40 por ciento respecto del programa original.

En (St78) se describe una metodologia para sistemas estructurados jerarquicamente en capas software. Este modelo està basado en la partición de las funciones software y firmware en una estructura jeràrquica, en tèrminos de relación de "USES": "IF Pi USES Pj THEN Pi es considerado como perteneciente a un nivel superior que Pj".

En este método heurístico, la función a ser migrada (A) se mantiene en su propio nivel y al mismo tiempo, su versión migrada (A\*) es creada en el nivel inferior. Las rutinas del nivel superior que hagan uso de "A", son ahora dirigidas a su versión migrada "A\*". Si dentro esta función existe una bifurcación condicional a otra función diferente de "A", puesto que este salto no puede hacerse desde "A\*" y requiere de la versión no migrada, cuando se produzca esta condición se regresarà a la versión original "A" desde "A\*" mediante una instrucción de Trap (llamada a una rutina de nivel superior desde un nivel inferior). La versión no migrada reejecuta la rutina desde el principio, lo cual requiere que todos los datos que han sido modificados duran-

te la ejecución de "A\*" (que ha sido abandonada) deben ser restablecidos antes de entrar en "A".

Los resultados obtenidos dan un factor de 5 a 10 en la velocidad de ejecución de las primitivas en particular y del 50 por ciento en la mejora de la velocidad de ejecución del programa de aplicación.

#### 1.2.b Estudio Analítico

Rauscher y Agrawala (Ra78) desarrollaron un mètodo de sintesis de la arquitectura de un sistema, de forma diferente. Su enfoque enmarca el problema en los programas que son escritos en un lenguaje de alto nivel y son traducidos por un compilador a un lenguaje de representación intermedio. En lugar de la fase normal de generación de código por el compilador, se ejecuta un procedimiento que realiza las siguientes funciones:

- 1 Generación de los microprogramas que definen una nueva arquitectura, la cual soporte de manera eficiente el programa en lenguaje de alto nivel que está siendo compilado.

- 2 Generación del programa en lenguaje màquina que haga uso de la nueva arquitectura.

Para la definición de las nuevas instrucciones se describen dos métodos : el de "secuencia de instrucciones" y el de "estructura del programa".

En el primero se analiza la representación en lenguaje intermedio del programa, para encontrar todas las secuencias de instrucciones y el número de veces que aparece que aparece cada secuencia (Ra76). La implementación microprogramada de cada secuencia es comparada con su implementación en lenguaje màquina, y aquellas secuencias que produzcan un mayor ahorro de tiempo son elegidas como nuevas e instrucciones màquina.

segundo mètodo, llamado de "estructura del programa", supone un conocimiento "a priori" del comportamiento dinâmico del programa, más concretamente de la frecuencias de ejecución de los bloques del programa, esto es, de las secuencias de operaciones que son ejecutadas secuencialmente sin bifurcaciones o selecciones. Para realizar el estudio dinàmico del comportamiento del programa se hacen suposiciones sobre el flujo de control del mismo que permite hacer estimaciones de las frecuencias de ejecución (Ra75). Una vez conocido su comportamiento, se hacen comparaciones entre las realizaciones microprogramadas de los bloques del programa y sus versiones originales en lenguaje máquina. Finalmente se consideran las frecuencias esperadas de los bloques y aquellos bloques que generen un mayor ahorro de tiempo de ejecución se seleccionan como nuevas instrucciones maquina.

Estos dos métodos presentados por Rauscher para definir arquitecturas orientadas a aplicaciones, usan sólo

parte de la información disponible, es decir, el primer mètodo define instrucciones que aparecen globalmente a lo largo del programa sin considerar el comportamiento dinàmico del mismo, y el segundo define instrucciones que son locales a una parte del programa, no teniendo en cuenta las operaciones que constituyen los bloques a lo largo del programa. Por esta razón el propio Rauscher propone combinar ambos mètodos. El nuevo mètodo es similar al de las secuencias de instrucciones pero al que se añaden las frecuencias de ejecución de las secuencias para seleccionar las nuevas instrucciones.

En el proceso de selección de las nuevas instrucciones, Rauscher elige aquellas secuencias que producen un

mayor ahorro de tiempo por cada palabra de la memoria de

control. El procedimiento detallado es como sigue :

- 1 Calcular la frecuencia esperada de ocurrencia para los bloques del programa. Llamamos V1, V2, ..., Vt a los elementos de este vector.

- 2 Encontrar todas las secuencias que aparezcan en dos o más partes del programa. Añadir todas las secuencias que constituyan bloques básicos.

- 3 Calcular el número de apariciones ponderado para cada secuencias diferente.

$$Qi = \sum_{j=1}^{t} Nij \forall i$$

donde Nij es el número de veces que la secuencia "i"

aparece en el bloque "j".

4 - Calcular el tiempo de ahorro ponderado por espacio de la memoria de control para cada secuencia.

donde Xi = número de microinstrucciones necesarias para interpretar la secuencia "i", y Si es el tiempo ahorrado al ejecutar la secuencia "i".

5 - Repetir las siguiente operaciones hasta agotar el vector Y o llenar la memoria de control totalmente.

a- Encontrar el mayor elemento de Y (Yi màximo) cuya versión microprogramada no supere el tamaño de la memoria de control disponible. Lo llamaremos elemento K-esimo.

b- Añadir el microprograma de interpretación de la secuencia "K" a la memoria de control.

c- Representar todas las ocurrencias de las secuencia "K" en el programa en lenguaje intermedio por una nueva instrucción en lenguaje màquina.

d- Reevaluar Nij, Qi y Yi para todas las secuencias que sean subsecuencias o supersecuencias de la secuencias "K".

e- Borrar el elemento K-esimo del vector Y para eliminar posteriores consideraciones.

6 - Representar las restantes operaciones en el programa por instrucciones en lenguaje màquina que son interpretadas por microprogramas estandar en la memoria de control. Dado que este procedimiento de sintesis de la arquitectura no considera todas las secuencias simultaneamente, pueden aparecer situaciones en las que no se den resultados óptimos.

Esta tècnica fuè implementada y verificada en un entorno de simulación y la mejora de comportamiento obtenida fuè alrededor del 25 por ciento para los programas de aplicación seleccionados.

Una metodologia analitica mas rigurosa ha sido desarrollada por Luque y Ripoll (Lu81b), la cual introduce una fase de análisis dinámico.

Este proceso de adaptación comprende los siguientes pasos :

- 1 Un analisis estatico del programa (Lu80a) con objeto de identificar todas las secuencias de instrucciones que puedan ser microprogramadas. Las secuencias seleccionadas las denominaremos "secuencias microprogramables".

- 2 Un anàlisis del comportamiento dinàmico del programa para obtener el perfil de ejecución dado un conjunto de datos de entrada representativo..

- 3 Una evaluación del tiempo de ahorro que se producirla al microprogramar cada secuencia microprogramable (Lu80b).

- 4 Una selección de aquellas secuencias microprogramables que generen un mayor tiempo de ahorro durante la ejecución del programa (Lu80c). Las secuencias seleccionadas (primitivas) serán representadas por simples instrucciones de lenguaje máquina.

Estos autores plantean la resolución práctica del proceso de selección de las secuencias que seben ser migradas, dado el tamaño limitado de la memoria de control, como un problema de programación lineal binaria; el problema del Knapsack, el cual es de complejidad exponencial. Como alternativa a este método proponen la resolución de la selección mediante un algoritmo que proporciona una solución aproximada de complejidad polinômica. En (Di87) y (Lu87b) se muestran los resultados de este algoritmo aproximado.

Un enfoque similar al que acabamos de describir es el que dan Holtkamp y Wagner en (Ho84), en èl tambièn se plantea el problema de la selección de candidatos a ser microprogramados como el problema del Knapsack (complejidad exponencial) y se propone un algoritmo aproximado con el que se obtienen resultados muy pròximos a los teòricos, siendo aplicado al caso particular del sistema operativo UNIX.

#### I.1.3 ADAPTACION DE LA ARQUITECTURA EN TIEMPO DE EJECUCION

Los mèritos esenciales de los mètodos descritos la eliminación del trabajo humano, justamente en un campo donde la habilidad y manejo de la estructura fisica de la màquina son fundamentales. Las ganancias obtenidas por los metodos descritos fueron muy alentadoras y en muchos casos competitivas con las obtenidas por tècnicas de tuning manual. Todo ello hace pensar, creemos de forma realista, en ir hacia una automatización completa del proceso de Tuning. Para conseguir esto es preciso que el proceso de Tuning sea continuo y en tiempo real con la ejecución del programa, y no una actividad aislada, previa a la ejecución del programa. La optimización de un proceso global generalmente es dificil y puede conducir a soluciones no optimas, sin embargo tiene sentido intentarlo si examinamos los puntos que quedan por resolver. (B183)

En primer lugar, ninguno de los mètodos mencionados es completamente transparente al usuario. El Tuning se obtiene en una o más ejecuciones especialmente realizadas a tal efecto previamente a la ejecución real. De este modo es automático pero no transparente.

En segundo lugar, el Tuning està basado en un perfil de ejecución particular, con conjuntos de datos particulares. Esta es la critica que Rauscher y Agrawala hacen de los mètodos heuristicos, pero su mètodo està basado en estimaciones hechas en tiempo de compilación, menos especi-

fico, pero más irrealizable que las medidas hechas en tiempo de ejecución. Este problema fue también claro para El-Ayat y Howard, quienes después de hacer el Tuning de la arquitectura, proponían un periodo de observación para verificar la adaptación de la nueva arquitectura y en caso negativo rehacer el Tuning. De forma similar en el método de Luque y Ripoll, el análisis dinámico es hecho mediante la ejecución del programa para diversos conjuntos de datos de entrada, que pretenden ser representativos de la "vida" del programa, y obteniendo un promedio de frecuencias.

En tercer lugar, el perfil de ejecución de un programa puede cambiar en función del conjunto de datos de entrada. Este es el punto mas debil, quizas, en la mayoría de mètodos que se basan en ejecuciones preliminares o en anàlisis estàticos del programa. De este modo se corre el riesgo de optimizar adecuadamente en determinados periodos de tiempo, mientras que en otros puede producirse una pèrdida de prestaciones (rendimiento). En los mètodos clásicos tendríamos una optimización de tipo estadístico.

El objetivo que en realidad se perseguía con los mètodos que se han descrito hasta ahora era el de adaptar la arquitectura de un sistema en el caso de programas que han de ser ejecutados un gran número de veces en dicho sistema, ya sean sistemas operativos o programas de aplicación, puesto que sólo en estos casos se justifican todas las fases de estudio de las secuencias microprogramables que se requieren

previamente a la ejecución de dichos programas.

En el presente trabajo, el problema que nos hemos planteado es el de conseguir dar un paso más allà de los conseguidos con los métodos hasta ahora existentes, es decir, pretendemos dotar al proceso de adaptación de la arquitectura de un sistema de características tales como (B183):

- 1 TRANSPARENCIA es decir, que el proceso de tuning se realice al margen del usuario, sin necesidad de que este deba llevar a cabo ningún proceso de anàlisis y estudio de la microprogramabilidad de las secuencias del programa; y por otra parte que sea operativo para cada ejecución del mismo.

- 2 Que sea **ADAPTIVO.** Que siga constantemente el perfil de ejecución de un programa.

- 3 Que se igualmente eficiente en medios estacionarios, quasi-estacionarios y no-estacionarios.

En general, y con objeto de enmarcar nuestro trabajo, vamos a describir la clasificación que Shin y Malek (Sh83) hacen sobre los esquemas de migración vertical, basàndose en la forma de llevar a cabo los procesos de sintesis y carga del código migrado:

|       |          | SINTESIS |          |  |  |

|-------|----------|----------|----------|--|--|

|       |          | ESTATICA | DINAMICA |  |  |

| CARGA | ESTATICA | E/E      |          |  |  |

| CHROH | DINAMICA | E/D      | D/D      |  |  |

Esquemas de Migración Vertical según Shin & Malek

El tèrmino estàtico se refiere al hecho de que la acción se realice previamente y al margen de la ejecución real del programa, es decir off-line. Mientras que el tèrmino dinâmico supone que se realiza simultaneamente a la ejecución real del programa (on-line).

E/E: Sintesis estàtica, carga estàtica. Las secuencias candidatas son migradas y cargadas en la memoria de control, mientras exista espacio disponible para ello. Dado que el tamaño de memoria de control es limitado, no es posible migrar la totalidad del programa, por tanto se hace necesaria la selección de las secuencias candidatas a ser migradas. Este proceso de selección vendra seguido por el de generación del código migrado, su carga en la memoria y la inclusión de la nueva instrucción sintetizada en el programa original. Todos estos procesos como ya se ha dicho son realizados como tareas previas a la ejecución del programa.

E/D: Sintesis estática, carga dinámica. Requiere que el còdigo correspondiente a las secuencias seleccionadas, sea

migrado y almacenado con anterioridad a la ejecución, en una zona de la memoria principal destinada a ello. La carga en la memoria de control se lleva a cabo durante la ejecución del programa. Sólo cuando son necesarias para su ejecución, las partes migradas son llevadas desde la memoria principal a la de control.

Sintesis dinàmica, carga dinàmica. En ella las D/D secuencias candidatas han de ser migradas y cargadas en tiempo de ejecución. Comparada con los dos esquemas anteriores, esta tècnica no necesita de ningûn tiempo adicional para procesos de sintesis off-line, salvo para el proceso de los limites de los lazos. Este método es apropiado para el procesamiento paralelo, donde un procesador separado (coprocesador) sintetice el còdigo migrado mientras el programa estè en ejecución. Un ejemplo correspondería al caso en que los lazos estuvieran almacenados en la memoria principal cuando se va a ejecutar el programa. Cuando el procesador inicia la ejecución del programa, el coprocesador empieza a sintetizar (migrar) lazos, buscando sus limites e identificando su localización. Las direcciones de los lazos migrados son mantenidas en una tabla y cuando la ejecución alcanza un lazo, su código migrado es cargado en la memoria de control. Sin embargo, tal y como es presentado por Shin y Malek en su trabajo, si el procesador principal intenta ejecutar una secuencia que todavla no ha sido completamente migrada por el coprocesador, deberá esperar hasta el término de su migración. Además esta técnica precisa de un conocimiento previo de los límites de las secuencias candidatas (lazos) y su migrabilidad. Esta tècnica es especialmente adecuada en medios multiprogramados en los que a cada una de las tareas de usuario es posible dedicarle el "writable control store" en su totalidad cuando es atendida por el procesador.

#### I.2 PLANTEAMIENTO DEL TRABAJO

La estrategia de Tuning automàtico que se presenta en esta memoria, se enmarca dentro del último esquema presentado (D/D), es decir, que cumple las tres caraterísticas del Tuning ideal de Transparencia, Adaptación y Eficiencia, pero con las siguientes características diferenciales:

- La fase de generación del (microcódigo) código de las secuencias migradas es eliminada y substituida por la inclusión de un mecanismo de interconexión entre el código a ser migrado y el conjunto de nuevas rutinas de interpretación (nuevo interprete).

- Funciona sin tècnicas firmware de monitorización, y puede ser aplicado sin necesidad de conocer los limites de los lazos ni su migrabilidad (microprograma-bilidad).

- El proceso de generación de las interconexiones es hecho en paralelo con la ejecución de la instrucción,

sin añadir ningún tiempo extra al de ejecución de un programa.

El objetivo, en definitiva, es el de reducir el tiempo de ejecución de cada programa en cada ejecución, para sistemas monoprocesador, sin realizar ningún análisis offline del mismo, es decir, realizar un Tuning en tiempo real y completamente automàtico.

Para describir el sistema propuesto supongamos que estamos trabajando en una maquina con un cierto lenguaje de "K" orientado al procedimiento u orientado al problema. Supongamos también que dicho lenguaje originalmente es interpretado por un nivel inferior "J", no necesariamente consecutivo con "K". Si ejecutamos un programa escrito en el lenguaje "K", todas aquellas sentencias o instrucciones pertenecientes a estructuras repetitivas dentro del progrageneraran secuencias de rutinas de interpretación, como la decodificación, el anàlisis sintàctico, validaciones de tipos de datos, extracción de parâmetros, traslación de referencias simbòlicas, etc, completamente innecesarias después de la primera iteración. Puès bien, introduzcamos en nuestra màquina una "Unidad de Adaptación" o "Coprocesador de Adaptación" (Tuning) (Lu87a) destinada a generar una traducción de las sentencias o instrucciones a un lenguaje intermedio entre los niveles "K" y "J" que podemos llamar "J+1/2". Este lenguaje "J+1/2" es interpretado en el nivel "J", pero no por el interprete original (en "J"), sino por un nuevo interprete, atendiendo al tipo y formato del lenguaje intermedio introducido. Al ejecutar las sentencias correspondientes en el lenguaje "J+1/2", ya no serà necesario realizar aquellas fases innecesarias por su repetitividad.

Durante la primera iteración de un lazo, y simultàneamente a la ejecución de cada sentencia o instrucción, el coprocesador genera una interconexión (sentencia instrucción del lenguaje intermedio "J+1/2") entre la sentencia o instrucción "K" y su rutina de interpretación en el nuevo interprete (interprete intermedio "J+1/2"). Asi durante las siguientes iteraciones del lazo, este se ejecuta en su forma migrada (por medio de su nuevo intêrprete), ahorràndonos, como consecuencia, las fases innecesarias antes mencionadas. El coprocesador trabaja en tiempo real, es decir, en paralelo con la ejecución de cada instrucción, y sin añadir ningûn tiempo extra a la ejecución de un programa. De modo que si ejecutamos un programa sin ninguna estructura repetitiva, en una màquina que incorpore el coprocesador no sufre ninguna demora con respecto a su ejecución en una maquina que no posea dicho coprocesador.

Dado que el coprocesador debe trabajar en tiempo real y sin añadir tiempo a la ejecución normal, significa que cuando estamos en fase de búsqueda de una instrucción en la memoria principal, o de análisis sintáctico de una sentencia; simultaneamente el coprocesador debe determinar la existencia de su interconexión, por ello dicha interconexión

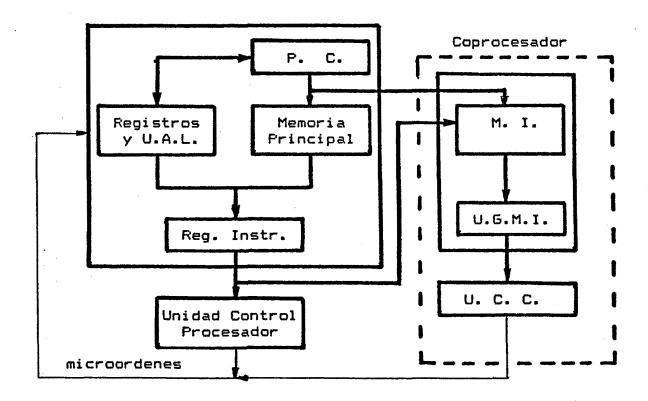

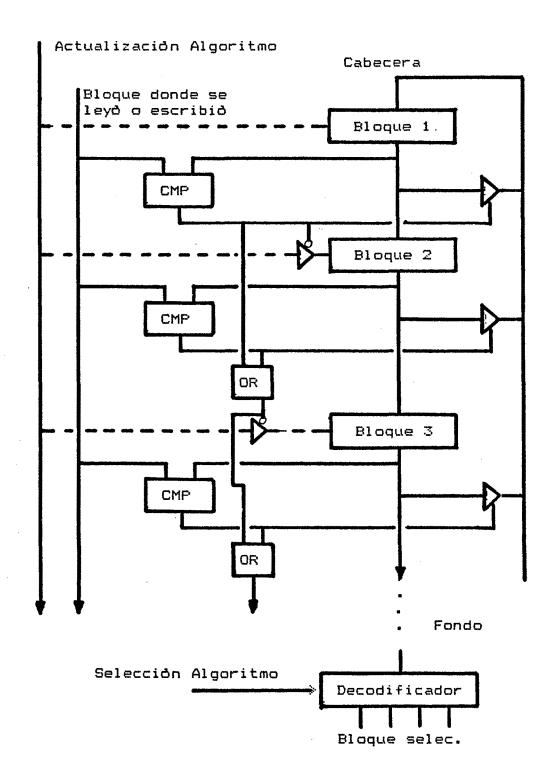

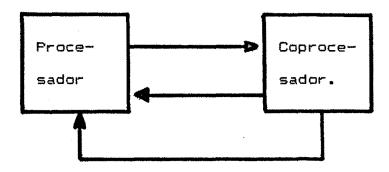

debe quedar almacenada, desde su creación, en una memoria independiente y perteneciente al coprocesador que denominamos Memoria de Interconexión (M.I.), para que este último pueda actuar sobre ella con independencia de la memoria principal (Lu86). Esta memoria de interconexión lògicamente deberà ser como minimo igual de ràpida que la principal para conocer la existencia de la interconexión lo antes posible, y nunca más tarde que la obtención de la forma original en la memoria principal. Además de la memoria de interconexión, el coprocesador incluirá una Unidad de Gestión de la Memoria de Interconexión (U.G.M.I.) y su propia Unidad de Control del Coprocesador (U.C.C.) (Fig I.1).

Figura I.1 Estructura del sistema para migración vertical dinámica

A diferencia de los métodos que han sido descritos con anterioridad, en los cuales los estudios estadísticos que precisan, los hacen globales en cuanto a su comportamiento y modo de realizar la adaptación sobre el perfil, así como a la hora de evaluar los rendimientos y ganancias sobre los tiempos de ejecución, el método que presentamos es òptimo en cuanto a su adaptación local, ya sea temporal o espacial, asignando dinàmicamente la actuación del coprocesador en los instantes y zonas del programa que más lo precisen durante su ejecución, para obtener un mayor aumento de la velocidad de ejecución, evitando la posibilidad de que en ciertos casos, el procesador deba esperar el termino de la acción del coprocesador para poder ejecutar una secuencia, como ocurre con el método propuesto por Shin y Malek (Sh83).

Se entiende por localidad espacial de un programa al hecho de que al acceder a una posición de memoria, existe una gran probabilidad de que futuros accesos nos lleven a posiciones cercanas a la actual. Este comportamiento se puede observar en la ejecución de las instrucciones, que suele ser secuencial; incluso las de salto conllevan desplazamientos generalmente cortos, esto es debido a la estructuración por bloques y/o procedimientos que definen entornos locales. En cuanto a los datos, suele ser razonable mantener próximos aquellos que tengan cierta relación lógica.

La localidad temporal se refiere a que la informa-

ciòn que puede ser utilizada en un futuro cercano, dentro de un programa, tiene una probabilidad alta de haber sido usada con anterioridad.

La capacidad de adaptación local del método presentado, lo hace especialmente adecuado en medios de multiprogramación, puesto que permite asignar toda la Memoria de Interconexión a cada programa, en cada una de sus ejecuciones sin que aparezca ningún "overhead". La migración vertical en sistemas multiprogramados también podría ser incorporada mediante los métodos clásicos, pero ello supondría un enorme overhead debido a las operaciones de actualización y/o restauración entre el Writable Control Store y la Memoria Principal. Una forma de reducir (pero no eliminar) este overhead, sería dividiendo el writable control store en bloques asignables a programas, pero como consecuencia de ello asignará poca capacidad de WCS a cada uno de los programas.

Justamente aprovechando la localidad de los programas durante su ejecución, podríamos ver nuestra Memoria de Interconexión como una memoria cache, la cual con un adecuado sistema de gestión, se adapte dinâmicamente al perfil de ejecución. Lo que separa conceptualmente nuestra M.I. de la memoria cache, es que en M.I. no se almacena directamente código mâquina sino instrucciones de lenguaje intermedio ("J+1/2"), posee una organización particular para facilitar la búsqueda de las interconexiones (la inclusión de estas se hace una a una, por palabras) y no manejamos ninguna

información relativa a los datos. For ello nuestra M.I. podria verse como una generalización del concepto de memoria cache por cuanto la información almacenada en ella no mantiene el mismo formato ni el mismo nivel de lenguaje, y ni siquiera la misma cantidad de información; lo cual implicará un proceso diferente (más simple y rápido) de interpretación. For otro lado en nuestra formulación la "posición conceptual" de la M.I. va ligada a la "posición" de los lenguajes implicados (dentro de la jerarquía de lenguajes de un sistema informático). Esto no implica necesariamente la creación de un nivel diferenciado (por velocidad) como en el caso de la memoria cache, sino que define un nuevo "nivel" en razón del formato adoptado y del interprete que actuarà sobre ella. Lo que si implicaría es la existencia de un almacenamiento propio para las interconexiones, para permitir la simultaneidad en el acceso a la forma codificada original y a la migrada (interconexiones).

La Memoria de Interconexión deberà ser mucho más pequeña que la memoria principal, los factores fundamentales que nos conducen a ello son :

- Al tratar de implementar un mecanismo de optimización dinàmico, local y adaptivo, el recurso debe de

estar en consonancia con el "tamaño" de la localidad

existente en un programa (temporal y espacial), lo que

implica un tamaño reducido.

- Al ser un mecanismo dinâmico, local y adaptivo, un

tamaño pequeño implicará un uso intensivo del mismo produciendo un uso más eficiente del recurso.

- Su duplicidad (respecto a un nivel ya existente) o nueva incorporación (nuevo nivel más rápido) hacen necesario reducir su coste.

La desventaja que presenta un tamaño reducido y que es semejante a la que aparece en la memoria cache (Sm82), es la existencia de fallos de pagina (carencia de interconexión) con toda la problematica que rodea su resolución:

- Elección del tamaño total de M.I.

- Elección del número de bloques en que se particione

M.I..

- Asignación de las p\u00e4ginas y bloques (Mapping). Entendiendo por p\u00e4gina y bloque lo mismo que se entiende en esquemas de memoria virtual (p\u00e4gina de memoria principal, bloque f\u00e1sico de M.I.)

- Localización de una referencia.

- Resolución de fallos de interconexión o fallos de pàgina cuando la memoria està completamente llena. Algoritmo de reemplazamiento.

- Minimizar los fallos de p\u00e4gina con un algoritmo de reemplazamiento adecuado.

La solución a todos estos puntos se consigue con

una buena partición de la M.I. y una adecuada U.G.M.I. que incluya un algoritmo de reemplazamiento lo más eficiente posible.

El tamaño de los bloques en que se particione la M.I. es uno de los parâmetros fundamentales que influirà de forma decisiva en la ganancia en velocidad del sistema. tamaño de bloque pequeño tiene la ventaja de que permite una mejor adaptación al perfil de ejecución de un programa, puesto que proporciona una partición más fina de M.I., y ademàs disminuye la probabilidad de que los bloques de M.I. contengan información que no se vaya a necesitar. La desventaja es obviamente el alto costo que representa, puesto que una partición fina supone un gran número de bloques y ello significa replicar para cada bloque toda la circuitería necesaria para su control. Si los bloques son grandes, disminuimos de forma importante la complejidad del hardware y en consecuencia los costes, la contrapartida la constituye una particiòn mucho màs gruesa que no permite una adaptación tan buena al perfil real de ejecución de un programa

## I.3 ESTRUCTURA DEL SISTEMA

El desarrollo del método presentado se ha realizado para el caso particular de Adaptación Dinàmica, o proceso dinàmico de aceleración de programas, entre Lenguaje Màquina ("K") y Microprogramación ("J"), pero los resultados obtenidos pueden generalizarse conceptualmente a la migra-

ciòn entre dos niveles de programación cualesquiera. Los motivos por los que se ha elegido el lenguaje máquina y la microprogramación para este trabajo son los siguientes:

Estos son los niveles más cercanos a la propia estructura de la máquina y por ello es posible manejar directamente los recursos de la misma. La estructura propuesta resultará más clara en cuanto a las interacciones existentes entre las diferentes partes del sistema. Así mismo la estructura del coprocesador puede ser definida a nivel de microprogramación, lo cual facilitaria su concepción en la fase experimental.

- El nuevo interprete es escrito directamente en microprogramación, y en la mayorla de los casos bastará con introducir modificaciones a los microprogramas originales que interpretaban el lenguaje máquina. En (So82) se describe un sistema que facilita el diseño y la depuración de microprogramas, permitiendo durante su depuración actuar directamente sobre el hardware al que definitivamente iran destinados. Esta herramienta permitiría el desarrollo y depuración del nuevo interprete

- Estos dos niveles (màquina y microprogramación) corresponden al caso màs desfavorable a la hora de obtener ganancias en velocidad en una màquina, puesto que las fases de decodificación, anàlisis sintàctico, validaciones de tipos de datos, extracción de parametros etc, cuyo ahorro en niveles superiores puede suponer enormes ganancias de tiempo, en estos dos niveles en concreto se reducen a las fases

de búsqueda y decodificación de la instrucción. Es por ello que con la elección de estos dos niveles tratamos de establecer la cota inferior de la ganancia en velocidad de ejecución que se puede obtener en un sistema que incorpore este método.

Partiendo puès desde ahora de un sistema microprogramado describimos cual es la estructura y funcionamiento del Tuning desarrollado en esta memoria.

Dado que los microprogramas originales de la màquina, almacenados en la memoria de control de la misma, interpretan las instrucciones màquina del repertorio del procesador, cuando se ejecute una instrucción cuya interconexión haya sido creada y por tanto ya existe, deberà ser ejecutada sobre el nuevo intérprete, el cual estará almacenado en la unidad de control del coprocesador.

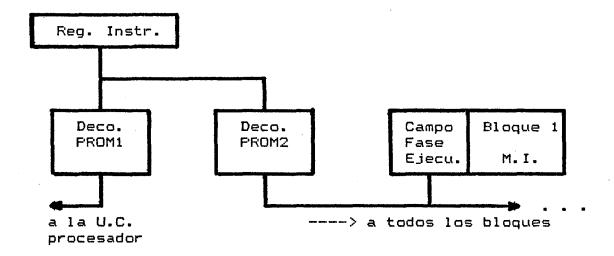

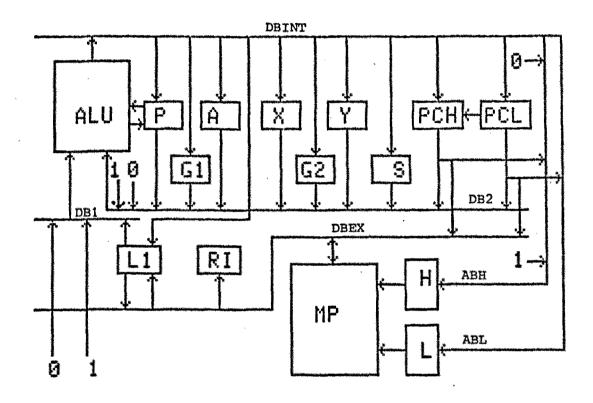

El coprocesador està organizado alrededor de tres unidades básicas :

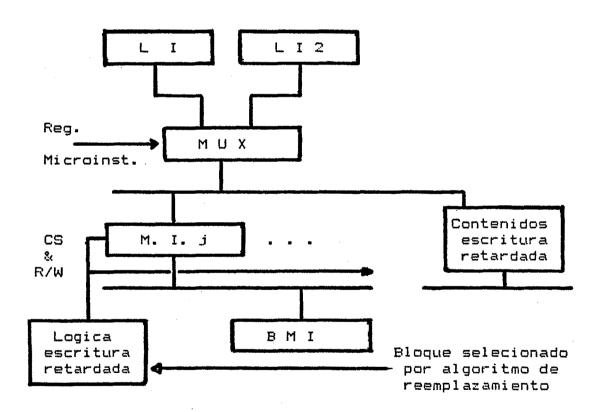

La Memoria de Interconexión (M.I.), la cual almacena las interconexiones correspondientes a las instrucciones màquina pertenecientes a una "ventana" del programa en ejecución en la memoria principal. Esta ventana està constituida por la zona del programa donde el caracter dinàmico del algoritmo ha hecho que se aplique actualmente su capacidad de adaptación local.

Dicha zona crecerá en tamaño a medida que avance la ejecución hasta encontrar una instrucción de vuelta atràs, o completar su capacidad total de almacenamiento. Cada "interconexión" es en si misma una "sentencia del lenguaje intermedio J+1/2" y ocupa una sola palabra de la M.I.. Por las razones ya expuestas, el tamaño de la M.I. es una pequeña fracción del de la memoria principal y ha sido organizada en bloques.

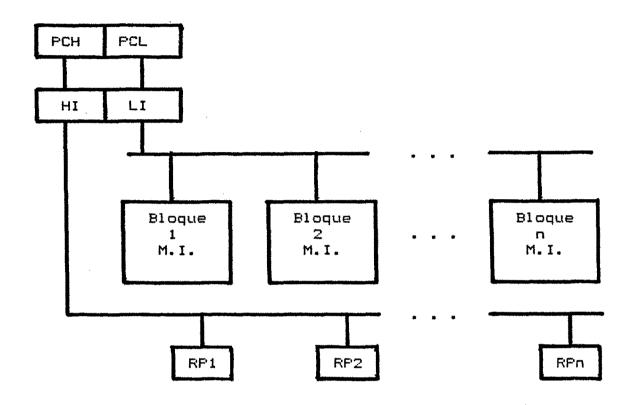

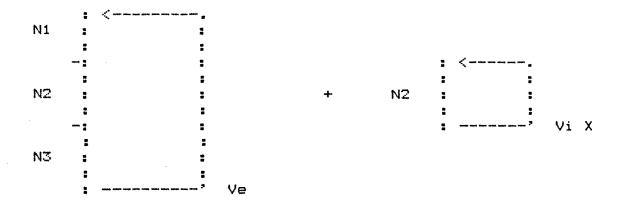

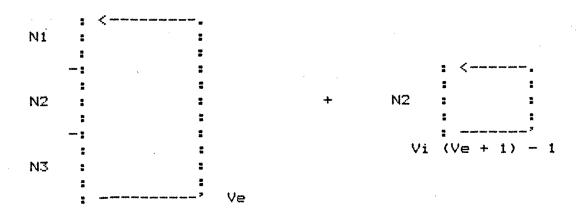

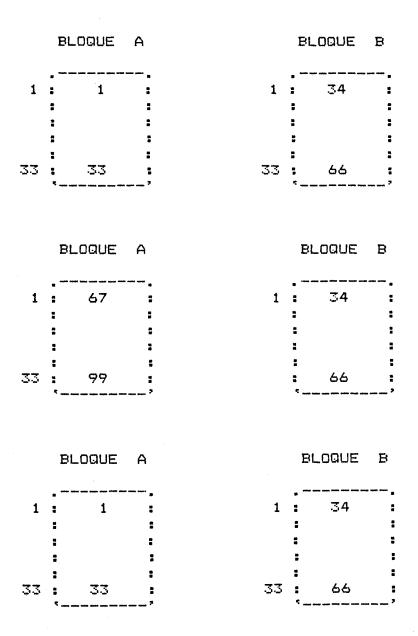

La Memoria de Interconexión tiene un tiempo de ciclo igual al de la memoria de control del procesador y està organizada en bloques físicos con objeto de permitir una adaptación eficiente al perfil de ejecución y facilitar el manejo de la información que constituyen las interconexiones. La memoria principal està conceptualmente organizada en páginas de igual tamaño al elegido para los bloques de la M.I.. Esto hace posible establecer una correspondencia (Mapping) entre las páginas de la memoria principal y los bloques de la M.I..

La Unidad de Gestibn de la Memoria de Interconexibn (U.G.M.I.), que maneja las interconexiones y soporta el proceso de "mapping" entre las pàginas de la

memoria principal y los bloques de la memoria de interconexibn. Para realizar esta estrategia y soportar el

manejo de la estructura de bloques, se ha incorporado

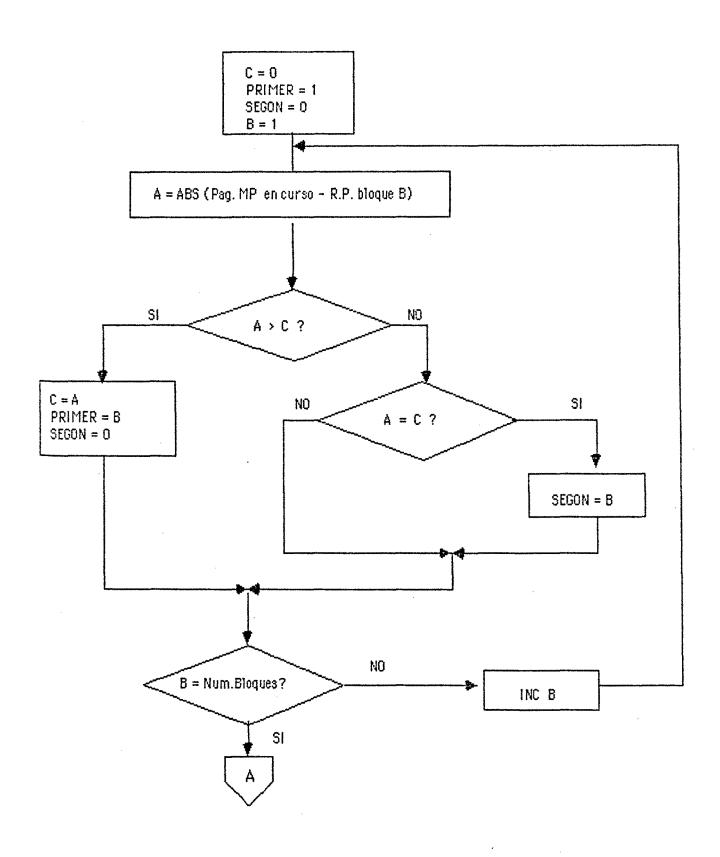

un algoritmo que además resuelva los fallos de pàgina y

determine que bloques han de ser reemplazados en cada

caso. Dado que la ejecución del programa avanza en incrementos de una página, la ventana de interconexiones crecerà también en incrementos de un bloque, y el algoritmo selecciona el bloque vacío a ser ocupado en cada momento. Cuando la ventana alcance su tamaño màximo permitido (el tamaño total de M.I.) y se aborda una nueva página del programa, el algoritmo selecciona el bloque que debe ser reemplazado, creando un deslizamiento dinâmico (scroll) de la ventana a lo largo del programa.

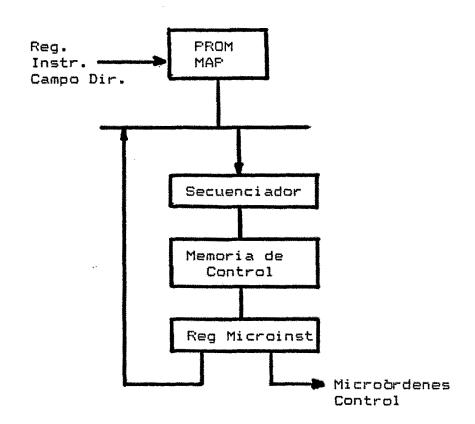

La Unidad de Control del Coprocesador (U.C.C.),

que contiene los microprogramas para controlar al coprocesador y el interprete intermedio, para que tome el

control del sistema durante la ejecución de las instrucciones que tienen su correspondiente interconexión

(instrucción del lenguaje intermedio) almacenada en la

M.I..

## I.4 FUNCIONAMIENTO DEL SISTEMA

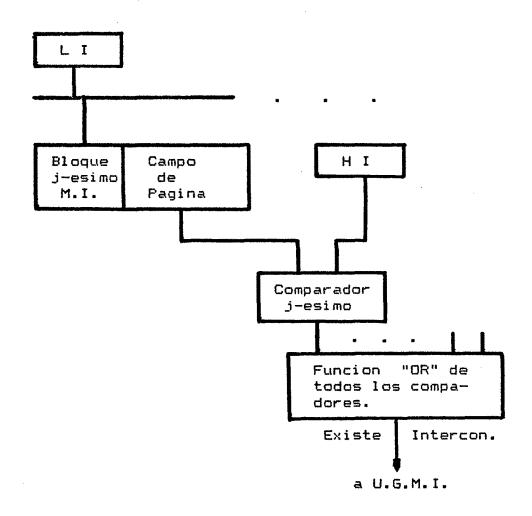

Al iniciar la ejecución de una instrucción màquina, en su fase de búsqueda, se lanza simultaneamente una operación de lectura de la interconexión de esta instrucción en la M.I.. Todos los bloques son direccionados en paralelo para que en caso de que la interconexión estuviera en algún bloque, con independencia de cual sea, pueda ser obtenida.

En este punto hemos de distinguir las dos posibilidades, que exista la interconexión o no :

la interconexión no existe en ninguno de los abloques de la M.I., la operación de lectura que se inició en M.I. es abandonada y el sistema espera la obtención de instrucción desde la memoria principal. Cuando la instrucciòn ha sido leida, el decodificador proporciona la dirección de comienzo de la fase normal de interpretación (ejecuciòn) de la instrucciòn. En paralelo, se crea su interconexiòn (instrucciòn del lenguaje intermedio), escribiendo en M.I., la dirección de comienzo de la fase de interpretación sobre el nuevo interprete, las direcciones de los operandos y todos los parametros de la instrucción (obtenidos del registro de instrucciones). Para realizar esta escritura, el algoritmo seleccionarà el bloque vacío donde deberà ser insertada la interconexión, y en caso de no existir ningún bloque libre (fallo de página) el algoritmo señalará cual debe ser reemplazado. Es necesaria la actualización del algoritmo de reemplazamiento para su posterior utilización en otros accesos. De esta manera el proceso de generación de la interconexión no añade ningún tiempo extra al tiempo normal de ejecución (Lu85).

Si la interconexión existe en alguno de los bloques porque la instrucción ha sido ejecutada anteriormente, la lectura iniciada en la memoria principal ya no hace falta finalizarla y es abandonada. La interconexión contiene la dirección de comienzo de la fase de interpretación interme-

dia, por lo que podemos atacar su ejecución directamente obviando las fases de búsqueda y decodificación de la instrucción. En paralelo se actualiza el algoritmo de reemplazamiento para su uso posterior.

Es importante destacar que en el caso en que la migración vertical se haga entre lenguaje máquina y microprogramación, que es el caso que nos ocupa, el tratamiento dinàmico posee una ventaja adicional sobre el estàtico y que consiste en el hecho de que para el caso estàtico todos los segmentos migrados deben estar simultánemante almacenados en el writable control store, lo cual hace que el número y tamaño de las secuencias migradas estê limitado por el tamaño de èsta. En nuestro caso se almacena en M.I. una interconexión (una palabra) por cada instrucción que sea ejecutada, por lo cual el tamaño de la M.I. sólo limita el tamaño máximo del lazo que puede capturar. En definitiva, el caso estàtico es global en si mismo mientras que el caso que se presenta (dinàmico) es fuertemente local.

#### I.5 PARAMETROS DE DISEÑO

A la hora de incorporar nuestro coprocesador, en un caso real, para dotar a un sistema del mecanismo de Tuning, es preciso encontrar un compromiso entre las prestaciones adquiridas por el sistema y el coste que ello implica. Los principales paràmetros que influyen en esta relación

de una forma más directa son : el tamaño total asignado a la M.I., el número de bloques en que se particione dicha memoria y el algoritmo de reemplazamiento que se elija. Por otra parte, de forma general también influirá el lenguaje intermedio definido, por las siguientes razones :

El formato de las instrucciones del lenguaje intermedio influye en el tamaño de las palabras de la M.I.

El nivel del lenguaje intermedio influirà en la estructura y tamaño del interprete intermedio, por tanto en el tamaño de su soporte físico en el coprocesador.

Tambièn influirà en la velocidad, dependiendo de la ganancia que suponga sobre el còdigo original.

En el caso de una partición elevada de M.I., es decir, dividirla en un gran número de bloques, aunque el tamaño de cada bloque sea pequeño (caso ideal), se consigue para el coprocesador una muy alta capacidad de adaptación al perfil de ejecución de los programas, incluso en el caso de que las secuencias lineales que conformen un lazo, se encuentren muy distantes entre si. La contrapartida que se produce ante este hecho, consiste en que al aumento del número de bloques viene acompañado de un aumento también importante del coste del sistema, debido a toda la circuitería de control que lleva asociado cada bloque, así como la necesaria para la comunicación de cada bloque con su bus.

El algoritmo de reemplazamiento debe ser implementado directamente a nivel de circuito, de este modo se consigue que la resolución de los fallos de página no supongan la adición de un "overhead" al tiempo de ejecución normal del programa. Ello hace que la complejidad y por tanto el coste de dicho algoritmo crezca rapidamente con el número de bloques de la M.I.. Lo mismo ocurre con toda la lògica responsable de la localización de las interconexiones en M.I. así como con su creación y almacenamiento cuando sea preciso.

## I.6 COMPORTAMIENTO DEL SISTEMA

miento del coprocesador en operación en un sistema dado, y estudiar la incidencia de algunos de los parámetros antes mencionados sobre las prestaciones, ha sido desarrollado un programa de simulación, descrito en el capítulo tercero, el cual además nos permitirà establecer criterios para la elección de la configuración más conveniente para cada caso, estableciendo como objetivo final un modelo matemático de comportamiento del sistema con el coprocesador, para que de una forma algoritmica ser capaces de predecir el comportamiento y las ganancias en velocidad para una configuración elegida y un programa dado.

Considerando las capacidades de adaptación local del método propuesto para la realización de Tuning mediante la Migración Vertical Dinàmica, es lógico pensar que el tipo de estructura que debíamos elegir para el estudio del com-

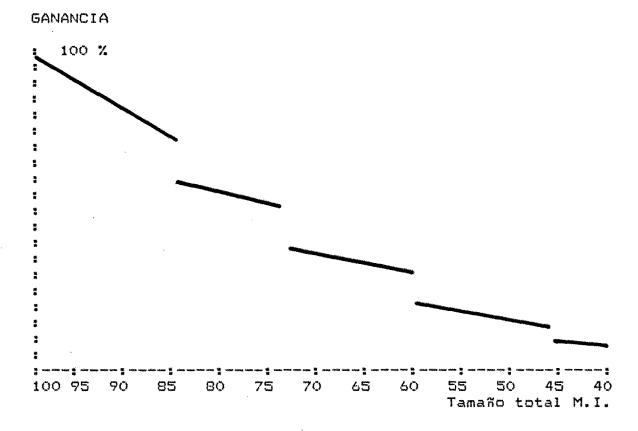

portamiento del coprocesador, y en particular analizar el del algoritmo de reemplazamiento, es la del lazo simple, o estructuras tipo lazo en general (Al76), debido a que cualquier estructura repetitiva puede ser reducida al final a un simple lazo, y es en estas estructuras donde se producirán las ganancias en velocidad de ejecución. Lo que hace que el método sea localmente adaptivo al perfil de ejecución de un programa, de forma dinâmica, es el hecho de que si un lazo es capturado por el coprocesador en la M.I., es decir, el lazo está totalmente traducido al lenguaje intermedio "J+1/2", la ganancia en velocidad obtenida al ser ejecutado el lazo de forma migrada, lo será con independencia de la complejidad de la estructura a la que pertenezca el lazo.

Los programas de simulación que se han desarrollado permiten analizar el comportamiento de los programas

sobre un sistema que incorporase el coprocesador para migración vertical en tiempo de ejecución, midiendo parâmetros

tales como el número total de instrucciones ejecutas en un

programa, el número de instrucciones ejecutadas en su formato de lenguaje "J+1/2", la ganancia total en velocidad

obtenida, etc. Los simuladores aceptan dos tipos de parâmetros de entrada:

## Paràmetros del programa :

Descripción de la estructura estàtica del programa

(de forma esquemàtica) mediante su diagrama de flujo.

- Descripción del flujo de control del programa de forma deterministica o probabilistica.

- Parametros para el coprocesador :

- Características de la M.I. : Tamaño total y número de bloques de la partición.

- Tipo de algoritmo de reemplazamiento.

La simulación permite incorporar dos filosofías diferentes a la hora de tratar la ejecución del programa, una determinística en la cual las rupturas se secuencia en el programa, es decir las vueltas atras en los lazos se expresan mediante el número de veces que se ejecuta dicho lazo y otra mas general en que las rupturas de secuencia (no ligadas necesariamente a lazos) se expresan mediante una cierta probabilidad de salto (probabilista).

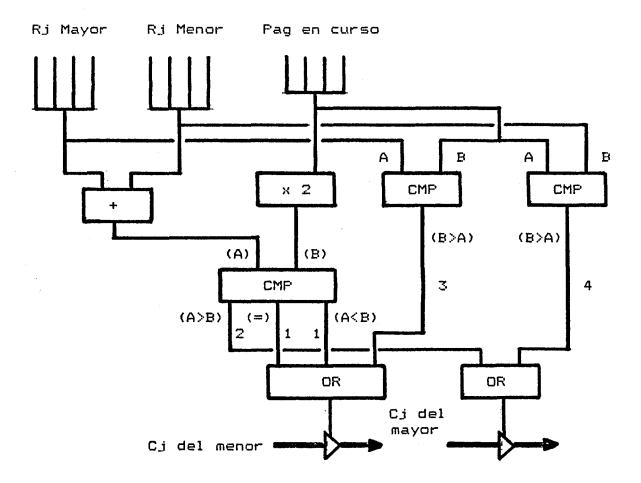

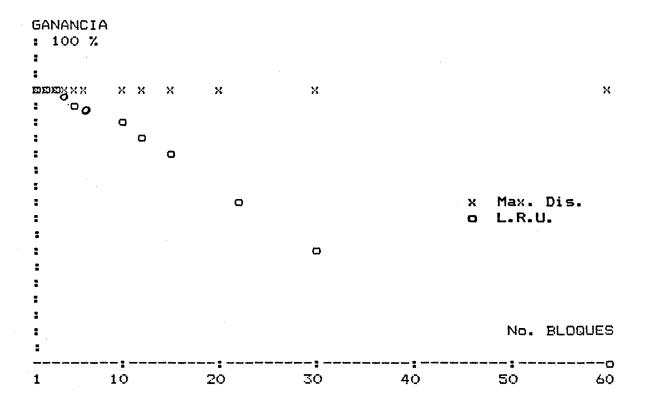

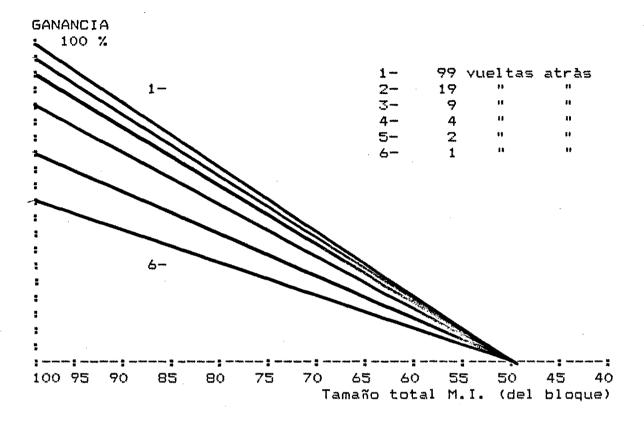

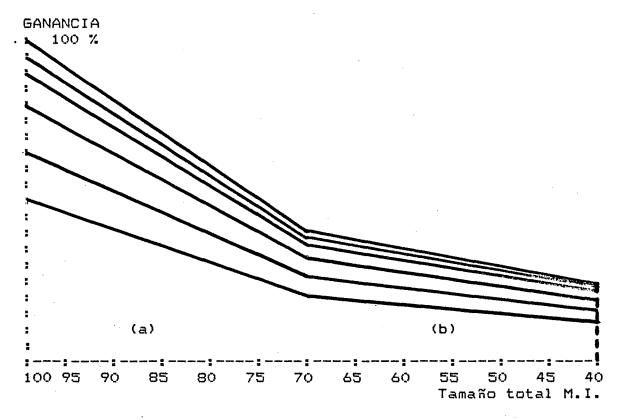

El anàlisis de comportamiento ha sido hecho para dos algoritmos de reemplazamiento distintos: un algoritmo L. R. U. (Last Recently Used / menos recientemente utilizado) y un algoritmo de Màxima Distancia (M.D.). El algoritmo de Màxima Distancia como bloque a ser reemplazado o reasignado, aquel, de entre todos, que en la actualidad contenga la página más alejada en el espacio de direcciones, de la que se halla en curso. Se ha comprobado que para los lazos que son capturados en su totalidad dentro de la M.I., las ganancias obtenidas con ambos algoritmos son

idènticas, pero que cuando el tamaño del lazo es superior al de la M.I. el algoritmo de L.R.U. nos dà ganacia cero y el de Màxima Distancia hace que la ganancia disminuya gradual-mente al crecer el tamaño del lazo, hasta alcanzar el cero.

Para ilustrar la incorporación del coprocesador en un sistema, se ha desarrollado a modo de ejemplo su inclusión en un sistema basado en el microprocesador R6502. Dado que dicho microprocesador està construido en un circuito integrado, de forma que no es posible acceder a las diferentes partes del mismo, se ha desarrollado la estructura de un microprocesador microprogramado y microprogramable que emule (respetando los mismos diagramas de tiempo) al R6502. Este microprocesador se ha elegido por el hecho de que existe una realización de una unidad de control orientada a la emulación del R6502 (S082) (B184) y han sido desarrollados los microprogramas necesarios para la emulación del R6502, a partir de los cuales se ha llevado a cabo la realización de un simulador de dicho microprocesador (He86).

## CAPITULO II

## ESTRUCTURA Y FUNCIONAMIENTO DEL SISTEMA

Como se ha descrito en el capitulo anterior, la implementación de la adaptación dinàmica de la arquitectura de un sistema, supone la adición al mismo de un coprocesador que realice las funciones necesarias para la creación de la versión en lenguaje "J+1/2" del programa original. La estructura que se describe, corresponde al caso de adaptación de la arquitectura en el nivel de lenguaje máquina, mediante la migración a un lenguaje intermedio entre el lenguaje máquina y la microprogramación.

## II.1 ORGANIZACION Y MODO DE OPERACION DEL COPROCESADOR

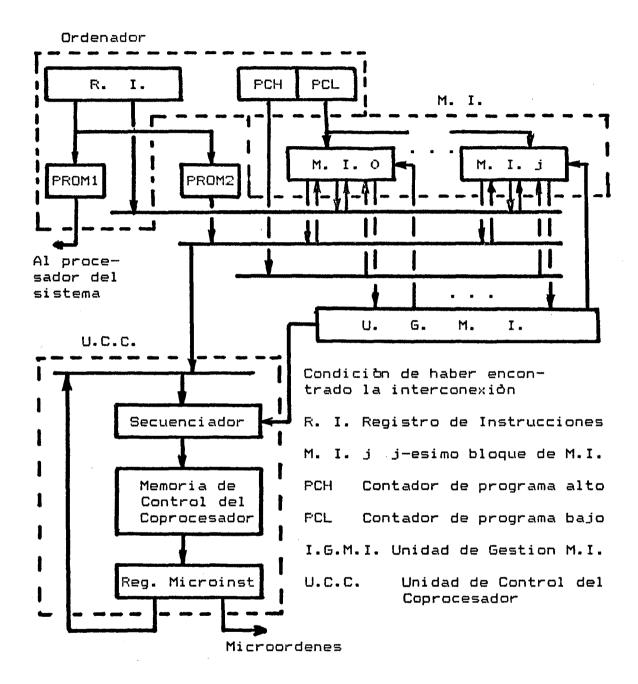

El coprocesador està organizado alrededor de tres unidades bàsicas (figura II.1): La Memoria de Interconexión (M. I.) donde se almacenan las instrucciones del lenguaje de nivel "J+1/2", que hemos llamado "interconexiones", la Unidad de Gestión de la Memoria de Interconexión (U. G. M.

I.) que lleva a cabo la manipulación de la información almacenada en la memoria de interconexión, y la Unidad de Control del Coprocesador (U.C.C.) que proporciona el control

Figura II.1 Estructura del Coprocesador

de las unidades del coprocesador y almacena el intèrprete del lenguaje "J+1/2". A continuación se describen detallada-

mente cada una de la unidades mencionadas.

## II.1.1 FUNCIONAMIENTO DEL SISTEMA

En este apartado se intenta dar una idea de conjunto de cual es el funcionamiento global de un sistema que incorpore el mètodo propuesto.

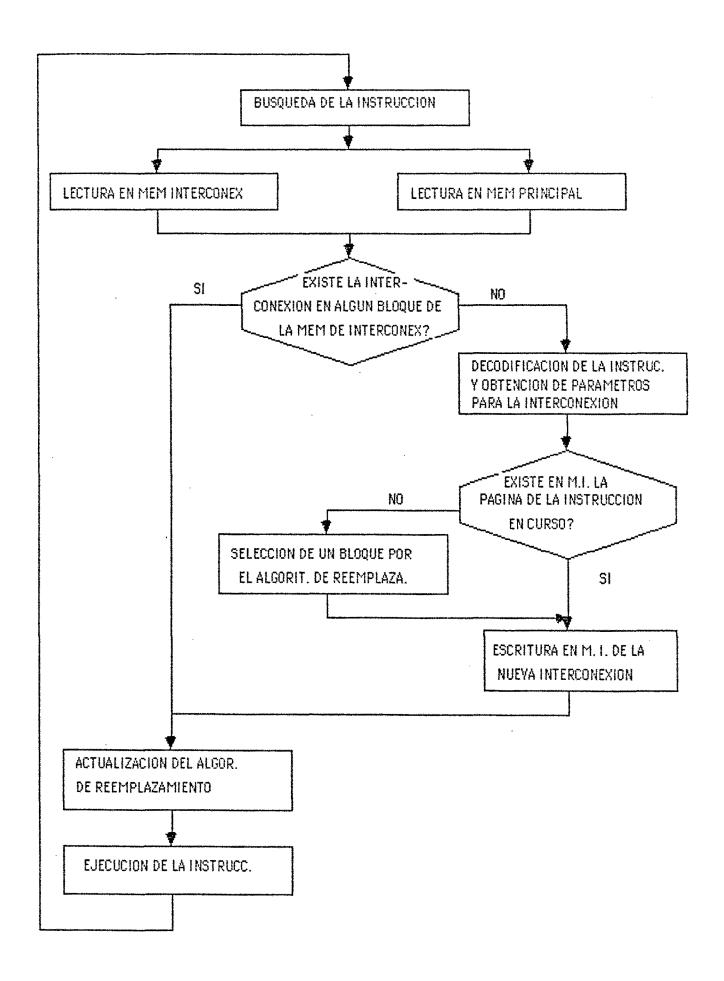

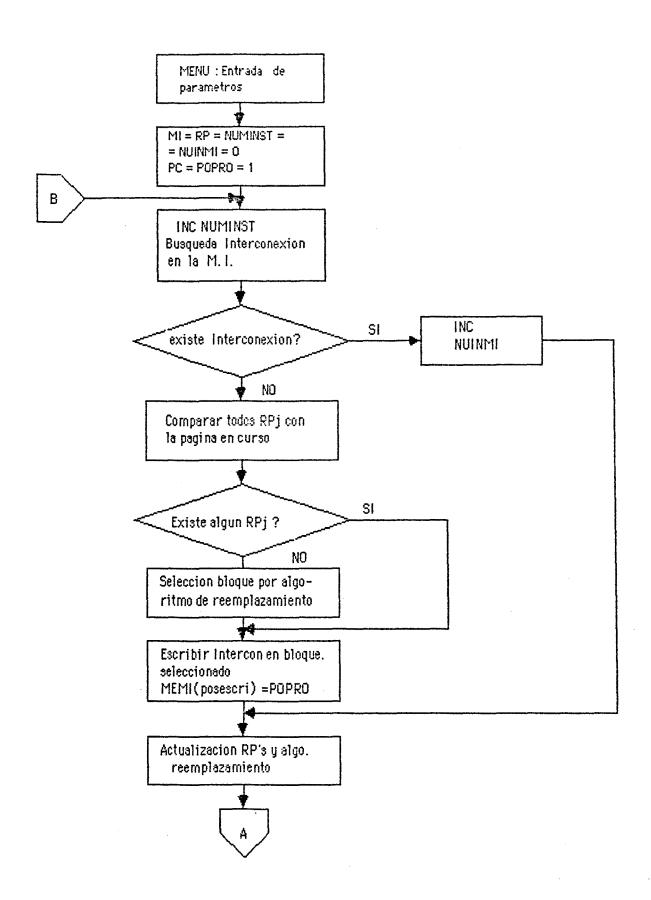

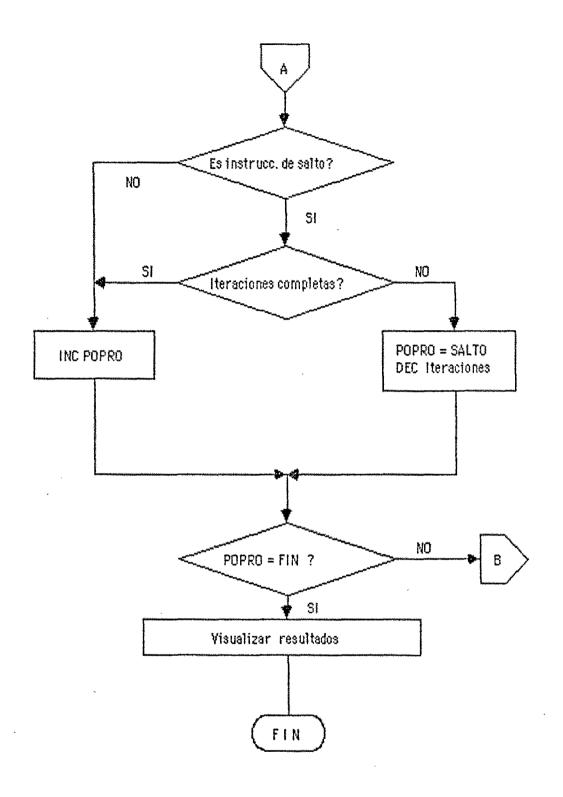

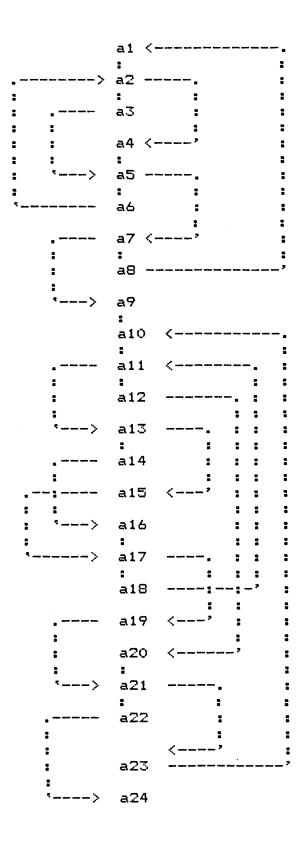

En la figura II.2 se muestra un diagrama general de flujo donde se recojen las principales operaciones que se realizan durante la actuación del coprocesador, en tiempo de ejecución de un programa, para la interpretación de una instrucción en su forma normal y en su forma migrada al lenguaje "J+1/2".

En primer lugar vamos a partir del supuesto de que la instrucción que se va a ejecutar, no lo ha sido nunca con anterioridad, o se ha perdido (se genero una nueva interconexión en su lugar), y que por tanto no existe en la M.I. ninguna interocnexión que haga referencia a ella.

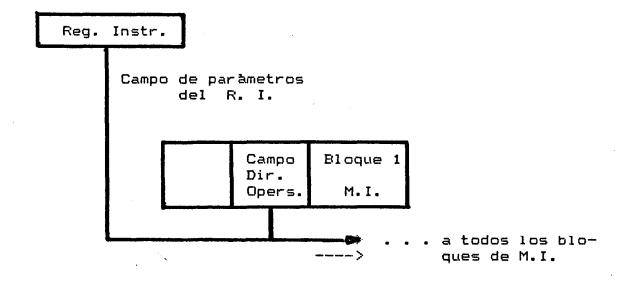

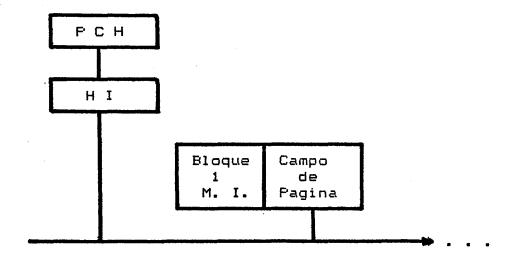

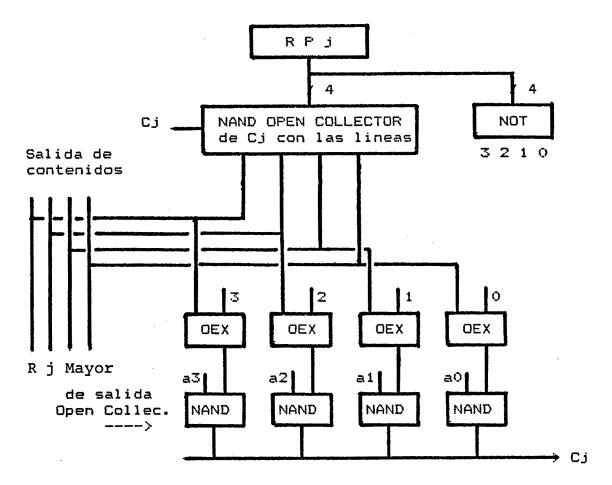

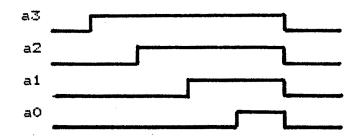

Al iniciarse la fase de búsqueda de la instrucción , se da comienzo a la lectura de la instrucción en la memoria principal, direccionándola con el contenido actual del registro contador de programa. Simultàneamente a esta lectura, se inicia otra lectura en la memoria de interconexión. Esta última lectura se realiza, en paralelo, sobre todos los bloques, direccionados al mismo tiempo por la parte baja del

Figura II.2 Funcionamiento del Sistema

contador de programa (PCL).

Dado que se ha considerado que la interconexión de esta instrucción todavía no existe, el resultado de la lectura sobre todos los bloques de M.I. serà infructuoso, debido a ser negativas todas las comparaciones realizadas entre la indicación (dentro de la interconexión) de la pàgina de la memoria principal a la que pertenece la interconexión leida y el valor actual de la parte alta del registro contador de programa (PCH) (pàgina en curso).

La lectura realizada sobre la M.I. es obviada y se continúa la fase de búsqueda de la instrucción que supone esperar el resultado de la lectura de la memoria principal. Una vez obtenida la instrucción, esta será cargada en el registro de instrucciones y decodificada. Hecho esto, entraremos a la parte del microprograma correspondiente al cálculo de la dirección de los operandos.

A partir de este punto debe empezar la generación de la interconexión de esta instrucción y la búsqueda de un bloque que pueda albergarla. Para ello se analizan todos los registros de página para ver si alguno de ellos contiene la página donde se halla la instrucción en la memoria principal. Si es así, se obtiene la información que configura la interconexión y se almacena en el bloque seleccionado, en caso contrario deberemos recurrir al algoritmo de reemplazamiento.

El algoritmo de reemplazamiento seleccionarà el bloque que deberà ser asignado a esta nueva pagina y la interconexión se almacenara en el, respetando toda la información que no corresponda a la palabra donde se inserte la interconexión. El registro de pagina debera ser actualizado con el valor correspondiente a la nueva pagina a la que hace referencia y también el algoritmo, a su vez, habra de ser actualizado para su uso posterior.

Una vez finalizada la ejecución normal de la instrucción, se iniciará la búsqueda de la siguiente instrucción en la memoria principal.

Supongamos ahora que la instrucción cuya fase de búsqueda està iniciandose, ha sido ejecutada con anterioridad y su interconexión se halla todavia almacenada en alguno de los bloques de la M.I..

Al iniciar la lectura de la memoria principal y de la memoria de interconexión simultáneamente conseguimos que en este caso, se obtenga el conocimiento de la existencia de la interconexión mucho tiempo antes finalizar la lectura de la memoria principal. En este momento, la lectura de la instrucción en la memoria principal es obviada y un campo del contenido de la interconexión nos proporciona la dirección de entrada al microprograma que ejecuta su versión migrada.

En los casos en que la instrucción máquina estè

constituida por más de una palabra y precise de más de un acceso a la memoria principal para completar su lectura, el tiempo ahorrado con este mecanismo se ve incrementado de forma muy notable, puesto que la interconexión tiene un formato de palabra única y en ella aparecen todos los parámetros de la instrucción.

En los casos que acabamos de mencionar, como ocurre con el microprocesador R6502 (utilizado en el ejemplo descrito en el capitulo IV), las interconexíones se almacenan en la M.I. dejando huecos entre ellas, puesto que la dirección que ocupa una interconexión en M.I. es la correspondiente a la primera palabra de la instrucción en memoria principal. La presencia de estos huecos no genera un desaprovechamiento de la M.I. sino que estos huecos serân ocupados con gran probabilidad en subsiguientes asignaciones del bloque de M.I., dejando intacto, en ese caso, los contenidos de las interconexiones pertenecientes a asignaciones anteriores. Este comportamiento hace que en este tipo de procesadores no se produzca ningûn desaprovechamiento de la M.I. sino que al contrario se aumente la probabilidad hallar una interconexiòn perteneciente a antiguas asignaciones de un bloque de M.I..

Una vez ejecutada la instrucción en su versión migrada, deberá ser actualizado (si así lo requiere) el algoritmo de reemplazamiento para posteriores accesos. El siguiente paso correspondería ya al inicio de la búsqueda de

la instrucción siguiente.

A continuación se describen cada una de las unidades que componen el coprocesador en cuanto a lo que se refiere a su estructura y funcionamiento particular.

# II.1.2 MEMORIA DE INTERCONEXION (M. I.)

La función básica de la Memoria de Interconexión es la de almacenar las interconexiones entre las instrucciones del programa principal y los microprogramas que las interpretan, es decir, las instrucciones del lenguaje intermedio "J+1/2". Las interconexiones están formadas por una única palabra independientemente de que el formato de las instrucciones originales sea de formato fijo o variable, de una sola palabra o de varias. Las interconexiones son generadas por el coprocesador en tiempo de ejecución del programa, y en ellas se incluyen, en una sola palabra, los parámetros a los que haga referencia la instrucción de la que son imagen.

Durante la primera ejecución de cada instrucción del programa, el coprocesador va creando, la imagen (interconexión) de la misma en la memoria de interconexión, de modo que existe una correspondencia entre las instrucciones màquina de la memoria principal y las instrucciones "J+1/2" de la memoria de interconexión. Todas aquellas instrucciones que pertenezcan a una estructura repetitiva, como puedan ser

los lazos o bucles, obtendrán su correspondiente imagen en la memoria de interconexión durante su primera ejecución, de manera que en las sucesivas iteraciones del bucle al que pertenecen, serán ejecutadas en su versión "J+1/2", incrementándose así la velocidad de ejecución del programa.

Dado que las interconexiones constituyen la alternativa a las instrucciones del programa a la hora de ser ejecutadas, el conocimiento de la existencia de una interconexión correspondiente a la instrucción en curso debe obtenerse antes de la finalización de la fase de búsqueda de dicha instrucción, es por ello que se hace necesaria la existencia de una memoria independiente de la principal (M. I.) para albergar dichas imágenes, y ser manipuladas con independencia de las instrucciones.

El tiempo de acceso de la memoria de interconexión viene delimitado por el incremento de velocidad que se quiera obtener en el sistema. Si dicho tiempo es igual al de la memoria principal, el ahorro de tiempo obtenido con, la incorporación del coprocesador, es practicamente nulo. Especialmente en aquellos sistemas en que el formato de la instrucción sea de palabra única. En el caso de procesadores con un formato de instrucción de longitud variable, o de más de una palabra, el ahorro de tiempo conseguido sería el debido al hecho de que en el formato "J+1/2" todos los parametros de la instrucción se obtienen en un sólo acceso a M.I. y con ello nos ahorrarlamos un cierto número de accesos a la memoria principal.

Si el tiempo de acceso de la M.I. es inferior al de la memoria de control. no se obtiene ninguna ganancia con respecto al caso en que dicho tiempo sea igual al de la memoria de control. Supongamos que durante el inicio de la ejecución de la última microinstrucción del microporgrama que interpreta una instrucción determinada, se inicia lectura de la siguiente instrucción en la memoria principal (como ocurriría en aquellos sistemas donde se solapa la ejecución de una instrucción con la búsqueda de la siguiente); bajo este supuesto y teniendo en cuenta, como se ha descrito en el capitulo anterior, que la lectura de la M.I. debe producirse simultàneamente con la lectura en la memoria principal, nada se ganaria con el conocimiento o no de la existencia de la interconexión de la siguiente instrucción antes de finalizar esta última microinstrucción, puesto que hasta su fin no es posible tomar ninguna decisión al respecto.

El tiempo de acceso elegido para la memoria de interconexión tiene como cota inferior al de la memoria de control del coprocesador, que serà igual al de la memoria de control del procesador, puesto que más rápida no puede ser y más lenta no tendría sentido teniendo en cuenta además que los tamaños manejados para dicha M.I. serán siempre relativamente pequeños.

Dado que nuestro objetivo es el de poder capturar,

en cada momento que sea preciso, los bucles que aparezcan en el perfil de ejecución del programa, es necesario que la M.I. tenga capacidad de adaptación a ese perfil de ejecución. A la hora de analizar esta flexibilidad se nos plantean dos cuestiones: