# AUTOMATIC DATA DISTRIBUTION FOR MASSIVELY PARALLEL PROCESSORS

# AUTOMATIC DATA DISTRIBUTION FOR MASSIVELY PARALLEL PROCESSORS

#### Jordi GARCIA

Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

Barcelona

A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor en Informàtica

FEBRUARY, 1997

# **ABSTRACT**

Massively Parallel Processor systems provide the required computational power to solve most large scale High Performance Computing applications. Machines with physically distributed memory allow a cost-effective way to achieve this performance, however, these systems are very difficult to program and tune. In a distributed-memory organization each processor has direct access to its local memory, and indirect access to the remote memories of other processors. But the cost of accessing a local memory location can be more than one order of magnitude faster than accessing a remote memory location. In these systems, the choice of a good data distribution strategy can dramatically improve performance, although different parts of the data distribution problem have been proved to be NP-complete.

The selection of an optimal data placement depends on the program structure, the program's data sizes, the compiler capabilities, and some characteristics of the target machine. In addition, there is often a trade-off between minimizing interprocessor data movement and load balancing on processors. Automatic data distribution tools can assist the programmer in the selection of a good data layout strategy. These use to be source-to-source tools which annotate the original program with data distribution directives. Crucial aspects such as data movement, parallelism, and load balance have to be taken into consideration in a unified way to efficiently solve the data distribution problem.

In this thesis a framework for automatic data distribution is presented, in the context of a parallelizing environment for massive parallel processor (MPP) systems. The applications considered for parallelization are usually regular problems, in which data structures are dense arrays. The data mapping strategy generated is optimal for a given problem size and target MPP architecture, according to our current cost and compilation model.

A single data structure, named Communication-Parallelism Graph (CPG), that holds symbolic information related to data movement and parallelism inherent in the whole program, is the core of our approach. This data structure allows the estimation of the data movement and parallelism effects of any data distribution strategy supported by our model. Assuming that some program characteristics have been obtained by profiling and that some specific target machine features have been provided, the symbolic information included in the CPG can be replaced by constant values expressed in seconds representing data movement time overhead and saving time due to parallelization. The CPG is then used to model a minimal path problem which is solved by a general purpose linear 0-1 integer programming solver. Linear programming techniques guarantees that the solution provided is optimal, and it is highly efficient to solve this kind of problems.

The data mapping capabilities provided by the tool includes alignment of the arrays, one or two-dimensional distribution with BLOCK or CYCLIC fashion, a set of remapping actions to be performed between phases if profitable, plus the parallelization strategy associated. The effects of control flow statements between phases are taken into account in order to improve the accuracy of the model. The novelty of the approach resides in handling all stages of the data distribution problem, that traditionally have been treated in several independent phases, in a single step, and providing an optimal solution according to our model.

# **ACKNOWLEDGEMENTS**

I am really in debt to Eduard Ayguadé, my thesis advisor, for his guidance, support, advice, and specially for being a friend during my stage as a graduate student. All my gratitude is for him. I would also like to thank Mateo Valero, who caught me to start researching on this never ending field. He is the guilty that I have written this stuff. I wish to thank Jesús Labarta, the leader of the compilers group, for his time and advice.

I feel very proud to belong to the DDTeam. I am indebted to Mercè Gironès for her support in my head-on collision against the ParaScope programming environment. She has been a great work-mate and currently she is a very good friend. Jordi Torres has left a trace in the inter-procedural analysis of DDT, but his personal encouragement has been much more fruitful for me. However, my best gratitude is for Mari Luz Grande, not only for her lots of megaflops in this work, but mainly for her trust in me and her great friendship. Thanks a lot to all the team for this nice work environment.

During my experience optimizing compilers I have met a lot of outstanding people. However I am indebted to Uli Kremer for the fruitful discussions in this topic in several *tapas* bars. I am also grateful to Elena Fernández for her insights in linear programming and for all her time. Professor Ron Perrott has given me a friendly relationship and the chance to work with him in Belfast. A lot more of people has influenced me on this research. It is exciting to know such brilliant researchers from all over the world.

I have been fortunate to work in the Computer Architecture Department, in which I have met a lot of excellent people. José Manuel Martín has been my first room mate, much better as a good friend than as researcher. And Josep Ramón Herrero, my current room mate, has kept a lot of interesting discussions about computer science and about *salsa*. They both have constantly been very patient with me.

I would also like to thank several other colleagues from this department for their company during these five years. A lot of dinners with award holders, assistant professors, and related, have provided an optimal work environment. Thanks to the people that have read a draft of this thesis and still are my friends. I feel privileged to have met this excellent group of researchers and good friends. Also thanks to the splendid technical support provided by the staff from the LCAC and from the CEPBA.

Special thanks go to my friends from Vilanova, that have never understood what I am doing here, but during multiple week-ends have supplied me feedback for these weeks of hard work. Thanks a lot to Meji, Juanki, Josep, Javi, Gabi, Juan Ramón, Panchi, Toni, Carlos, Janine, and more recently, Ignasi. My gratitude is also for Emilio Gutiérrez, my best academic fried, and Oriol Valero, who lent me his home for a summer and shares many lunches with me.

Finally, I want to thank all my family, my brother and his childs, for their love and support, but in special my sister Neus, and my niece and stepdaughter Cristina, that is the nicer child in the world. My deepest gratitude, however, is reserved to my parents, Daniel and Carme, those who have made possible me to be here, and those who have given me all their unconditional love and support during all my life. They have made this thesis possible, and this is dedicated to them.

This work was been partially supported by the Ministry of Education of Spain under contracts TIC 880/92 and TIC 429/95, by CIRIT grant BE94/1-100, the CEPBA (European Center for Parallelism of Barcelona), and by CONVEX Computer Corporation that has supported the development of the DDT tool.

## **AGRAIMENTS**

Estic molt en deute amb l'Eduard Ayguadé, el meu director de tesi, per la seva orientació, suport, bons consells, però especialment per ser un amic durant la meva etapa com a estudiant de doctorat. Tot el meu agraïment és per a ell. També m'agradaria donar les gràcies a Mateo Valero, que em va enganxar per a fer recerca en aquest mon inacabable. Ell és el culpable de que jo hagi escrit això. Desitjaria agrair a Jesús Labarta, el cap del grup de compilació, l'haver-me dedicat part del seu temps i dels seus consells.

Em sento realment orgullós de pertànyer al DDTeam. Estic en deute amb la Mercè Gironès per el seu suport en el meu xoc frontal contra l'entorn de programació ParaScope. Ella ha sigut una gran companya de treball i és una molt bona amiga. En Jordi Torres ha deixat la seva empremta en l'anàlisi interprocedural del DDT, però els seus ànims personals han estat molt més fructífers per a mi. Malgrat això, el més sinzer agraïment és per la Mari Luz Grande, no només per tots els megaflops que ha posat en aquest treball, sinò que principalment per la seva confian ca en mi, i per la seva gran amistat. Moltes gràcies a tot l'equip per aquest agradable entorn de treball.

Durant la meva experiència optimitzant compiladors m'he trobat amb molta gent excepcional. Però em sento endeutat amb l'Uli Kremer per les bones xerrades en aquesta àrea de recerca en múltiples bars de tapes. També estic agrait a la Elena Fernández per la seva ajuda en la programació lineal i per tot el temps que m'ha dedicat. El Professor Ron Perrott m'ha donat una bona amistat i l'oportunitat de treballar amb ell a Belfast. Molta més gent m'ha influenciat en aquesta recerca. És excitant conèixer aquest grup d'investigadors tant brillants d'arreu el món.

He estat afortunat de treballar en el Departament d'Arquitectura de Computadors, en el qual he conegut molta gent excel·lent. En José Manuel Martín ha sigut el meu primer company de despatx, molt millor com a bon amic que com a investigador. Amb en Josep

Ramón Herrero, el meu actual company de despatx, he tingut moltes bones xerrades relacionades amb l'informàtica i amb la salsa. Tots dos han estat constantment molt pacients amb mi.

També m'agradaria agrair molts altres col·legues d'aquest departament per la seva companyia durant aquests cinc anys. Molts sopars amb becaris, professors, i afins, m'han donat un entorn de treball òptim. Gràcies a la gent que s'ha llegit un esborrany d'aquesta tesi i encara són amics meus. Em sento privilegiat d'haver conegut aquest excel·lent grup d'investigadors i bons amics. També vull agrair l'esplèndid suport tècnic proporcionat per l'equip del LCAC i del CEPBA.

Un agraïment especial és per als meus amics de Vilanova, que tot i que mai no han entés el que estic fent per aquí, durant molts caps de setmana m'han estat realimentant per a aquestes setmanes de treball dur. Moltes gràcies al Meji, Juanki, Josep, Javi, Gabi, Juan Ramón, Panchi, Toni, Carlos, Janine, i més recentment a l'Ignasi. El meu agraïment és també per l'Emilio Gutiérrez, el meu millor amic de la Facultat, i per l'Oriol Valero, que em va deixar la seva casa durant un estiu i que comparteix molts dinars amb mi.

Finalment, vull agrair a la meva família, al meu germá i als seus fills, per el seu amor i suport, però en especial a la meva germana Neus, i a la meva nebodeta i fillola Cristina, que és la nena més bonica de tot el mon. El més profund agraïment, però, està reservat als meus pares, Daniel i Carme, que han fet possible que jo estés aquí, i que m'han donat el seu amor i suport incondicional durant tota la meva vida. Ells han fet aquesta tesi possible, i se la dedico a ells.

Aquest treball ha estat subvencionat parcialment per el Ministeri d'Educació Español amb els contractes TIC 880/92 i TIC 429/95, per la beca CIRIT BE94/1-100, per el CEPBA (Centre Europeu de Paral.lelisme de Barcelona), i per CONVEX Computer Corporation que ha col.laborat en el desenvolupament de l'eina DDT.

# CONTENTS

| ABS  | STF           | RACT                                | V    |

|------|---------------|-------------------------------------|------|

| LIST | ГΟ            | F FIGURES                           | xvii |

| LIST | ГΟ            | F TABLES                            | xxii |

| 1    | IN.           | TRODUCTION                          | 1    |

|      | 1.1           | Background                          | 1    |

|      | 1.2           | Motivating Example                  | 6    |

|      | 1.3           | Overview of Our Tool                | 8    |

|      | 1.4           | High Performance Fortran            | 11   |

|      |               | 1.4.1 Data Mapping with HPF         | 12   |

|      |               | 1.4.2 Compilers for HPF             | 15   |

| 2    | $\mathbf{RE}$ | LATED WORK                          | 19   |

|      | 2.1           | Related Work                        | 19   |

|      | 2.2           | Previous Work in Our Group          | 29   |

|      | 2.3           | Contribution of this Thesis         | 36   |

| 3    | ON            | E-DIMENSIONAL DISTRIBUTION          | 39   |

|      | 3.1           | The Communication-Parallelism Graph | 39   |

|      |               | 3.1.1 Nodes in the CPG              | 40   |

|      |               | 3.1.2 Data Movement Edges           | 42   |

|      |               | 3.1.3 Parallelism Hyperedges        | 45   |

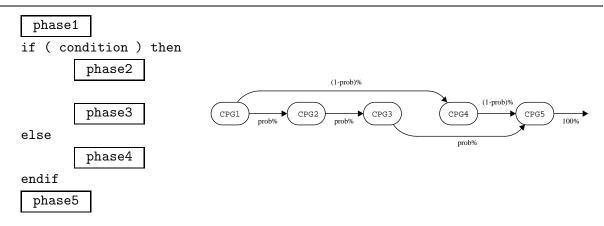

|   |     | 3.1.4 Control Flow Analysis                                 | 46 |

|---|-----|-------------------------------------------------------------|----|

|   |     | 3.1.5 CYCLIC Distributions                                  | 50 |

|   | 3.2 | Alignment and Distribution in the CPG                       | 52 |

|   | 3.3 | Cost Model in the CPG                                       | 56 |

|   |     | 3.3.1 Data Movement Cost                                    | 56 |

|   |     | 3.3.2 Computation Cost                                      | 58 |

|   | 3.4 | Modeling the Problem                                        | 60 |

|   |     | 3.4.1 Node Based Model                                      | 61 |

|   |     | 3.4.2 Edge Based Model                                      | 64 |

|   | 3.5 | An Example: The ADI Integration Kernel                      | 67 |

|   | 3.6 | Summary                                                     | 72 |

| 4 |     | O-DIMENSIONAL DISTRIBUTION WITH CONSTANT POLOGY             | 73 |

|   | 4.1 | Extending the Communication-Parallelism Graph               | 73 |

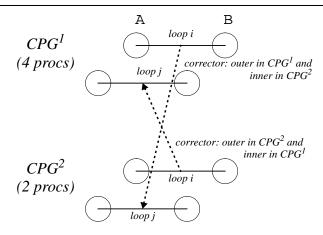

|   |     | 4.1.1 Duplication of the CPG                                | 74 |

|   |     | 4.1.2 Corrector Edges in the CPG                            | 76 |

|   | 4.2 | Two-dimensional Cost Model                                  | 77 |

|   |     | 4.2.1 Data Movement Cost                                    | 77 |

|   |     | 4.2.2 Computation Cost                                      | 81 |

|   | 4.3 | Modeling the Problem                                        | 84 |

|   |     | 4.3.1 New Constraints                                       | 84 |

|   | 4.4 | An Example: Two-dimensional Distribution for the ADI Kernel | 86 |

|   | 4.5 | Summary                                                     | 89 |

| 5 |     | O-DIMENSIONAL DISTRIBUTION WITH VARIABLE POLOGY             | 91 |

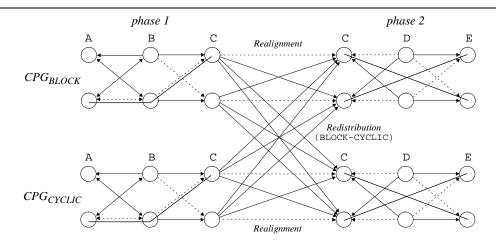

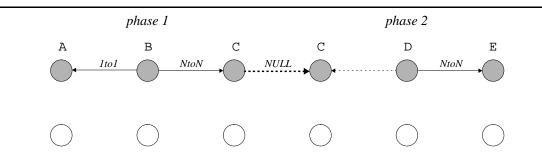

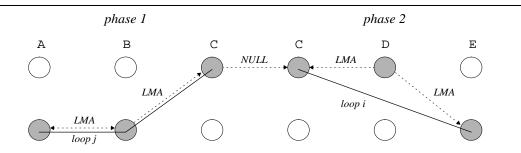

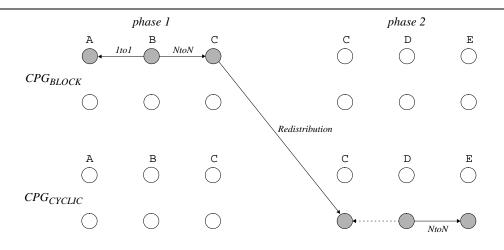

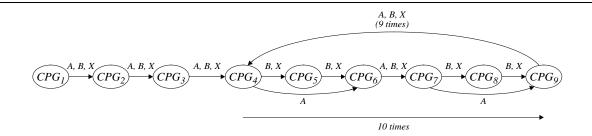

|   | 5.1 | Multiple Communication-Parallelism Graphs                   | 91 |

|   |     | 5.1.1 Redistribution Information                            | 93 |

|   | 5.2 | Cost Model for Redistributions                              | 95 |

|   | 5.3 | Modeling the Problem                                        | 96 |

Contents

|    |     | 5.3.1 New Set of Constraints                                        | 97  |

|----|-----|---------------------------------------------------------------------|-----|

|    | 5.4 | An Example: General Two-dimensional Distribution for the ADI Kernel | 100 |

|    | 5.5 | Summary                                                             | 103 |

| 6  | EX  | PERIMENTAL RESULTS                                                  | 105 |

|    | 6.1 | Performance Prediction Tool                                         | 105 |

|    |     | 6.1.1 ADI                                                           | 106 |

|    |     | 6.1.2 ERLEBACHER                                                    | 108 |

|    |     | 6.1.3 SHALLOW                                                       | 109 |

|    | 6.2 | Complexity of the Approach                                          | 111 |

|    | 6.3 | Summary                                                             | 114 |

| 7  | CO  | NCLUSIONS AND FUTURE WORK                                           | 115 |

| RE | FEF | RENCES                                                              | 121 |

| A  |     | I: THE ALTERNATE DIRECTION IMPLICIT<br>FEGRATION KERNEL             | 129 |

| В  |     | ANSFORMED ALTERNATE DIRECTION IMPLICIT FEGRATION KERNEL             | 133 |

# LIST OF FIGURES

| Chapte | er 1                                                                 |    |

|--------|----------------------------------------------------------------------|----|

| 1.1    | Shared memory multiprocessor architecture.                           | 2  |

| 1.2    | Distributed memory multicomputer architecture.                       | 3  |

| 1.3    | Speed-up for the ADI code with different bandwidths.                 | 8  |

| 1.4    | Main components in our optimization environment.                     | 10 |

| 1.5    | HPF template and alignment directive examples.                       | 13 |

| 1.6    | HPF processors and distribute directive examples.                    | 14 |

|        |                                                                      |    |

| Chapte | er 2                                                                 |    |

| 2.1    | Example of a Component Affinity Graph.                               | 21 |

| 2.2    | Main components of DDT.                                              | 31 |

| 2.3    | Source code for ADI with HPF data mapping and remapping directives   |    |

|        | generated by DDT.                                                    | 33 |

| 2.4    | Transformed code for phases 4 and 7 of ADI generated by PDDT.        | 36 |

|        |                                                                      |    |

| Chapte | er 3                                                                 |    |

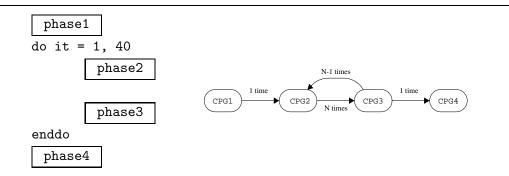

| 3.1    | Sample code used to illustrate the components of the Communication-  |    |

|        | Parallelism Graph.                                                   | 40 |

| 3.2    | Nodes in the CPG.                                                    | 42 |

| 3.3    | CPG with data movement information.                                  | 44 |

| 3.4    | CPG with parallelism information.                                    | 46 |

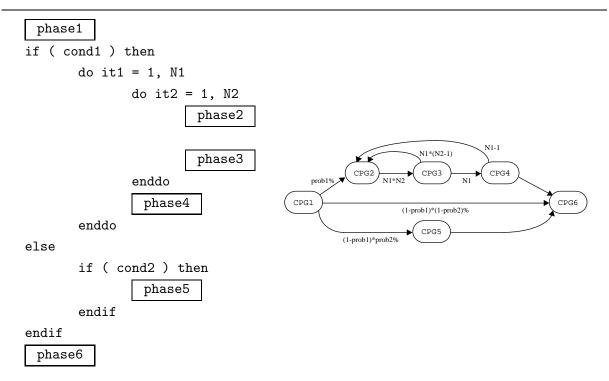

| 3.5    | Sample code with a conditional statement, and its phase control flow |    |

|        | analysis.                                                            | 47 |

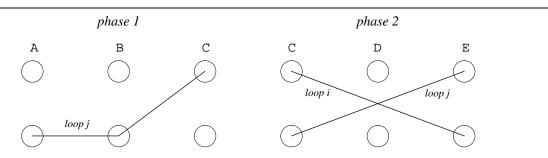

| 3.6    | Sample code with an iterative loop statement, and its phase control flow analysis. | 48 |

|--------|------------------------------------------------------------------------------------|----|

| 3.7    | Sample code with conditional statements and iterative loops and its                |    |

| 0.1    | control flow analysis.                                                             | 49 |

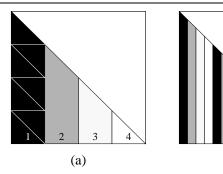

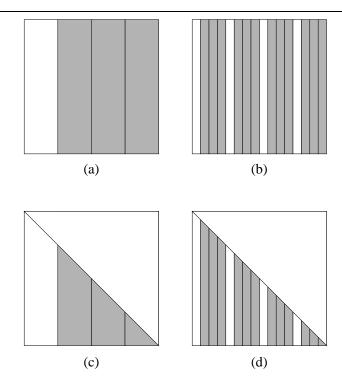

| 3.8    | Effects of (a) BLOCK and (b) CYCLIC distributions in triangular loops.             | 50 |

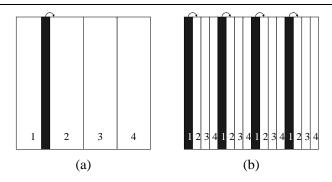

| 3.9    | Effects of (a) BLOCK and (b) CYCLIC distributions in neighbor                      |    |

|        | communications.                                                                    | 51 |

| 3.10   | CPG with BLOCK and CYCLIC information.                                             | 52 |

| 3.11   | Legal mapping in the CPG for the sample code.                                      | 53 |

| 3.12   | Optimal mapping in the CPG for the sample code.                                    | 54 |

| 3.13   | Legal mapping for the sample code with the CPG supporting both BLOCK               |    |

|        | and CYCLIC distributions.                                                          | 55 |

| 3.14   | Amount of computation saved for different loop structures and                      |    |

|        | distribution fashion.                                                              | 59 |

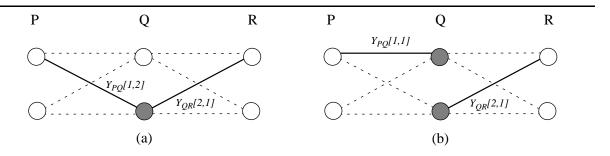

| 3.15   | Constraint $C1$ . (a) right case and (b) wrong case.                               | 65 |

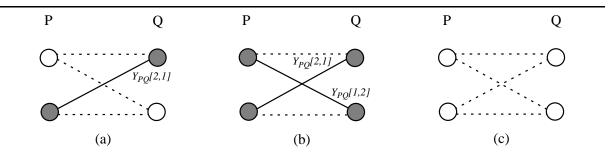

| 3.16   | Constraints $C2$ and $C3$ . (a) right case. (b) and (c) wrong cases.               | 66 |

| 3.17   | Phase control flow graph and data flow analysis for the ADI program.               | 68 |

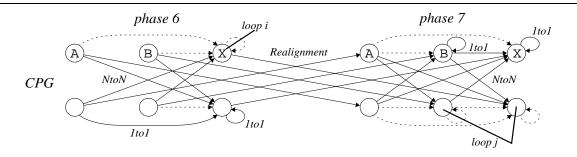

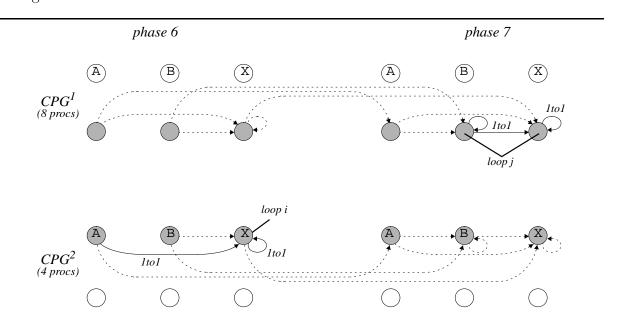

| 3.18   | CPG for phases 6 and 7.                                                            | 69 |

| 3.19   | Optimal data mapping for phases 6 and 7 of the ADI code.                           | 70 |

| Chapte | er 4                                                                               |    |

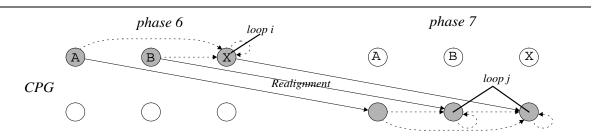

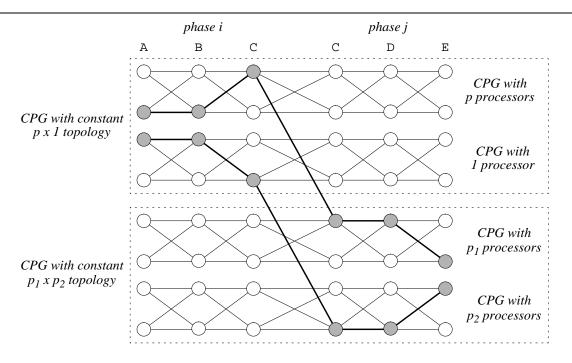

| 4.1    | Valid solution in a 2-dimensional CPG.                                             | 75 |

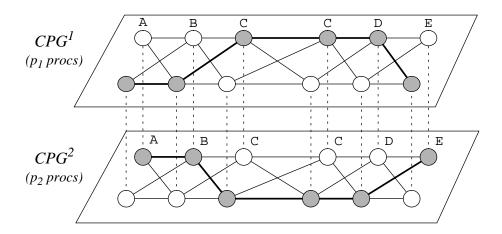

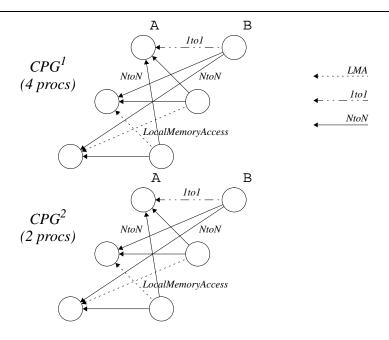

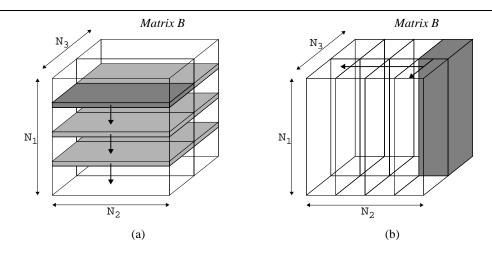

| 4.2    | Reference pattern for a 2-dimensional CPG.                                         | 79 |

| 4.3    | Examples of two-dimensional data movement.                                         | 80 |

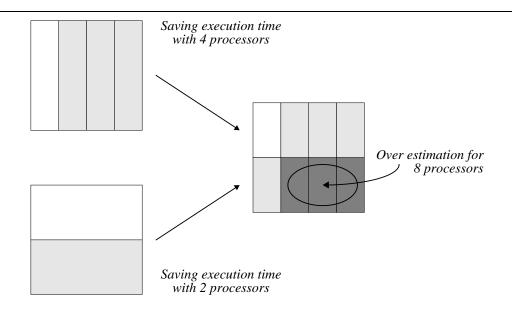

| 4.4    | Over estimation of the loop execution time with $4 \times 2$ processors.           | 82 |

| 4.5    | CPG fragment with two-dimensional parallelism information.                         | 83 |

| 4.6    | Constraint $C5$ . (a) right case and (b) wrong case.                               | 86 |

| 4.7    | Optimal two-dimensional data mapping for phases 6 and 7 of the ADI                 |    |

|        | code.                                                                              | 88 |

List of Figures xix

| Chapte | er 5                                                                       |     |

|--------|----------------------------------------------------------------------------|-----|

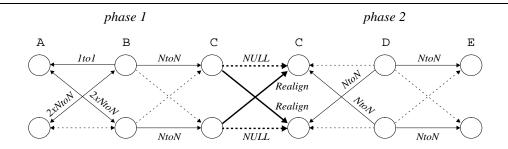

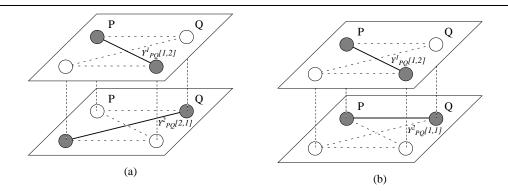

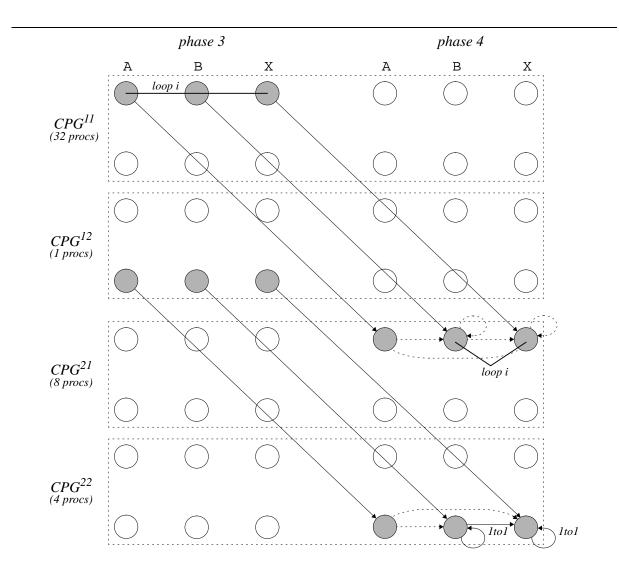

| 5.1    | Valid solution in a general two-dimensional CPG.                           | 93  |

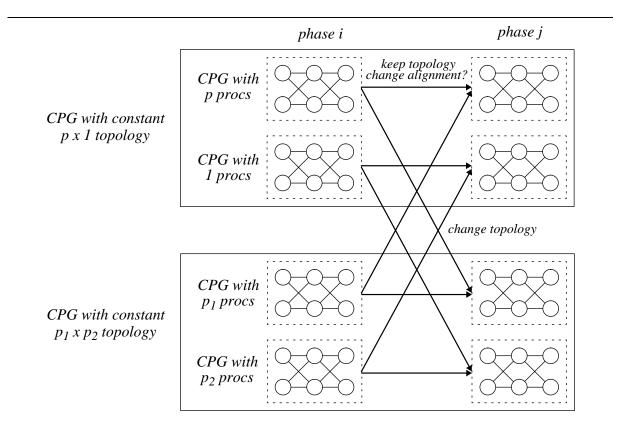

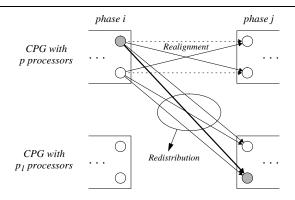

| 5.2    | Realignment and redistribution connections from the $p \times 1$ topology. | 94  |

| 5.3    | Set of edges included in realignment and redistribution connections.       | 95  |

| 5.4    | Optimal one and two-dimensional data mapping for phases 3 and 4 of the     |     |

|        | ADI code.                                                                  | 102 |

|        |                                                                            |     |

| Chapte | er 6                                                                       |     |

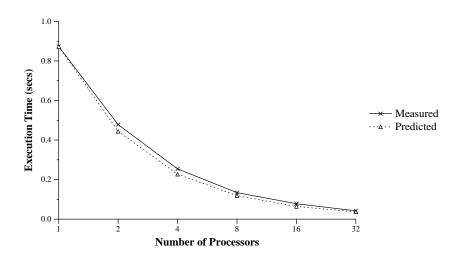

| 6.1    | Predicted and measured execution times for the ERLEBACHER program          |     |

|        | with 2, 4, 8, 16, and 32 processors.                                       | 109 |

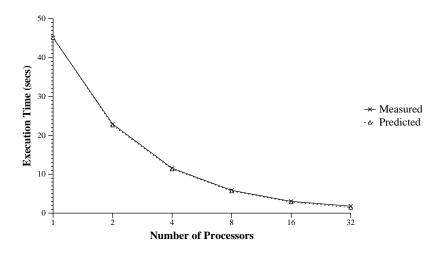

| 6.2    | Predicted and measured execution times for the SHALLOW program with        |     |

|        | 2, 4, 8, 16, and 32 processors.                                            | 110 |

|        |                                                                            |     |

| Chapte | er 7                                                                       |     |

# Appendix A

# Appendix B

# LIST OF TABLES

| Chapte | er 1                                                                                                                                                 |     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1    | Speed-up for the ADI code with different data sizes.                                                                                                 | 7   |

| 1.2    | List of currently available research compilers for HPF. F: full language definition; O: official subset; S: some features; +: additional features.   | 16  |

| 1.3    | List of currently available commercial compilers for HPF. F: full language definition; O: official subset; S: some features; +: additional features. | 16  |

|        | definition, O. official subset, S. some readures, 7. additional readures.                                                                            | 10  |

| Chapte | er 2                                                                                                                                                 |     |

| Chapt  | er 3                                                                                                                                                 |     |

| 3.1    | Matching between reference patterns and communication primitive.                                                                                     | 57  |

| 3.2    | Estimated block size $B$ for each data movement primitive for BLOCK distributions.                                                                   | 58  |

| 3.3    | CPG complexity for the ADI code in node and edge based models.                                                                                       | 70  |

| 3.4    | Complexity for the static CPG version with the ADI code.                                                                                             | 71  |

| Chapte | er 4                                                                                                                                                 |     |

| 4.1    | CPG complexity for two-dimensional distributions of the ADI code.                                                                                    | 88  |

| Chapte | er 5                                                                                                                                                 |     |

| 5.1    | CPG complexity for the ADI program in the general two-dimensional data mapping model.                                                                | 101 |

| 6.1 | Comparison of measured and predicted execution times for row, column,    |     |

|-----|--------------------------------------------------------------------------|-----|

|     | dynamic, and two-dimensional data mapping.                               | 107 |

| 6.2 | Comparison between the parallelization strategy proposed by PFA and      |     |

|     | the one selected by our tool.                                            | 108 |

| 6.3 | Characteristics of the selected programs.                                | 111 |

| 6.4 | Characteristics of the one-dimensional model.                            | 112 |

| 6.5 | Characteristics of the two-dimensional model with constant topology.     | 112 |

| 6.6 | Characteristics of the general two-dimensional model for a subset of the |     |

|     | selected programs.                                                       | 113 |

| 6.7 | Behavior of the set of selected programs when limiting the number of     |     |

|     | iterations of the solver                                                 | 114 |

# Chapter 7

# Appendix A

# Appendix B

## INTRODUCTION

Automatic data distribution in the context of a parallelizing environment for massive parallel processors systems is a key topic of current research. In this Chapter we intend to provide the background of our research, covering architectural issues, the data parallel programming model, and assistant tools for parallelization. This introduction is followed by a motivating example that illustrates the importance of data distribution in a real program. Then, an overview of our environment is presented, which includes a description of the main modules of our tool. At the end of this Chapter we provide a Section introducing the main HPF data mapping features that will be used along the following Chapters, and a survey of current HPF compiler implementations.

#### 1.1 BACKGROUND

High performance computing systems provide practical solutions to complex problems, with accuracies not possible some years ago. Their applicability includes fields such as weather modeling, environmental modeling and management, manufacturing design, biomedicine, molecular biology, computational chemistry or computational physics [HPC97]. For instance, weather models allow meteorologists to track severe storms and hurricanes with sufficient accuracy to implement more precise evacuation plans so as to save lives and property. Researchers use numerical simulations to estimate the effect of major storms and floods on the distribution of toxic materials in lakes and streams. Ground water contamination is a serious environmental and economic problem, with detoxification costs for existing sites estimated in the hundreds of billions of dollars. A

simulation analysis of the flow about a Delta II rocket, demonstrated an anomaly that had sent a launch vehicle into the wrong orbit. The modeling of biological membranes allows researchers to design drugs that need to pass through membranes effectively. The combination of hardware technology, improvements in parallel languages and compilers, and development of high performance mathematical and scientific libraries, allows very large scale applications in science and engineering to be successfully executed.

To meet the high computational requirements of such applications, high performance computers are needed. Currently high performance computers can be constructed from available hardware components and produce machines that are highly reliable and efficient. *Massively Parallel Processor* systems (MPP) built from off-the-shelf powerful microprocessors are one of the current trends in affordable high performance computing systems. Tipically all processors in these systems work together to obtain higher speed in the program execution. The peak performance provided by these systems is the addition of the individual performance of each processor. However, programs for these machines are much more difficult to design, implement, and debug, than sequential programs. The programmer has to organize the concurrent execution of the program on the parallel machine. There are two main architectural trends towards the design of MPP: *Shared memory multiprocessors* and *Distributed memory multicomputers*.

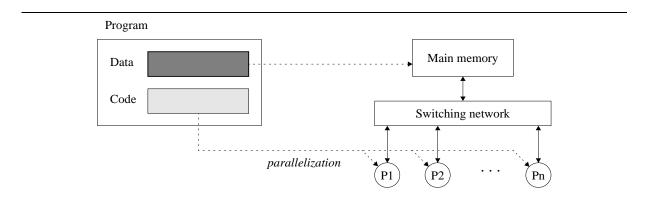

Shared Memory Multiprocessor (SMM) systems connect several processors that share a single physical memory through a switching network or a shared bus. The memory access

Figure 1.1 Shared memory multiprocessor architecture.

time is uniform for each processor. Each processor computes a part of the same program over a common data set stored on the main memory, as shown in Figure 1.1. With a small number of processors these systems compute efficiently, but in larger numbers the access to the main memory causes bottlenecks. The number of processors connected in a SMM system is heavily limited to the bandwidth of the interconnection network.

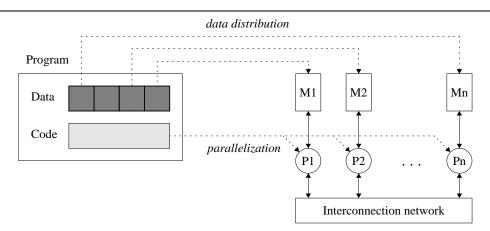

Distributed Memory Multicomputer (DMM) systems provide a cost-effective scalability to solve many large scale scientific problems. In DMM systems, each processor has direct access to its local memory, and indirect access to the remote memories of other processors through an interconnection network, as can be seen in Figure 1.2. The key drawback in DMM systems is that communicating data between processors can be more than one order of magnitude higher than the cost of accessing a local memory location. These systems are also called Non-Uniform Memory Access (NUMA), since the memory access time depends on the location of a datum in memory. Reducing the impact of the high memory latency may be achieved by restructuring the data in order to make more accesses local. A good data placement minimizes the remote memory accesses while keeping the parallelism inherent in the program. Unfortunately, the efficiency of the resulting program depends on many complex factors of the target machine, such as the processor topology, synchronization or inter-processor communication overhead.

Figure 1.2 Distributed memory multicomputer architecture.

The first approach to program DMM machines is to use an existing sequential programming language enhanced with message-passing constructs. The programmer has to design

the creation, synchronization and communication of parallel processes. This is achieved by distributing data and work over processors, and keeping track of the program execution at a very low level of detail. The references of data owned by other processors are satisfied by inserting appropriate message-passing statements in the code. Managing communication through low-level constructs is time consuming, error prone, and inhibits portability between different DMM machines. The resulting programming style can be compared to assembly programming on a sequential machine.

Data parallel programming languages provide code portability across both shared memory and distributed memory architectures. For this purpose, data parallel programs must be able to be compiled on different target machines, and to achieve reasonably high efficiency on different machines with the same number of processors. These languages allow the programmer to write code using global data references, but require the specification of data distribution over the individual memories of the physical processors. In the late eighties and early nineties, much research has been carried out to design and implement the first data parallel programming and compilation systems. Some early implementations such as Superb, Kali, and Booster are summarized in [CP95]. The main interest in data parallelism was generated by languages such as CM Fortran [TMC91], Fortran D [FHK+90], and Vienna Fortran [CMZ92]. These languages not only produced features to assist the user with data alignment and distribution, but also implemented many of the features. These languages also preceded the effort in producing High Performance Fortran, or HPF [HPF93]. In fact, HPF was heavily influenced by the language designers and implementers involved in these languages.

Data distribution is then used to guide the compiler to generate a Single Program Multiple Data (SPMD) program [Kar87] for execution on the target distributed memory multiprocessor. Each processor executes the same program, but operates on different data. This is implemented by loading the same program image into each processor, and then, each processor allocates and operates on its own local portion of distributed arrays. The compiler has to translate global data references into local and non-local references based on the data mapping specified by the programmer. All non-local references must be satisfied by inserting explicit message-passing statements, usually respecting the owner computes

rule [CK88], according to which it is the processor owning a data item that has to perform all computations for that datum.

Much work remains to be carried out in the development of these compilers, however the programmer still has to specify the placement of the data, and understand some features of the target machine. The choice of a good data distribution is important as it determines the amount of remote data accesses and the potential parallelism in the resulting program. The optimal data distribution depends on the program structure, the compiler capabilities, the characteristics of the target machine, and the program's data sizes. The layout of the data may be changed during program execution, this is known as remapping. Due to their influence on the amount of inter-processor communication, the choice of data mapping and remapping have a significant impact on the performance of the parallel program. In addition, there is often a trade-off between minimizing interprocessor data movement and load balancing on processors. Crucial aspects such as data movement, parallelism, and load balance have to be taken into consideration in a unified way to efficiently solve the data distribution problem.

Automatic data distribution tools can assist the programmer in this task. These may be source to source tools, which annotate the original high level program with data distribution directives and executable statements offered by data parallel languages. Automatic data distribution maps arrays onto the physically distributed memory of the processors according to the array access patterns and parallel execution of operations within computationally intensive blocks of code, named *phases*. If there is a single mapping for the whole program, then the solution is said to be *static*. However, in large problems where several computationally intensive phases occur, remapping actions between phases may improve the efficiency of the solution. In this case, the solution is said to be *dynamic*.

There are many other tools to support the development of parallel programs that can help the final success of High Performance Fortran. Run-time systems providing process management and execution control features, such as breakpointing facilities and instrumentation services. Parallel debugging tools providing views of different program levels. Performance analysis and monitoring tools for the identification and tuning of performance problems. Program restructuring tools that free the user from manually

transforming the parallel application during the optimization process. Visualization tools and interactive graphic user interfaces that provide more comprehensive information. All these tools should be carefully integrated to provide a friendly and unified environment, useful enough to assist the programmer to write his parallel application codes efficiently.

#### 1.2 MOTIVATING EXAMPLE

In this Section we intend to demonstrate the impacts of the program data sizes and the target architecture parameters on the data mapping selection. For this purpose we use the Alternate Direction Implicit (ADI) integration kernel, which defines a two-dimensional data space of size 256 in each dimension. It has a sequence of initialization loops, followed by an iterative loop that performs the computation. In each iteration of the loop, forward and backward sweeps along rows and columns are done in sequence. The ADI source code can be found in Appendix A.

The computational weight of the program is within the iterative loop, which contains 6 loop nests. In the first three loop nests, data movement takes place across the second dimension of the arrays, and parallelism can be exploited in their first dimension. Therefore a row distribution of the arrays may achieve a good performance. However, in the last three loop nests data movement takes place across the first dimension of the arrays, and the parallelizable loops traverse the second dimension of the arrays. In this case a column distribution of the arrays is advisable. This trade-off suggests several data mapping choices. The optimal choice depends on the program data size and certain target architecture parameters.

In order to illustrate the importance of choosing a good data mapping, we will consider the following five data distributions:

Sequentialization of all arrays within a single processor. This data distribution does not benefit from the parallel capabilities of the target architecture, but will be considered for comparison purposes. For shorter, this strategy will be named sequential.

• Static one-dimensional data distribution of the first dimension of each array. This data mapping will be referenced row for shorter.

- Static one-dimensional data distribution of the second dimension of each array. This data mapping will be named *column* for shorter.

- Dynamic one-dimensional data distribution. In this case the first dimension of the arrays will be distributed in the first three loop nests within the iterative loop, and the second dimension of the arrays will be distributed in the last three loop nests within the iterative loop. This data mapping will be referenced *dynamic* for shorter.

- Static two-dimensional data distribution. Both array dimensions will be distributed over a two-dimensional processors grid, whose topology is assumed to be squared, assigning the same number of processors at each array dimension. This data mapping will be named two\_dim for shorter.

The number of processors considered for this example is 16, and the data movement bandwidth assumed is  $10^6$  bytes/second. Profiling of the execution time for this code has been performed on a HP PA-RISC workstation. Table 1.1 shows the estimated speed-up of the ADI code with different data sizes. The original ADI code has been modified, declaring arrays of  $64 \times 64$ ,  $128 \times 128$ ,  $256 \times 256$ , and  $512 \times 512$  elements.

|                 | N = 64 | N = 128 | N = 256 | N = 512 |

|-----------------|--------|---------|---------|---------|

| sequential      | 1.00   | 1.00    | 1.00    | 1.00    |

| row             | 1.53   | 1.69    | 1.77    | 1.85    |

| column          | 1.58   | 1.72    | 1.83    | 1.88    |

| dynamic         | 2.39   | 2.48    | 2.58    | 2.74    |

| ${ m two\_dim}$ | 3.21   | 3.57    | 3.79    | 3.93    |

Table 1.1 Speed-up for the ADI code with different data sizes.

Note that with this code, all data mapping strategies improve speed-up when the data sizes are larger. Both the row and the column static distributions tend to reach a speed-up of 2. Speed-up in the dynamic data mapping is better than any static data mapping. However high remapping costs limits the speed-up growth. Finally, the two-dimensional data mapping strategy behaves better than the rest, although speed-up is also limited to 4.

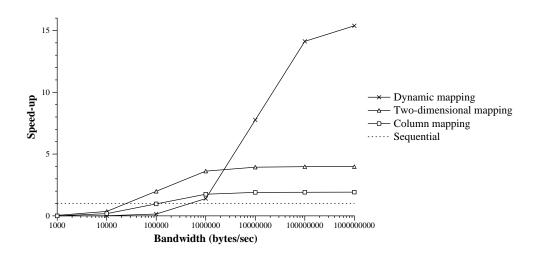

The impact of the bandwidth of the target machine is much higher. We have compared the speed-ups of the column, dynamic, and two-dimensional data mapping strategies, with different bandwidths, ranging from 10<sup>3</sup> bytes/second to 10<sup>9</sup> bytes/second, and assuming 16 processors. Results are shown in the graphic of Figure 1.3. Note that with a low bandwidth, all data mapping strategies tend to a speed-up of zero. With a bandwidth of 10<sup>6</sup> the best data mapping strategy is the two-dimensional, although its speed-up is limited to 4. But with higher bandwidth, the dynamic data mapping strategy grows up to the optimal speed-up of 16.

Figure 1.3 Speed-up for the ADI code with different bandwidths.

#### 1.3 OVERVIEW OF OUR TOOL

Our thesis proposes a new framework for an automatic data mapping tool in the context of a parallelizing environment for Massive Parallel Processor (MPP) systems. The applications considered for parallelization are usually regular patterned problems in which data structures are dense arrays. The tool analyzes Fortran 77 programs and determines a data mapping and parallelization strategy for this program. This data mapping is used to annotate the original sequential Fortran program using HPF data mapping and loop parallelization directives. The data mapping strategy generated is optimal for a given

problem size and target MPP architecture, according to our current cost and compilation model.

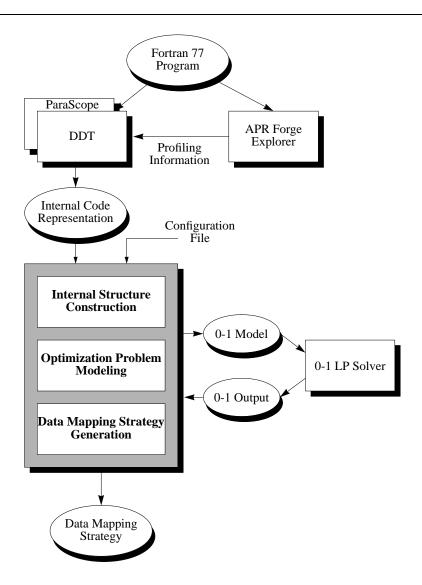

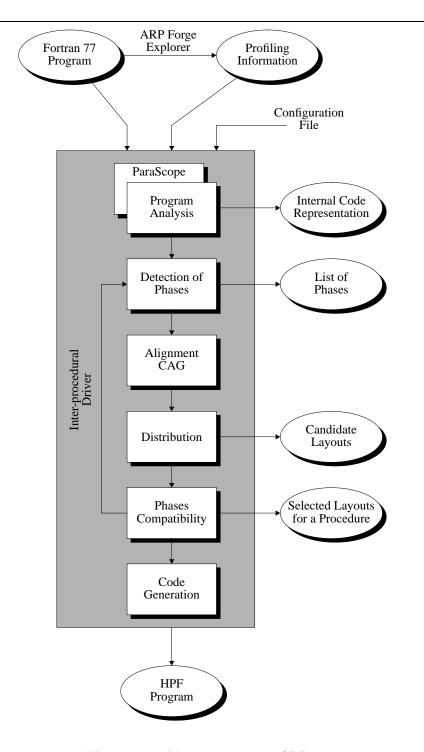

Profiling the sequential execution of the original Fortran 77 program is required in order to obtain some problem specific parameters, such as array sizes, loop bounds and execution time, and probabilities of conditional statements. The main steps performed during the optimization process are outlined below:

- Program Analysis. DDT [AGG+97] acts as a preprocessing platform that parses the sequential program, and analyzes the code. The analysis includes reference patterns recognition and optimization, data dependence analysis and phase control flow graph construction.

- Internal Data Structure Construction. The data structure defined in our framework is the core of our tool. It contains all the information required to estimate the effects of any possible data mapping and parallelization strategy according to our model.

- Optimization Problem Modeling. The main internal data structure is used to model a minimal path problem. Linear 0-1 integer programming techniques are used to find the optimal solution.

- Data Mapping Strategy Generation. The output of a general purpose linear programming solver is captured and interpreted to generate the data mapping and parallelization strategy. The solution derived is optimal according to our model.

Profiling information is obtained using the APR Forge Explorer's performance profiler [APR95]. There exists a configuration file which allows the user to specify machine related parameters, such as number of processors and its grid topology, and interconnection network bandwidth. The main components in our environment, shown in Figure 1.4, are described next.

The parsing of the code is performed using the parser module of DDT, another research tool for automatic data distribution implemented by our group. DDT is built on top of ParaScope [KMT90], an interactive parallel programming environment developed at Rice

Figure 1.4 Main components in our optimization environment.

University. All reference patterns are obtained from the source code after performing a set of optimizations, such as expression substitution, subscript substitution, and induction variable detection, which improve the quantity and quality of the reference patterns analyzed [AGG<sup>+</sup>94].

All this information is used by our tool to generate the internal data structure which contains all the information regarding data movement and parallelism inherent in the

original Fortran 77 program. This structure is used to model an optimization problem in which the optimal data mapping, according to our model, is obtained. The optimization problem is based on a minimal path problem with a set of additional constraints that ensures the correctness of the solution. The formulation of this problem as a linear 0-1 integer programming problem is written in a data file which contains the set of constraints and the objective function that has to be minimized.

LINGO [LIN94] is a general purpose linear programming solver used to find the optimal solution to the modeled problem. The solver generates an output data file with the value of each 0-1 integer variable. This file is interpreted by our tool to generate the final file containing information about the data mapping and the parallelization strategy suggested. This information can be finally used to annotate the original Fortran 77 source code with HPF data mapping and loop parallelization directives.

The data mapping strategy generated can be static or dynamic, one or two-dimensional, with either BLOCK or CYCLIC distribution fashion. The tool estimates the effects of control flow statements between phases, although when performing estimations of the cost of different strategies, we assume that the compiler does not perform any loop transformation or communication optimization. Inter-procedural analysis is not supported.

#### 1.4 HIGH PERFORMANCE FORTRAN

The goal of HPF is to define a Fortran language extension to achieve high performance in MPP systems. Data parallel constructions allow data parallel programming (single threaded, global name space, loosely synchronous computation), data mapping features allow top performance in NUMA computers and multi-machine portability, and intrinsic functions and extrinsic procedures allow access to low level programming to tune the code in a specific architecture. In addition to the HPF specification, an official subset is also defined to allow earlier implementations. The more recent projects in this area, such as HPF2 or F90D are concerned with adding support to irregular computations and other less structured work and data distribution strategies.

In this Section we provide an overview of the HPF data mapping features that will be used along the remainder of this Thesis. In addition, a survey of current HPF compilers implementation is presented.

#### 1.4.1 Data Mapping with HPF

The HPF directives are structured comments that suggest implementation strategies to the compiler. They may affect the efficiency of the program, although they do not change the program semantics. The program should generate the same results whether the directives are processed or not.

HPF includes data alignment and distribution directives that allow the user to specify how the compiler allocates data objects across the processors memory. The HPF compiler interprets these annotations and manages the data placement, minimizing data movement while retaining parallelism.

There is a three-level mapping of data objects to the physical memory. Data objects, typically array elements, are first *aligned* relative to one another. Alignment is performed across dimensions (inter-dimensional alignment) and within dimensions (intra-dimensional alignment). This group of aligned arrays is then *distributed* on an abstract grid of processors, according to a given pattern. Finally there is an optional mapping step from abstract to physical processors.

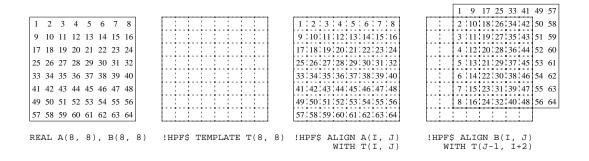

The ALIGN directive specifies relationships among array dimensions. Arrays are usually aligned onto a common array declared as the template. The TEMPLATE directive declares the name, size and dimensionality of a template. Arrays aligned to the same template are automatically aligned with each other. Inter-dimensional alignment is concerned with permuting the array dimensions with respect to the template. Intra-dimensional alignment allows, for each aligned dimension, shifting, striding, and reversing the ordering. For instance, in the following code:

```

REAL A(8, 8), B(8, 8)

!HPF$ TEMPLATE T(8, 8)

!HPF$ ALIGN A(I, J) WITH T(I, J)

```

```

!HPF$ ALIGN B(I, J) WITH T(J-1, I+2)

```

the array A is exactly mapped onto the template, whereas the array B is transposed with respect to the template. In addition, the first dimension of B is shifted by +2 with respect to the template, and the second dimension of B is shifted by -1. This is shown in Figure 1.5.

Figure 1.5 HPF template and alignment directive examples.

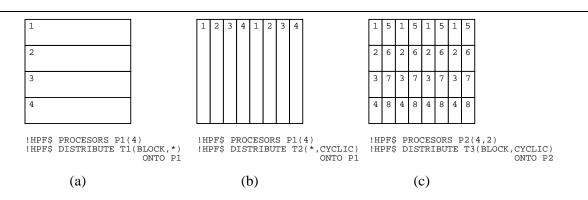

The DISTRIBUTE directive specifies a mapping of a group of arrays onto an abstract processors grid according to a given distribution fashion, either BLOCK or CYCLIC. A BLOCK distribution splits an array dimension by slicing it uniformly into blocks of contiguous elements. The CYCLIC distribution splits an array dimension in such a way that successive array elements are assigned to successive processors in a round-robin fashion. The CYCLIC(m) distribution, also known as block\_cyclic, assigns blocks of m consecutive elements to each processor in a round-robin fashion. By definition, CYCLIC(1) means the same than CYCLIC. The symbol \* is used to specify the dimensions that are not distributed. The group of arrays to distribute is usually specified by means of the template. In addition, the processor arrangement may be specified with the PROCESSORS directive, which declares its rank and the number of processors in each dimension. For instance, in the following code:

```

!HPF$ PROCESSORS P1(4)

!HPF$ TEMPLATE T1(8, 8), T2(8, 8)

!HPF$ ALIGN ...

!HPF$ DISTRIBUTE T1(BLOCK, *) ONTO P1

!HPF$ DISTRIBUTE T2(*, CYCLIC) ONTO P1

```

the processors arrangement P1 is one-dimensional with 4 processors. The first dimension of template T1 is distributed in a blocked fashion, and the second dimension is sequentialized. All arrays aligned to template T1 are distributed the same way. Similarly, the second dimension of template T2 is distributed in a cyclic fashion, as shown in Figure 1.6.a and 1.6.b. Alternatively, in the next code:

```

!HPF$ PROCESSORS P2(4, 2)

!HPF$ TEMPLATE T3(8, 8)

!HPF$ ALIGN ···

!HPF$ DISTRIBUTE T3(BLOCK, CYCLIC) ONTO P2

```

the processors arrangement P2 is two-dimensional, with 4 processors assigned to the first dimension, and 2 processors assigned to the second one. In addition, the first dimension of template T3 is distributed in a blocked fashion across 4 processors, and the second dimension is distributed cyclically across 2 processors, as shown in Figure 1.6.c. Note that the first array dimension is distributed by chunks, and the second array dimension is distributed to successive processors in a round-robin fashion.

**Figure 1.6** HPF processors and distribute directive examples.

An object can be remapped by realigning or redistributing it. In this case communication is required to move the data, in order to reflect the new mapping. Realignment is performed using the REALIGN directive, which is considered executable. Redistributing an object causes all objects aligned with it also to be redistributed to maintain the alignment relationships. This is performed using the REDISTRIBUTE directive, which is considered executable as well. Realignment and redistribution directives may appear only in the execution part of a program at any time, provided the objects have been declared dynamic, using the DYNAMIC directive.

Introduction 15

For instance, in the following code fragment:

```

REAL A(8, 8), B(8, 8)

!HPF$

PROCESSORS P(4)

!HPF$

TEMPLATE T(8, 8)

!HPF$

DYNAMIC A, B, T

!HPF$

ALIGN A(i, j) WITH T(i, j)

ALIGN B(i, j) WITH T(i, j)

!HPF$

!HPF$

DISTRIBUTE T(BLOCK, *) ONTO P

· · · code · · ·

REDISTRIBUTE T(*, CYCLIC)

!HPF$

· · · code · · ·

REALIGN A(i, j) WITH T(j, i)

!HPF$

```

both arrays A and B have been declared dynamic, as well as the template T. The redistribution directive causes all arrays aligned to the template to be dynamically redistributed, and the realignment directive causes array A to be realigned, transposing it with respect to the template. Remapping can require a lot of communication effort at run time, therefore the programmer must take care when using these directives.

There are many other HPF features not included in this Section, either related to data mapping or data parallelism. However they are not relevant to our work on automatic data mapping. A full HPF language description can be found in [HPF93].

# 1.4.2 Compilers for HPF

The HPF standards became publicly available by Spring of 1993. In the following years substantial progress has been made in finding solutions to many problems of implementing the language and data features defined in HPF. In addition to the HPF specification, an official subset has also been provided to allow earlier implementations. A wide range of systems are currently being implemented by various research groups and commercial companies.

Commercial HPF compilers have appeared for a broad range of architectures, from workstation clusters to massive parallel processor systems. However, many research groups

| Compiler Name     | Research Institution                       | Support |

|-------------------|--------------------------------------------|---------|

| ADAPTOR           | GMD - SCAI                                 | F+      |

| Annai Environment | CSCS - NEC                                 | O+      |

| The D System      | Rice University                            | S+      |

| HPFC              | Ecole de Mines de Paris                    | S+      |

| PANDORE           | IRISA                                      | S       |

| PARADIGM          | University of Illinois at Urbana-Champaign | S       |

| shpf              | University of Southampton                  | O+      |

| vfcs              | University of Vienna                       | S+      |

**Table 1.2** List of currently available research compilers for HPF. F: full language definition; O: official subset; S: some features; +: additional features.

have targeted their efforts toward a more effective compilation of HPF programs, including in some cases features not included in the official definition of the language. Table 1.2 shows a list of some of the available compiler prototypes for HPF developed at research institutions or universities. HPF compilers presented in Table 1.3 are commercial. Both tables show whether the compiler handles the full definition of the language (F), the official subset defined for it (O), or just some features (S). They also show if new features (+)

| Compiler Name  | Company Name                        | Support |

|----------------|-------------------------------------|---------|

| EXPERT HPF     | Associated Computer Experts         | О       |

| Fortran 90 HPF | Digital Equipment Corporation       | F+      |

| HPF Mapper     | N.A. Software                       | О       |

| Paragon HPF    | Intel Corporation                   | F-      |

| pghpf          | Portland Group Inc.                 | F-      |

| TM/HPF         | Thinking Machines Corporation       | O+      |

| VAST-HPF       | Pacific Sierra Research Corporation | F-      |

| xHPF           | Applied Parallel Research           | S       |

| XL HPF         | IBM Corporation                     | S       |

**Table 1.3** List of currently available commercial compilers for HPF. F: full language definition; O: official subset; S: some features; +: additional features.

Introduction 17

have been included in the standard definition. A more detailed study of these compilers can be found in [PAGT97] <sup>1</sup>.

In summary, only one implementation is available for the full language, but it also includes extra features, namely, DEC Fortran 90 HPF. Some other implementations have omitted some features of the official HPF standard, like GMD-SCAI's Adaptor, Intel Paragon HPF, The Portland Group pghpf, or VAST-HPF. The same is true for the official subset with the Annai Tool Environment, Southampton's shpf, ACE Expert HPF, and Thinking Machines TM/HPF. The other implementations still have to implement some features for the official set or subset.

<sup>&</sup>lt;sup>1</sup>This information is also available and updated at http://www.ac.upc.es/HPFSurvey/

# RELATED WORK

In this Chapter we present the work related to automatic data distribution that we think that is the most representative on this topic. Some of this work has influenced on our research. In addition, an overview of previous research developed by our group is also given. From this experience, we started from the scratch with a novel approach towards finding an optimal data distribution and parallelization strategy. The main aspects of our work are described and compared to the related work, and the most important contributions of this Thesis are finally enumerated.

#### 2.1 RELATED WORK

There is a large number of researchers that have addressed the problem of automatic data distribution in the context of regular applications. The main differences between the proposed methods is the kind of structure selected to represent the problem, the performance estimation model adopted, and the techniques applied to find a solution. Most of them split the static problem into two main independent steps: alignment and distribution. The alignment step tries to relate the dimensions of different arrays, according to the access patterns between them. A good alignment will minimize the overall overhead of inter-processor data movement. The distribution step decides which of the aligned dimensions are distributed, and the number of processors assigned to each of them. A good distribution maximizes the potential parallelism of the application, and offers the possibility of further reducing data movement by serializing. The main features of some systems are described below.

### Li and Chen

Li and Chen [LC90, LC91], have been involved in the Crystal language and compiler project at Yale University. Crystal is a high level functional language, compiled for execution on a massively parallel distributed-memory machine. They address the generic problem of automatic data layout, although they concentrate on the problem of finding a static inter-dimensional alignment within a single phase. In addition, they have developed a methodology for communication synthesis in generating parallel programs for DMM systems.

On compilation, a Crystal program is first decomposed into code blocks, named phases, each of which is treated as a unit in the layout problem. The alignment and distribution problems are independently solved for each phase, and the results of different phases are finally merged.

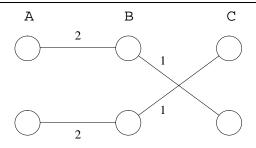

They solve the alignment problem in two separate steps: the inter-dimensional alignment step, in which permutation and embedding are considered; and the intra-dimensional alignment step, in which shift and reflection is considered. The inter-alignment problem is modeled as a graph problem. The graph is called the Component Affinity Graph (CAG), and it is constructed from an analysis of the reference patterns in the source program. The nodes in the graph represent array dimensions, and are grouped by columns, where each column represents the components of the same array. An edge represents a preference for alignment between the connected dimensions. They assign weights to the edges of the CAG to reflect the strength of the preference, however their metric is reduced to weights of  $\varepsilon$  or 1. All edges between a pair of nodes are replaced by a single edge whose weight is the sum of the original weights.

For instance, consider the following code fragment:

do i = 2, N

do j = 1, N

$$A(i, j) = B(i-1, j) + 1$$

$B(i, j) = A(i, j) + 2$

$C(j, i) = B(i, j) + 3$

enddo

enddo

with a loop nest, in which three reference patterns are identified:

$$A(i,j) \leftarrow B(i-1,j)$$

$B(i,j) \leftarrow A(i,j)$

$C(j,i) \leftarrow B(i,j)$

The reference patterns determine affinity relations between array dimensions. The generated CAG is illustrated in Figure 2.1. This consists of three columns with two nodes each. According to the affinity relations in the reference patterns, six edges are included, but only four of them are different. The graph contains global information about alignment preferences.

Figure 2.1 Example of a Component Affinity Graph.

The alignment problem is formulated as an optimization problem where edges in the CAG may carry different weights. They proved the alignment problem to be NP-complete in [LC90], so they present a heuristic algorithm to solve it. The algorithm is an enhanced greedy algorithm where a single array is chosen at each step for aligning with the target domain, and there is no back-tracking.

For the distribution step they propose to match the aligned reference patterns to a predefined set of data movement routines [LC91]. Each routine has an architecture-dependent cost parameterized in terms of number of processors involved in the data motion and the amount of data moved. The cost function for all the patterns is minimized by generating all possible distributions and selecting the most effective. They did not solve the dynamic problem, although their CAG has been used by many other researchers as the main data structure to solve the alignment problem.

# Wholey

Wholey [Who92] at Carnegie-Mellon University developed a compiler for the ALEXI high level language. Communication and parallelism are expressed by using a small set of primitives, that manipulate elements of arrays in parallel. The ALEXI system breaks the data mapping problem into two parts, alignment and layout, as they assume the alignment problem to be architecture independent.

For the alignment step, he adopted the Preference Graph defined by [KLS90] in the framework of SIMD architectures, which allows the addition of parallelism related information while solving the alignment problem. However, its solution is based on heuristic techniques.

The execution time is estimated using a cost estimate function which is constructed from the source program in a straightforward way. Each primitive has an associated cost function which computes the running time given the descriptions of the mapping of its arguments. When the problem size is not known at compile time, default values are used instead of profiling information. The estimated time of a program is then computed as the addition of the estimated times of each individual array primitive.

In order to solve the layout step, he uses a hill climbing search method as an approximation. Initially all data is assigned to a single processor, and this cost is computed. Then the number of available processors is doubled and the new cost is computed. This process is iteratively performed until all available processors have been distributed, or until the total cost is not further reduced. Multi-dimensional distributions are supported, but only for communication purposes. Nested parallelism is not addressed, nor dynamic data layouts.

# Gupta and Banerjee

Gupta and Banerjee [GB93] at the University of Illinois at Urbana-Champaign, implemented the PARADIGM compiler on top of the Parafrase-2 system, which is used to provide internal information about the program. They developed a methodology for auto-

matic data partitioning given a sequential or shared-memory parallel program, generating SPMD programs with explicit communication.

They split the automatic data distribution process in four passes. The align pass maps each array dimension to a processor-mesh dimension. The block-cyclic pass determines for each array dimension, whether it should be distributed in a blocked or cyclic manner. The block-size pass determines the block size for each dimension distributed in a cyclic manner. And the num-procs pass determines the number of processors assigned in each of the processor-mesh dimensions, assuming that the maximal number of distributed dimensions is two.

They estimate computational costs from the estimation of the computation of a single instance of each statement, and the count of the number of times that statement is executed. They also consider synchronization delays. For the communication costs they perform an accurate analysis of data sizes, number of processors involved in the communication, where the communication would be placed, and number of iterations that the communication takes place.

During the alignment step, they use the CAG defined in [LC90], although their metric to weight edges is more accurate. They assume a default distribution, and for each edge, they try to estimate the extra communication cost incurred if those dimensions are not aligned. Unfortunately, it is not possible to find a single alignment configuration under which the communication costs may be compared to determine this *extra* communication cost. However, this proposal is more accurate than the previous one, although they use the same heuristic algorithm to solve the alignment problem.

For each aligned array dimension, they decide if the distribution fashion has to be block or cyclic. This is performed by estimating the penalty incurred in execution time if the distribution is block, and if the distribution is cyclic, and the compiler chooses the one with the higher value. If the distribution selected is cyclic, they obtain a block size for the corresponding dimension.

Finally, they decide the candidate dimensions to distribute, assuming again a default number of processors to be assigned in each dimension and estimating the total data movement plus computation cost. When more than one dimension is candidate to be distributed, they choose two of them and decide the number of processors to be assigned at each dimension by generating all possible combinations.

The final data partitioning generated is static, i.e. dynamic remapping is not supported. A solution for the dynamic approach has actually been proposed by Palermo and Banerjee in [PB95] using [GB93] to find the static mapping for each phase in the program. They propose a divide-and-conquer approach in which the program is recursively decomposed into a hierarchy of candidate phases. Then, estimating the costs of remapping between these candidate phases, a shortest path algorithm determines the final sequence of phases with the lowest cost.

## Kremer and Kennedy

Kremer and Kennedy [KK95, Kre95] at Rice University, designed a framework to be used inside a data layout assistant tool for Fortran 77 that generates Fortran D or HPF. A prototype based on their framework has been implemented as part of the D system [ACG<sup>+</sup>94].

Their framework for automatic data layout consists of four steps. First they partition the program into program segments named phases. Then a set of candidate layouts are built for each phase. In the third step, each candidate data layout and their possible data remapping are evaluated in terms of estimated execution time. And finally, based on these estimations, the optimal data layout strategy is selected.

As usual, they split the static data layout problem for a single phase in two stages: alignment and distribution. The first stage is based on the CAG, but they formulate the inter-alignment problem as a linear 0-1 integer programming problem, which provides an exact solution for their model. Instead of selecting the best alignment, a promising set of alignment candidates is selected, and the decision of selecting the final alignment is postponed until all distribution candidates are known.

Distribution analysis is performed after the alignment analysis. An exhaustive distribution search is performed, considering BLOCK and CYCLIC distribution. Once the distribution candidates have been determined, the cross product of alignment candidates and distribution candidates defines the candidate data layout search spaces for each phase. The user can limit the number of candidate data layout selected for each phase.

Each candidate data layout and each possible remapping action between candidate data layouts are evaluated in terms of expected execution time. Their approach to estimate performance is based on training sets [BFKK91]. A training set is a collection of kernel routines that measure the cost of several communication and computation patterns. The statements in the source code are matched to a previously defined training set, and the measured cost is used as the execution estimation.

As a result of the performance estimation step, estimated execution times for all candidate data layouts and possible remapping between layouts are available. The data layout search space is modeled with the Data Layout Graph, which has one node for each candidate data layout, and edges represent possible remapping between phases. Again, the problem is modeled as a minimal path linear 0-1 integer programming problem suitable to be solved by a state-of-the-art general purpose integer programming solver [BKK94b]. Kremer proved in [Kre93] that this exploration is NP-complete.

#### Anderson and Lam

Anderson and Lam [AL93] have implemented their algorithms in the SUIF compiler at Stanford University. They propose a methodology to for automatically decompose both data and computation onto a virtual processor array. Their main interest is to find the *shape* of the decompositions, and do not worry about load balancing, block size of cyclic distributions, or determining the number of physical processors to lay out in each dimension. In addition, as the target compiler used is SUIF, they can generate data decompositions that can not be specified by means of HPF directives.

Initially, the compiler apply unimodular transformations in order to leave loop nests in a canonical form (fully permutable), and positions parallel loops at the outermost

level. They have developed a mathematical framework for expressing and calculating data and computation decompositions, and propose an iterative algorithm that looks for communication-free static decompositions for a single loop nest.

If communication-free decompositions can not be found, they propose to remove the constraints that force the sequential execution of a loop. This simplification requires to introduce nearest-neighbor communication, and will result in pipelined execution. The resulting decomposition is solved as a communication-free decomposition. Their communication cost estimation model is reduced to inexpensive and expensive data movements.

Finally, they describe the Communication Graph to model dynamic decompositions, and a heuristic algorithm to find the final dynamic decompositions. The algorithm tries to join loop nodes in order to eliminate possible remapping costs. Two nodes are merged if the performance of both nodes with the same decomposition is higher than the performance of each individual decomposition plus the remapping cost. They proved in [AL93] that the dynamic data distribution problem in the presence of control flow between loop nests is NP-hard.

### Schreiber et al.

Schreiber et al. [CGS93, CGSS94] at the Research Institute for Advanced Computer Science and at Xerox Park, in the framework of the Excalibur project, propose a methodology for compiling array-oriented languages, such as Fortran 90.

They have developed a data flow representation called the Alignment Distribution Graph (ADG), consisting of ports, nodes and edges. Ports represent array objects, nodes represent program operations and edges connect definitions of array objects to their usage in these operations. In [CGS93] they solved the alignment problem using a dynamic programming approach, trying to minimize data movement costs. In [CGSS94] they use a divide-and-conquer approach to the dynamic mapping problem. They initially assign a static mapping valid for all the nodes and then recursively divide them into regions which are assigned different mappings. Two regions are merged when the cost of the dynamic

mapping is worse than the static mapping considering computation, data movement, and remapping costs.

They also propose techniques in [SSGC95, SSP+95] to reduce the graph complexity transforming the ADG into the Constraint Graph, and further simplifications by graph contraction techniques.

## Other Proposals

There are several other researchers that in the last few years have developed some other new data distribution approaches. A summary of some of them is given as follows.

The FCS system [CP93] considers the problem in the framework of a data distribution tool for Fortran90 source codes. A phase is basically a DO-loop containing array-syntax assignment statements or WHERE masks in its body. Instead of looking for the optimal solution, they use a tree-exhaustive algorithm with some heuristics to prune the search space. A Conflict Table storing the conflicts between the mappings of the arrays from one phase to the other is the basis of the remapping algorithm. From this information, a tree showing all the different alternatives of remapping is built. The aim is to determine the path in the tree with the lowest cost. The full remapping tree can easily grow to intractable proportions.

In [CFZ93], a prototype to be included into their VFCS system is described, with the CAG as a basis for the alignment step. In the distribution step they propose as heuristic a bottom-up pass over the call graph to select a set of considered distributions for the arrays, and a top-down pass to select the final array distributions.

[DHR93] describe a parallelizing process, in which a methodology for data distribution is proposed. An exhaustive exploration tree of all possibilities is generated to solve the dynamic problem, and limits redistribution at the outermost loop level in order to reduce the complexity. Their cost model is based only in the data movement, and propose branch-and-bound to further reduce complexity.

[Fea93] considers the static distribution of data and computation among a two-dimensional processors geometry, in a DMM. The source code is restricted to assignments and DO loops. He constructs the Dataflow Graph that allows the representation of communication patterns in the source program. He concerns in minimizing communication, and seeks parallelism by scheduling statements. The algorithm used is a greedy algorithm based on the gauss-Jordan elimination.

[XN94] solve the alignment and distribution problems. During the alignment step they define the Alignment Graph, and propose a greedy algorithm as a heuristic to compute the graph. In the distribution step trapezoid distributions are considered as a universal distribution pattern to maximize processor load balance and minimize neighboring data movement.

[NDG95] as part of their EPPP system, describe a technique to decompose computation and data for distributed memory machines. The program is divided into collections of loop nests (Clustering Algorithm), and for each nest, decomposition and data locality constraints are formulated as a system of homogeneous linear equations (Locality Algorithm). Both algorithms are polynomial in complexity. They exploit several types of parallelism.

[Lee95] extends the CAG for two-dimensional alignments but uses the same heuristic to compute the graph. He proposes a dynamic programming algorithm that heuristically determines the dynamic data distribution for the full program. Some optimizations to hide data movement latency by data pipelining are described.

[KP96] define a weighted graph to solve the dynamic data distribution problem, taking into account several loop transformations, such as loop interchange and distribution. The graph includes communication and parallelism information. They formulate a minimal path algorithm, and perform an exhaustive search with pruning strategies to find the solution.

Some other authors [RS91, BKK<sup>+</sup>94a] present methods to obtain communication-free data distributions using matrix notation, and solving the problem with linear algebra.

When communication-free partitioning of the arrays is not possible, they propose different problem formulations to minimize communication costs.

#### 2.2 PREVIOUS WORK IN OUR GROUP

Some of the work referenced previously has influenced our research, however we obtained a lot of experience with the implementation of our first automatic data distribution tool (DDT and later PDDT), that derives inter-procedural dynamic multi-dimensional data distributions. Following there is a description the previous work developed by our group.

#### DDT