# Convertidor estático del filtro activo de potencia

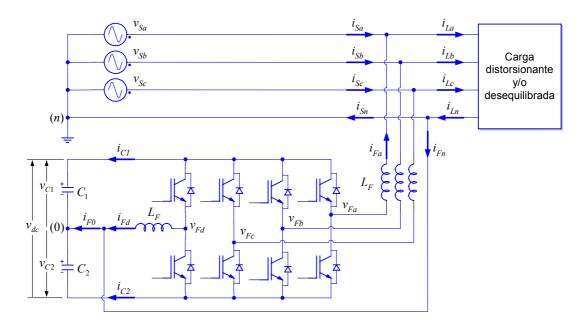

n un filtro activo de potencia en derivación (SAPF), el convertidor estático es el elemento responsable de la inyección de las corrientes de compensación en la red. Este convertidor siempre irá acompañado de un sistema de control que garantice que la corriente realmente inyectada en la red sigue fielmente las señales aportadas como referencia.

Desde un punto de vista ideal, el conjunto formado por el convertidor más el controlador de corriente, debería comportarse como una fuente lineal capaz de inyectar en todo momento las corrientes de compensación que se le aporten como referencia. Lógicamente, debido a las características intrínsecas del convertidor y del controlador, este comportamiento será inalcanzable, y sólo existirá un determinado rango de operación en el cual la respuesta del sistema podrá ser considerada como lineal.

Un factor primordial que hará que la respuesta del sistema convertidor-control difiera del comportamiento ideal estriba en que el convertidor estático es un sistema no lineal de estructura variable. En este sistema no lineal, el control de la corriente inyectada se realizará mediante el cambio del estado del convertidor, es decir, mediante la conmutación de los diferentes transistores que constituyen el mismo. Por tanto, la corriente de salida presentará un valor medio, que deberá coincidir con el valor aportado como referencia, más un rizado, que resulta de la sucesión de los diferentes estados de conmutación que atraviesa el convertidor. Según esto, para minimizar la amplitud de este rizado de corriente, sería deseable que la frecuencia de conmutación del convertidor fuese lo más elevada posible. En aplicaciones de gran potencia, los elevados tiempos de conmutación de los transistores, y las pérdidas asociadas a estas conmutaciones, dan lugar a que la frecuencia de conmutación de los convertidores convencionales sea relativamente baja, en torno a pocos miles de hertzios. En este tipo de aplicaciones, para minimizar el estrés en los transistores, se recurre al uso de convertidores con topologías avanzadas. En este grupo se

encuentran los convertidores multinivel [4.1], los convertidores en cascada [4.2], o las estructuras resonantes [4.3].

Independientemente del tipo de convertidor utilizado, en la salida del mismo siempre existirá una etapa de filtrado pasivo cuyo objetivo será "cortocircuitar" las corrientes de alta frecuencia, evitando así que estas corrientes sean inyectadas en la red [4.4]. En este punto, la frecuencia de conmutación del convertidor vuelve a ser importante, ya que es conveniente que la frecuencia de sintonización de este filtro pasivo esté muy por encima de la máxima frecuencia que puedan presentar las corrientes de referencia que se aportan al convertidor.

Como quedará justificado en este Capítulo, y suponiendo igualdad de condiciones para los diferentes casos, la capacidad de inyección de corriente del convertidor depende de la topología utilizada en el mismo [4.5]. Generalmente, aquellas topologías con menor capacidad de inyección de corriente presentan en contrapartida un sistema más simple de control para el inversor, mientras que las topologías con mayor capacidad de inyección de corriente necesitan un sistema de control más sofisticado. Esta dicotomía entre prestaciones y simplicidad en el control, hace que no todos los fabricantes de filtros activos utilicen la misma topología en el diseño del convertidor estático [4.6][4.7].

El convertidor estático de un SAPF enlaza con la red de potencia mediante elementos reactivos. Así mismo, el convertidor acumula energía en su lado de continua mediante otro elemento reactivo. La correcta elección de los valores y parámetros de trabajo de dichos elementos reactivos condicionará en gran medida la respuesta estática y dinámica del sistema resultante, determinando finalmente el ancho de banda de la hipotética fuente de corriente.

El sistema utilizado para de control de la corriente inyectada por el convertidor es una cuestión determinista de las prestaciones finales del SAPF. En un SAPF, la velocidad de respuesta en el seguimiento de las corrientes de referencia es crucial, lo cual hace intuir que los controladores no lineales que trabajan directamente sobre la corriente inyectada presentarán mejores prestaciones en este sentido [4.30], sin embargo, esta velocidad en la respuesta del controlador puede dar lugar a que el convertidor estático se encuentre conmutando bajo condiciones no óptimas, lo cual se traducirá en un incremento excesivo de las pérdidas de conmutación. Así mismo, es posible que aparezcan secuencias de conmutación que no puedan ser generadas debido a las limitaciones dinámicas de los transistores. La priorización de la respuesta dinámica del SAPF frente a una correcta secuencia de conmutación en el convertidor, también puede llevar asociada una pérdida en el control del rizado de corriente inyectada por el convertidor, tanto de su amplitud, como de su frecuencia. Teniendo en cuenta que dicho rizado no puede ser inyectado en la red, el diseño del filtro pasivo del lado de alterna del convertidor resultará más complicado e ineficiente cuando las conmutaciones del convertidor no sean apropiadamente secuenciadas. Por tanto, sobre todo en aplicaciones de gran potencia, es necesario adoptar un sistema de control que asegure, no sólo una correcta inyección de corriente inyectada, si no que además, el convertidor estático se encuentre trabajando en unas condiciones idóneas [4.8].

### 4.1. Topología del convertidor estático

Este Apartado tiene por objeto exponer las topologías del convertidor estático habitualmente utilizadas en la implementación de SAPF's, resaltando sus principales ventajas e inconvenientes, y delimitando su campo de aplicación. Posteriormente, en el Apartado 4.2, se hará una revisión de los sistemas de control de corriente en estos convertidores.

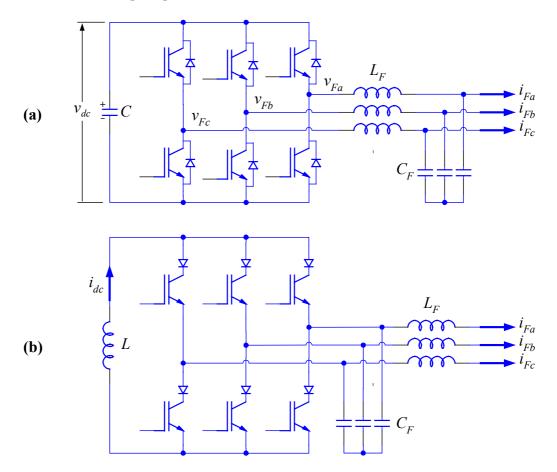

De manera general, el convertidor estático de un SAPF se puede implementar mediante un inversor en fuente de tensión (VSI – *Voltage Source Inverter*), o un inversor en fuente de corriente (CSI – *Current Source Inverter*). En la Figura 4.1 se muestra la estructura de ambos inversores para sistemas trifásicos de tres hilos. En esta figura, también se ha representado el filtro pasivo destinado a la atenuación de las componentes de alta frecuencia a la salida del inversor. El inversor en fuente de corriente resulta ser más robusto, aunque también es más caro de implementar [4.9][4.10], el inversor en fuente de tensión presenta menores pérdidas y es más económico [4.11]. En este trabajo se utilizará un convertidor en fuente de tensión, lo que concuerda con la tendencia existente en la mayoría de los equipos disponibles comercialmente [4.12].

**Figura 4.1.** Convertidor estático del SAPF para redes trifásicas de tres hilos.

- (a) Inversor en fuente de tensión (VSI).

- (b) Imversor en fuente de corriente (CSI)

El inversor mostrado en la Figura 4.1 recibe el nombre de "inversor de tres ramas en puente completo" (TLFB - Three-Leg Full-Bridge) y su aplicación en el filtrado activo de corriente en redes trifásicas de tres hilos fue presentada por Akagi en 1984 [4.13], convirtiéndose en un clásico dentro de este tipo de aplicaciones, y apareciendo multitud de nuevas aportaciones desde entonces [4.14][4.15][4.16]. Mediante el inversor TLFB resulta imposible invectar corrientes homopolares en la red, utilizándose para acondicionar las corrientes consumidas por cargas trifásicas sin neutro. En un inversor TLFB, para optimizar el control sobre la corriente invectada en la red, es importante que las tensiones de secuencia positiva y negativa sintetizadas a la salida del mismo puedan llegar a alcanzar el máximo valor posible. Existen multitud de trabajos que estudian diferentes técnicas de modulación del inversor TLFB con el objetivo de conseguir el máximo aprovechamiento de la tensión de su bus de continua, y a su vez, obtener unas secuencias de conmutación óptimas en el mismo [4.17]. En este sentido, la "modulación vectorial" se ha erigido como una técnica de modulación avanzada que consigue resultados óptimos en ambos aspectos. Sin embargo, la implementación convencional de esta técnica de modulación implica la utilización de un potente procesador de señal, y el consumo de un elevado tiempo de cálculo. En el Capítulo 5, se presentará un nuevo enfoque acerca de la modulación vectorial de inversores en puente completo, que simplifica enormemente el algoritmo de modulación, y permite su implementación en un procesador de bajo coste.

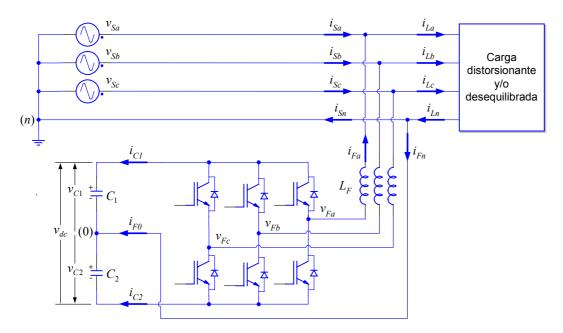

En sistemas trifásicos de cuatro hilos, de media y baja potencia, es habitual la existencia de cargas monofásicas conectadas entre fase y neutro. En estos casos, se hace necesaria la utilización de otras topologías en el convertidor estático del SAPF que permitan la inyección de corrientes de secuencia homopolar en la red. La solución más simple en este tipo de casos consiste en la topología mostrada en la Figura 4.2. Este inversor recibe el nombre de "inversor de tres ramas con condensador repartido" (TLSC – *Three-Leg Split-Capacitor*).

**Figura 4.2.** Estructura de un SAPF con un inversor TLSC.

En el inversor TLSC, al estar conectado el neutro de la carga con el punto intermedio de su bus de continua, las tres ramas del mismo trabajan de manera independiente; es decir, la tensión de salida de cada rama depende únicamente del estado de conmutación de sus dos transistores. Esta simplicidad en el control de la tensión de salida es la principal ventaja que ofrece el inversor TLSC, lo cual ha animado a los fabricantes de equipos a utilizarlo en filtros activos para redes de cuatro hilos de media y baja potencia [4.6]. Así mismo, existen multitud de trabajos sobre SAPF que utilizan esta estructura de convertidor en redes de cuatro hilos [4.18][4.19][4.20]. Sin embargo, esta topología presenta ciertas limitaciones e inconvenientes.

La primera limitación consiste en que, cuando se están sintetizando tensiones de salida de secuencia únicamente positiva y negativa, sin secuencia homopolar, el inversor TLSC no aprovecha completamente la tensión del bus de continua. Al no poder existir un potencial de flotación entre el punto medio del bus de continua y el neutro de la carga, la máxima amplitud de la tensión de secuencia positiva y negativa que se puede aplicar a dicha carga será, para un mismo valor de tensión en el bus de continua, inferior a la alcanzable con el inversor TLFB.

Otra limitación de esta topología consiste en que, en un momento dado, la máxima amplitud de la tensión de secuencia homopolar generable en la salida, no es independiente de la amplitud de tensión de secuencia positiva y negativa que se esté suministrando en ese momento; ya que ambas componentes de tensión deben ser sintetizadas por las tres únicas ramas del inversor. Por ejemplo, en una situación en la que el inversor esté suministrando en su salida la máxima amplitud alcanzable de secuencia positiva, o negativa, la tensión de secuencia homopolar generable depende de la forma de la onda resultante como combinación de ambas componentes, existiendo situaciones donde la máxima amplitud de la componente homopolar, sin alcanzar en ningún momento la saturación del inversor, deba ser nula.

Las dos limitaciones expuestas podrían hacer pensar que este inversor no es adecuado para su utilización práctica en aplicaciones de filtrado activo. En realidad esto no es así, ya que este tipo de inversor resulta adecuado para el acondicionamiento de corriente en sistemas de media y baja potencia en los que, además de componentes de secuencia positiva y negativa, pueden existir componentes homopolares de orden moderado. De hecho, la sencillez en el control del inversor TLSC ha determinado que ciertos fabricantes suministren filtros activos basados en esta topología de inversor que alcanzan hasta los 120A de corriente de compensación por fase en redes de 400V [4.21].

Sin embargo, en el inversor TLSC existe un problema que puede llegar a complicar su control, y a hace que los condensadores del bus de continua deban ser sobredimensionados. Este problema estriba en el hecho de que la totalidad de la corriente de secuencia homopolar que es inyectada por las tres ramas del filtro debe retornar por el punto intermedio del bus de continua del mismo, nodo '0'. La inyección de corriente en este nodo da lugar a la aparición de desequilibrio en el reparto de la tensión total del bus entre cada uno de los condensadores que componen el mismo, lo cual provoca que las ramas del inversor dejen de funcionar de manera simétrica, esto es, el valor absoluto de tensión de salida de las ramas será diferente en

función de que esté cerrado el interruptor superior o el inferior de las mismas. Lógicamente, esta falta de simetría en la tensión de salida de las ramas complica el control del inversor, ya que el valor medio de la tensión de salida ofrecida por dichas ramas deja de tener una relación lineal con el ciclo de trabajo de éstas. Además, el problema del desequilibrio de tensión en los condensadores del bus puede llegar a ser muy grave cuando el valor absoluto de tensión en alguno de los condensadores llega a ser lo suficientemente bajo como para impedir la controlabilidad de la corriente inyectada por alguna rama del filtro. En ese caso, la corriente inyectada por las ramas pasa a tener trayectorias descontroladas que pueden alcanzar elevados valores de pico, lo cual es perjudicial para la red de potencia, y puede llegar a destruir los semiconductores del inversor. En el Apartado 4.3 se propone una solución que solventa este problema en el inversor TLSC.

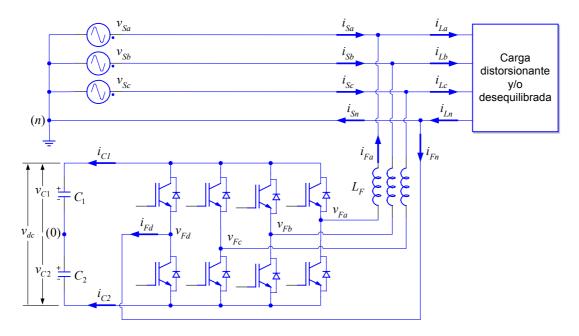

Cuando el nivel de corriente de secuencia homopolar que se debe compensar llega a ser considerable, el convertidor mostrado en la Figura 4.3 ofrece mejores prestaciones que el inversor TLSC. Este inversor es conocido como "inversor de cuatro ramas en puente completo" (FLFB – Four-Leg Full-Bridge). En la Figura 4.3, con el objetivo de clarificar las explicaciones venideras, se ha considerado que el bus de continua del inversor está constituido por dos condensadores, sin embargo, en una implementación real, dicho bus está compuesto por un único condensador. En esta topología, resulta evidente que, mediante la rama d, es posible regular el potencial de flotación del punto intermedio del bus de continua (nodo '0') respecto al neutro de la red (nodo 'n'). Por tanto, suponiendo que las ramas a, b y c se destinan a sintetizar únicamente las componentes de secuencia positiva y negativa de la tensión de salida, la tensión generada mediante la rama d (tensión medida respecto del nodo '0') determina la componente homopolar de tensión que, cambiada de signo, aparece finalmente a la salida de las otras tres ramas; habiéndose considerado que esta tensión de salida se mide respecto al neutro de la red.

**Figura 4.3.** Estructura de un SAPF con un inversor FLFB.

Lógicamente, si además de la rama *d*, las ramas *a*, *b* y *c* también se dedicasen a generar componentes de tensión de secuencia homopolar, la tensión de salida resultante con dicha secuencia podría llegar a ser bastante elevada, lo cual corrobora la afirmación inicial referente a la idoneidad del uso de esta topología de inversor en aplicaciones de filtrado activo de corriente donde existan grandes solicitaciones de componente homopolar.

Si en el inversor FLFB se considera que la rama d se encuentra desconectada, es decir, con sus dos interruptores abiertos, la topología resultante correspondería a la del inversor de tres ramas en puente completo, TLFB. Como se indicó anteriormente, mediante la utilización de la modulación vectorial en el inversor TLFB, era posible obtener el máximo aprovechamiento de los recursos de tensión del bus de continua en la generación de tensiones de secuencia positiva y negativa, y además obtener unas secuencias de conmutación óptimas. Como se explicará con mayor detalle en el Capítulo 6, el máximo aprovechamiento del bus de continua se logra mediante la regulación de la tensión de flotación ente el nudo '0' y el neutro de la red. Por tanto, cuando la rama d del inversor FLFB entra en funcionamiento, para conseguir las mismas prestaciones del inversor TLFB en la generación de tensiones de secuencia positiva y negativa, basta con hacer que la tensión generada por dicha rama sea igual, y de signo opuesto, a la tensión de flotación del bus de continua que existía en el convertidor TLFB. Este detalle se explicará con mayor profundidad en el Capítulo 5.

Como conclusión a la presentación del inversor FLFB, habría que decir que éste presenta excelentes prestaciones para aplicaciones de filtrado activo en redes trifásicas de cuatro hilos, ya que permite aprovechar al máximo la tensión del bus de continua para suministrar en su salida tensiones de secuencia positiva y negativa, y a su vez, también permite generar unos niveles elevados de tensión de secuencia homopolar. Sin embargo, las técnicas de modulación vectorial propuestas hasta el momento para el inversor FLFB resultan sumamente complejas, lo que hace necesario un hardware costoso con alta capacidad de procesado, no existiendo, además, demasiadas referencias bibliográficas acerca de esta modulación [4.22]. Estos inconvenientes han hecho que muchos fabricantes de equipos se muestren cautelosos a la hora de la utilización de este inversor en sistemas de filtrado activo en redes de cuatro hilos. En el Capítulo 5 de este trabajo, se propone un nuevo algoritmo para la síntesis de las tensiones de salida a partir de un enfoque tridimensional, simplificándose mucho el proceso de modulación.

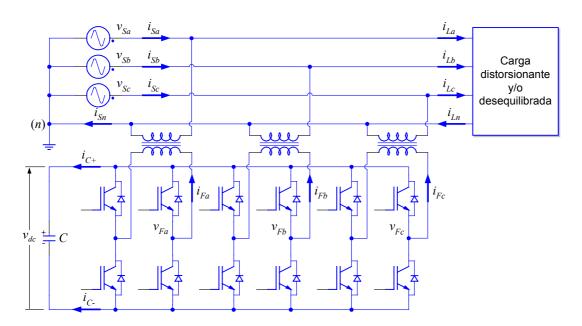

Por último, en sistemas de alta potencia, donde además el desequilibrio entre fases sea considerable, es común utilizar la topología mostrada en la Figura 4.4. Esta configuración recibe el nombre de inversor de "tres puentes completos y cuatro hilos" (TBFW – *Three-Bridge Four-Wire*) [4.23][4.24]. En principio, la funcionalidad de este inversor es relativamente similar a la del inversor FLFB mostrado en la Figura 4.3, aunque aporta valiosas ventajas en aplicaciones de alta potencia. En el inversor FLFB, la totalidad de la corriente de secuencia homopolar que era inyectada por el filtro circulaba por la cuarta rama (rama *d*). Si esta corriente alcanzase niveles elevados, los transistores utilizados en dicha rama deberían ser de gran potencia, lo cual podría llegar a suponer un inconveniente en situaciones extremas. En el inversor TBFW, mediante la utilización de transformadores de

**Figura 4.4.** Estructura de un SAPF con un inversor TBFW.

acoplamiento a red, la cuarta rama anteriormente mencionada es dividida en otras tres, dando lugar a tres inversores monofásicos independientes, uno para cada fase de la red, consiguiendo una mayor capacidad de inyección de corriente.

La tensión máxima de salida de cada inversor monofásico coincide con el valor de la tensión del bus de continua, por lo que dicha tensión de bus puede ser considerablemente menor que en las topologías anteriores. Además, utilizando una estrategia de modulación unipolar en los inversores, se consiguen tensiones de tres niveles a la salida de los mismos, lo cual permite reducir la frecuencia de conmutación de los transistores y disminuir el rizado de la corriente inyectada.

En esta topología, todas las ramas de transistores serán de igual potencia, y cada inversor monofásico tiene la misma capacidad de para aportar de corriente de secuencia positiva, negativa y homopolar. En el inversor TBFW mostrado en la Figura 4.4, los transformadores se diseñan de forma que integren la inductancia de dispersión necesaria para el adecuado acoplo entre la salida del inversor y la red.

El control de las secuencias de conmutación de este inversor es sencillo y clásico, lo que aumenta su fiabilidad en aplicaciones de gran potencia. Lógicamente, el aumento de prestaciones anteriormente mencionadas se ve acompañado también de un incremento en el coste del inversor, motivo por el cual no suele ser generalmente utilizado por los fabricantes de equipos de consumo, aunque la ventaja ofrecida por su modularidad debería ser una opción a considerar por dichos fabricantes de equipos.

Con el objetivo de argumentar las explicaciones ofrecidas acerca de las características y prestaciones de las distintas configuraciones del convertidor estático, seguidamente se muestran una serie de resultados de simulación que permiten tener una idea, algo más cuantitativa, sobre la capacidad de inyección de

corriente de dichos inversores. En estas simulaciones, no se ha considerado el caso del inversor de tres puentes completos y cuatro hilos, TBFW, por sobrentender que sus prestaciones son claramente superiores a las de los demás.

En todas las simulaciones realizadas se ha considerado que el valor de pico de la tensión de fase de la red es de 311V, que el valor de la tensión total del bus de continua es de 700V, y que el valor de las inductancias de acoplo entre el inversor y la red es de 2,2mH. Además, con el objetivo de mostrar la amplitud del rizado en la corriente inyectada en la red por los convertidores, el filtro pasivo de salida no ha sido instalado. En un primer paso, se compararán los inversores cuando éstos no inyectan corriente de secuencia homopolar en la red, suponiéndose una situación en la que el inversor se encuentra inyectando únicamente un séptimo armónico de corriente en la red.

En los siguientes comentarios, cuando se haga alusión a la *tensión de las ramas* del inversor se estará hablando de la tensión de salida de dichas ramas respecto al punto intermedio del bus de continua, nodo '0'. A partir de ahora, este convenio será adoptado a lo largo de todas las explicaciones que se realicen en este Capítulo.

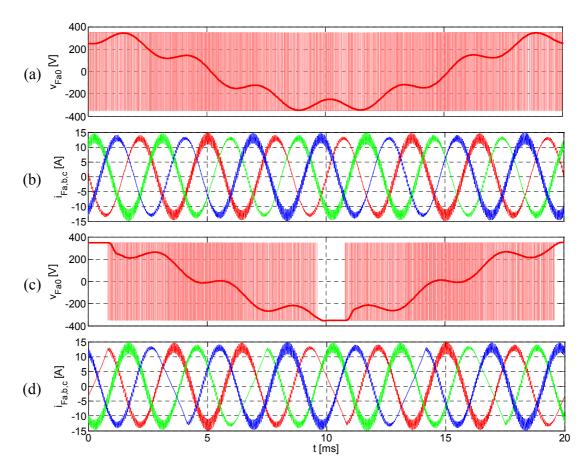

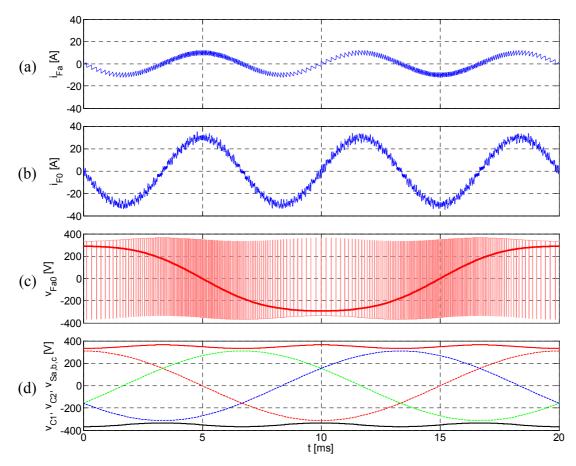

En la Figura 4.5 se muestran los resultados de simulación correspondientes al inversor de tres ramas y condensador repartido, TLSC, cuando éste se encuentra inyectando un séptimo armónico de corriente en la red.

**Figura 4.5.** Formas de onda del inversor TLSC invectado 7º armónico en la red.

La técnica de modulación utilizada en el inversor TLSC para la inyección de esta corriente es una modulación estándar por anchura de pulsos (SPWM – *Standard Pulse Width Modulation*), con una frecuencia de conmutación de 20kHz, y para la regulación de esta corriente se ha utilizado un sistema de control lineal.

La Figura 4.5a muestra la tensión de la rama *a* cuando la corriente inyectada en la red coincide con la de la Figura 4.5b, la cual responde a una señal de referencia sinusoidal, con un valor de pico de 13A. En la Figura 4.5a se ha representado la tensión modulada de la rama y, en trazo grueso, la tensión resultante del promediado local de la misma. Esta señal de trazo grueso evidencia cómo la tensión suministrada por la rama del inversor está constituida por una componente de frecuencia fundamental, la cual, para evitar la inyección de corriente de frecuencia fundamental en la red, será idéntica a la tensión de fase de ésta, más una componente de séptimo armónico. En la Figura 4.5a se aprecia cómo el inversor se encuentra al borde de la saturación (sobremodulación), pudiéndose afirmar que, para las condiciones de red, bus de continua e inductancia de acoplo consideradas, la corriente de la Figura 4.5b prácticamente coincide con la máxima corriente de séptimo armónico inyectable en la red mediante el inversor TLSC.

Si la referencia de corriente a inyectar estuviese desfasada 180° respecto al caso anterior, las formas de onda de la tensión de la rama del inversor, y de la corriente inyectada, coinciden con las mostradas en las Figuras 4.5c y 4.5d. En la Figura 4.5c se aprecia como el inversor atraviesa ahora zonas en las que entra en saturación, lo que origina la pérdida de control de la corriente inyectada.

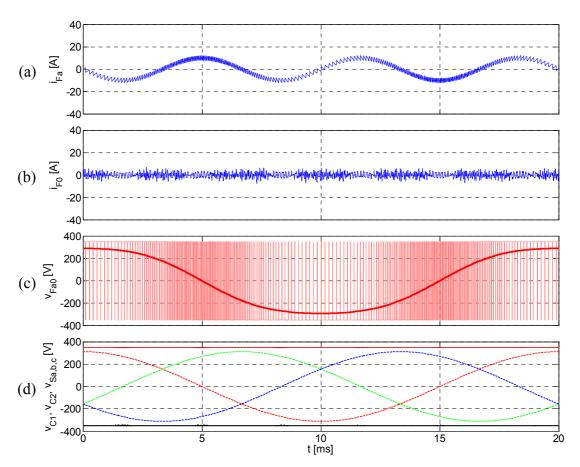

Ahora, manteniendo las mismas condiciones de red, de bus de continua, de frecuencia de conmutación y de inductancia de acoplo, se utilizará el inversor de cuatro ramas en puente completo, FLFB, para inyectar las mismas corrientes que en el caso anterior. Para inyectar estas corrientes, la técnica de modulación utilizada en el inversor FLFB es una modulación vectorial tridimensional (3D-SVM – *Three-Dimensional Space-Vector Modulation*), la cual se explicará con detalle en el Capítulo 5. Así mismo, para la regulación de la corriente inyectada se ha utilizado un control lineal.

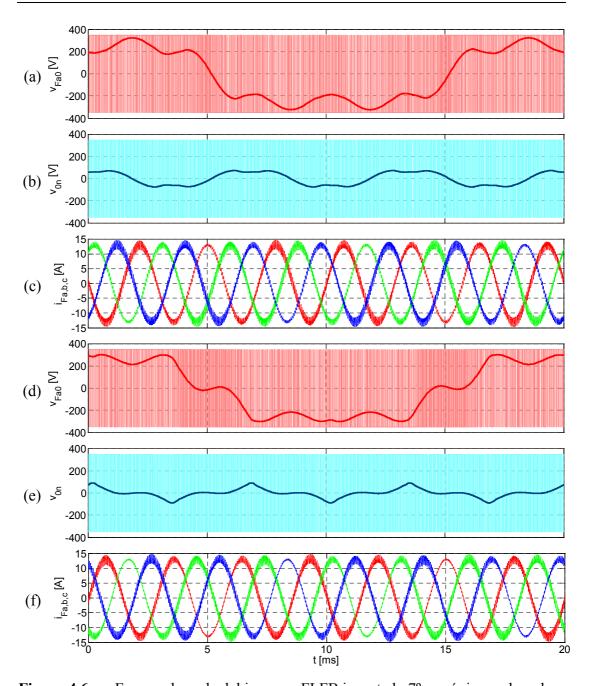

En la Figura 4.6 se muestran las formas de onda características del inversor FLFB cuando la referencia de corriente a ser inyectada coincide con la del caso anterior, es decir, un séptimo armónico de corriente equilibrado de 13A de amplitud.

En la Figura 4.6a se muestra la tensión de la rama *a* del inversor, resaltándose, mediante trazo grueso, la forma de onda resultante del promediado local de la misma. La Figura 4.5b muestra la tensión de flotación del punto intermedio del bus de continua respecto al neutro de la red, resaltándose también la evolución del promedio instantáneo de la misma. La Figura 4.6c muestra la corriente invectada en la red.

A partir de ahora, con el objetivo de simplificar nomenclatura, cuando se haga alusión a la *tensión de salida* del inversor se estará hablando de la tensión de salida de la rama medida respecto al neutro de la red, nodo 'n'. Este convenio será adoptado en todas las explicaciones que se realicen de ahora en adelante en este Capítulo.

**Figura 4.6.** Formas de onda del inversor FLFB inyectado 7º armónico en la red.

La suma de la tensión de rama, más la tensión de flotación del punto medio del bus de continua respecto al neutro de la red, da como resultado la tensión de salida del inversor. Lógicamente, a la vista de la forma de onda de corriente mostrada en la Figura 4.6c, la tensión de salida del inversor está constituida por un primer armónico de frecuencia fundamental, que es idéntico a la tensión de fase de la red, más un séptimo armónico.

En la Figura 4.6a, se aprecia como amplitud de la tensión de la rama *a* del inversor, entendiendo que se habla de su valor promediado instantáneo, podría crecer aún algo más antes de alcanzar la saturación. Esto indica que la corriente de séptimo armónico

inyectada por el inversor podría ser aún mayor de 13A. Concretamente, para el ángulo de fase establecido en la señal de referencia, se podrían llegar a alcanzar los 19A de pico en la corriente inyectada de séptimo armónico sin que existiese saturación en el inversor.

Cuando la señal de referencia se desfasa 180° respecto al caso anterior, las formas de onda resultantes para la tensión de rama, para la tensión de flotación del bus y para la corriente inyectada se muestran en las Figuras 4.6d, 4.6e y 4.6f, respectivamente. Hay que recordar que, para esta referencia de corriente, el inversor TLSC atravesaba zonas de saturación, sin embargo, como muestran las figuras señaladas anteriormente, la corriente de salida del inversor FLFB sigue correctamente a la referencia, ya que las ramas del inversor no se saturan en ningún momento. Es más, para este ángulo de fase en la señal de referencia, el margen de crecimiento de la tensión de rama puede ser aún algo mayor que en la situación anterior, llegándose a inyectar un séptimo armónico de 25A de pico, sin que exista saturación en el inversor.

Estos resultados de simulación argumentan suficientemente la afirmación realizada anteriormente, la cual otorgaba, para unas mismas condiciones de contorno, mayor capacidad de inyección de corriente de secuencia positiva y negativa al inversor FLFB que al inversor TLSC.

Es evidente que si la cuarta rama del inversor FLFB no estuviese operativa, el comportamiento de éste sería idéntico al del inversor de tres ramas en puente completo, TLFB. Como se expondrá con más detalle en el Capítulo 6, la actuación de la cuarta rama en el inversor FLFB hace que la evolución instantánea de la tensión modulada de salida difiera de la que se obtendría con el inversor TLFB, sin embargo, cuando se utiliza la modulación 3D-SVM, y para una misma señal de referencia, el valor medio instantáneo de esta tensión modulada es idéntico en ambos inversores. Por este motivo, no se realizará una simulación específica del inversor TLFB, sobreentendiéndose que su capacidad de inyección de corriente de secuencia positiva y negativa es la misma que la del inversor FLFB.

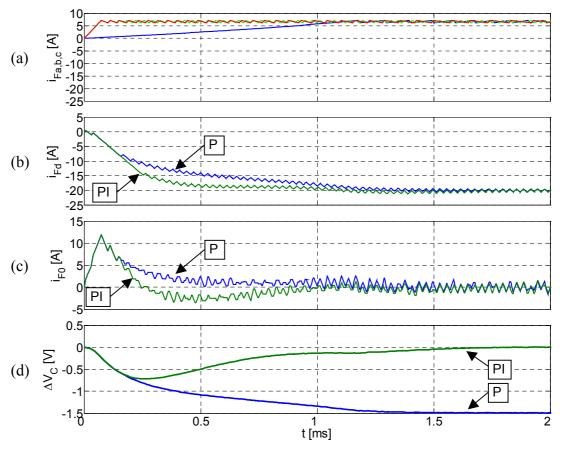

Por otro lado, cuando se intentan inyectar corrientes de secuencia homopolar en la red, el convertidor TLFB resulta inútil, por lo que no será considerado en las simulaciones que se mostrarán a continuación. En esas simulaciones, los convertidores TLSC y FLFB inyectarán corrientes de tercer y séptimo armónico, es decir, inyectarán corrientes de secuencia positiva y de secuencia homopolar.

Como se mostró en la Figura 4.5a, cuando el inversor TLSC se encontraba inyectando en la red una corriente de séptimo armónico con 13A de amplitud, las tensiones de las ramas se encontraban al borde de la saturación. Esto puede hacer pensar que el inversor no podrá inyectar corrientes armónicas adicionales, sin embargo, determinadas combinaciones armónicas harán que la tensión resultante que debe sintetizarse en las ramas del inversor se aleje de la saturación, haciendo viable la inyección de estas corrientes armónicas adicionales. Claramente, esta afirmación no abarca el caso general, ya que, en función de la distribución de módulos y fases en la corriente de referencia, puede ser que ésta sea correctamente generable o no.

Por tanto, en el convertidor TLSC, la corriente homopolar que puede ser inyectada en un momento dado depende de la corriente de secuencia positiva y negativa que se esté inyectando en ese momento.

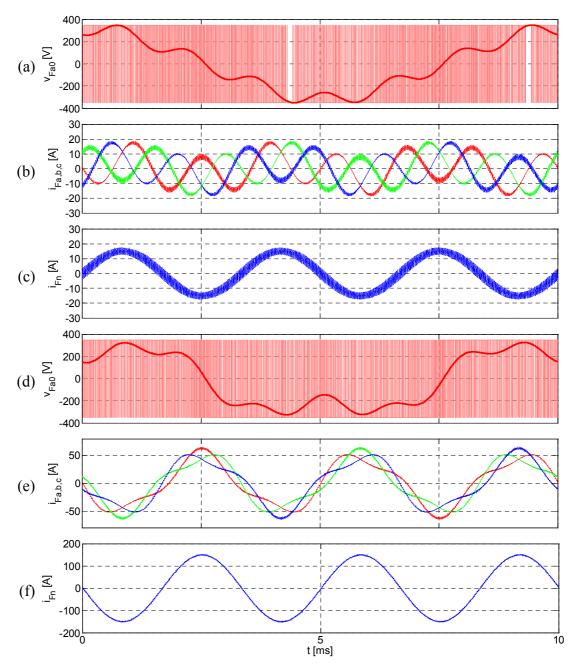

La Figura 4.7 se muestra los resultados de simulación obtenidos cuando el inversor TLSC se encuentra inyectando corriente de tercer y séptimo armónico en la red. Es importante destacar aquí que, para evitar el solapamiento de diferentes efectos que pudieran dar lugar a explicaciones confusas, se ha supuesto que la tensión del bus de continua siempre está perfectamente equilibrada, es decir, se ha considerado que

**Figura 4.7.** Formas de onda del inversor TLSC inyectado 3<sup>er</sup> y 7º armónico de corriente en la red.

dicho bus está constituido por dos fuentes de tensión ideales. Si se hubiese considerado una situación real, donde el bus de continua estuviese constituido por dos condensadores, la inyección de corriente de tercer armónico desequilibraría el reparto de tensión entre ambos condensadores, y consiguientemente, la capacidad de inyección de corriente de séptimo armónico variaría respecto a de las explicaciones que aquí se ofrecerán.

La forma de onda de la Figuras 4.7a corresponde a la tensión en la rama *a* del inversor cuando las corrientes inyectadas en la red coinciden con las mostradas en la Figura 4.5b. Estas corrientes están constituidas por un séptimo armónico de 13A, más un tercer armónico de 5A, entendiendo ambas magnitudes como valores de pico. En la Figura 4.7c se muestra la corriente que se deriva desde el conductor de neutro de la red hacia el inversor. En la Figura 4.7a se aprecia como el inversor se encuentra levemente saturado. En este caso, debido a que la magnitud de la corriente inyectada de séptimo armónico es la máxima posible, y teniendo en cuenta la fase aportada a la referencia del tercer armónico, la máxima amplitud alcanzable en esta última componente homopolar, sin saturar al inversor, es bastante baja.

En este mismo inversor, manteniendo la inyección de los 13A de séptimo armónico, cuando la referencia del tercer armónico de corriente está en contrafase respecto al caso anterior, la máxima amplitud inyectable de este tercer armónico es mucho más elevada. Esto se puede apreciar en las Figuras 4.7d, 4.7e y 4.7f. En la Figura 4.7d se observa como, para la fase considerada en la referencia de tercer armónico, la tensión resultante que debe ser sintetizada por las ramas del inversor se aleja del límite de saturación. En la figura 4.7e se muestran las corrientes que cada rama inyecta en la red, las cuales están constituidas por los 13A de séptimo armónico, más 50A de tercero. En la Figura 4.7f se muestran los 150A de tercer armónico que están siendo derivados desde el neutro de la red hacia el inversor.

En el inversor TLSC, hay que resaltar que si la corriente inyectada de séptimo armónico hubiese sido algo menor, por ejemplo 10A, el margen de tensión generable por las ramas del inversor habría sido lo suficientemente grande como para permitir la inyección de corrientes de tercer armónico con una amplitud considerable para cualquier ángulo de fase. Esto es lógico, ya que si se tiene en cuenta que la impedancia de secuencia homopolar que enlaza el inversor y la red es bastante baja para esta frecuencia, basta con generar pequeños niveles de tensión en las ramas del inversor para conseguir inyectar elevados niveles de corriente.

En la Figura 4.8 se muestran los resultados de simulación obtenidos cuando el inversor FLFB se encuentra inyectando en la red una corriente con tercer y séptimo armónico. En este caso se ha considerado que, para un determinado ángulo de fase en la señal de referencia, el inversor se encuentra inyectando en la red la máxima amplitud posible de corriente de séptimo armónico. Esta amplitud es de 25A, magnitud inalcanzabe en ningún caso por el inversor TLSC. Así mismo, se ha supuesto que la amplitud de la corriente inyectada de tercer armónico es de 50A por fase, es decir, se están derivando 150A de tercer armónico desde el conductor de neutro hacia el inversor.

**Figura 4.8.** Formas de onda del inversor FLFB inyectado 3<sup>er</sup> y 7º armónico de corriente en la red.

En la Figura 4.8a se muestra la tensión que será sintetizada por la rama *a* del inversor. Considerando que la corriente de séptimo armónico que se está inyectando en la red no varía, la tensión de la rama *a* será siempre la misma, con independencia de la fase que presente la referencia de corriente de tercer armónico. Esto es debido a

que la responsable de la inyección de esta corriente de tercer armónico es la cuarta rama del inversor.

En la Figura 4.8b se muestra la tensión que aparece entre el nodo '0' y el nodo 'n' cuando las corrientes de las fases, y la derivada desde el neutro, coinciden respectivamente con las mostradas en las Figuras 4.8c y 4.8d. De la misma manera, la Figura 4.8e muestra la tensión existente entre el nodo '0' y el nodo 'n' cuando las formas de onda de corriente corresponden a las mostradas en las Figuras 4.8f y 4.8g.

Hay que indicar que la independencia existente entre las componentes de tensión generables con secuencia positiva y negativa, y con de secuencia homopolar, no se mantiene indefinidamente, existiendo un momento en el que dichas componentes de tensión comienzan a ser dependientes. Sin embargo, esta dependencia se da para valores bastante elevados de la tensión de secuencia homopolar, lo que implica que la corriente que estaría siendo derivada desde el conductor de neutro de la red sería tan elevada que posiblemente el inversor FLFB dejase de ser el más indicado. En tales circunstancias, toda esa corriente de secuencia homopolar debería estar circulando por la cuarta rama del inversor, haciendo que los transistores de dicha rama tuviesen que presentar excelentes prestaciones.

La revisión realizada en este Apartado, acerca de las diferentes topologías del convertidor estático del SAPF, permite discernir las ventajas e inconvenientes de cada una de ellas para su aplicación en redes de potencia de cuatro hilos. Como se expondrá seguidamente, la utilización de una determinada topología en aplicaciones de filtrado activo vendrá determinada, no sólo por las prestaciones intrínsecas del propio convertidor, sino también por la facilidad de su control en este tipo de aplicaciones. En este sentido, la topología de tres ramas y condensador partido, TLSC, resulta fácilmente aplicable, por lo que en el Apartado 4.3 se propondrá una modificación de la misma a modo de solventar los inconvenientes asociados con el desequilibrio en las tensiones de los condensadores de su bus de continua.

#### 4.2. Controlador de corriente

El controlador de corriente del SAPF tiene por objetivo conseguir que las corrientes de salida del inversor sigan fielmente a las referencias aportadas al mismo.

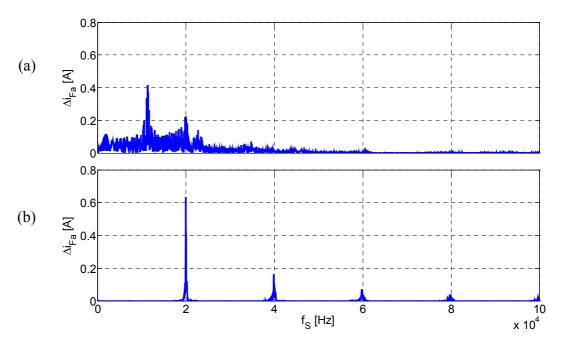

Con independencia de la técnica de control elegida, y suponiendo que no existe ningún tipo de filtro pasivo para las componentes de alta frecuencia, la corriente inyectada en la red presentará un rizado superpuesto. Dicho rizado de corriente resulta de la conmutación de las ramas del inversor, y sus parámetros característicos son su frecuencia y su amplitud. En los filtros activos en derivación, ambos parámetros son contrapuestos, ya que, debido a la evolución temporal de la tensión de red, no existe ninguna técnica de control que permita mantener constantes la frecuencia y la amplitud del rizado de corriente de manera simultanea. Mantener constante la frecuencia del rizado de la corriente, o lo que es lo mismo, mantener constante la frecuencia de conmutación, se traducirá en una mayor sencillez a la hora de sintonizar el pequeño filtro pasivo de la salida del inversor, y se minimizará el

problema de las resonancias que pudieran aparecer. Si se mantiene constante la amplitud del rizado, las corrientes inyectadas tendrán una apariencia más uniforme, aunque es posible que aparezcan secuencias de conmutación que no puedan ser convenientemente ejecutadas debido a las limitaciones impuestas por los tiempos de muertos de los transistores.

Los avances acontecidos en el campo de los procesadores digitales de señal (*DSP's*) han dado lugar a la aparición de diferentes técnicas en el control de la corriente inyectada por el convertidor estático. En [4.25][4.26][4.27][4.28][4.29] se realiza una revisión general de estas técnicas para inversores trifásicos. Debido a la aleatoriedad en la forma de onda de la corriente que debe ser inyectada por el inversor, y a la influencia de las variaciones en las tensiones de red, no todas las técnicas de control citadas en las referencias anteriores son apropiadas para aplicaciones de filtrado activo. En [4.30][4.31][4.32] se ofrece una comparación de algunas técnicas de control utilizadas en filtros activos. A modo de revisión, a continuación se detallan las técnicas de control de corriente que han demostrado mayor efectividad en aplicaciones prácticas de filtrado activo, describiendo en cada una de ellas sus principales características.

#### (A) Control lineal de corriente

La versión convencional del control lineal de corriente utiliza una modulación PWM estándar del convertidor. En este control, la señal moduladora que se compara con la portadora triangular proviene de la salida de un regulador lineal, generalmente un regulador proporcional-integral. Este control puede ser implementado mediante circuitos analógicos o digitales [4.33][4.34]. Una variante al método convencional consiste en modificar la moduladora original añadiéndole una señal de secuencia homopolar. Para inversores en puente completo, esta variante del método convencional consigue extender el rango lineal del convertidor y permite disminuir las pérdidas de conmutación en el mismo [4.35]. Aunque el control lineal se puede implementar perfectamente sobre un sistema de referencia estacionario [4.36], una variante consiste en la utilización de un sistema de referencia rotativo; ejes d-q [4.37][4.38]. La elección de los parámetros del regulador es directa cuando se trabaja en tiempo continuo. La discretización de este control se puede hacer fácilmente en el paso final de diseño, eligiendo entre diferentes métodos de integración (por ejemplo Euler o trapezoidal). Este método de control presenta una excelente inmunidad al ruido, teniendo en cuenta que el limitado ancho de banda del regulador elimina las componentes de alta frecuencia de la señal de error de corriente. En sistemas continuos, la limitación del ancho de banda se debe a la restricción impuesta por la máxima pendiente de la señal moduladora, la cual no puede superar en ningún momento la pendiente de la portadora triangular. En sistemas discretos, esta limitación viene impuesta por la constante de tiempo de actualización de consignas en el modulador. La limitación del ancho de banda del regulador lineal, implica errores significativos en el seguimiento de la señal de referencia de armónicos de orden elevado. Por tanto, en aplicaciones de filtrado activo, el retardo introducido por el modulador, y el efecto de la respuesta natural del regulador, hace que el control lineal de corriente no consiga unos resultados completamente satisfactorios en la compensación armónica de corrientes de red con alto grado de variabilidad [4.30].

#### (B) Control predictivo de corriente

Este tipo de control predice, en cada periodo de modulación, y en base al error actual y a los parámetros del sistema, el valor que debería de adoptar la tensión de salida del inversor para asegurar que la corriente invectada alcance el valor de referencia. Cuando la tensión de salida del inversor se elige de forma que el error de corriente es eliminado al final del siguiente periodo de conmutación, este control se conoce como dead-beat [4.39][4.40] y es inherentemente la estrategia de control pseudo-lineal más rápida que puede ser adoptada [4.41][4.42]. En régimen permanente, este control asegura que la corriente sigue exactamente a la referencia con un retraso de dos periodos de muestreo. Este sistema de control se basa en la existencia de un modelo interno del sistema conectado a la salida del inversor, el cual se usa para predecir la respuesta dinámica. Lógicamente, las variaciones en los parámetros del modelo, respecto a la situación real, hacen que este control sea susceptible a inestabilidades y oscilaciones. El control dead-beat se suele programar en un procesador digital de señal, y generalmente utiliza modulación vectorial en el convertidor, la cual es también apropiada para implementación digital. Esta técnica de control requiere una elevada potencia de procesado, y necesita una frecuencia de muestreo relativamente elevada. En versiones avanzadas del control dead-beat, es común el uso de un estimador de la tensión de red, con lo que se evita el sensado de dicha variable. Sin embargo, los errores cometidos en esta estimación influirán negativamente en la estabilidad y robustez del controlador. Así mismo, los retardos debidos a estos cálculos suponen una seria desventaja en esta técnica [4.43]. Con el objetivo de reducir el retraso de dos periodos de conmutación, la corriente se muestrea dos veces en cada periodo de conmutación, con lo que se consigue reducir dicho retardo a solo un periodo [4.44]. Otro aspecto importante en este control es la influencia del filtro pasivo de alta frecuencia que está colocado a la salida del inversor, el cual debe ser tenido en cuenta en el modelo, dando lugar a un aumento adicional del tiempo de procesado. En el control dead-beat, el rizado de la corriente no puede ser establecido explícitamente, y no presenta la capacidad inherente de limitar la corriente instantánea. La idoneidad de esta técnica de control para ser programada en un procesador digital de señal junto con sistemas avanzados de modulación del convertidor, ha hecho que en los últimos hayan aparecido numerosas aplicaciones de control de filtros activos basadas en ella [4.48][4.49][4.50].

#### (C) Control deslizante de corriente

Los convertidores de potencia se encuentran enmarcados dentro de los sistemas de estructura variable, los cuales son sistemas no lineales con acciones discontinuas de control. Esto hace que el control deslizante (*sliding control*), debido a sus características de invariancia, robustez y simple implementación, resulte un camino natural para el control de convertidores de potencia [4.48]. El control en modo deslizante es un control de estructura variable, el cual selecciona el estado de conmutación adecuado en el inversor para guiar la trayectoria de las variables de estado hacia una superficie de conmutación predefinida. Cuando un sistema gobernado en modo deslizante alcanza la superficie de control, éste es forzado a restringir su evolución sobre dicha superficie de control para todos los instantes de tiempo subsecuentes [4.49]. La respuesta dinámica del sistema, restringida a esa

superficie de control, representa el comportamiento del sistema controlado. En este tipo de control, básicamente se deben considerar tres pasos, que son: proponer la superficie de control, verificar la existencia de control en modo deslizante, y analizar la estabilidad del sistema en esa superficie [4.50][4.51][4.52]. En filtros activos, la aplicación del control deslizante de corriente en tiempo continuo es una práctica habitual [4.53][4.54]. El control deslizante en tiempo continuo asume una frecuencia de conmutación infinita, y se debe aplicar una banda de histéresis para conseguir limitar la frecuencia de conmutación. Por tanto, la frecuencia de conmutación en este caso no es constante, y presenta un espectro continuo en el rizado de la corriente inyectada. La discretización del control soluciona este problema, dando como resultado una frecuencia de conmutación constante [4.55]. En los últimos años, está creciendo el uso de esta técnica de control en aplicaciones de filtrado activo, debido a su idoneidad para ser implementada en procesadores digitales de señal [4.56][4.57].

#### (D) Control por histéresis de corriente

El control por histéresis se ha utilizado extensamente en la regulación de corriente de convertidores estáticos, y concretamente, en el campo del filtrado activo de corriente, este controlador ya fue empleado en los primeros desarrollos [4.13]. En la versión básica de este controlador, la corriente inyectada se compara con la corriente de referencia, y el error resultante se aplica a un comparador de histéresis de banda fija, obteniéndose así las señales de conmutación de los transistores para mantener el error en la corriente invectada dentro de esta banda de histéresis [4.25]. Debido a su inherente no linealidad, y a la ausencia de retardos, este método de control es capaz de suministrar la respuesta dinámica más rápida posible. Este sistema de control resulta estable y robusto a variaciones de carga y otro tipo de perturbaciones dinámicas. El control por histéresis resulta sencillo de implementar y es muy utilizado en el control de inversores, suministrando además una limitación instantánea de la corriente. A pesar de las ventajas citadas, esta técnica de control muestra varias características indeseables. La principal desventaja es que da lugar a una frecuencia de modulación variable en el inversor de potencia, lo cual complica el diseño del filtro pasivo de salida del mismo, y puede dar lugar a resonancias con la red. El control por histéresis se aplica fácilmente a inversores en los que las ramas de transistores trabajan de manera independiente, sin embargo en inversores en puente completo, la interacción entre las corrientes de las fases afecta de manera negativa en el funcionamiento de este controlador. En los últimos años se han realizado múltiples mejoras sobre el controlador original. La primera de ellas consiste en la obtención de una frecuencia de conmutación constante a partir del establecimiento de una anchura de banda de histéresis variable [4.58]. En el Apartado 4.5 se propone un algoritmo sencillo para conseguir esta funcionalidad. Otra mejora al método original, aplicable a convertidores en puente completo, consiste en desacoplar las señales de error de las diferentes fases, lo cual se consigue restando al error de corriente de cada fase, la interferencia producida por la tensión instantánea de secuencia homopolar existente a la salida del inversor [4.59]. Cuando los errores de corriente en las diferentes fases se encuentran desacoplados, los instantes de conmutación de las ramas pueden ser sincronizados mediante una señal de reloj, con lo que se pueden obtener secuencias óptimas de conmutación [4.60]. La sencillez del control básico por histéresis posibilita la implementación de un sistema de naturaleza analógica, aunque la inclusión de las diferentes mejoras realizadas sobre el método original propician su implementación digital [4.61][4.62], apareciendo continuamente nuevas aportaciones y prestaciones [4.63][4.64][4.65][4.66]. Las características finales obtenidas en este método de control lo hacen apropiado para aplicaciones de altas prestaciones, como puede ser el filtrado activo de corriente, en las que es necesario un error de seguimiento acotado y una elevada velocidad de respuesta..

Existe otra técnica de control que, debido a su sencillez de implementación en sistemas digitales con frecuencia de muestreo constante, es muy utilizada en los SAPF's. Esta técnica es conocida como *control bang-bang* o *modulación delta* [4.67][4.68][4.69]. En este trabajo, este tipo de control no ha sido considerado de forma separada, ya que, a juicio del Autor, puede ser catalogado como un control de histéresis con amplitud de banda nula y frecuencia de muestreo constante. En lo referente a velocidad de respuesta y simplicidad, la modulación delta básica presenta características muy similares al control por histéresis, aportando la ventaja de limitar la máxima frecuencia de conmutación a la mitad de la frecuencia de muestreo, lógicamente, a costa de no mantener constante la amplitud del error de corriente.

En los prototipos experimentales desarrollados en este trabajo, se han utilizado dos técnicas diferentes de control de corriente. En aquellos prototipos en los que deseaba evaluar la bondad de los algoritmos de modulación vectorial expuestos en el Capítulo 5, se ha utilizado un control lineal. En los prototipos en los que se deseaba evaluar el comportamiento de la topología propuesta en el Aparato 4.3, cuando actuaba bajo las consignas aportadas por el controlador energético expuesto en el Capítulo 6, se ha utilizado un control por histéresis de banda adaptativa.

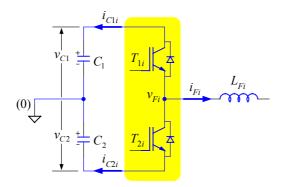

## 4.3. Inversor de cuatro ramas con condensador repartido

El inversor de tres ramas con condensador partido, TLSC, ha sido bien acogido por parte de fabricantes e investigadores para su utilización en aplicaciones de filtrado activo de corriente en redes de cuatro hilos.

En apartados anteriores se indicó que la amplia utilización de este convertidor no reside en la excelencia de sus prestaciones, ya que existen otras topologías que aprovechan mejor los recursos de tensión del bus de continua y alcanzan mayores niveles de inyección de corriente; sino que dicha utilización viene justificada por la sencillez de su control, ya que las tres ramas del mismo funcionan de manera independiente, y consiguientemente, dicho control puede ser concebido como el de tres inversores monofásicos independientes.

También se indicó anteriormente que, cuando este inversor inyecta corriente homopolar, aparece un desequilibrio en el reparto de la tensión de los condensadores de su bus de continua. Este desequilibrio, obliga a incrementar el tamaño de dichos condensadores para asegurar las adecuadas condiciones de operación del SAPF y complica el control del inversor.

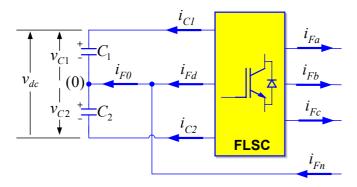

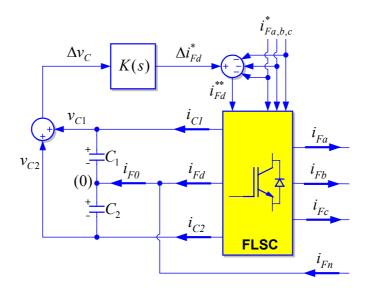

**Figura 4.9.** Estructura de un SAPF con un inversor FLSC.

En este trabajo se propone una topología alternativa que permite solventar el problema del desequilibrio de tensión en el bus de continua del convertidor TLSC. Esta topología se muestra en la Figura 4.9, y como se puede apreciar, en ella se ha añadido una cuarta rama encargada del equilibrado de tensiones en el bus de continua. A este inversor se le ha denominado "inversor de cuatro ramas con condensador repartido" (FLSC – *Four-Leg Split-Capacitor*). En lo referente a sencillez de control, este inversor presenta las mismas ventajas que el inversor TLSC, pero además, la cuarta rama aporta un nuevo grado de libertad que permite controlar la corriente inyectada en el punto intermedio del bus de continua. Es justo decir que esta topología fue presentada, de forma muy breve, en una conferencia celebrada en 1997 [4.70], y a pesar de sus ventajas, existen muy pocos trabajos en los que se aplique para el filtrado activo de corriente [4.70][4.71].

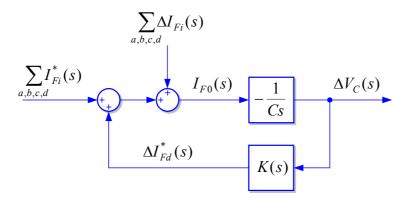

En esta topología de inversor, si la corriente inyectada por la rama d,  $i_{Fd}$ , es idéntica, y de signo opuesto, a la corriente derivada desde el conductor de neutro de la red,  $i_{Fn}$ , entonces la corriente inyectada en el nodo intermedio del bus de continua,  $i_{F0}$ , será nula, por lo que no aparecerá desequilibrio en el reparto de tensiones en dicho bus. En principio, para conseguir este comportamiento basta con imponer que la referencia de corriente de la rama d sea igual, y de signo opuesto, al sumatorio de las referencias de corriente de las otras tres ramas. Sin embargo, la imposición de esta corriente de referencia en la rama d no garantizará en todo momento una inyección nula de corriente en el nodo intermedio del bus, ya que, en primer lugar, el sumatorio del rizado de corriente en las cuatro ramas no será instantáneamente nulo, y en segundo lugar, podrán aparecer errores transitorios en el seguimiento de las corrientes de referencia. Por consiguiente, será necesaria la utilización de un controlador de la tensión diferencial del bus de continua que garantice la correcta ecualización de tensiones entre los condensadores del mismo. Este controlador se presenta en el Apartado 4.6.

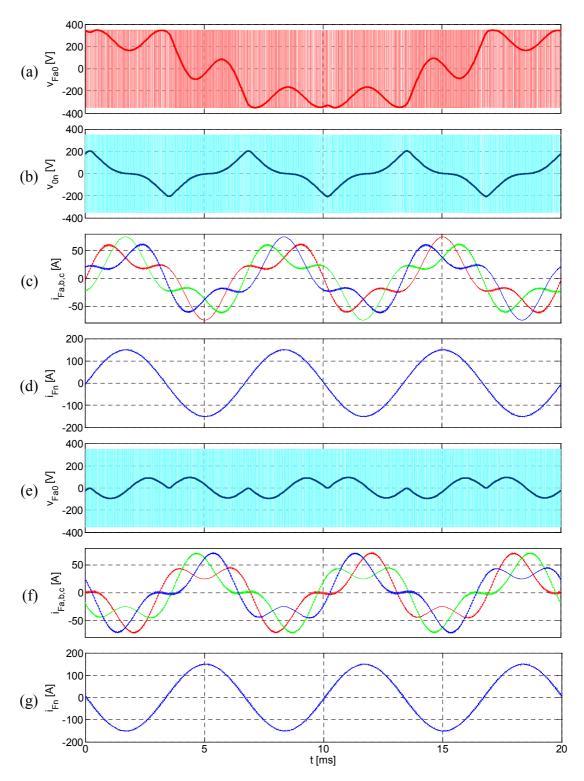

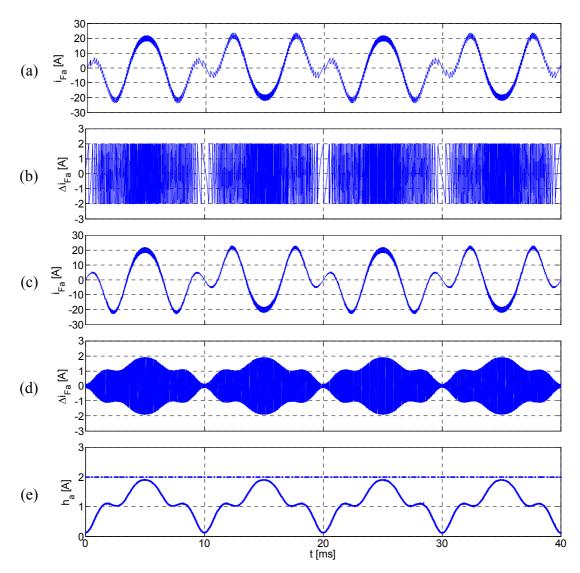

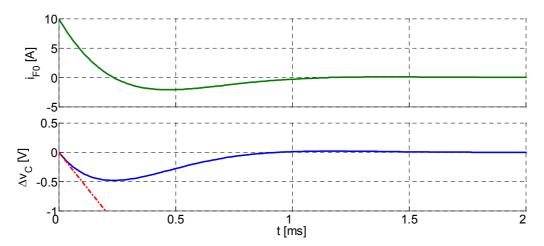

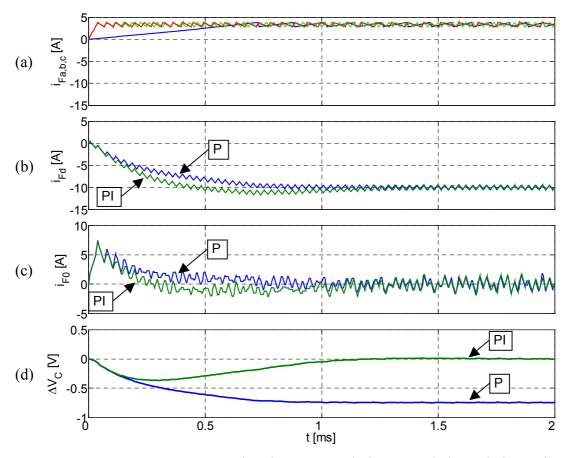

En la Figura 4.7 se mostraban las formas de onda de tensión y corriente del inversor TLSC cuando éste inyectaba corrientes de secuencia homopolar. En aquel caso, el bus de continua estaba constituido por dos fuentes ideales de tensión, con lo que no existía el efecto del desequilibrio provocado por las corrientes de secuencia homopolar. Para evidenciar el fenómeno del desequilibrado del bus de continua se ha utilizado el convertidor TLSC que se mostró en la Figura 4.2. En este circuito se ha considerado que: i) el valor de los condensadores del bus de continua es  $C_1 = C_2 = 1000 \mu F$ ; ii) la tensión inicial del bus es de 700V (350V en cada condensador); iii) el valor de pico de la tensión de fase de la red es de 311V; iv) las inductancias de acoplo a red son de 2,2mH. Además, se ha utilizado un control de corriente por histéresis, con una banda de amplitud constante igual a 2A.

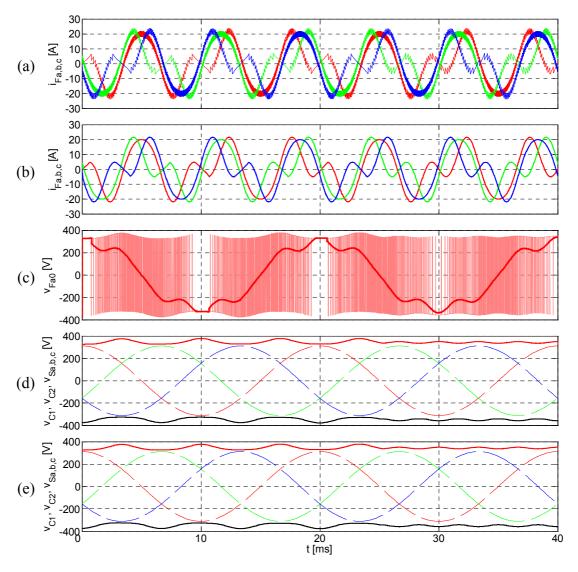

La Figura 4.10 muestra los resultados de simulación obtenidos cuando el convertidor TLSC inyecta 10A de tercer armónico en cada fase. La corriente inyectada en la fase a se muestra en la Figura 4.10a, pudiéndose apreciar como, al estar trabajando con una banda de histéresis de amplitud constante, la frecuencia de conmutación de los transistores es variable. En la Figura 4.10b se muestra la corriente inyectada en el punto intermedio del bus de continua, la cual presenta un rizado seudo-aleatorio que resulta de la combinación de los rizados individuales de las corrientes inyectadas por cada una de las ramas del inversor. La Figura 4.10c muestra la tensión de la rama a, resaltando en trazo grueso la tensión resultante del promediado local de la misma.

**Figura 4.10.** Desequilibrio de tensiones en el bus DC del inversor TLSC cuando inyecta corriente de secuencia homopolar.

En la Figura 4.10 se aprecia como el reparto de tensión entre los condensares del bus de continua va variando a lo largo del tiempo, aunque la tensión absoluta del bus permanece prácticamente constante. Este desequilibrio de tensión en el bus de continua ha de ser tenido en cuenta a la hora de plantear el algoritmo de modulación del inversor, ya que origina la pérdida de la relación de proporcionalidad entre el índice de modulación de la rama y la tensión media que aparece a la salida de la misma (por ejemplo, en el caso de una modulación estándar basada en portadora). Además, como se aprecia en la Figura 4.10d, el desequilibro de tensión en el bus de continua disminuye la capacidad de inyección de corriente por parte del inversor, pudiéndose llegar a alcanzar situaciones en las que, al disminuir la tensión de alguno de los condensadores por debajo del valor de pico de las tensiones de red, se pierda completamente el control de la corriente inyectada. Para evitar estos efectos indeseables en el inversor TLSC, únicamente se puede aumentar el valor nominal de la tensión del bus de continua, o aumentar el tamaño de los condensadores.

Manteniendo los mismos parámetros de trabajo que en el caso anterior, en la Figura 4.11 se muestran los resultados de simulación obtenidos al utilizar el inversor FLSC de la Figura 4.9. Ahora, se puede observar como la corriente inyectada en el punto intermedio del bus de continua es prácticamente nula. La Figura 4.11b muestra el rizado que finalmente se inyecta en dicho punto medio, el cual aparece de la combinación de los rizados individuales de las corrientes inyectadas por las cuatro

**Figura 4.11.** Equilibrado de las tensiones del bus DC del inversor FLSC cuando inyecta corrientes de secuencia homopolar.

ramas del inversor. Las Figuras 4.11c y 4.11d muestran como ahora existe un reparto equitativo de tensión entre los dos condensadores del bus de continua, lo cual conduce a una relación de proporcionalidad entre el índice de modulación de la rama y la tensión media que aparece a la salida de la misma. En estas figuras también se puede apreciar como, para las condiciones de simulación consideradas, el equilibrado de las tensiones del bus aumenta el margen de tensión suministrable por el inversor antes de alcanzar la saturación, por lo que su capacidad de invección de corriente también aumenta. Por último, el margen de controlabilidad del inversor también ha aumentado, ya que las tensiones de los condensadores no se aproximan peligrosamente al valor de pico de las tensiones de red.

En el Apartado 4.6, se realiza un estudio analítico detallado de la evolución de la tensión diferencial del bus de continua, y se presentan las reglas de diseño de un regulador simple que evite los errores de régimen permanente que pudieran aparecer en la misma.

En las simulaciones realizadas hasta el momento, se ha considerado que la tensión de red no presenta componente homopolar, por lo que la potencia activa instantánea desarrollada por el SAPF cuando inyecta corriente con esa secuencia es permanentemente nula. Consiguientemente, como se puede observar en las simulaciones anteriores, la energía acumulada en el bus de continua permanece prácticamente constante, salvando únicamente las pequeñas variaciones de energía que se ocasionan a raíz de la carga y descarga de las inductancias de acoplo. Cuando el SAPF inyecte en la red componentes de corriente que generen valores no nulos en la evolución de la potencia instantánea asociada al mismo, la energía acumulada en el bus de continua variará, lo cual también provocará variaciones en la tensión absoluta de dicho bus. En el Capítulo 6 de este trabajo se realiza un estudio analítico de la evolución de la energía en el bus de continua y se diseña el controlador apropiado encargado de mantener constante el valor medio de la misma.

El inversor FLSC aquí presentado no pretende competir en prestaciones con el inversor FLFB, sino que, en concordancia con el título de este trabajo, pretende aportar una solución efectiva a los problemas que el desequilibrio de las tensiones de los condensadores plantea en el inversor TLSC, el cual es sumamente utilizado en trabajos de investigación y en equipos comerciales.

## 4.4. Modelo promediado en espacio de estado del SAPF

Para poder diseñar los diferentes controladores del SAPF es necesario disponer de un modelo de éste que determine el comportamiento de sus variables características en función de los parámetros de control y de las condiciones de contorno del sistema.

Si en la concepción del modelo de simulación del convertidor estático del SAPF se tiene en cuenta la estructura variable de sistema, esto es, si en dicho modelo se hacen intervenir las variables de conmutación de los transistores del convertidor, el coste de procesado en la simulación del convertidor será muy elevado, lo cual se traducirá en varias horas de computación para simular intervalos de tiempo que sólo abarcan algunas decenas de ciclos de la tensión de red. En este Apartado, mediante la utilización de la técnica de promediado en espacio de estado, se procede a la generación de un modelo continuo del SAPF que refleja la evolución promediada de las variables de estado del mismo. Este modelo agilizará enormemente las tareas de simulación y posibilitará el diseño de los controladores necesarios.

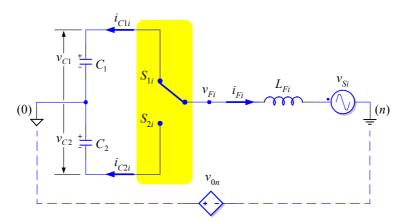

En los convertidores bidireccionales de corriente, se puede identificar una unidad genérica de conmutación, como la mostrada en la Figura 4.12, denominada *rama de conmutación*. Cada rama está compuesta por dos elementos de conmutación, y tiene una fuente de tensión en un lado (un condensador en este caso), y una fuente de corriente en el otro (una inductancia en este caso). Estas características convierten a la rama en una unidad genérica de conmutación.

**Figura 4.12.** Rama genérica de convertidores bidireccionales de corriente.

En el circuito de la Figura 4.12, se ha considerado que el bus de continua está constituido por dos condensadores para facilitar explicaciones posteriores. Los elementos de conmutación mostrados en esta figura pueden ser descritos mediante un interruptor genérico S, como muestra la Figura 4.13, cuya función de control se expone en (4.1).

$$s = \begin{cases} -1, & i = 0, \text{ si } s \text{ abierto} \\ 1, & v = 0, \text{ si } s \text{ cerrado} \end{cases}$$

(4.1)

**Figura 4.13.** Interruptor genérico *S*.

Existen ciertas restricciones para los dos elementos de conmutación de una rama. Las restricciones incluyen que la fuente de tensión, o los condensadores, no pueden ser cortocircuitados, y que la fuente de corriente, o la inductancia, no puede quedar en circuito abierto. Estas restricciones conducen al requerimiento de que los dos interruptores de una rama deben trabajar de forma complementaria, es decir, para evitar el cortocircuito de los condensadores, sólo uno de los dos interruptores puede estar cerrado al mismo tiempo. De la misma manera, para evitar que la inductancia quede en circuito abierto, uno de los dos interruptores debe estar cerrado en cualquier

momento. Basándonos en la función de conmutación definida en (4.1), se puede describir la siguiente relación aritmética:

$$s_{1i} + s_{2i} = 0. ag{4.2}$$

Como resultado, cada rama puede ser representada mediante un conmutador de un solo polo y doble vía como el mostrado en la Figura 4.14. En esta figura, se ha representado la conexión a red de la rama genérica, así como las diferentes variables de interés. Si esta rama trabajase de manera individual, sería imposible la circulación de corriente alguna, a no ser que se estableciese un vínculo de unión entre los nodos '0' y 'n'. Este vínculo de unión aparece cuando las diferentes ramas del convertidor trabajan de manera conjunta para confeccionar las topologías de los inversores anteriormente expuestos.

En la Figura 4.14, la tensión  $v_{0n}$  representa la tensión de flotación del punto medio del bus de continua respecto al neutro de la red. Lógicamente, el valor de esta tensión será nulo para aquellos inversores que presentan el punto intermedio del bus conectado a neutro de la red, mientras que en los inversores en puente completo, su valor dependerá del estado de conmutación de las diferentes ramas.

**Figura 4.14.** Rama genérica de conmutación representada mediante un conmutador de simple polo y doble vía.

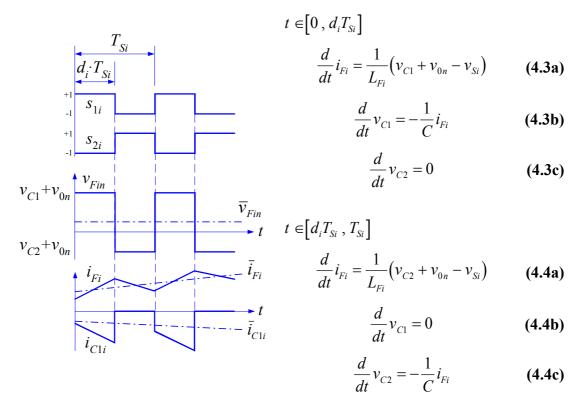

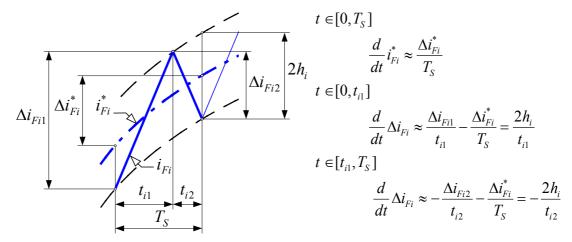

Las señales de PWM de esta rama se muestran en la Figura 4.15, donde  $T_{Si}$  es el periodo de conmutación y  $d_i$  es el ciclo de trabajo del interruptor superior de la rama,  $S_{Ii}$ . En esta figura, para evaluar la contribución particular de esta rama sobre las corrientes del bus de continua, se ha supuesto que la fuente tensión  $v_{0n}$  adopta un valor finito, encontrándose físicamente conectada entre los nudos '0' y 'n', por lo que podrá existir circulación de corriente en dicha rama. Así mismo, se ha considerado un instante particular en el que  $|v_{C1}| > |v_{C2}|$ ,  $v_{Si} = 0$ V y  $d_i = 0.5$ , con lo que la corriente por la inductancia, en promedio, será creciente.

Considerando que en la rama de conmutación mostrada en la Figura 4.14 se cumple que  $C_1$ = $C_2$ =C, un análisis simple permite obtener las expresiones (4.3) y (4.4), las cuales describen la evolución de las diferentes variables para cada intervalo de conmutación. En la interpretación de estas ecuaciones, hay que recordar que, según los criterios de medida de la Figura 4.14, se tiene que  $v_{C1} > 0$  y  $v_{C2} < 0$ .

**Figura 4.15.** PWM de la rama de conmutación y sus correspondientes corrientes y tensiones.

A partir de las expresiones (4.3) y (4.4), la rama genérica de conmutación puede ser representada mediante el modelo promediado en espacio de estado mostrado en (4.5), donde (4.5a) corresponde a la ecuación de estado y (4.5b) a la ecuación de salida. Con objeto de simplificar la notación, las variables de esta ecuación representan directamente valores promediados sobre un periodo de conmutación, es decir:  $i_{Fi} \equiv \bar{i}_{Fi}$ ,  $v_{Si} \equiv \bar{v}_{Si}$ , etc. En posteriores ecuaciones, y mientras no se especifique lo contrario, se adoptará este criterio de notación para las variables promediadas.

$$\begin{bmatrix} \dot{i}_{Fi} \\ \dot{v}_{C1} \\ \dot{v}_{C2} \end{bmatrix} = \begin{bmatrix} 0 & \frac{d_i}{L_{Fi}} & \frac{(1-d_i)}{L_{Fi}} \\ -\frac{d_i}{C} & 0 & 0 \\ -\frac{(1-d_i)}{C} & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{Fi} \\ v_{C1} \\ v_{C2} \end{bmatrix} + \begin{bmatrix} -\frac{1}{L_{Fi}} \\ 0 \\ 0 \end{bmatrix} (v_{Si} - v_{0n})$$

$$(4.5a)$$

$$\begin{bmatrix} v_{Fi0} \\ i_{C1i} \\ i_{C2i} \end{bmatrix} = \begin{bmatrix} 0 & d_i & 1 - d_i \\ -d_i & 0 & 0 \\ -(1 - d_i) & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{Fi} \\ v_{C1} \\ v_{C2} \end{bmatrix}$$

(4.5b)

Se define ahora la variable de control  $c_i \in [-1, 1]$ , la cual guarda las relaciones mostradas en (4.6) con el ciclo de trabajo  $d_i \in [0, 1]$ .

$$c_i = -1 + 2d_i \tag{4.6a}$$

$$d_i = \frac{1+c_i}{2}$$

;  $1-d_i = \frac{1-c_i}{2}$  (4.6b)

Por lo que las ecuaciones en espacio de estado mostradas en (4.3) pueden ser expresadas como:

$$\begin{bmatrix} \dot{i}_{Fi} \\ \dot{v}_{C1} \\ \dot{v}_{C2} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} \frac{1}{L_{Fi}} & 0 & 0 \\ 0 & \frac{1}{C} & 0 \\ 0 & 0 & \frac{1}{C} \end{bmatrix} \begin{bmatrix} 0 & 1+c_i & 1-c_i \\ -(1+c_i) & 0 & 0 \\ -(1-c_i) & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{Fi} \\ v_{C1} \\ v_{C2} \end{bmatrix} + \begin{bmatrix} -\frac{1}{L_{Fi}} \\ 0 \\ 0 \end{bmatrix} (v_{Si} - v_{0n}), \quad (4.7a)$$

$$\begin{bmatrix} v_{Fi0} \\ i_{C1i} \\ i_{C2i} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} 0 & 1+c_i & 1-c_i \\ -(1+c_i) & 0 & 0 \\ -(1-c_i) & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{Fi} \\ v_{C1} \\ v_{C2} \end{bmatrix}.$$

(4.7b)

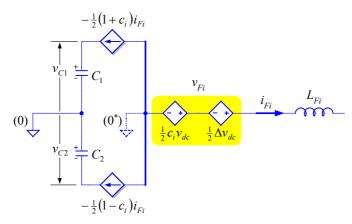

De (4.7b), la tensión promediada de la rama es:

$$v_{Fi0} = \frac{1}{2} \left[ (1 + c_i) v_{C1} + (1 - c_i) v_{C2} \right] = \frac{1}{2} (c_i v_{dc} + \Delta v_{dc}),$$

(4.8)

donde,  $v_{dc} = v_{C1} - v_{C2}$  representa la *tensión absoluta* del bus de continua, y  $\Delta v_{dc} = v_{C1} + v_{C2}$  representa la *tensión diferencial* de dicho bus.

Por tanto, en base a las ecuaciones (4.7b) y (4.8), la rama genérica que se mostró en la Figura 4.12 puede ser ahora representada mediante el modelo continuo promediado mostrado en la Figura 4.16. Nótese en esta figura que el nodo '0' se encuentra virtualmente conectado al nodo '0\*', es decir, las tensiones  $v_{Fi0}$  y  $v_{Fi0*}$  serán idénticas en todo momento.

**Figura 4.16.** Modelo promediado de una rama de conmutación en función de la variable de control  $c_i$ .

A partir de la ecuación (4.8), la variable de control  $c_i$  puede expresarse en función de las tensiones que afectan a la rama, obteniendo:

$$c_{i} = \frac{2v_{Fi0} - \Delta v_{dc}}{v_{dc}}.$$

(4.9)

Sustituyendo (4.9) en (4.7b) se llega a:

$$i_{C1i} = -\frac{1}{2} \left( \frac{v_{dc} + 2v_{Fi0} - \Delta v_{dc}}{v_{dc}} \right) i_{Fi} = -\frac{\left(v_{Fi0} - v_{C2}\right)}{v_{dc}} i_{Fi},$$

(4.10a)

$$i_{C2i} = -\frac{1}{2} \left( \frac{v_{dc} - 2v_{Fi0} + \Delta v_{dc}}{v_{dc}} \right) i_{Fi} = \frac{\left( v_{Fi0} - v_{C1} \right)}{v_{dc}} i_{Fi}.$$

(4.10b)

Teniendo en cuenta que la tensión de la rama vale:

$$v_{Fi0} = v_{Fin} - v_{0n} = L_{Fi}\dot{l}_{Fi} + v_{Si} - v_{0n},$$

(4.11)

Entonces las expresiones de (4.10) se transforman en:

$$i_{C1i} = \frac{1}{v_{dc}} \left[ (v_{0n} + v_{C2}) i_{Fi} - v_{Si} i_{Fi} - L_{Fi} i_{Fi} i_{Fi} \right],$$

(4.12a)

$$i_{C2i} = \frac{1}{v_{dc}} \left[ -(v_{0n} + v_{C1})i_{Fi} + v_{Si}i_{Fi} + L_{Fi}i_{Fi}i_{Fi} \right].$$

(4.12b)

Las ecuaciones mostradas en (4.12) reflejan el significado energético de las corrientes que circulan por el bus de continua, y su utilidad quedará perfectamente evidenciada cuando se considere el efecto conjunto de todas las ramas que constituyen el inversor.

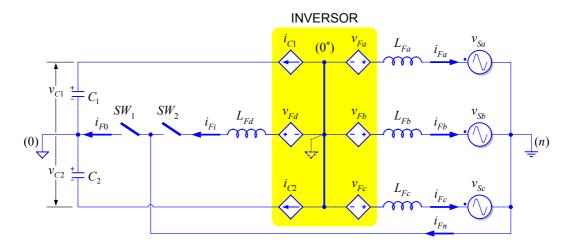

Una vez presentado el modelo de una rama de conmutación, resulta sencillo obtener el modelo promediado en espacio de estado del SAPF mediante la agregación de las diferentes ramas que constituyen el inversor. En base al circuito que se mostraba en la Figura 4.16, se puede dibujar la Figura 4.17, la cual presenta un modelo general del SAPF. En este modelo general, las fuentes de tensión controladas,  $v_{Fi}$ , simbolizan las dos fuentes agrupadas de la Figura 4.16, ver ecuación (4.8). Así mismo,  $SW_1$  y  $SW_2$  representan dos interruptores genéricos, como los mostrados en la Figura 4.13, y en función de sus variables de control, el modelo de la Figura 4.17 describe el comportamiento del SAPF cuando en su diseño se utilizan los convertidores enumerados en la Tabla 4.1.

| $sw_1$ | $sw_2$ | Convertidor | Variables                                           |

|--------|--------|-------------|-----------------------------------------------------|

| 0      | 0      | TLFB        | $v_{0n} \neq 0$ ; $i_{F0} = i_{Fd} = i_{Fn} = 0$    |

| 0      | 1      | FLFB        | $v_{0n} \neq 0$ ; $i_{F0} = 0$ ; $i_{Fd} = -i_{Fn}$ |

| 1      | 0      | TLSC        | $v_{0n} = 0$ ; $i_{F0} = i_{Fn}$ ; $i_{Fd} = 0$     |

| 1      | 1      | FLSC        | $v_{0n} = 0$ ; $i_{F0} = i_{Fd} + i_{Fn}$           |

**Tabla 4.1.** Topologías del modelo del SAPF en función de  $sw_1$  y  $sw_2$ .

**Figura 4.17.** Modelo promediado general del SAPF.

A partir de la combinación de las expresiones mostradas en (4.7) para las diferentes ramas, este modelo general del SAPF puede ser representado mediante las ecuaciones de estado de (4.13a) y las ecuaciones de salida de (4.13b):

$$\dot{\mathbf{I}}_{F} = \frac{1}{L_{F}} \cdot \left( \mathbf{C} \cdot \mathbf{V}_{C} - \mathbf{V}_{S} + \mathbf{V}_{0n} \right) \quad , \quad \dot{\mathbf{V}}_{C} = -\frac{1}{C} \cdot \mathbf{C}^{T} \cdot \mathbf{I}_{F} \,, \tag{4.13a}$$

$$\mathbf{V}_{F0} = \mathbf{C} \cdot \mathbf{V}_C$$

,  $\mathbf{I}_C = -\mathbf{C}^T \cdot \mathbf{I}_F$ , (4.13b)

donde:

$$\mathbf{I}_{F} = \begin{bmatrix} i_{Fa} & i_{Fb} & i_{Fc} & i_{Fd} \end{bmatrix}^{T} , \quad \mathbf{I}_{C} = \begin{bmatrix} i_{C1} & i_{C2} \end{bmatrix}^{T},$$

(4.14a)

$$\mathbf{V}_{C} = \begin{bmatrix} v_{C1} & v_{C2} \end{bmatrix}^{T}$$

,  $\mathbf{V}_{F0} = \begin{bmatrix} v_{Fa0} & v_{Fb0} & v_{Fc0} & v_{Fd0} \end{bmatrix}^{T}$ , (4.14b)

$$\mathbf{V}_{S} = \begin{bmatrix} v_{Sa} & v_{Sb} & v_{Sc} & 0 \end{bmatrix}^{T}, \quad \mathbf{V}_{0n} = v_{0n} \begin{bmatrix} 1 & 1 & 1 & 1 \end{bmatrix}^{T},$$

(4.14c)

$$\mathbf{C} = \frac{1}{2} \begin{bmatrix} (1+c_a) & (1-c_a) \\ (1+c_b) & (1-c_b) \\ (1+c_c) & (1-c_c) \\ (1+c_d) & (1-c_d) \end{bmatrix},$$

(4.14d)

habiéndose considerado que  $C_I = C_2 = C$  y  $L_{Fi} = L_F \ \forall i_{i=\{a,b,c,d\}}$  .

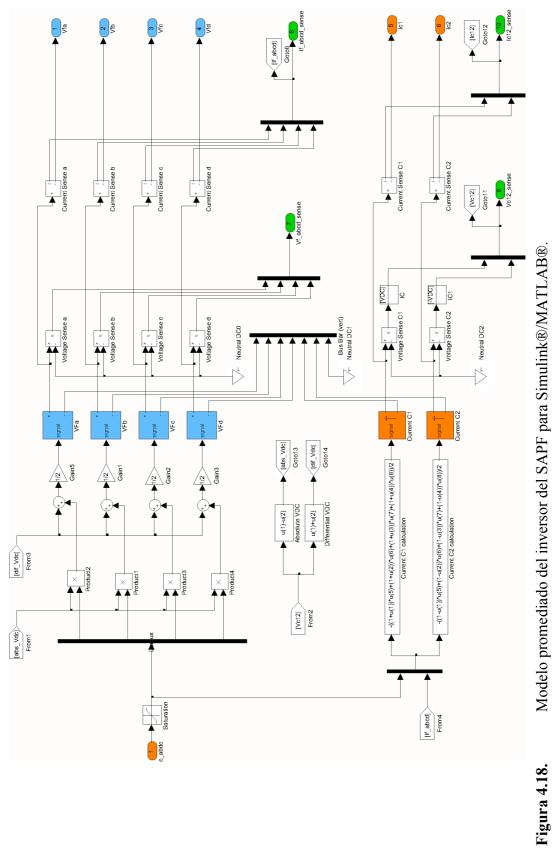

En esta última consideración, hay que destacar como particularidad que, en el caso del inversor FLFB, la inductancia de acoplo de la rama d es teóricamente nula, aunque en la práctica, se suele insertar una pequeña inductancia en esta del inversor con el objetivo de limitar las elevadas diferenciales de corriente que se pueden generar en la misma (ruidos) a consecuencia de la pequeña capacidad parásita de acoplamiento que existe entre el bus de continua y tierra. Estimándose que pudiera resultar de utilidad, en la Figura 4.18 se muestra la implementación del modelo inversor del SAPF para Simulink®/MATLAB®.

Modelo promediado del inversor del SAPF para Simulink®/MATLAB®.

Para obtener una expresión de la corriente que circula por los condensadores del bus de continua en función de términos con significado energético, basta con realizar el sumatorio de las ecuaciones mostradas en (4.12) para las diferentes ramas. De esta forma llega a:

$$i_{C1} = \frac{1}{v_{dc}} \left[ \left( v_{0n} + v_{C2} \right) \sum_{i=a,b,c,d} i_{Fi} - \sum_{i=a,b,c} v_{Si} i_{Fi} - L_F \sum_{i=a,b,c,d} \left( i_{Fi} i_{Fi} \right) \right], \tag{4.15a}$$

$$i_{C1} = \frac{1}{v_{dc}} \left[ -(v_{0n} + v_{C1}) \sum_{i=a,b,c,d} i_{Fi} + \sum_{i=a,b,c} v_{Si} i_{Fi} + L_F \sum_{i=a,b,c,d} (i_{Fi} \dot{i}_{Fi}) \right],$$

(4.15b)

donde:

$\sum_{i=a,b,c,d} i_{Fi} = i_{F0}$  es la corriente inyectada en el punto medio del bus;

$\sum_{i=a,b,c} v_{Si} i_{Fi} = p_{F3\phi}$  es la potencia activa instantánea desarrollada por el SAPF;

$L_F \sum_{i=a,b,c,d} (i_{Fi} \dot{i}_{Fi})$  es la potencia activa instantánea asociada a las inductancias de acoplo.

Además, teniendo en cuenta que, para todas las topologías de inversor mostradas en la Tabla 4.1, se cumple que, o  $v_{0n}$ =0, o  $i_{F0}$ =0, entonces las ecuaciones de (4.15) se pueden escribir como:

$$i_{C1} = \frac{1}{v_{dc}} \left[ v_{C2} i_{F0} - p_{F3\phi} - L_F \sum_{i=a,b,c,d} (i_{Fi} i_{Fi}) \right], \tag{4.16a}$$

$$i_{C2} = \frac{1}{v_{dc}} \left[ -v_{C1} i_{F0} + p_{F3\phi} + L_F \sum_{i=a,b,c,d} (i_{Fi} i_{Fi}) \right].$$

(4.16b)

Las ecuaciones mostradas en (4.16) constituirán la base del diseño de los controladores del SAPF. A partir de estas ecuaciones, en el Apartado 4.6 se realiza un estudio de la evolución de la tensión diferencial del bus de continua. Así mismo, en los Apartados 5.1 y 5.2 de este trabajo se realiza un estudio de la evolución de la tensión absoluta del bus de continua y de la energía almacenada en el mismo.

### 4.4.1. Control de la corriente inyectada en el modelo promediado

Partiendo de las ecuaciones (4.11) y (4.8), la corriente inyectada en red por una rama del inversor valdrá:

$$i_{Fi} = \frac{1}{L_F} \int (v_{Fi0} + v_{0n} - v_{Si}) dt = \frac{1}{L_F} \int \left[ \frac{1}{2} (c_i v_{dc} + \Delta v_{dc}) + v_{0n} - v_{Si} \right] dt .$$

(4.17)

En esta ecuación, se aprecia como la corriente inyectada por la rama no sólo depende de la variable de control del convertidor y de la tensión total del bus de continua, sino que también depende de la tensión diferencial de dicho bus, de la tensión de flotación del mismo, y de la tensión de red. Estas tres últimas variables actuarían como perturbaciones en el lazo de control de la corriente inyectada.

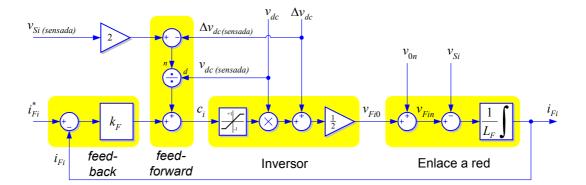

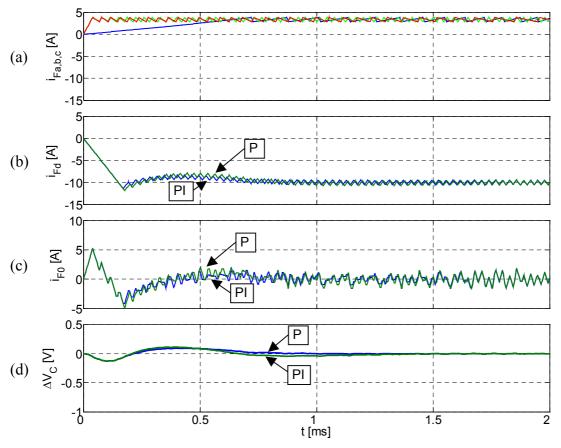

La Figura 4.19 muestra la estructura inicial del controlador lineal utilizado para regular la corriente inyectada por una rama genérica del inversor modelado anteriormente. En este diagrama de control, el bloque de tipo *feed-forward* es el encargado de eliminar el efecto perturbador producido por la tensión diferencial del bus de continua y por la tensión de red. De esta manera, se puede relajar la acción de control del bloque de tipo *feed-back*, el cual está constituido por un regulador proporcional con ganancia  $k_F$ . Así mismo, en el bloque referente al inversor, se ha insertado un limitador para respetar el rango de la variable de control,  $c_i \in [-1, 1]$ . Un análisis de este diagrama de control conduce a la siguiente función de transferencia:

$$I_{Fi}(s) = \frac{\frac{k_F}{2L_F} V_{dc}(s)}{s + \frac{k_F}{2L_F} V_{dc}(s)} I_{Fi}^*(s) + \frac{\frac{1}{L_F}}{s + \frac{k_F}{2L_F} V_{dc}(s)} V_{0n}(s).$$

(4.18)

**Figura 4.19.** Controlador lineal de la corriente inyectada por una rama.

La ecuación (4.18) evidencia como la tensión de flotación del bus de continua sigue actuando como una perturbación en el controlador de corriente. Evidentemente, en los inversores con conexión en el punto intermedio del bus de continua, TLSC y FLSC, la tensión de flotación del bus es nula, por lo que la citada perturbación no existe y el diagrama de control mostrado en la Figura 4.19 resulta perfectamente válido con  $v_{0n}$ =0. En los inversores en puente completo, TLFB y FLFB, el valor de la tensión de flotación del bus depende de la acción conjunta de sus ramas. En principio, y entendiendo que se habla de valores promediados de las variables, para una misma tensión de salida del inversor (tensión de salida de las ramas medida respecto al neutro de la red), la tensión de flotación del bus de continua podría adoptar infinitos valores. La selección de la tensión de flotación del bus de continua está relacionada con aspectos tales como son el aprovechamiento de la tensión de

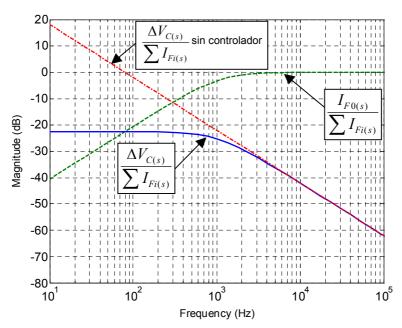

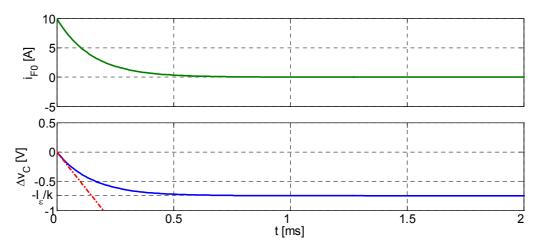

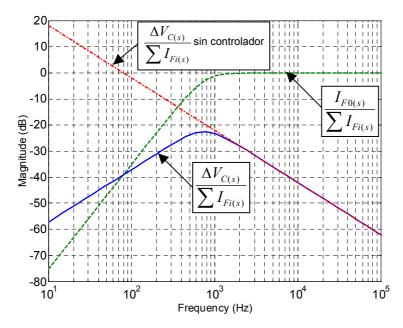

dicho bus, el rizado de la corriente inyectada y las pérdidas de conmutación en los transistores del inversor.