ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons:

ADVERTENCIA. El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons:

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

BY NC ND

# Efficient Data Management Strategies for Sequence Alignment on Heterogeneous Clusters

**Chen Shaolong**

Supervisor: Miquel Angel Senar Rosell

Department of Computer Architecture and Operating System Universidad Autònoma de Barcelona

> This dissertation is submitted for the degree of Doctor of Philosophy April 2019

Dedicate this thesis to my loving grandmother

•••

### Declaration

This dissertation is submitted by Chen Shaolong for the degree of Doctor of Philosophy at the Universidad Autònoma de Barcelona, under the supervision of Prof. Miquel Angel Senar Rosell, Computer Architecture and Operating System Department, PhD. in Computer Science. I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and acknowledgements.

> Chen Shaolong April 2019

### Acknowledgements

After an intensive period of four years in UAB, now is the day to write section acknowledgements to everyone is the finishing touch on my dissertation. This four years in Barcelona has been an unforgettable memory during my whole life, not only in the academic arena, but also on the personal level. I would like to reflect on the people who have supported and helped me so much throughout this period.

I first would like to acknowledge my advisor Miquel Angel Senar who helps me a lot for the last four years in UAB. He taught me much about how to analysis and solve problems, how to present your slides and do your research. His kindnesses and generosities help me not only shape my own perspective profoundly on research activities, but also on my personal life. He is a great person to cooperate with during the last four years.

I also would like to thank all the colleagues in CAOS of UAB. They are Josefina, Pilar, Liu Zhengchun, Cesar, Joe, Cecilia and so on. They show kindly heart and make me feel like living in my mother country. Special thanks to Pilar and Cecilia, their kindness helps me a lot.

I also would like to thank all the friends in Cerdanyola Del Valles. I lived in this small town for four years and never forget this impressive memory in life. Special thanks to my roommates, Lu Xiaoxue, Lv Jike, Liu Bin and Li Liang, they help me a lot and make me feel like living at home. Special thanks to my best friend in Barcelona and my cat, Pan Yu and Jaja, without them, I would feel lonely myself. Finally, I would like to thank my parents and girlfriend Fang, their patience, love and support are indispensable part for me. Without them, I can not complete this thesis . Special to my grandmother, you left me forever. I always miss you.

This research would not be possibly completed without the financial support of China Scholarship Council(CSC) under reference number 201406890007 and Spanish Project under contract TIN2014- 53234-C2-1-R. I am especially indebted to Na Yan and Prof.Li Hong, who work in Shanghai University and have been supportive of my grant goals during last four years. I am also especially appreciated to Gemma and Daniel in UAB, thanks for their great support and assistant in my academic time in UAB.

Thank you very much, everyone!

Chen, Shaolong

Barcelona, April, 2019.

### Abstract

Among the high performance computing systems, the Intel Xeon Phi is an accelerator that turns out to be a very attractive alternative to improve the performance of applications with intense computing needs that are traditionally executed in systems based on multicore servers. These applications can be migrated from a multicore server to an accelerator with a low coding effort because both systems are based on nuclei with the same basic architecture.

In our study, we focused our attention on BWA, one of the most popular sequence aligners, and we have analyzed different modes of execution of BWA in various heterogeneous computing systems that incorporate an accelerator.

The alignment of sequences is a fundamental phase in the analysis of genomic variants and has a high computational cost. Although its coding to run in a multicore system can be simple, achieving good performance is not easy in this type of systems, as our results show. We have developed and evaluated different strategies that have been applied on BWA and, of all of them, we conclude that the MDPR variant, which combines data parallelization and data replication, is the one that provides the best results in all systems evaluated. MDPR has a generic design that allows it to be used in different heterogeneous systems. On the one hand, we have applied it in a system consisting of a server with Intel Xeon multicore processors and a Xeon Phi accelerator. And, on the other hand, we have also evaluated it in other heterogeneous systems based on multicore servers equipped with AMD and Intel processors. In all these hardware configurations, we have tested two dynamic modes and one static mode of data distribution in MDPR. Our experimental results show that the best results for MDPR are obtained when the static mode of data distribution is applied. The dynamic strategy based on round robin achieves a similar performance without the off-line overhead incurred by the static mode. Although our proposal was applied to BWA using human genome data samples, this strategy can be easily applied to other sequence data and other alignment tools that have operating principles similar to those of the BWA aligner.

#### Resumen

Entre los sistemas de computación de alto rendimiento, el Intel Xeon Phi es un acelerador que resulta ser una alternativa muy atractiva para mejorar el rendimiento de aplicaciones con necesidades de cómputo intensas que tradicionalmente se ejecutan en sistemas basados en servidores multinúcleo. Esas aplicaciones se pueden migrar de un servidor multinúcleo a un acelerador con un bajo esfuerzo de codificación porque ambos sistemas se basan en núcleos con una misma arquitectura básica.

En nuestro estudio, centramos nuestra atención en BWA, uno de los alineadores de secuencia más populares, y hemos analizado diferentes modos de ejecución de BWA en varios sistemas informáticos heterogéneos que incorporan un acelerador.

La alineación de secuencias es una fase fundamental en el análisis de variantes genómicas y tiene un alto coste computacional. Aunque su codificación para ejecutarse en un sistema de múltiples núcleos puede ser simple, lograr un buen rendimiento no es fácil en este tipo de sistemas, como muestran nuestros resultados. Hemos desarrollado y evaluado diferentes estrategias que se han aplicado en BWA y, de todas ellas, llegamos a la conclusión de que la variante MDPR, que combina la paralelización de datos y la replicación de datos, es la que proporciona los mejores resultados en todos los sistemas evaluados. MDPR tiene un diseño genérico que permite su uso en diferentes sistemas heterogéneos. Por un lado, lo hemos aplicado en un sistema que consta de un servidor con procesadores multinúcleo Intel Xeon y un acelerador Xeon Phi. Y, por otro lado, también lo hemos evaluado en otros sistemas heterogéneos basados en servidores multinúcleo equipados con procesadores AMD e Intel.

En todas estas configuraciones de hardware, hemos probado dos modos dinámicos y un modo estático de distribución de datos en MDPR. Nuestros resultados experimentales muestran que los mejores resultados para MDPR se obtienen cuando se aplica el modo estático de distribución de datos. La estrategia dinámica basada en round robin logra un rendimiento similar sin el sobrecoste inicial que requiere el modo estático. Aunque nuestra propuesta se aplicó a BWA utilizando muestras de datos del genoma humano, esta estrategia se puede aplicar fácilmente a otros datos de secuencia y a otras herramientas de alineación que tienen principios operativos similares a los del alineador BWA.

#### Resum

Entre els sistemes de computació d'alt rendiment, l'Intel Xeon Phi és un acelerador que resulta ser una alternativa molt atractiva per millorar el rendiment d'aplicacions amb necessitats de còmput intensiu que s'executen tradicionalment en sistemes basats en servidors multinucli. Aquestes aplicacions es poden migrar d'un servidor multinucli a un accelerador amb un esforç de codificació baix perquè tots dos sistemes es basen en una mateixa arquitectura bàsica.

En el nostre estudi, centrem la nostra atenció en BWA, un dels alineadors de seqüència més populars, i hem analitzat diferents modes d'execució de BWA en diversos sistemes de computació heterogenis que incorporen un accelerador.

L'alineació de seqüències és una fase fonamental en l'anàlisi de les variants genòmiques i té un cost computacional alt. Encara que la seva codificació per executar-se en un sistema de múltiples nuclis pot ser senzilla, aconseguir un bin rendiment en aquest tipus de sistemes no és fàcil, com mostren els nostres resultats. Hem desenvolupat i avaluat diferents estratègies que s'han aplicat a BWA i, de totes, arribem a la conclusió que la variant MDPR, que combina la paral·lelització de dades i la replicació de dades, ésla que aconsegueix els millors resultats en tots sistemes avaluats. MDPR té un disseny genèric que permet el seu ús en diferents sistemes heterogenis. Per un costat, l'hem aplicat en un sistema que consta d'un servidor amb processadors multinucli Intel Xeon i un accelerador Xeon Phi. I, per un altre costat, també l'hem avaluada en altres sistemes heterogènics basats en servidors multinucli equipats amb processadors AMD i Intel.

En totes aquestes configuracions de maquinari, hem provat dos modes dinàmics de distribució de dades en MDPR i un d'estàtic. Els nostres resultats experimentals mostren que els millors resultats per a MDPR s'obtennen quan s'aplica el mode de distribució de dades estàtic. L'estratègia dinàmica obté resultats similars sense el sobrecost inicial del model estàtic. Encara que la nostra proposta s'hagi aplicat a BWA utilitzant mostres de dades del

genoma humà, aquesta estratègia es pot aplicar fàcilment amb altres dades de seqüències i altres eines d'avanç que tinguin principis operatius semblants als de l'algorisme BWA.

## **Table of contents**

List of figures

| List of tables |       |         |                         |   |

|----------------|-------|---------|-------------------------|---|

| 1              | Intro | oductio | n                       | 1 |

|                | 1.1   | Backgı  | round                   | 1 |

|                |       | 1.1.1   | Genome Data Booming     | 1 |

|                |       | 1.1.2   | HPC Hardware Limitation | 3 |

|                |       |         |                         |   |

xxi

1

1

|   |       | 1.1.1 Genome Data Booming                                               | 1  |

|---|-------|-------------------------------------------------------------------------|----|

|   |       | 1.1.2 HPC Hardware Limitation                                           | 3  |

|   |       | 1.1.3 Sequence Alignment                                                | 6  |

|   | 1.2   | Motivation                                                              | 7  |

|   | 1.3   | Objective                                                               | 11 |

|   | 1.4   | Contribution                                                            | 12 |

|   | 1.5   | Outline                                                                 | 14 |

| 2 | I ito | rature Review on Related Works                                          | 17 |

| 4 | Litte | Tature Review on Related Works                                          | 1/ |

|   | 2.1   | Performance Improvement of Sequence Aligner in the Heterogeneous System | 18 |

|   | 2.2   | Performance Improvement on BWA Aligner                                  | 19 |

| 3 | Vari | ant Analysis                                 | 23 |

|---|------|----------------------------------------------|----|

|   | 3.1  | Overview                                     | 23 |

|   | 3.2  | Sequence Alignment                           | 27 |

|   |      | 3.2.1 Overview                               | 27 |

|   |      | 3.2.2 Short Read Alignment                   | 28 |

|   |      | 3.2.3 Existing Aligner                       | 29 |

|   | 3.3  | Burrows-Wheeler Aligner: BWA                 | 32 |

|   |      | 3.3.1 Introduction                           | 32 |

|   |      | 3.3.2 Performance Analysis                   | 34 |

|   |      | 3.3.3 Conclusion                             | 40 |

|   | 3.4  | Variant Calling                              | 41 |

|   | 3.5  | Variant Annotation                           | 42 |

| 4 | Hete | erogeneous Multicore-Manycore Architecture   | 43 |

|   | 4.1  | Multicore System: AMD Opteron and Intel Xeon | 43 |

|   |      | 4.1.1 Architecture                           | 43 |

|   |      | 4.1.2 NUMA effect                            | 45 |

|   | 4.2  | Manycore System: Intel Xeon Phi              | 48 |

|   |      | 4.2.1 Architecture                           | 48 |

|   |      | 4.2.2 Basic Execution Mode                   | 50 |

|   | 4.3  | Thread Parallelism Library                   | 52 |

|   |      | 4.3.1   | Pthread                                                           | 52 |

|---|------|---------|-------------------------------------------------------------------|----|

|   |      | 4.3.2   | OpenMP                                                            | 53 |

|   |      | 4.3.3   | Intel Cilk                                                        | 54 |

| 5 | Data | Manag   | gement Strategies Based on Data Parallelization and Data Replica- |    |

|   | tion |         |                                                                   | 57 |

|   | 5.1  | Overvi  | ew                                                                | 58 |

|   | 5.2  | Data M  | lanagement on Homogeneous Architecture: DP, DR and DPR Strategies | 60 |

|   |      | 5.2.1   | Analysis of Sequence Alignment Procedure                          | 60 |

|   |      | 5.2.2   | DP, DR and DPR Strategies                                         | 62 |

|   | 5.3  | Data M  | Ianagement on Heterogeneous Architecture: MDPR Strategy           | 65 |

|   |      | 5.3.1   | MDPR Strategy                                                     | 65 |

|   |      | 5.3.2   | Static Distribution                                               | 66 |

|   |      | 5.3.3   | Even Distribution                                                 | 67 |

|   |      | 5.3.4   | Round-robin Distribution                                          | 68 |

| 6 | Expe | eriment | al Implementation and Environment                                 | 71 |

|   | 6.1  | Sample  | e Dataset                                                         | 71 |

|   | 6.2  | Implen  | nentation System                                                  | 72 |

|   | 6.3  | Related | l Software                                                        | 74 |

|   |      | 6.3.1   | BWA-ALN-Xeon-Phi                                                  | 74 |

|   |      | 6.3.2   | mBWA                                                              | 75 |

|   |      | 6.3.3                                   | pBWA                                                     | 77  |

|---|------|-----------------------------------------|----------------------------------------------------------|-----|

|   |      | 6.3.4                                   | Intel VTune Amplifier                                    | 78  |

| 7 | Exp  | eriment                                 | tal Results and Evaluation                               | 81  |

|   | 7.1  | Evalua                                  | tion of Parallelism on Basic Execution Modes             | 82  |

|   |      | 7.1.1                                   | Implementation                                           | 82  |

|   |      | 7.1.2                                   | Performance Analysis                                     | 83  |

|   | 7.2  | Thread                                  | Parallelism Evaluation: Pthread, Intel Cilk and OpenMP   | 85  |

|   |      | 7.2.1                                   | Implementation                                           | 85  |

|   |      | 7.2.2                                   | Performance Analysis                                     | 86  |

|   | 7.3  | Scalab                                  | ility Evaluation of DP, DR and DPR                       | 91  |

|   |      | 7.3.1                                   | Implementation                                           | 91  |

|   |      | 7.3.2                                   | Performance Analysis                                     | 91  |

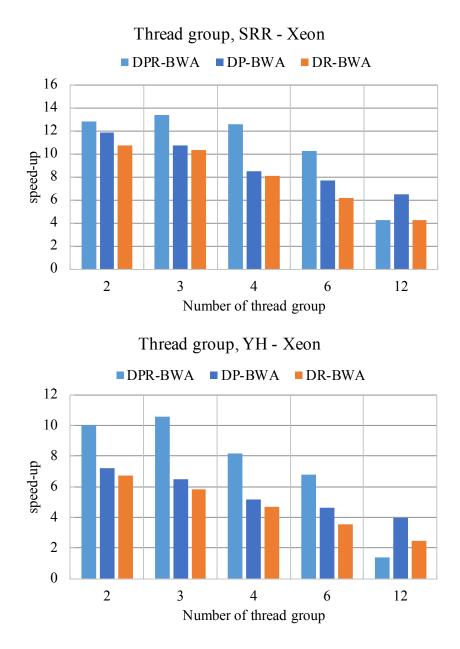

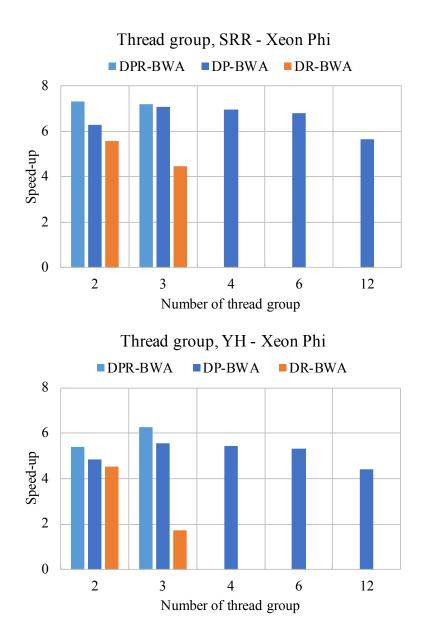

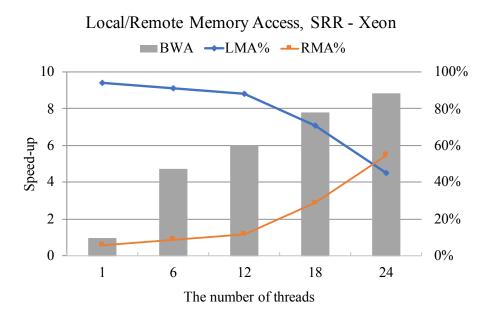

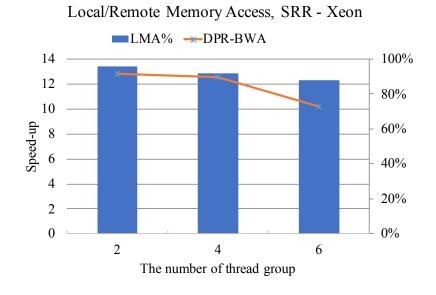

|   | 7.4  | Analys                                  | sis of Thread Groups and Data Replicas in DP, DR and DPR | 94  |

|   |      | 7.4.1                                   | Implementation                                           | 94  |

|   |      | 7.4.2                                   | Performance Analysis                                     | 95  |

|   | 7.5  | Perform                                 | mance Evaluation of MDPR                                 | 100 |

|   |      | 7.5.1                                   | Implementation                                           | 100 |

|   |      | 7.5.2                                   | Performance Analysis                                     | 101 |

| 8 | Disc | ussion a                                | and Conclusion                                           | 107 |

|   | 8.1  | Conch                                   | usion                                                    | 107 |

|   |      | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |                                                          |     |

| 8.2 | Future Work          | 111 |

|-----|----------------------|-----|

| 8.3 | List of Publications | 113 |

#### References

115

# List of figures

| Growth of NCBI DNA sequence data and user amount in 24 years, from         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1989 to 2013                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The cost of sequencing a human genome vs Moore's law in HPC hardware .     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Evolution of the number of cores per processor from TOP500 supercomputer   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| list, from June 2006 to 2015                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Typical performance curves of pure MPI and hybrid MPI+OpenMP               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

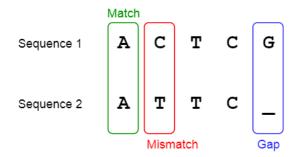

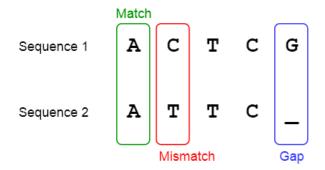

| A simple example of sequence alignment                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

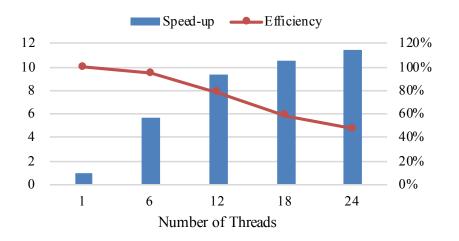

| BWA scalability on 24-thread system of Intel Xeon. Speed-up and efficiency |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| are measured according to the value of 1-thread BWA aligner. Speed-up is   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| illustrated at the left y-axis and efficiency at the right y-axis          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

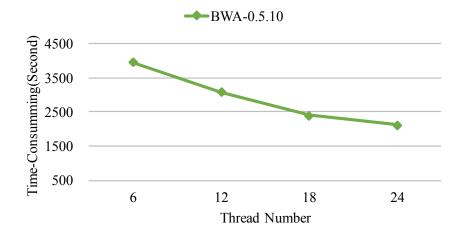

| BWA scalability on 2-socket 12-core 24-thread system of Intel Xeon         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

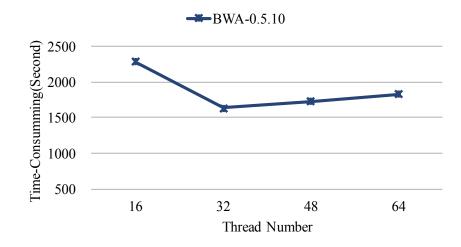

| BWA scalability on 4-socket 32-core 64-thread system of Intel Xeon         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The molecular structure of DNA, four types of nitrogen-containing nucle-   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| obases: Adenine[A], Thymine[T], Guanine[G] and Cytosine[C], two base       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| pairings(A-T, C-G)                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                            | 1989 to 2013The cost of sequencing a human genome vs Moore's law in HPC hardware .Evolution of the number of cores per processor from TOP500 supercomputerlist, from June 2006 to 2015Typical performance curves of pure MPI and hybrid MPI+OpenMPA simple example of sequence alignmentBWA scalability on 24-thread system of Intel Xeon. Speed-up and efficiencyare measured according to the value of 1-thread BWA aligner. Speed-up isillustrated at the left y-axis and efficiency at the right y-axis.BWA scalability on 2-socket 12-core 24-thread system of Intel XeonBWA scalability on 4-socket 32-core 64-thread system of Intel XeonThe molecular structure of DNA, four types of nitrogen-containing nucleobases: Adenine[A], Thymine[T], Guanine[G] and Cytosine[C], two base |

| 3.2  | Basic workflow of variant analysis for genome sequencing. Quality assess-   |    |

|------|-----------------------------------------------------------------------------|----|

|      | ment, read alignment, variant identification and variant annotation are the |    |

|      | four crucial steps of all.                                                  | 25 |

| 3.3  | The cost of sequencing a human genome over years                            | 26 |

| 3.4  | Three crucial workflows in the variant analysis for genome sequencing       | 27 |

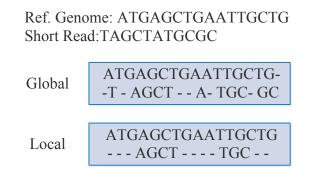

| 3.5  | Example of pairwise sequence alignment                                      | 29 |

| 3.6  | Two types of pairwise sequence alignment                                    | 30 |

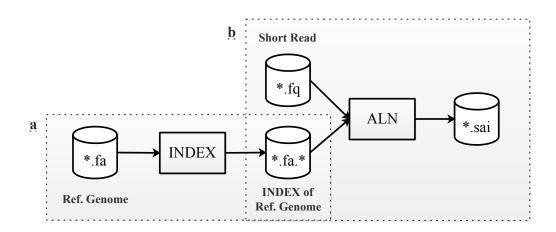

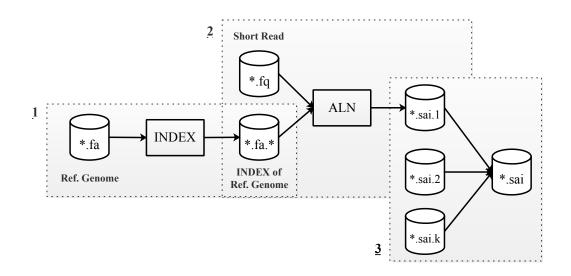

| 3.7  | Two flows of BWA-backtrack. a. Building the BWT index against the           |    |

|      | reference genome. b. Alignment of short read against the reference genome   |    |

|      | using BWA-backtrack module                                                  | 34 |

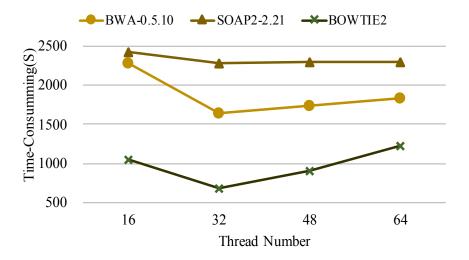

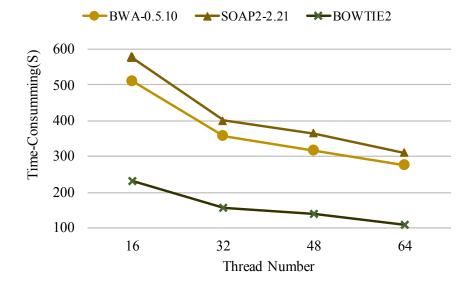

| 3.8  | Scalability on 2-socket 2-NUMA 24-thread system, genome Data 17.6GB .       | 35 |

| 3.9  | Scalability on 4-socket 4-NUMA 64-thread system, genome Data 17.6GB .       | 36 |

| 3.10 | Scalability on 4-socket 4-NUMA 64-thread system, genome Data 4.3GB          | 36 |

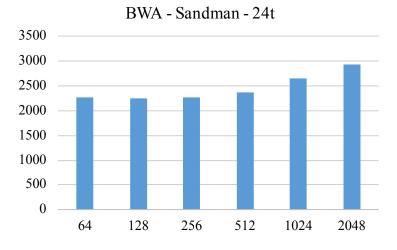

| 3.11 | The increasing batch size in Sandman with 24 threads                        | 39 |

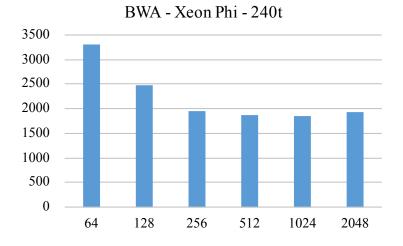

| 3.12 | The increasing batch size in Sandman-Xeon Phi with 240 threads              | 39 |

| 3.13 | The example of variant calling or variant identification                    | 41 |

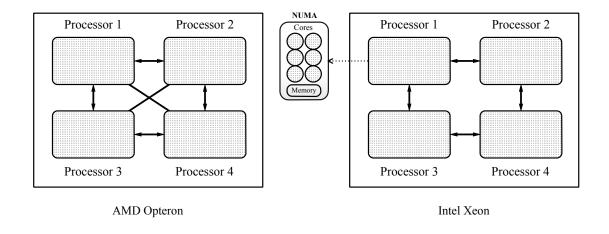

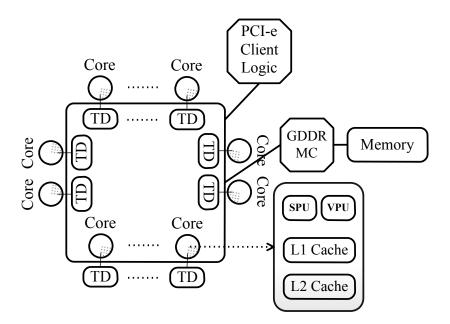

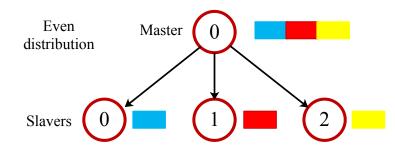

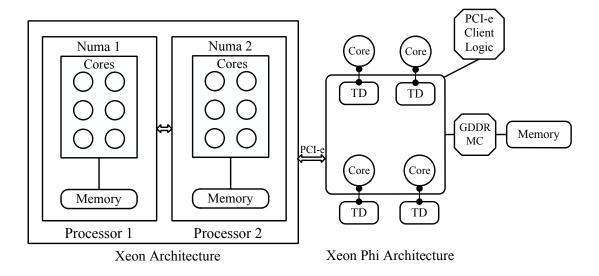

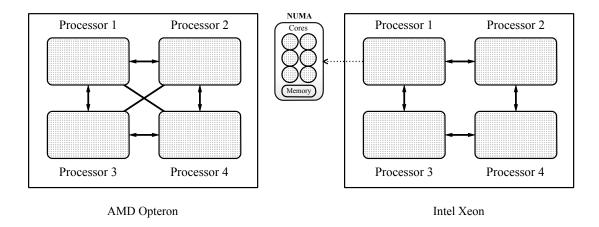

| 4.1  | Multicore architecture: AMD Opteron and Intel Xeon                          | 44 |

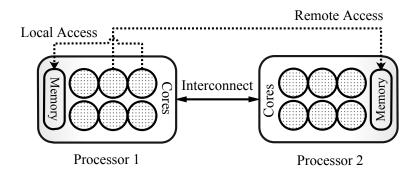

| 4.2  | Memory access in NUMA nodes                                                 | 46 |

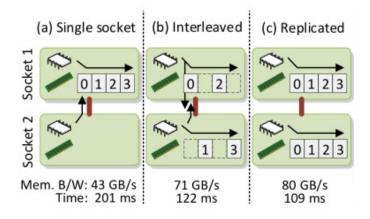

| 4.3  | Parallel summation of an array on a 2-socket 2-NUMA node with different     |    |

|      | memory policies                                                             | 47 |

| 4.4  | Intel Xeon Phi coprocessor chip architecture                                | 48 |

| 4.5  | Intel Xeon processor and Intel Xeon Phi coprocessor system                  | 50 |

| 4.6 | Three basic execution modes on the heterogeneous system of Intel Xeon and      |    |

|-----|--------------------------------------------------------------------------------|----|

|     | Intel Xeon Phi                                                                 | 51 |

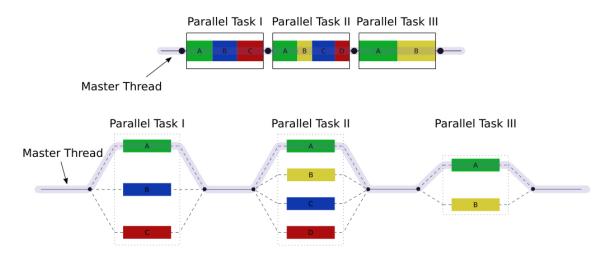

| 4.7 | The fork-join parallel flow                                                    | 53 |

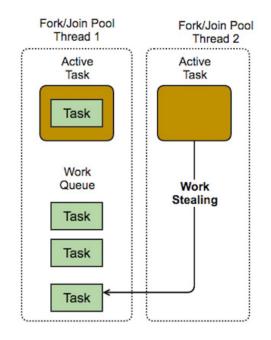

| 4.8 | An example of work-stealing mechanism                                          | 55 |

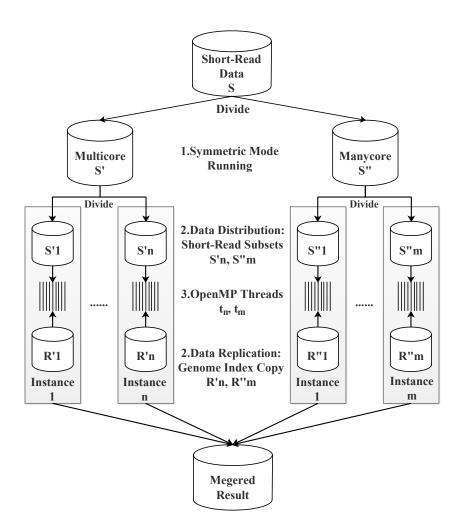

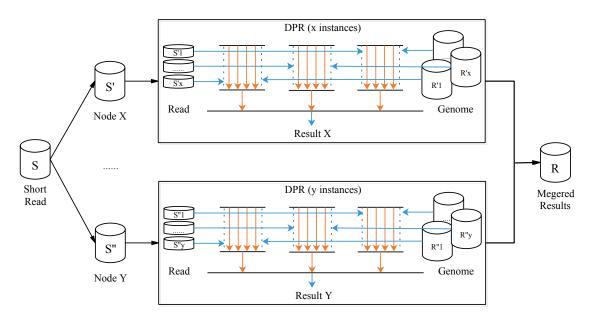

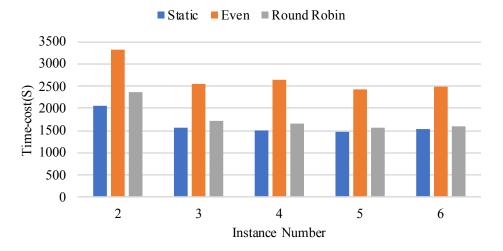

| 5.1 | MDPR-BWA implementation procedure in the case of n and m instances are         |    |

|     | applied in multicore and manycore parts (Intel Xeon + Xeon Phi), respectively. | 59 |

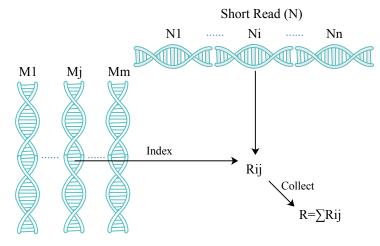

| 5.2 | Sequence alignment procedure                                                   | 61 |

| 5.3 | Three main phases in the process of sequence alignment                         | 62 |

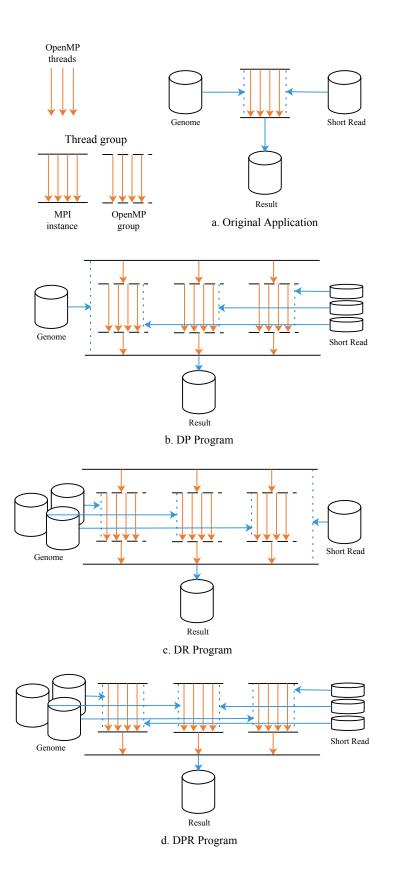

| 5.4 | Implementation of DP, DR and DPR                                               | 64 |

| 5.5 | MDPR strategy with the case of x and y instances are implemented in node       |    |

|     | X and Y, respectively                                                          | 65 |

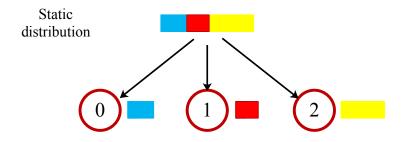

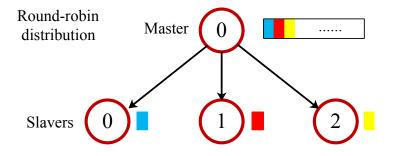

| 5.6 | An example of static distribution in MDPR strategy                             | 67 |

| 5.7 | An example of even distribution in MDPR strategy                               | 67 |

| 5.8 | An example of round-robin distribution in MDPR strategy                        | 68 |

| 6.1 | The system of S1, Intel Xeon + Intel Xeon Phi                                  | 73 |

| 6.2 | The system of S2, AMD Opteron + Intel Xeon                                     | 73 |

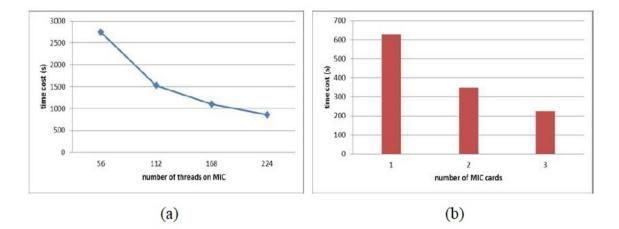

| 6.3 | Effectiveness of MIC. (a) Scalability of mBWA on Intel Xeon Phi. (b)           |    |

|     | Performance of mBWA under different number of Intel Xeon Phi                   | 76 |

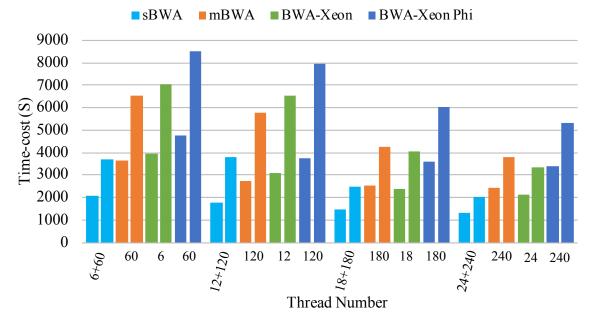

| 7.1 | Scalability of BWA aligners (identical color in short column: the results from |    |

|     | dataset SRR, and long column: the results from dataset YH)                     | 83 |

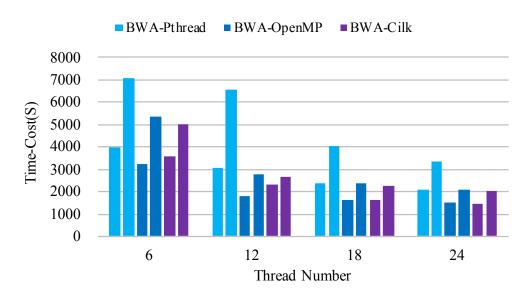

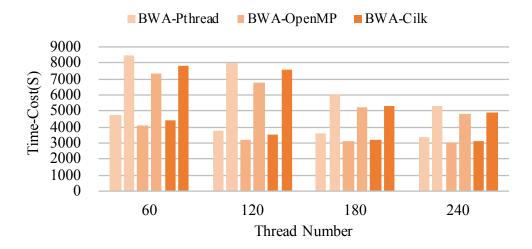

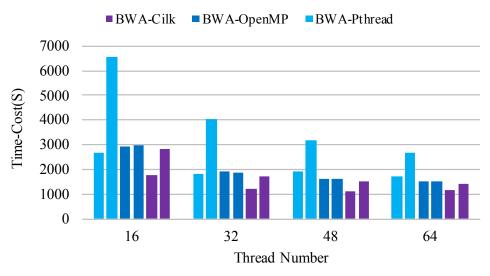

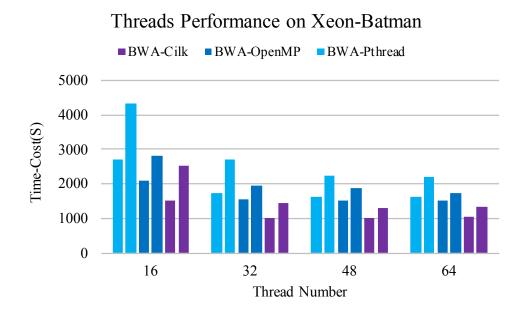

| 7.2  | Thread scalability in the Intel Xeon (Sandman). Identical color in short                                                                                                 |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | column: the results from dataset SRR, and long column: the results from dataset YH                                                                                       | 86 |

| 7.3  | Thread scalability in the Intel Xeon Phi (Sandman-Xeon Phi). Identical color in short column: the results from dataset SRR, and long column: the results from dataset YH | 87 |

| 7.4  | Thread scalability in the 4-socket Intel Xeon Phi (Penguin). Identical color in short column: the results from dataset SRR, and long column: the results from dataset YH | 88 |

| 7.5  | Thread scalability in the AMD Opteron (Batman). Identical color in short column: the results from dataset SRR, and long column: the results from dataset YH              | 88 |

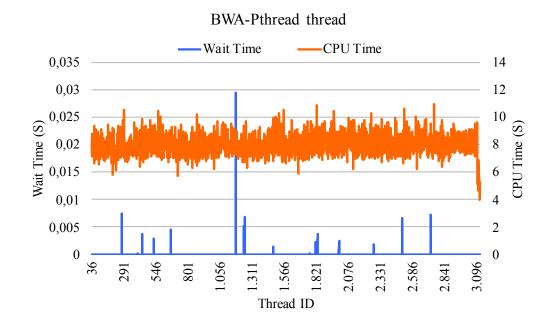

| 7.6  | Thread performance of BWA-Pthread in the Intel Xeon(Sandman) with dataset SRR by VTune                                                                                   | 89 |

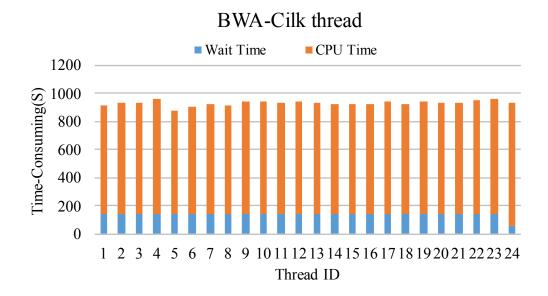

| 7.7  | Thread performance of BWA-Cilk in the Intel Xeon(Sandman) with dataset SRR by VTune                                                                                      | 89 |

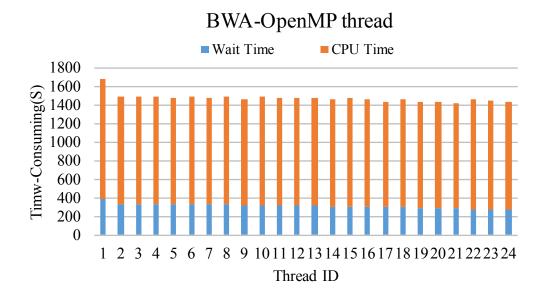

| 7.8  | Thread performance of BWA-OpenMP on the Intel Xeon(Sandman) with dataset SRR by VTune                                                                                    | 90 |

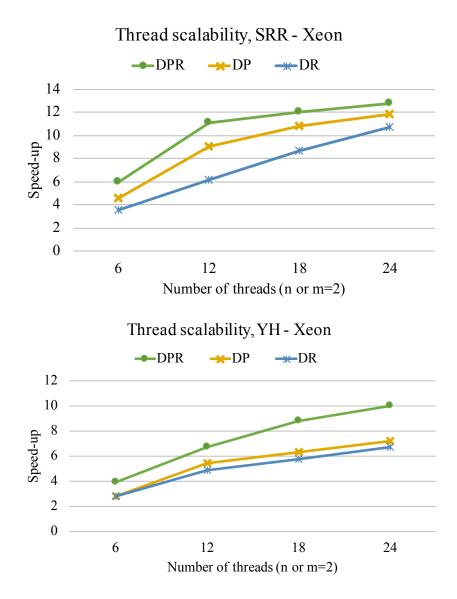

| 7.9  | DP, DR and DPR scalability comparison on Sandman                                                                                                                         | 92 |

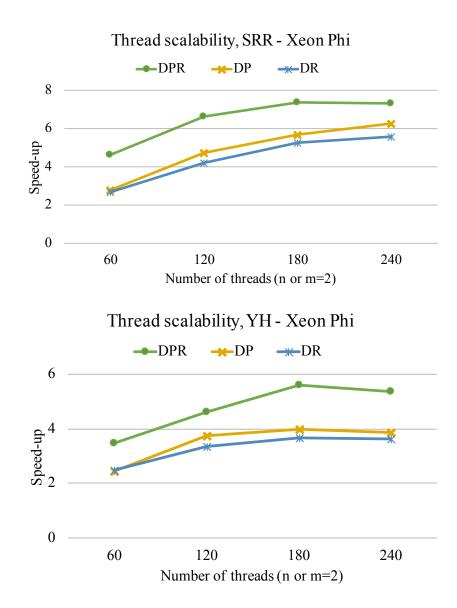

| 7.10 | DP, DR and DPR scalability comparison on Sandman-Xeon Phi                                                                                                                | 93 |

| 7.11 | DP, DR and DPR performance comparison on Sandman                                                                                                                         | 96 |

| 7.12 | DP, DR and DPR performance comparison on Sandman-Xeon Phi                                                                                                                | 97 |

| 7.13 | BWA Memory Access                                                                                                                                                        | 98 |

| 7.14 | DPR-BWA Memory Access                                                                                                                                                    | 99 |

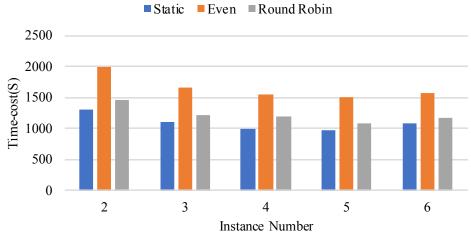

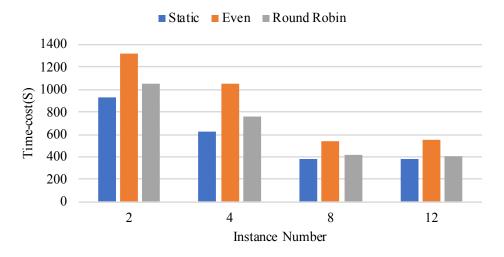

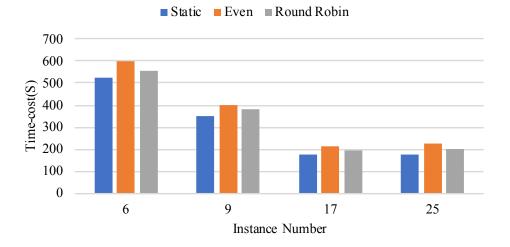

| 7.15 | Static, even and round-robin schedule distribution of MDPR strategy, perfor-       |     |

|------|------------------------------------------------------------------------------------|-----|

|      | mance comparison on the Intel Xeon and Xeon $Phi(S1)$                              | 102 |

| 7.16 | Static, even and round-robin schedule distribution of MDPR strategy, perfor-       |     |

|      | mance comparison on the Intel and AMD NUMA nodes(S2) $\ldots \ldots \ldots$        | 103 |

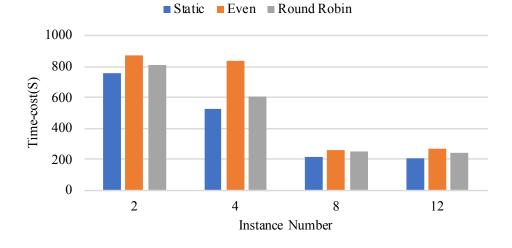

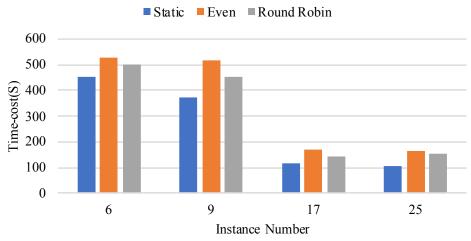

| 7.17 | Static, even and round-robin schedule distribution of MDPR strategy, perfor-       |     |

|      | mance comparison on multiple nodes(S3) $\ldots \ldots \ldots \ldots \ldots \ldots$ | 104 |

### List of tables

| 4.1 | AMD Opteron processor distance                                                                                                                                                                                                                                                                                                                                                          | 44  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | Intel Xeon processor distance                                                                                                                                                                                                                                                                                                                                                           | 45  |

| 6.1 | Experiment dataset                                                                                                                                                                                                                                                                                                                                                                      | 72  |

| 6.2 | Experiment system                                                                                                                                                                                                                                                                                                                                                                       | 74  |

| 6.3 | pBWA executed with 350 million paired 50 bp reads. T, the number of threads; P, the number of processors; Time-used for running aln for each of the pair read file. Efficiency calculated based on the combined time in minutes (m) or seconds (s) of aln and sampe commands, and is calculated as Speedup divided by the number of threads or processors or the combined total threads | 78  |

| 7.1 | BWA aligner versions on basic execution mode                                                                                                                                                                                                                                                                                                                                            | 82  |

| 8.1 | BWA Performance Summary on Intel Xeon                                                                                                                                                                                                                                                                                                                                                   | 108 |

| 8.2 | BWA Performance Summary on Intel Xeon Phi                                                                                                                                                                                                                                                                                                                                               | 108 |

| 8.3 | BWA Performance Summary on S1                                                                                                                                                                                                                                                                                                                                                           | 109 |

| 8.4 | BWA Performance Summary on S2 and S3                                                                                                                                                                                                                                                                                                                                                    | 109 |

### Chapter 1

### Introduction

### 1.1 Background

### **1.1.1 Genome Data Booming**

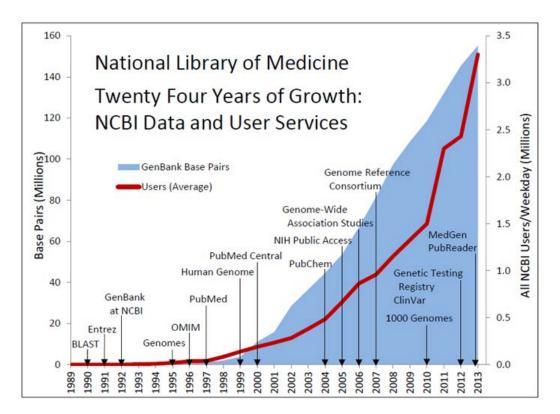

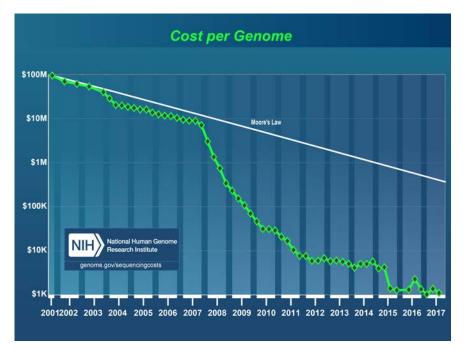

Nowadays, the amount of sequence data has explosively increased from the GB level to the TB level as the computation cost decreases from 10 million in 2007 to 1000 in 2017 [1]. Figure 1.1 shows the growth of DNA sequence data in Genbank and its user amount in last 24 years(1989-2013) [2]. GenBank is the world's largest annotated collection of publicly available DNA sequences. Genome sequence data and biological users are increasing rapidly with the emerging the next generation sequence technology.

Fig. 1.1 Growth of NCBI DNA sequence data and user amount in 24 years, from 1989 to 2013

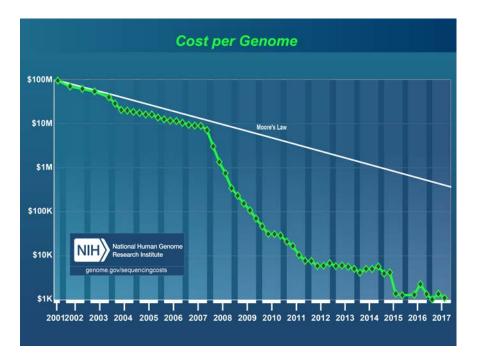

The decreasing costs of sequencing drives DNA research developing rapidly. As shown in Figure 1.2 that illustrates the costs per genome based the U.S [3]. National Institute of Health, with the NGS technology burgeoning, sequencing a human genome has decreased in cost from \$100 million in 2001 to \$1000 in 2017, which leads to an explosive increasing of sequence data from the GB level to the TB level. While the amount of genome data is doubling every 12 months, computing power of a single processor is only doubling every 18 months. Which means that biology's big data sets are being generated faster than improvements in storage and processing of computing technology. Therefore, new advances in software tools are needed to handle this challenge by efficiently exploiting technological features presented in modern parallel architectures.

Fig. 1.2 The cost of sequencing a human genome vs Moore's law in HPC hardware

#### **1.1.2 HPC Hardware Limitation**

In recent years, heterogeneous systems consisting of different architectures have become a significant trend in the high performance computing(HPC) arena [4]. GPUs have obtained a significant popularity despite the difficulty associated with the usage of specific programming languages such as OpenCL or CUDA [5]. Intel Xeon Phi, which is based on a common architecture x86 and provides 57 to 61 cores on one board, is an attractive solution that can easily transform programs written in the same language used on multicore CPU architectures [6], without requiring the complexity of porting processes.

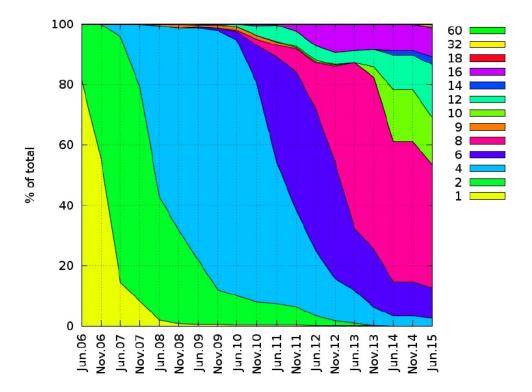

Figure 1.3 displays evolution of the number of cores for per processor in TOP 500 supercomputer list [7]. Obviously, the processing units integrated in such systems tend to provide more parallelism in processors year by year. Moreover, manycore integrate in one coprocessor such as Intel Xeon Phi and GPUs, has been paid growing up attention nowadays. Manycore architectures, such as GPUs, have obtained considerable popularity, despite the fact that the specific programming languages such as OpenCL and CUDA requiring significant coding skills [5]. Intel Xeon Phi [6] is another manycore coprocessor, which has became an

attractive solution that existing programs on multicore systems can be easily ported because Xeon Phi is also based on the same x86 architecture.

Fig. 1.3 Evolution of the number of cores per processor from TOP500 supercomputer list, from June 2006 to 2015

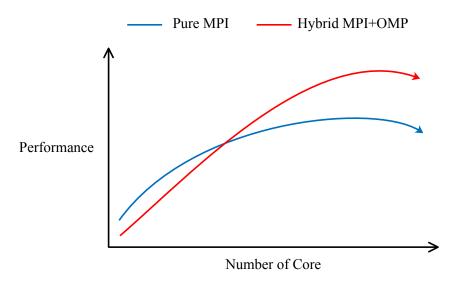

For the sake of better utilization of heterogeneous cluster, it is common now that application programs apply hybrid MPI and OpenMP programming on the HPC systems [8], as shown in Figure 1.4. Three significant motivations for this hybrid programming model, one is that the reduction of memory consumption, one is that performance improvement at high core counts, another is that we could utilize the heterogeneous architecture under the shared and distributed memory level.

In term of reduction of memory footprint, the reason is that designing and implementing MPI applications generally requires that some same data be replicated among MPI processes, while OpenMP is based on the shared data access. Additional, modern HPC system always owns a limited hardware resource, especially a small size in memory bank. Typically only 1

Fig. 1.4 Typical performance curves of pure MPI and hybrid MPI+OpenMP

or 2 GB memory per core. Thus, comparing to pure MPI execution, hybrid MPI and OpenMP programming consumes less memory footprint, comparing to pure OpenMP execution, hybrid MPI and OpenMP programming improves the efficiency of utilization of memory.

In term of performance improvement, when low core counts are applied, overheads between MPI and OpenMP make the performance of the pure MPI achieve better than that of hybrid MPI and OpenMP. On the contrary, when at high core counts, hybrid MPI and OpenMP would outperform pure MPI and pure OpenMP, due to the exploiting additional parallelism in OpenMP or MPI. Ultimately, in term of memory architecture, hybrid MPI and OpenMP programming mode give us a better utilization of the shared and distributed memory level, to reduce communication overheads, load imbalance and memory access costs, especially in our NUMA architecture, which is a local shared memory among local cores.

#### 1.1.3 Sequence Alignment

Compared to computing evolution (doubling the number of transistors every 18 months), the amount of sequence genome data only doubles every 12 months [9]. This spectacular growth of genome data constitutes an important challenge that requires efficient applications to process them.

Fig. 1.5 A simple example of sequence alignment

Sequence alignment, variant calling and variant annotation comprises three fundamental operations in genome data studies [10]. Sequence alignment is a crucial step that can provide primary consequences for the other two remaining procedures. Sequence alignment involves mapping short reads to a genome sequence reference as accurately as possible [11].

Figure 1.5 displays a simple example of sequence alignment process which allows mismatch and gap in the algorithm of alignment. Each aligner owns its algorithm to calculate distance between short read and genome reference. In this case, we mapped two sequences according to best score in algorithm and posit ACTCG and ATTC-. Mismatch is allowed in the second positon and gap in the last position. This result could be useful for next workflows in sequence variant analysis.

Although many aligners have been developed in recent years, such as MAQ, SOAP and BLAST, they all exhibit a significant execution time and a large memory footprint. BWA aligner is one of the most prevalent and widespread sequence alignment tool available. As many existing mappers, BWA takes advantage of parallelization techniques in order to reduce

the computational demands involved in the alignment of millions of reads. Although, its execution time is similar to other existing aligners, BWA (Burrows-Wheeler Aligner) [12] takes advantage of the BWT indexing technique that decreases the memory requirements of the alignment process. This reduction in memory needs combined with its mapping accuracy have made BWA one of the most popular aligners in the scientific community.

However, BWA exhibits significant scalability problems when it is run on systems with large number of cores. Similar scalability problems are observed on manycore architectures, such as the Intel Xeon Phi, or in hybrid architectures combining both multicore CPUs and manycore accelerators. These behaviors were also observed in our experiment in the following section.

### **1.2** Motivation

Genome data is booming with the development of next generation sequence technology, high performance computer hardware can not achieve the speed of genome data, which limits the performance improvement of sequence aligners. All factors indicts that more efficient software is needed in variant analysis in the high performance computing arena.

As shown in Figure 1.6, we choose the widespread and popular sequence alignment application, BWA aligner, to evaluate its performance. We set up a base point which implements BWA aligner on Intel Xeon under one thread. Speed-up is measured on that base point. Original BWA aligner only can be executed on Xeon platform(Sandman) without revision. With applying 24 threads, as Figure 1.6 illustrates, it achieves the highest performance, 11.5-fold speed-up under the execution of Intel Xeon. The tendency of speed-up varies from linear to very smooth and approaches its performance pole under 24 threads, but its thread efficiency decreases to 48%. It's finite to enhance the performance of BWA aligner by increasing the number of working threads, we are demanded to further research in a more efficient way.

Fig. 1.6 BWA scalability on 24-thread system of Intel Xeon. Speed-up and efficiency are measured according to the value of 1-thread BWA aligner. Speed-up is illustrated at the left y-axis and efficiency at the right y-axis.

In order to demonstrate our motivation clearly, we illustrate a result of our experiments in advance. The addition of multi-threading to an aligner does not guarantee it will utilize threads efficiently. In fact, it is quite common to observe that efficiency decreases when the thread count grows large enough.

Fig. 1.7 BWA scalability on 2-socket 12-core 24-thread system of Intel Xeon

Fig. 1.8 BWA scalability on 4-socket 32-core 64-thread system of Intel Xeon

This phenomenon is observed and shown in Figures 1.7 and 1.8. These figures illustrate the results obtained by BWA aligner when mapping a large short-read genome example of 17.4GB against human genome reference. Each figure illustrates the results obtained when BWA aligner was executed on two different servers. Both systems are based on NUMA architectures but they differ in the total number of processors and cores available. The first system (Fig.1.7) owns two-socket Intel Xeon CPU with 12 cores. Twenty-four threads can be executed simultaneously using Hyper Thread technology. The second system (Fig.1.8) is a 4-socket Intel Xeon CPU. Each socket contains 8-core processor, so the total number of cores is 32 and 64 threads can be executed simultaneously. In both cases, each socket is connected with a memory bank, which constitutes a NUMA node. NUMA nodes are connected by QuickPath Interconnect links.

Interesting results occur in the experiments. When BWA runs in these NUMA systems, threads are spread throughout the system and memory is allocated using a first-touch data allocation policy, which means that, when a program is started on a CPU, data requested by that program will be stored on a memory bank corresponding to its local CPU. In particular, this behavior affects the allocation of the reference index of genome in the implementation of BWA.

Threads that run on the same NUMA node where the reference index is allocated have a lower latency when they access it. Therefore, when the number of threads increases, all the speed up gained due to multi-thread is mitigated by the latency of remote accesses and traffic saturation of interconnection links. This degradation of performance can be observed in Figure 1.7 which shows a continuous reduction of execution times, but the gain in performance reduces as more threads are added in the execution.

Being a system with only two NUMA nodes, performance degradation starts to be significant when more than 12 threads are used and threads are allocated on both NUMA nodes. Especially, when the application goes from 18 to 24 threads, potential gains due to the extra threads. However, the extra threads have a small impact in execution time due to the memory latency issues on both NUMA nodes, which is the crucial factor that affects performance.

When the thread count grows large enough, problems with memory accesses are getting worse. As Figure 1.8 illustrates, BWA runs in a large NUMA system, and when more than 32 threads are used, execution times are degraded and adding more threads has a negative impact in overall performance. This loss in performance can be explained, on the one hand, by the increased latency of remote memory accesses and, on the other hand, by the memory bank in which the reference genome is allocated becoming a bottleneck that generates memory contention.

More discussions and details we would talk about in the following sections. Multiple threads ability can not enable the threads efficiency, specially when facing a large amount of genome sequence dataset. In general, our HPC system always has a limited hardware, how can we make maximal usage of computing hardware with less coding to improve performance in sequence alignment? It is worth something to do some further research in this arena.

## **1.3** Objective

In this thesis, the ultimate goal we focus on is that exploring efficient data management strategies of data parallelization and data replication for variant analysis workflows, specially sequence alignment, on the heterogeneous cluster which consists of multicore and manycore system.

The following objectives we explore in the thesis with the purpose of achieving our goals:

- Definition of a data management strategy of MDPR to efficiently utilize the heterogeneous cluster on BWA aligner application by evaluating its performance on various values of thread groups and three data distribution schedule on the heterogeneous cluster. This MDPR strategy could be summarized in the following steps:

- Data replication on the genome reference

- Data parallelization on the short read

- Data distribution of static mode on the heterogeneous cluster

- Data distribution of dynamic mode that comprises even and round-robin fashion on the heterogeneous cluster

- Through the evolution of data management strategies to recognize efficiently evaluate of data parallelization and data replication for variant analysis workflows. This development could be concluded in the following contents:

- A strategy of DP based on data replication of genome reference on the homogeneous cluster

- A strategy of DR based on data parallelization of short read on the homogeneous cluster

- A strategy of DPR which combines DP and DR strategies on the homogeneous cluster

- A strategy of MDPR generated from DPR strategy that utilizes the heterogeneous cluster

- Evaluation of some relevant performance factors that demonstrates the impact of system architecture and sequence aligner, which comes to perform a significant result on the overall performance.

- NUMA effect

- Three basic execution mode on the multicore-manycore heterogeneous architecture

- Three thread libraries: Pthread, OpenMP and Intel Cilk

## 1.4 Contribution

In this thesis, we explore different strategies that allow BWA running on the heterogeneous systems, such as manycore and multicore systems. We analyze some proposed strategies in the literature and propose new strategies and crucial elements to improve global performance. This paper concentrates on which we proposed the strategies of data parallelization and data replication and we made an evaluation of BWA-based aligners in the native mode, offload mode and symmetric mode in manycore-based systems. From our experiment works, best results were obtained with the strategy that combines data parallelism and data replication. We denoted this combined strategy as MDPR(Multiple level Data Parallelization and Replication).

The strategy (MDPR) utilizes multiple instances in order to reduce memory bottlenecks by decreasing memory congestion and improving memory locality. Our results in the experiments show that MDPR achieved a considerable speed up compared with other implementations of BWA.

From these results, we present a more extensive study where we analyze the performance of different BWA variants on multicore and manycore systems. We have also adjusted the design of MDPR so that it can be executed indistinctly in multicore or manycore systems, and we have augmented it with different mechanisms of dynamic data distribution.

Main contributions of this thesis can be summarized as follows:

- We provide an OpenMP version of BWA aligner. Although BWA has taken advantage of multi-threading ability with Pthread library, it illustrates a poor performance in scalability when a large threads were applied. Moreover, we also made a comparison among Pthread library, OpenMP library and Intel Cilk library, and found OpenMP-based BWA we proposed outperforms others in terms of overall time and load balance.

- We compare three basic execution modes, native mode, offload mode and symmetric mode, in which we could utilize the heterogeneous architecture of Intel Xeon and Xeon Phi. Moreover, thread scalability performance of three execution modes was evaluated in the experiments.

- We propose four strategies (DP, DR, DPR and MDPR) that cover different combinations of data parallelization and data replication when we applied them to BWA, one of the most popular genome read mapper, in order to explore efficient data parallelism in the homogeneous and heterogeneous systems.

- We analyze three data distribution schedule in MDPR strategy, one static mode and two dynamic modes. Static mode focuses on the data load among nodes based on the native mode running performance. Dynamic modes distribute dataset among nodes in a fashion of even and round-robin data management. Although static mode achieve the best time-consuming of all, it needs a complicated configurations beforehand. In term of complexity and convenience, dynamic mode could be a better choice in performance improvement, specially round-robin mode could reach an approximate time-cost with static mode.

- We carry out an experimental study comparing different versions of BWA on multicore and manycore systems, including the strategies proposed in this work and other

alternatives proposed in the literature, such as mBWA, pBWA, BWA-ALN, etc. This study has shown us the best alternatives to run BWA on manycore systems based on Intel Xeon Phi and other multicore systems based on Intel and AMD processors.

## 1.5 Outline

The works of the thesis is structured as follows.

#### • Chapter 1: Introduction

In this chapter, some crucial elements in this research are proposed, like motivations, objectives of works. We also give our contributions and outline for better reviewing.

#### • Chapter 2: Literature Review on Related Works

In this chapter, we make a literature reviews on related works in performance improvement of sequence alignment on the heterogeneous multicore-manycore architecture and sequence aligners, especially the most popular and widespread aligner, BWA aligner.

#### • Chapter 3: Variant Analysis

In this chapter, relevant subjects concerning variant analysis in DNA sequence are discussed. We discuss more information about alignment since we concentrate on sequence aligner.

#### • Chapter 4: Heterogeneous Multicore-Manycore Architectures

In this chapter, we provide a brief description of the basic architectures that we have used in our study, namely, multicore systems with NUMA nodes and manycore accelerators, Intel Xeon, Intel Xeon Phi, and AMD Opteron.

## Chapter 5: Data Management Strategies Based on Data Parallelization and Replication

In this chapter, we discuss the strategies of DP, DR, DPR and MDPR which are based on data parallelization and replication. Detailed architecture is illustrated in this chapter for viewers to readily understand our works. We also make a comparison with these strategies with our previous research.

#### • Chapter 6: Experimental Implementation and Environment

In this chapter, sample datasets we utilize, implementation systems we apply, related software we use and experiment environment we set, are illustrated in details here.

#### • Chapter 7: Experimental Results and Evaluation

In this chapter, we not only make an evaluation of the three basic execution modes in the heterogeneous system made of Intel Xeon and Xeon Phi, but also propose a OpenMP-based version of BWA aligner. The data management strategies, including DP, DR, DPR and MDPR, are also evaluated in this chapter.

#### Chapter 8: Discussion and Conclusion

In this chapter we discuss about the results from the experiments and conclude the achievements we achieve in the research. We also illustrate some promising perspectives on the future research directions.

## Chapter 2

## **Literature Review on Related Works**

Our work explores effective data parallelism solutions on the sequence aligner that are suitable for the heterogeneous architectures.

Majority of works on the alignment provide significant performance improvements. However, they are only designed to run on multicore architecture or on GPUs, and underestimated in another manycore architecture like the Intel Xeon Phi. Although some existing studies ([11] and [13]-[14]) that were designed to execute aligner on multicore and manycore architecture and finally achieve a considerable performance improvement, they exhibits some advantages and bottlenecks we would discuss below.

First we concentrate literature review on the performance improvement of sequence aligners in multicore-manycore heterogeneous system. Afterwards, research about BWA aligner is evaluated in many arenas to improve the performance of alignment application.

## 2.1 Performance Improvement of Sequence Aligner in the Heterogeneous System

For the purpose of better utilizing modern system architectures with alignment application, we need to make a compromise between these two crucial factors. Some previous works from our research group [15] [16] [17] that investigated memory interleaving and data parallelization strategy we proposed on NUMA and Bi-ring architecture under four aligner cases which came to the result that memory interleaving and data parallelization strategy could provide a considerable performance improvement on such two architectures.

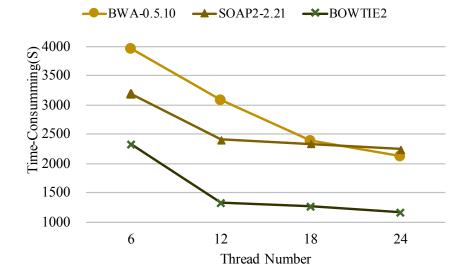

Blast [18], Bowtie [19], SOAP2 [20] and BWA [21], many sequence aligners were put forward to solve this booming problem. They are suitable for multicore system while complex coding job is needed for transmitting to manycore part. Many works keep a view of alignment in the architecture of multicore.

Zhang et al. [22] illustrated that sequence alignment is memory-sensitive and tried to optimize BWT index on multicore system. This optimization can not be readily transited to manycore system since it is special designed for multicore system. Although it could compile on the manycore system of Intel Xeon Phi since an identical architecture they used, it can not reach an improvement of performance since they owns different bits wide.

Olivier et al. [23] compared different task parallel schedule of OpenMP and Qthreads on multi-socket multicore architecture and concluded that hierarchical work stealing scheduler is competitive in all benchmarks. One crucial factor that this paper indicates is task parallel schedule plays a significant role in overall performance. Thus we tried different schedule, such as static and dynamic schedule in data distribution, to explore in the experiments.

Macedo et al. [24] introduced an using multi-threading and multi-instance in master/slave parallel strategy to facilitate multiple sequence alignment on heterogeneous multicore clusters. Their results display allocation policy and the master node has great impact on the overall performance of the system. Although they are something similar with our research, they do not explore our ideas of data replication in DR strategy and data parallelization in DP strategy. Our experiments also display the evolution of data parallelization step by step. Jing Nagarajan et al. [25] presented multiple parallelization skills could be useful on multicore system. But they have not tried on the manycore architecture and BWA-backtrack algorithm as we did in the experiments.

Chen et al. [26] raised an offloading acceleration of the seed extension of BWA aligner in FPGA architecture. Houtgast et al. [27][28] made an effort to adopt alignment application on GPU-based and FPGA-based architectures. Tens of research about alignment performance improvement on FPGA are discussed in details in paper [29]. Otherwise, same phenomena occurs on GPU architecture. Many papers [30] about alignment improvement on GPUs are proposed in HPC field. However, it is observed that a few reviews of alignment on Intel Xeon Phi manycore architecture.

## 2.2 Performance Improvement on BWA Aligner

Many research describe different approaches to improve the performance of alignment application, specially BWA aligner on one special architecture system, multicore or GPUs architectures.

Zhang et al. [22] showed that BWA is a memory-sensitive aligner and improved its performance by optimizing cache mechanisms on the multicore architectures. But two disadvantages they have. On the one hand, the skill of cache optimization requires a comprehensive coding ability, we can not easily transit for other platforms. On the other hand, they do not try experiments on memory-sensitive system, manycore architecture like Intel Xeon Phi and GPUs.

Jing Nagarajan et al. [25] found that BWA aligner owns their performance bottlenecks in thread scalability, scattering and gathering of data and memory bandwidth limitations, respectively. These restrictions are consistent with we observed in the experiments of the scalability evaluation of BWA aligner. Afterwards they introduced an approach of multiple parallelization to accelerate BWA aligner in multicore system, which consists of thread parallelization, data parallelization, and concurrent parallelization. The differences between this work and ours is that we focus on OpenMP thread library instead of Pthread they concentrate, and we also illustrate the evolution and the evaluation of data parallelization strategy.

Houtgast et al. [31] accelerated BWA by offloading some highly parallel computing which is applied on the GPU system. Houtgast et al. [32] utilized a simple adaptive load balance algorithm on GPUs for BWA aligner and achieved a considerable improvement in performance. However, this two research proposed above focus on BWA-MEM algorithm in GPU system, instead of the most widespread algorithm, BWA-backtrack. We did experiments for dynamic data distribution among heterogeneous systems which quite differs with the simple adaptive load balance algorithm, and we also compared one offload version of BWA, mBWA, which works in manycore architecture, Intel Xeon Phi.

BarraCUDA [33] is an implementation of BWA aligner based on GPU which achieves about 3X speed-ups when comparing to the multi-threading original BWA version. Moreover, CUSHAW [34] and SOAP3 [35], they are GPU-based implementation of BWA aligner as well as BarraCUDA and already reach a considerable improvement of performance compared to the original BWA aligner. However, these two versions of BWA do not permit gapped alignments in procedure, which could lead to some mapping results undiscovered. Tens of research about alignment performance improvement in GPU platform as well as another HPC architecture called FPGA are discussed in details in paper [29]. But there are few works of BWA aligner existing in FPGA.

For the distributed computing among multiple clusters, by utilizing Hadoop technology, BigBWA [36] achieved a significant improvement of performance on multiple nodes. While SparkBWA [37] tried to use another big data technology, Spark, to boost BWA aligner. This is some versions that might be convenient for distributed computing implementation. There are also many other proposals focusing on the utilization of BWA under the heterogeneous architecture, especially one multicore system with MIC architecture, Intel Xeon + Intel Xeon Phi.

pBWA [14] is an efficient parallel version of BWA based on the Open MPI library. It not only preserves the multi-thread capability provided by BWA but also adds efficient parallelization for core alignment functions on the heterogeneous cluster. Unfortunately, on the one hand, it cannot be evaluated at the case of large number of instances of pBWA on the Xeon Phi architecture as a limited memory is used. On the other hand, even data distribution among multiple instances which leads to a crucial bottleneck in the heterogeneous system cause of the huge difference might be on the performance of dissimilar architectures, according to our experiments in MDPR.

Xinmin Tian et al. [13] presented several practical SIMD vectorization techniques on MIC architecture to achieve improvements in performance of BWA. However, such SIMD techniques require sophisticated coding skills in order to incorporate with the existing genome aligners. Suejb Memeti et al. [38] and Lipeng Wang et al. [39] provided parallel solutions for large scale DNA analysis which exploits thread-level and SIMD techniques in the Xeon Phi, but their solution does not deal with data-level parallelism as we explore in the research.

New aligner MICA [40] optimized MIC limitation and explored the extra parallelism inside each MIC core. But MICA still an initial version which needs many configurations before implementation. Yingbo Cui et al. [11] proposed mBWA which works according to offload mode with Intel Xeon Phi. mBWA utilizes a multi-level parallelization strategy that includes data IO parallelization and a parallel pipeline in reads alignment because of data-dependent. However, mBWA is not an open source project and can not be executed readily under multiple Intel Xeon Phi nodes. Charlotte Herzeel et al. [41] evaluated an Intel Cilk implementation of BWA on the heterogeneous systems that consists of Intel Xeon Phi, and at some extent corrected data load imbalance that produced by differences in data reads. It is worth something that could provide a third-part view of thread library when we compared with Pthread and OpenMP libraries.

## Chapter 3

## Variant Analysis

In this chapter, relevant subjects concerning variant analysis in DNA sequence are discussed. The properties of a DNA molecule and genome sequence are shown in Section 3.1. Then the details of sequence alignment are discussed in Section 3.2. Following by Section 3.3 we analyze the performance of BWA, a widespread sequence alignment application, to demonstrate some interesting behaviors in BWA aligner. Section 3.4 and 3.5 is a short overview of variant calling and variant annotation, which consist of the two remaining main functions in the variant analysis workflows.

## 3.1 Overview

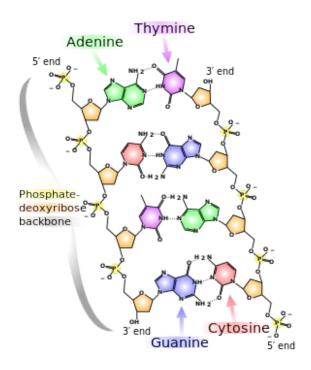

Biological information is stored in deoxyribonucleic acid (DNA). DNA is a kind of nucleic acid composed of double chains, as shown in Figure 3.1, that coil around each other to form a double helix carrying the genetic instructions used in the growth, development, functioning and reproduction of all known living organisms and many viruses [42]. This double-stranded structure could store the same biological information in both chains.

This double-stranded structure is also known as polynucleotides since they are composed of simpler monomeric units called nucleotides [43]. There are four types of nitrogen-

Fig. 3.1 The molecular structure of DNA, four types of nitrogen-containing nucleobases: Adenine[A], Thymine[T], Guanine[G] and Cytosine[C], two base pairings(A-T, C-G)

containing nucleobases called Adenine(A), Thymine(T), Guanine(G) and Cytosine(C). According to the rule of base pairing (A with T, C with G), two separate strands are bound together into a double-stranded structure. But most parts of DNA do not serve for protein sequences which is denoted as non-coding parts. The non-coding genome consists in the majority part of fraction of the total sequence genome in many species. For human DNA sequence, only 1.5% of the human genome can code protein, while 50%+ of the human genome consisting of the non-coding part in genome sequence [44]. However, these noncoding section in genome sequence may still encode some functional RNA molecules that is crucial elements involved in the gene expression [45].

For next generation sequence (NGS) in human gene, variant analysis is necessary to distinguish Mendelian disorders, complex diseases and somatic mutations in DNA sequence. In fact, three common scenarios are considered for human gene in NGS data [10].

• Identification of causative genes in Mendelian disorders (germline mutations),

- · Identification of candidate genes in complex diseases for further functional studies and

- Identification of constitutional mutations as well as driver and passenger genes in cancer (somatic mutations).

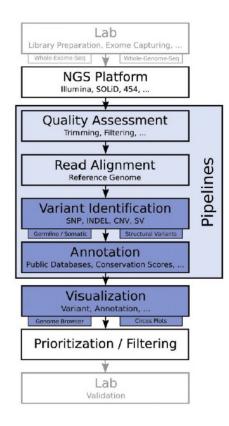

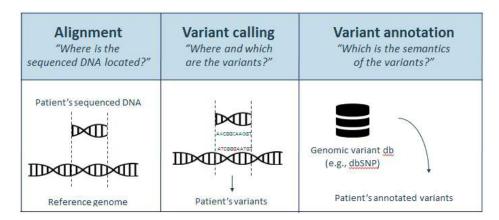

As shown in Figure 3.2, it is the basic workflow for variant analysis in genome sequencing [10]. There are four significant workflows consist of the main pipelines in variant analysis, quality assessment, read alignment, variant identification and variant annotation. Quality assessment is to evaluate the quality of raw reads from NGS platform, trim and correct them when necessary in order to reach defined standards. Nowadays, many NGS dataset projects provide standard NGS datasets. It is convenient for the tools of variant analysis of NGS to use without any efforts. Thus, read alignment or sequence alignment, variant identification or variant calling, and variant annotation are consist of the most important steps in variant analysis.