#### NONLINEAR CONTROL OF DC-DC SWITCHING CONVERTERS WITH CONSTANT POWER LOAD

#### Blanca Areli Martínez Treviño

**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# Nonlinear control of dc–dc switching converters with constant power load

Blanca Areli Martínez Treviño

DOCTORAL THESIS

2019

## **UNIVERSITAT ROVIRA i VIRGILI**

## Nonlinear control of dc-dc switching converters with constant power load

Blanca Areli Martinez Treviño

DOCTORAL THESIS 2019

## Blanca Areli Martinez Treviño

Nonlinear control of dc-dc switching converters with constant power load

Doctoral Thesis

Advisors Dr. Abdelali El Aroudi Dr. Luis Martínez Salamero

Department of Electronics, Electrical Engineering and Automatic Control

Automatic Control and Industrial Electronics Group

## UNIVERSITAT ROVIRA i VIRGILI

Tarragona 2019

FEM CONSTAR que aquest treball, titulat "Nonlinear control of dc-dc switching converters with constant power load", presentat per Blanca Areli Martínez Treviño per a l'obtenció del títol de Doctor, ha estat realitzat sota la meva direcció al Departament d'Enginyeria Electrònica Elèctrica i Automàtica d'aquesta universitat.

HAGO CONSTAR que el presente trabajo, titulado "Nonlinear control of dc-dc switching converters with constant power load", que presenta Blanca Areli Martínez Treviño para la obtención del título de Doctor, ha sido realizado bajo mi dirección en el Departamento de Ingeniería Electrónica Eléctrica y Automática de esta universidad.

I STATE that the present study, entitled "Nonlinear control of dc-dc switching converters with constant power load", presented by Blanca Areli Martínez Treviño for the award of the degree of Doctor, has been carried out under my supervision at the Department of Electronic, Electric and Automatic Control Engineering of this university.

Tarragona, 01 April 2019

El/s director/s de la tesi doctoral El/los director/es de la tesis doctoral Doctoral Thesis Supervisor/s

Dr. Luis Martínez Salamero

Dr. Abdelali El Aroudi

### Acknowledgements

Firstly, I would like to express my gratitude to my advisors, Dr. Luis Martínez Salamero and Dr. Abdelali El Aroudi. I would like to thank them for sharing their knowledge with me, and for guiding and support me during this PhD thesis. Special thanks to Dr. Luis, who give me the opportunity to start this research work.

Also, I would like to thank my colleagues of the GAEI laboratory, whom I met in this process: Juan M. Salmeron, Ricardo Bonache, Sara García, Nazmul Hasan, David Elvira, Juan D. Espitia, Edgar Zahino, Ezequiel Rodriguez, Ramon Estalella and Josep Guasch. Especial thanks to Catalina González for her professional and personal support and for Dr. Josep M. Bosque, Dra. Reham Haroun and Albert Teixidó for their technical support at the laboratory. I also would like to thank Dr. Angel Cid and Dr. Enric Vidal for their collaboration and support in the experimental prototypes developed.

I want to express the deepest and warmers gratitude to my parents, Roberto Martínez and Bony Treviño, my sister Nayely Karina, my brother Rigoberto, his partner Moli, to all my other relatives and friends for always showing me their love and support, even in the distance. Last and no least, I would especially like to recognize Albert for being with me in this part of my life, and encouraging me in the good and bad times.

Thesis written by Blanca Areli Martínez Treviño.

Nonlinear control of dc-dc switching converters with constant power load.

Ph.D. in Technologies for Nanosystems, Bioengineering and Energy.

This research has been funded by the Agència de Gestió d'Ajuts Universitaris i de Recerca (AGAUR).

This work has been sponsored by the Spanish Agencia Estatal de Investigación (AEI) and the Fondo Europeo de Desarrollo Regional (FEDER) under grants PI2013-47293-R, DPI2015-67292-R DPI2016-80491-R(AEI/FEDER, UE) and DPI2017-84572-C2-1-R.

> To my parents for everything they have done for me.

# Contents

| $\mathbf{Li}$ | List of Figures vii |         |                                                               |          |  |

|---------------|---------------------|---------|---------------------------------------------------------------|----------|--|

| $\mathbf{Li}$ | List of Tables xiii |         |                                                               |          |  |

| N             | omer                | nclatur | e x                                                           | viii     |  |

| 1             | Introduction        |         | 1                                                             |          |  |

|               | 1.1                 | Consta  | ant Power Load Definition                                     | 2        |  |

|               | 1.2                 | Risk o  | f Instability                                                 | 2        |  |

|               | 1.3                 | Dc-dc   | Switching Converters in CCM Loaded with a CPL                 | <b>5</b> |  |

|               | 1.4                 | Transf  | er Functions of Unstable System                               | 8        |  |

|               | 1.5                 | Motiva  | ation                                                         | 10       |  |

|               | 1.6                 | Objec   | tives                                                         | 13       |  |

| <b>2</b>      | Ope                 | en-loop | o dc-dc Converters with CPL in the Boundary CCM-DCM           | 15       |  |

|               | 2.1                 | Introd  | uction                                                        | 15       |  |

|               | 2.2                 | Averag  | ge Circuit Model of the Elementary Converters with CPL in CCM | 16       |  |

|               | 2.3                 | Bound   | lary CCM-DCM                                                  | 18       |  |

|               | 2.4                 | Minim   | num Power of the CPL for CCM Operation                        | 18       |  |

|               |                     | 2.4.1   | Buck Converter                                                | 18       |  |

|               |                     | 2.4.2   | Boost Converter                                               | 19       |  |

|               |                     | 2.4.3   | Buck-Boost Converter                                          | 19       |  |

|               |                     | 2.4.4   | Comparison of Minimum Values of Power                         | 19       |  |

|               | 2.5                 | Stabili | ty of the Equilibrium Point in the Boundary CCM-DCM           | 20       |  |

|   |      | 2.5.1  | Buck Converter Case                                                                                             | 20        |

|---|------|--------|-----------------------------------------------------------------------------------------------------------------|-----------|

|   |      | 2.5.2  | Boost Converter Case                                                                                            | 21        |

|   |      | 2.5.3  | Buck-boost Converter Case                                                                                       | 22        |

|   | 2.6  | Simula | ation of Elementary Converters Operation in the Boundary CCM-                                                   |           |

|   |      | DCM    |                                                                                                                 | 24        |

|   |      | 2.6.1  | Buck Converter                                                                                                  | 24        |

|   |      | 2.6.2  | Boost Converter                                                                                                 | 25        |

| 3 | Two  | о Аррі | coaches for the Closed-loop Operation of Power Converters                                                       | 5         |

|   | witł | n CPL  | in CCM: Two-loop Linear Control and SMC                                                                         | <b>29</b> |

|   | 3.1  | Introd | uction                                                                                                          | 29        |

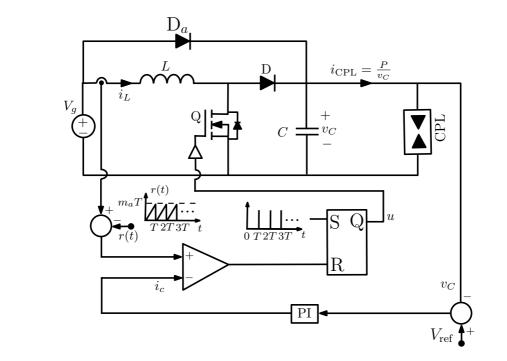

|   | 3.2  | Two-le | pop Linear Control                                                                                              | 30        |

|   |      | 3.2.1  | Inner Loop based on a Peak-Current Mode Control                                                                 | 31        |

|   |      | 3.2.2  | Outer Loop based on a PI Compensator                                                                            | 32        |

|   |      | 3.2.3  | Simulation Results                                                                                              | 33        |

|   | 3.3  | SMC o  | of a Boost Converter with CPL                                                                                   | 38        |

|   |      | 3.3.1  | Equilibrium Point Locus                                                                                         | 38        |

|   |      | 3.3.2  | Sliding Surface                                                                                                 | 38        |

|   |      | 3.3.3  | Equilibrium Point                                                                                               | 40        |

|   |      | 3.3.4  | Control Law and Existence Sliding Mode Condition $\ . \ . \ .$ .                                                | 41        |

|   |      | 3.3.5  | Equivalent Control $\ldots \ldots \ldots$ | 42        |

|   |      | 3.3.6  | Ideal Sliding Dynamics                                                                                          | 43        |

|   |      | 3.3.7  | Analysis of Switching Surface                                                                                   | 44        |

|   |      | 3.3.8  | Numerical Simulations                                                                                           | 45        |

|   | 3.4  | Simula | ation and Experimental Results of the Prototype                                                                 | 47        |

| 4 | Two  | o-loop | PWM-digital SMC of Boost Converter with CPL                                                                     | 55        |

|   | 4.1  | Introd | uction                                                                                                          | 55        |

|   | 4.2  | Discre | te-time Modeling of a Boost Converter Loaded by a CPL $\ . \ . \ .$                                             | 56        |

|   |      | 4.2.1  | System Description                                                                                              | 56        |

|   |      | 4.2.2  | Discrete-time Mathematical Modeling                                                                             | 58        |

|   |      | 4.2.3  | Open-loop Model Validation                                                                                      | 59        |

|   | 4.3 | Discre | te-time Sliding-mode Inner Loop Control Design                    | 60       |

|---|-----|--------|-------------------------------------------------------------------|----------|

|   |     | 4.3.1  | Large Signal Model with Voltage Loop Open                         | 60       |

|   |     | 4.3.2  | Equivalent Control                                                | 61       |

|   |     | 4.3.3  | DSMC Design                                                       | 62       |

|   |     | 4.3.4  | Control-oriented Full-order Discrete-time Small-signal Model $$ . | 63       |

|   | 4.4 | Discre | te-time Output Voltage Loop Control Design                        | 65       |

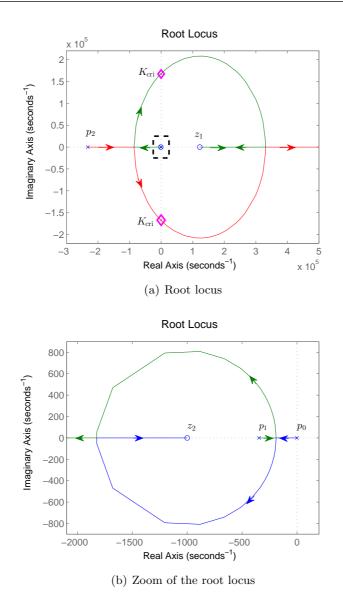

|   | 4.5 | Design | n of the Output Voltage Feedback Loop Using the Root-locus Tech-  |          |

|   |     | nique  |                                                                   | 67       |

|   | 4.6 | Nume   | rical Simulations and Experimental Results                        | 69       |

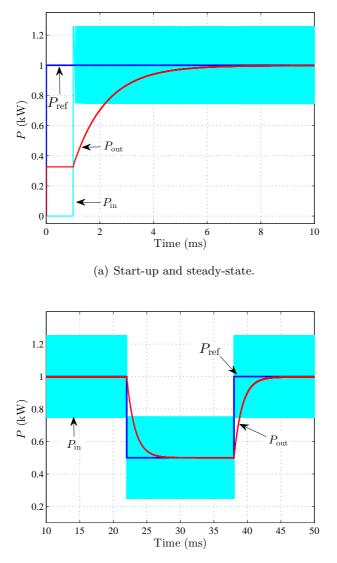

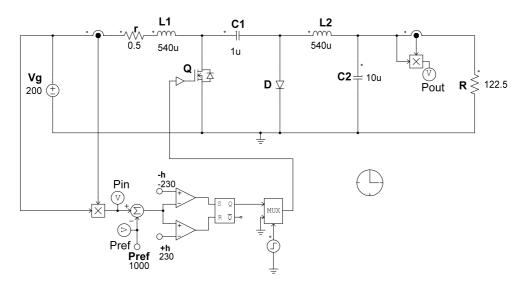

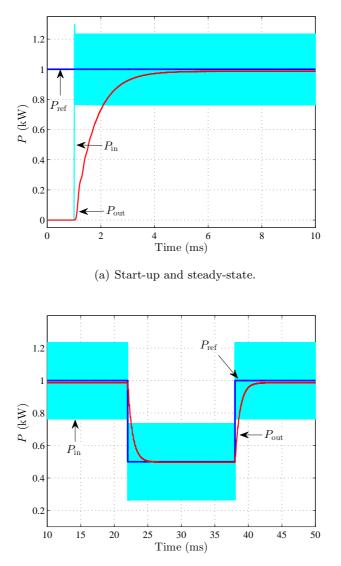

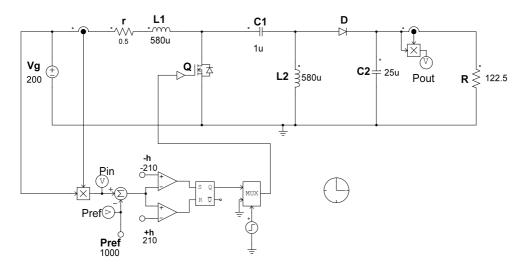

|   |     | 4.6.1  | System Startup and Steady-state Operation                         | 69       |

|   |     | 4.6.2  | Experimental Setup                                                | 70       |

|   |     | 4.6.3  | Results                                                           | 72       |

| 5 | РW  | M nor  | nlinear analog control: virtual mesh approach and adaptive        | 9        |

| - |     |        | with CPL power estimation                                         | 79       |

|   | 5.1 | Introd | uction                                                            | 79       |

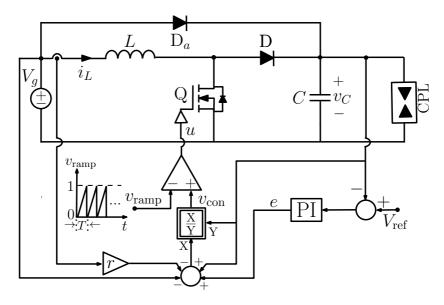

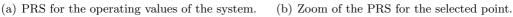

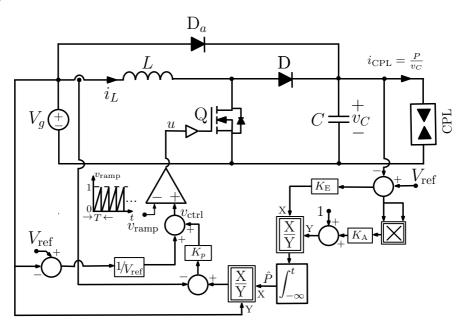

|   | 5.2 | PWM    | Nonlinear Control for Virtual Mesh Emulation                      | 80       |

|   |     | 5.2.1  | Closed-loop Equations                                             | 81       |

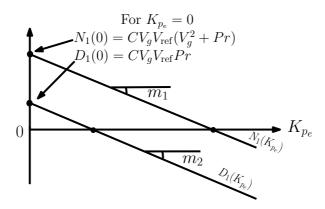

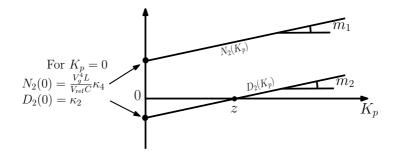

|   |     | 5.2.2  | Stability Analysis                                                | 82       |

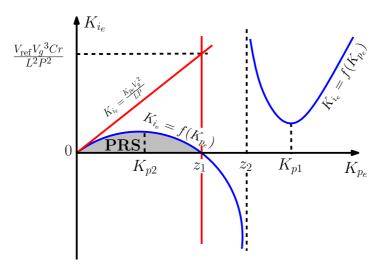

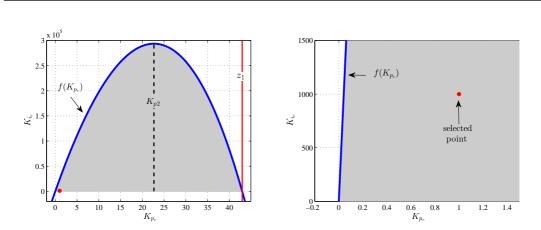

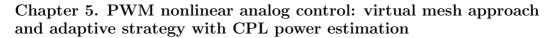

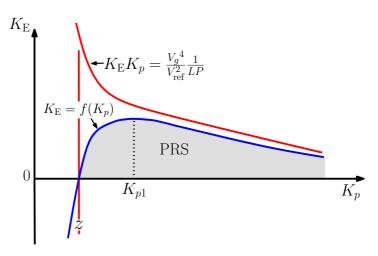

|   |     | 5.2.3  | Parametric Region of Stability                                    | 84       |

|   |     | 5.2.4  | Numerical Simulations and Experimental Results                    | 86       |

|   | 5.3 | PWM    | Adaptive Control for the Voltage Regulation of a Boost Converter  |          |

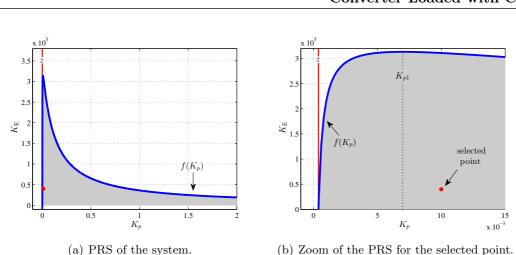

|   |     | Loade  | d with CPL                                                        | 94       |

|   |     | 5.3.1  | Control Design                                                    | 94       |

|   |     | 5.3.2  | Closed-loop Equations                                             | 95       |

|   |     | 0.0.2  |                                                                   |          |

|   |     | 5.3.3  | Stability Analysis                                                | 96       |

|   |     |        |                                                                   | 96<br>99 |

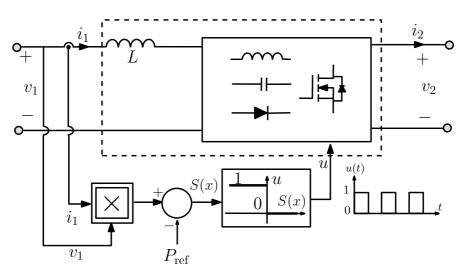

| 6 | Syn  | thesis | of CPLs Using Switching Converters under SMC                                                                                                  | 109 |

|---|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 6.1  | Introd | $uction \ldots \ldots$ | 109 |

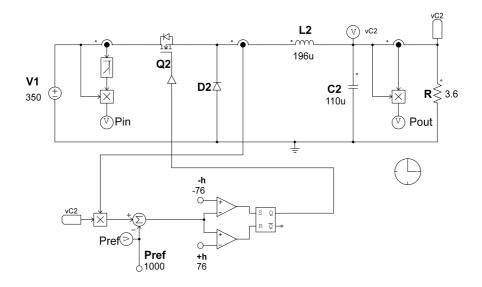

|   | 6.2  | Instan | taneous CPL based on a Buck Converter                                                                                                         | 110 |

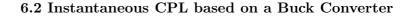

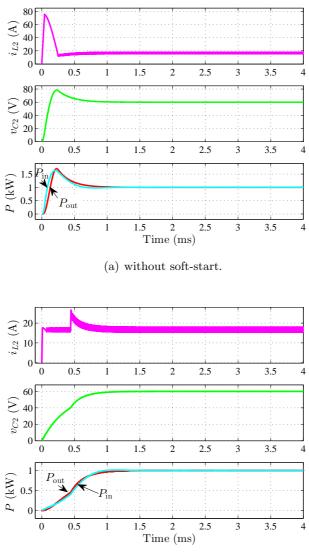

|   |      | 6.2.1  | Simulation Results of the Buck Converter Operating as CPLs                                                                                    | 113 |

|   |      | 6.2.2  | Design and Implementation of the Buck Converter                                                                                               | 117 |

|   | 6.3  | Boost  | Converter Supplying Constant Power to a Buck Converter                                                                                        | 121 |

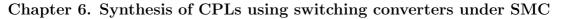

|   | 6.4  | Synthe | esis of CPLs Using Switching Converters under SMC                                                                                             | 123 |

|   | 6.5  | SMC o  | of the Converter Candidates that Can Operate as CPLs                                                                                          | 125 |

|   |      | 6.5.1  | Synthesizing a CPL Using a Boost Converter                                                                                                    | 125 |

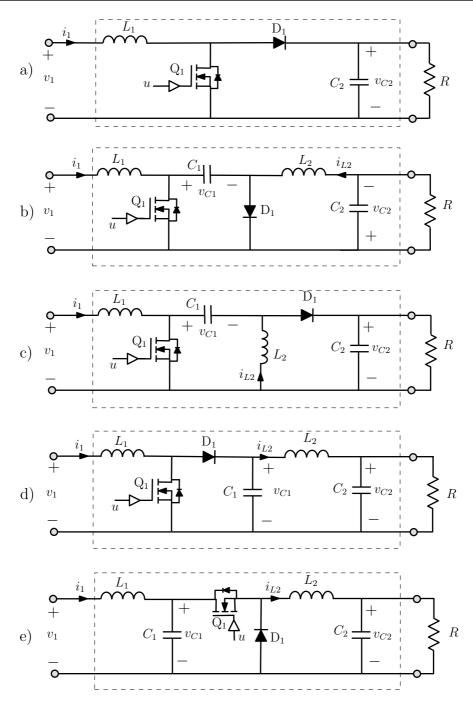

|   |      | 6.5.2  | Synthesizing a CPL Using a Ćuk Converter                                                                                                      | 131 |

|   |      | 6.5.3  | Synthesizing a CPL Using a Transformerless SEPIC Converter .                                                                                  | 132 |

|   |      | 6.5.4  | Synthesizing a CPL Using a BOF Converter                                                                                                      | 134 |

|   |      | 6.5.5  | Synthesizing a CPL Using a Buck Converter with Input-filter                                                                                   | 135 |

|   | 6.6  | Design | of the Power Stage of the Converter Candidates that Can Operate                                                                               |     |

|   |      | as CPI | Ls                                                                                                                                            | 135 |

|   |      | 6.6.1  | Design of the Boost Converter                                                                                                                 | 136 |

|   |      | 6.6.2  | Design of the Ćuk Converter                                                                                                                   | 137 |

|   |      | 6.6.3  | Design of the SEPIC converter                                                                                                                 | 139 |

|   | 6.7  | Simula | ation Results of the Converter Candidates that Can Operate as                                                                                 |     |

|   |      | CPLs.  |                                                                                                                                               | 140 |

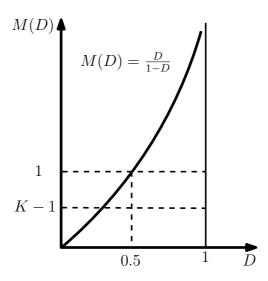

|   |      | 6.7.1  | Simulation Results of the Boost Converter.                                                                                                    | 141 |

|   |      | 6.7.2  | Simulation Results of the Ćuk Converter.                                                                                                      | 143 |

|   |      | 6.7.3  | Simulation Results of the SEPIC Converter                                                                                                     | 144 |

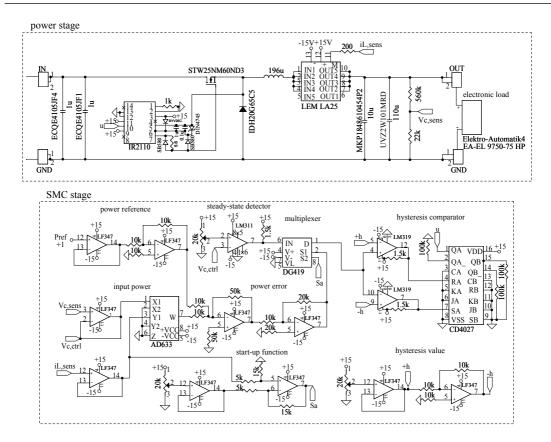

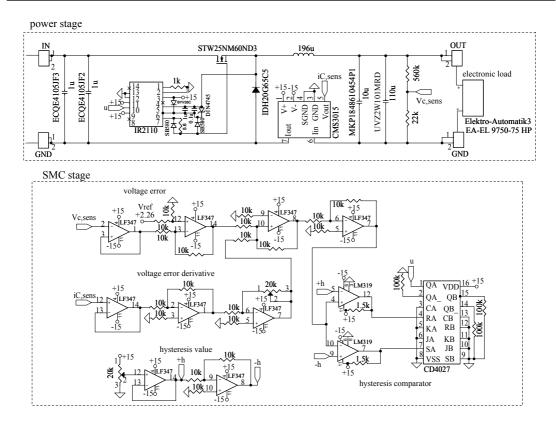

|   | 6.8  | Design | and Implementation of Prototypes of the Converter Candidates                                                                                  |     |

|   |      | that C | an Operate as CPLs                                                                                                                            | 146 |

|   |      | 6.8.1  | Power Stage Experimental Setup                                                                                                                | 146 |

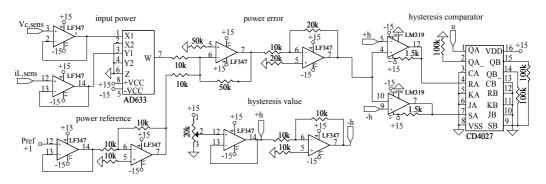

|   |      | 6.8.2  | Control Stage Experimental Setup                                                                                                              | 148 |

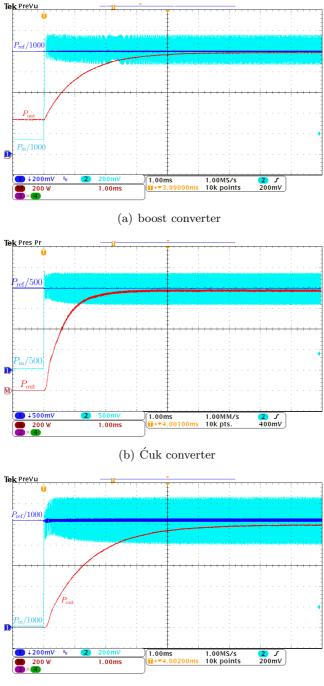

|   | 6.9  | Experi | imental Results of the Converter Candidates that Can Operate as                                                                               |     |

|   |      | CPLs.  | · · · · · · · · · · · · · · · · · · ·                                                                                                         | 149 |

|   | 6.10 | Genera | al Procedure to Design Switching Converters Operating as CPLs                                                                                 |     |

|   |      |        | he proposed sliding function $S(x)$                                                                                                           | 152 |

# CONTENTS 7 Conclusions 153 References 157 List of Publications 169

# List of Figures

| 1.1 | Cascade connection of power converters.                                  | 1  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | CPL definition.                                                          | 2  |

| 1.3 | Model of an ideally regulated high efficient converter with input filter | 3  |

| 1.4 | Intersection of CPL characteristic curve and load line                   | 4  |

| 1.5 | Elementary converters loaded with CPL                                    | 6  |

| 1.6 | ON and OFF trajectories corresponding to the elementary dc-dc convert-   |    |

|     | ers with CPL.                                                            | 7  |

| 1.7 | Linearization of a CPL.                                                  | 9  |

| 1.8 | Small-signal average dynamic model of a boost converter with resistive   |    |

|     | load and control variations.                                             | 9  |

| 1.9 | Circuit model of the small-signal dynamic behavior of a boost converter  |    |

|     | with CPL for control variations.                                         | 10 |

| 2.1 | Averaged circuit model of elementary converters with CPL                 | 16 |

| 2.2 | Steady-state model corresponding to the circuits in Fig. 2.1             | 17 |

| 2.3 | Steady-state inductor current $i_L$ in the boundary CCM-DCM for any      |    |

|     | elementary converter.                                                    | 18 |

| 2.4 | Buck converter behavior with CPL in open loop in the boundary CCM-       |    |

|     | DCM operation mode.                                                      | 25 |

| 2.5 | Buck converter behavior with CPL in open loop in DCM $P = 290$ W         |    |

|     | $< P_{\min_{\text{CCM}}}$                                                | 25 |

| 2.6 | Buck converter behavior with CPL in open loop in CCM $P = 350$ W         |    |

|     | $> P_{\min_{\text{CCM}}}$                                                | 26 |

| 2.7  | Boost converter behavior with CPL in open loop in the boundary CCM-                            |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | DCM operation mode.                                                                            | 27 |

| 2.8  | Boost converter behavior with CPL in open loop in DCM $P = 200$ W                              |    |

|      | $< P_{\min_{\text{CCM}}}$                                                                      | 27 |

| 2.9  | Boost converter behavior with CPL in open loop in CCM $P = 300$ W                              |    |

|      | $> P_{\min_{CCM}}$                                                                             | 28 |

| 3.1  | Block diagram of a two-loop linear analog control of a boost converter                         |    |

|      | loaded with a CPL                                                                              | 31 |

| 3.2  | Dynamic models of the two control loop PWM linear analog control. $ .$                         | 32 |

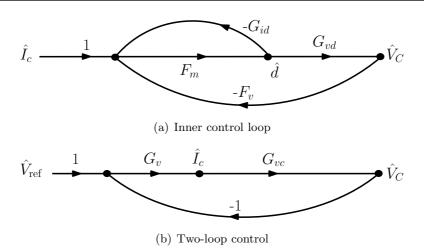

| 3.3  | Pole-zero map in s-plane of the boost converter supplying CPL under                            |    |

|      | the proposed control                                                                           | 34 |

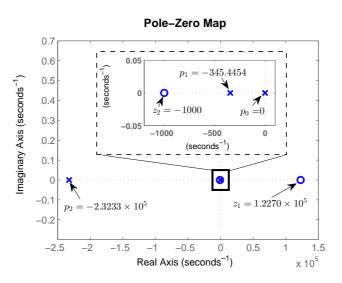

| 3.4  | Root locus of the of the system                                                                | 35 |

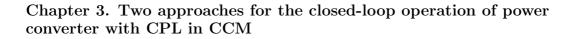

| 3.5  | Start-up and steady state of the boost converter under CPL with the                            |    |

|      | two-loop control without soft-start $((a)-(b))$ and with soft-start $((c)-(d))$ .              | 36 |

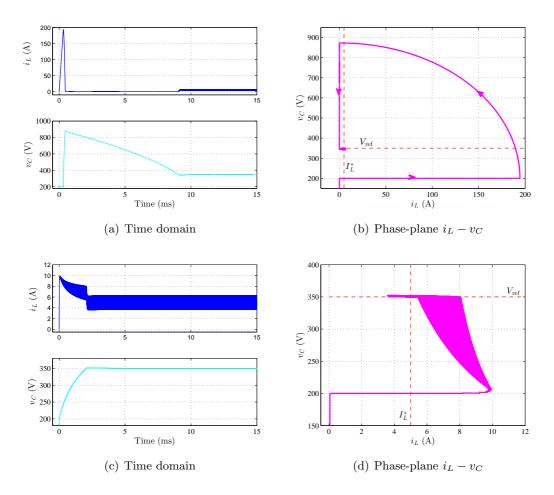

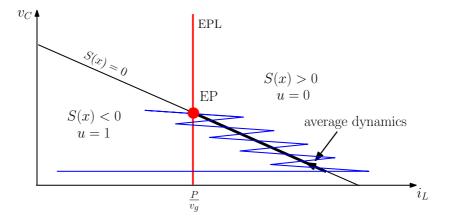

| 3.6  | Numerical simulation of the boost converter under the two-loop control                         |    |

|      | in front of power load changes (1 kW $\rightarrow$ 0.5 kW at 32 ms, 0.5 kW $\rightarrow$ 1     |    |

|      | kW at 48 ms). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 37 |

| 3.7  | Numerical simulation of the boost converter under two-loop front of in-                        |    |

|      | put voltage changes (200 V $\rightarrow$ 250 V at 92 ms, 250 V $\rightarrow$ 200 V at 108      |    |

|      | ms)                                                                                            | 37 |

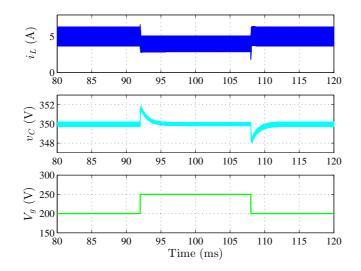

| 3.8  | Combining ON and OFF trajectories to create a stable trajectory that                           |    |

|      | attains the desired equilibrium point from zero initial conditions                             | 39 |

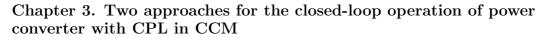

| 3.9  | Block diagram of a SMC of a boost converter loaded with a CPL $\ . \ . \ .$                    | 40 |

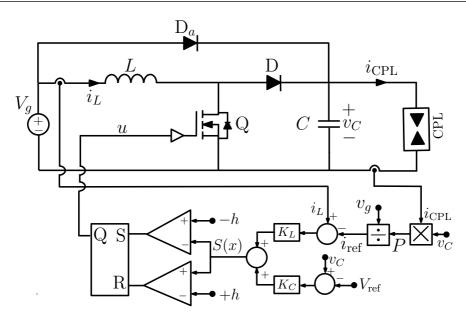

| 3.10 | Plot of $f(v_C)$ for different values of $M$ , ESM region, $S(x)$ , EPL and                    |    |

|      | equilibrium point                                                                              | 43 |

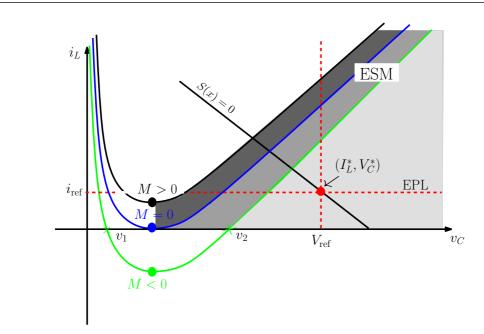

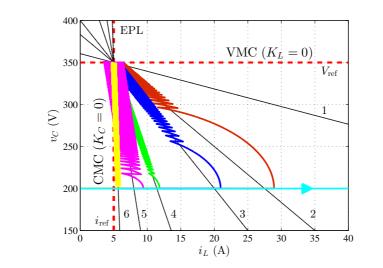

| 3.11 | Family of switching surfaces for different combinations of $K_L, K_C$                          | 45 |

| 3.12 | Switching surfaces and trajectories with different values of $K_L$ and $K_C$ .                 | 47 |

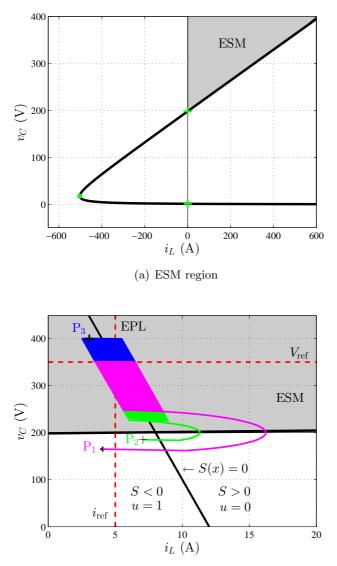

| 3.13 | Region of existence of sliding-mode for the boost converter with CPL. $$ .                     | 48 |

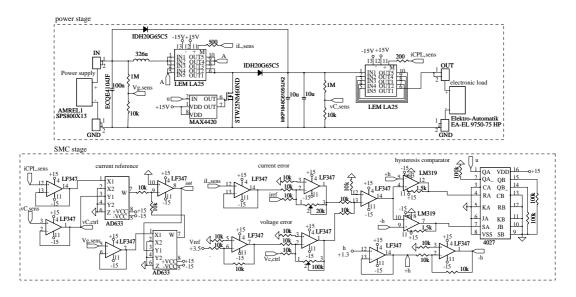

| 3.14 | Schematic circuit diagram of the experimental prototype of the boost                           |    |

|      | converter with the proposed SMC                                                                | 49 |

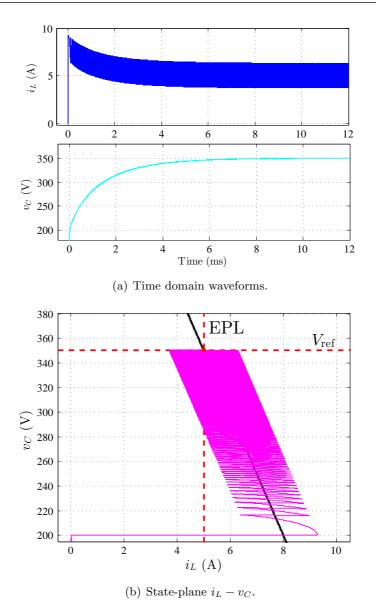

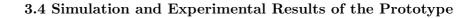

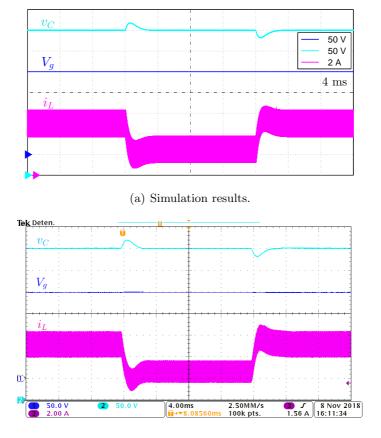

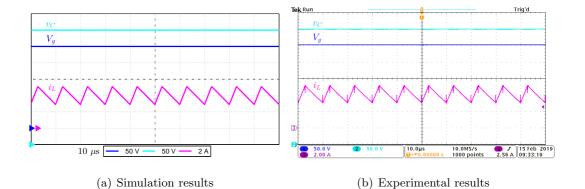

| 3.15 | System response during start-up.                                                                                                   | 51  |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.16 | Steady-state waveforms of the boost converter supplying a CPL ( $P = 1$ kW).                                                       | 52  |

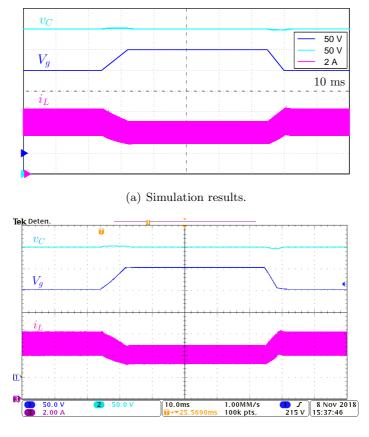

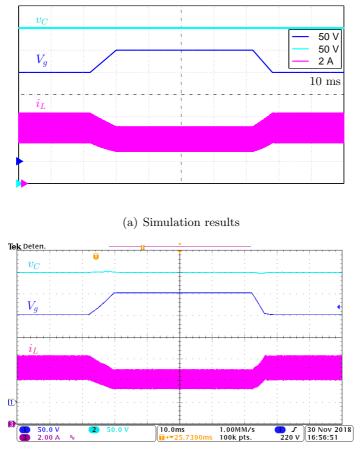

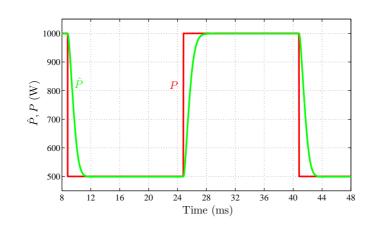

| 3 17 | Waveforms of the boost converter for power changes of step type in the                                                             | 02  |

| 0.17 | CPL (from 1 kW to 500 W and restored back to 1 kW).                                                                                | 53  |

| 2 10 | Simulation waveforms of the converter for input voltage $V_q$ changes from                                                         | 00  |

| 3.10 |                                                                                                                                    | F 4 |

|      | 200 V to 250 V at 92 ms and from 250 V to 200 V at 108 ms. $\ldots$                                                                | 54  |

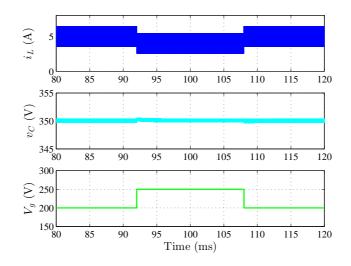

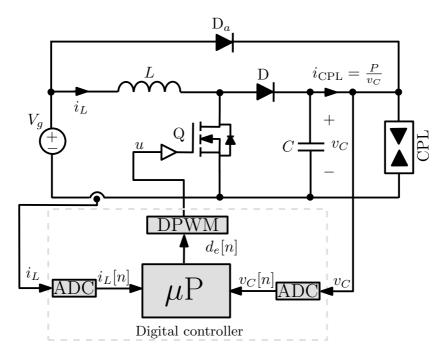

| 4.1  | Schematic circuit diagram of a boost converter with CPL                                                                            | 57  |

| 4.2  | Control scheme with a two-loop voltage regulation.                                                                                 | 58  |

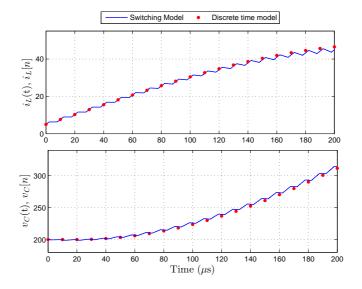

| 4.3  | Comparison between the evolution of the state variables from the approx-                                                           |     |

|      | imate discrete-time model and from the switched model implemented                                                                  |     |

|      | in $\text{PSIM}^{\textcircled{O}}$ software for the parameter values given by Table 3.1 and                                        |     |

|      | $d_e[n] = D_e = 0.5. \dots $ | 60  |

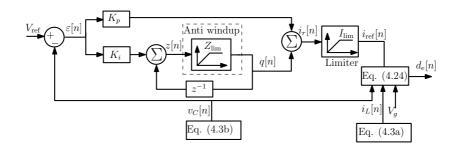

| 4.4  | Block diagram of the large-signal model of the system with a double                                                                |     |

|      | control loop based on the proposed DSMC.                                                                                           | 67  |

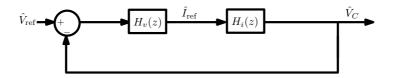

| 4.5  | Block diagram of the $z$ -domain small-signal model                                                                                | 67  |

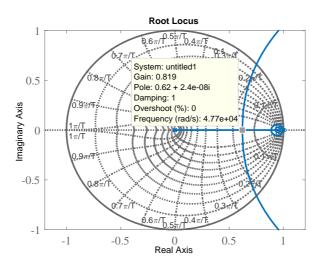

| 4.6  | Root locus of the system. At the double pole position $z_{\rm ba} \approx 0.62 + 0j$ ,                                             |     |

|      | marked by a square on the real axis, the gain $K_{p,ba} = 0.82$ according                                                          |     |

|      | to (4.31a) and (4.31b) leading theoretically to damping coefficient $\zeta = 1$                                                    |     |

|      | and null overshoot.                                                                                                                | 70  |

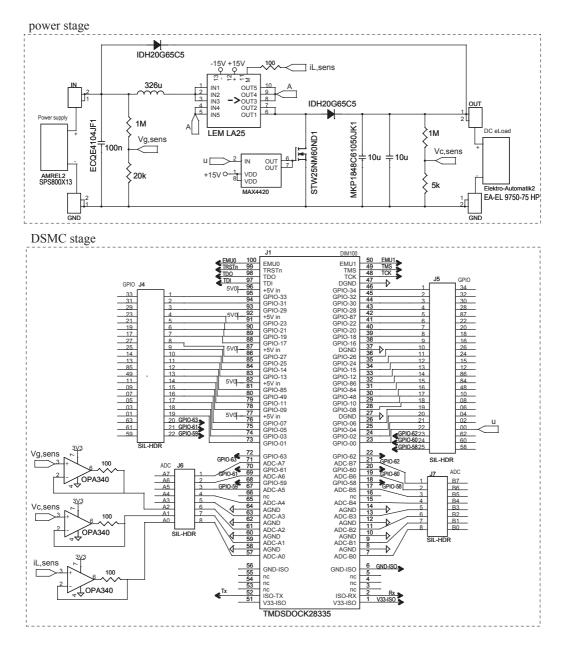

| 4.7  | Schematic diagram of the implemented experimental prototype                                                                        | 71  |

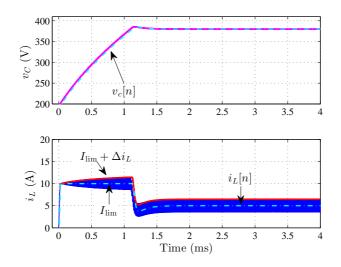

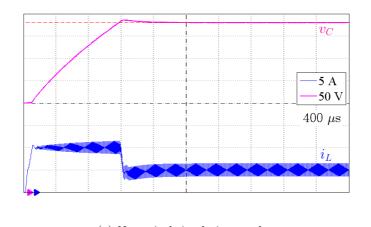

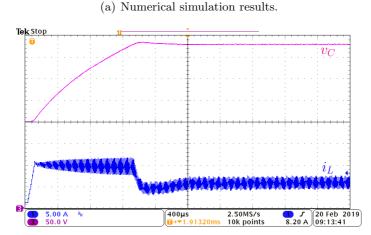

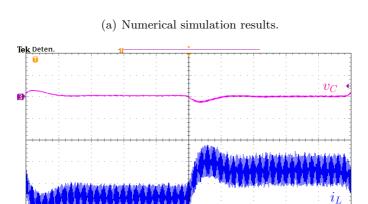

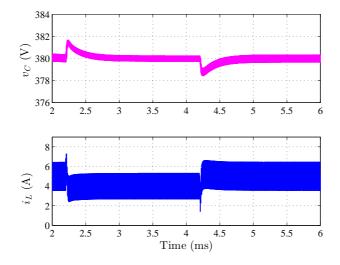

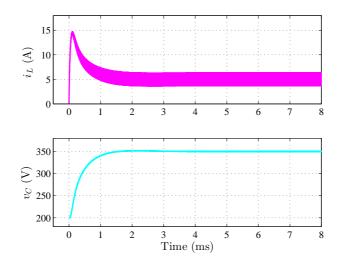

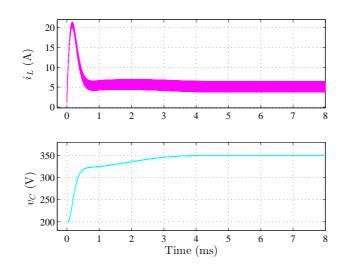

| 4.8  | Start-up and steady-state response from numerical simulations and from                                                             |     |

|      | the discrete-time model.                                                                                                           | 72  |

| 4.9  | Start-up and steady-state of the system.                                                                                           | 74  |

| 4.10 | Start-up and steady-state responses of the system from experimental                                                                |     |

|      | measurements with slope limiter $\frac{di_{ref}}{dt}\Big _{lim} = 100 \text{ kA/s.} \dots \dots$                                   | 75  |

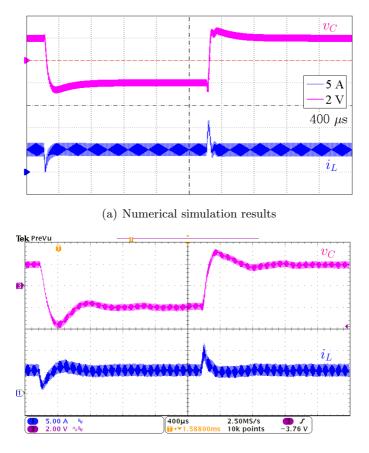

| 4.11 | Small-signal transient response in front of a $\pm 4$ V step change between                                                        |     |

|      | 378 V and 382 V in the reference voltage.                                                                                          | 76  |

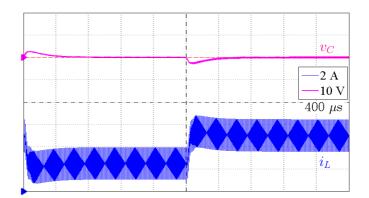

| 4.12 | Small-signal transient response in front of 50% step change in the nom-                                                            |     |

|      | inal power.                                                                                                                        | 77  |

| 4.13 | Small-signal transient response in front of a $20\%$ step change in the input     |    |

|------|-----------------------------------------------------------------------------------|----|

|      | voltage from numerical simulations.                                               | 78 |

| 5.1  | Schematic block diagram of the PWM nonlinear control of a boost con-              |    |

|      | verter with CPL                                                                   | 81 |

| 5.2  | Slopes of $N_1(K_{p_e})$ and $D_1(K_{p_e})$                                       | 85 |

| 5.3  | Parametric region for stability in the plane $K_{p_e} - K_{i_e}$                  | 86 |

| 5.4  | PRS in the plane $K_{p_e}$ - $K_{i_e}$ for the proposed system                    | 87 |

| 5.5  | Circuit schematic of the prototype of the boost converter with the pro-           |    |

|      | posed nonlinear PWM control                                                       | 88 |

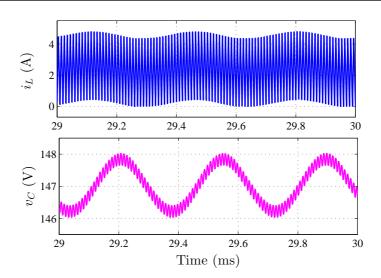

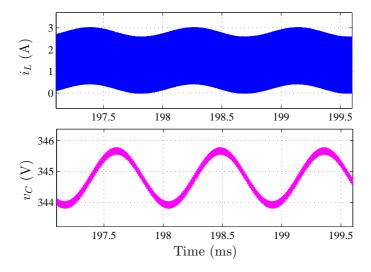

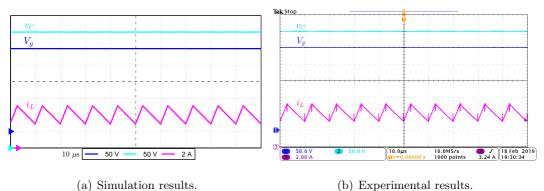

| 5.6  | Simulated waveforms of the inductor current and the capacitor voltage             |    |

|      | of the boost converter with CPL under the proposed PWM nonlinear                  |    |

|      | control                                                                           | 89 |

| 5.7  | Measured transient response in front of input voltage changes from 200 V $$       |    |

|      | to 250 V and restored back. $\ldots$                                              | 90 |

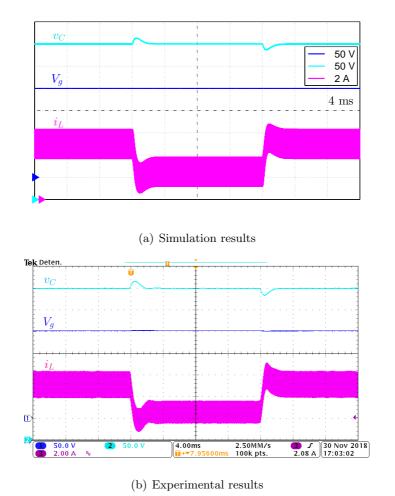

| 5.8  | Measured transient response in front of load changes from 1 kW to                 |    |

|      | $0.5~\mathrm{kW}$ and restored back. $\ldots$                                     | 91 |

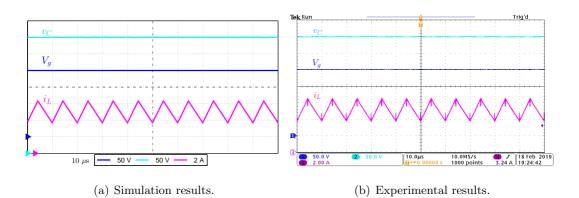

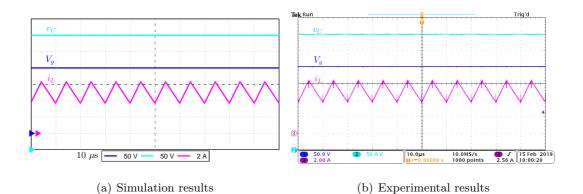

| 5.9  | Steady-state of the converter for $V_g = 200$ V and $f_s = 100$ kHz               | 92 |

| 5.10 | Steady-state of the converter for $V_g = 250$ V and $f_s = 100$ kHz               | 92 |

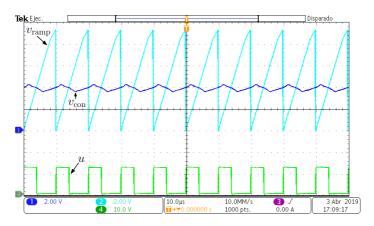

| 5.11 | Control and sawtooth signals in steady-state.                                     | 93 |

| 5.12 | Block diagram of a boost converter feeding a CPL under the proposed               |    |

|      | nonlinear PWM control and power estimation.                                       | 94 |

| 5.13 | Slopes of $N_2(K_p)$ and $D_2(K_p)$                                               | 99 |

| 5.14 | Parametric region for stability in the plane $K_p - K_E$                          | 00 |

| 5.15 | PRS in the plane $K_p - K_E$ for the proposed system                              | 01 |

| 5.16 | Circuit schematic of the boost converter with the proposed PWM adap-              |    |

|      | tive control. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$  | 02 |

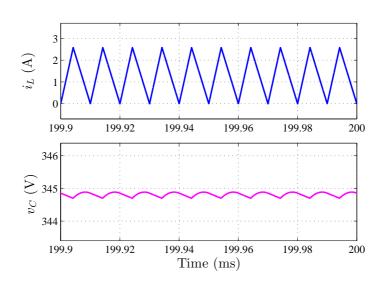

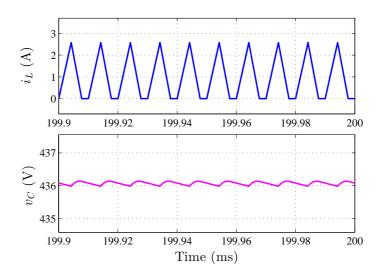

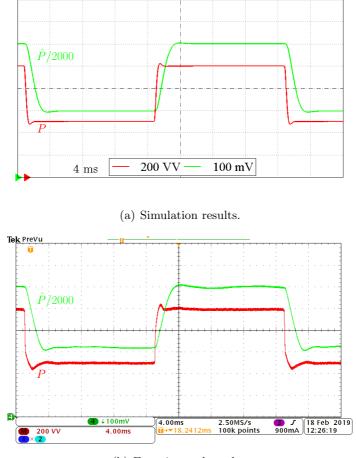

| 5.17 | Simulated waveforms of the inductor current and the capacitor voltage             |    |

|      | of the boost converter feeding a CPL with the proposed control. $\ . \ . \ . \ 1$ | 03 |

| 5.18 | Measured transient response in front of input voltage changes from 200 V $$       |    |

|      | to 250 V and restored back                                                        | 04 |

| 5.19 Measured transient response in front of load changes from 1 kW to                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| $0.5 \text{ kW}$ and restored back. $\ldots \ldots 105$ |

| 5.20 Steady-state of the converter for $V_g = 200$ V and $f_s = 100$ kHz $\ldots$ 106                                                       |

| 5.21 Steady-state of the converter for $V_g = 250$ V and $f_s = 100$ kHz $\ldots$ 106                                                       |

| 5.22 Numerical simulation of the power estimation without resistive losses 107                                                              |

| 5.23 Effect of the resistive losses on the output power estimation 108                                                                      |

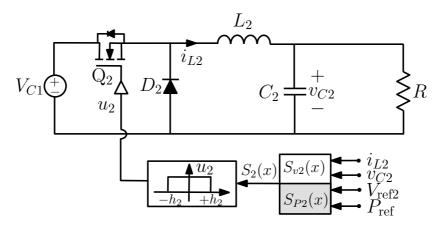

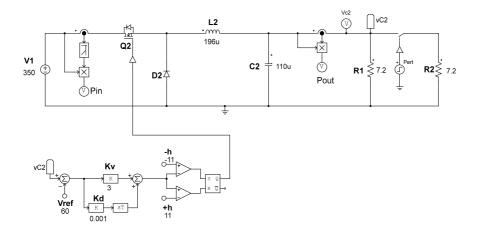

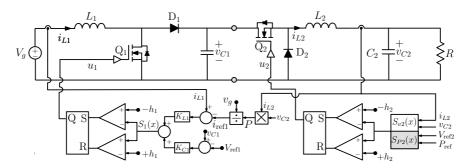

| 6.1 Buck-converter-based CPL with the proposed SM control                                                                                   |

| $6.2$ PSIM <sup><math>\odot</math></sup> schematic circuit diagram of the buck converter with the pro-                                      |

| posed power reference sliding surface $S_{P2}(x)$                                                                                           |

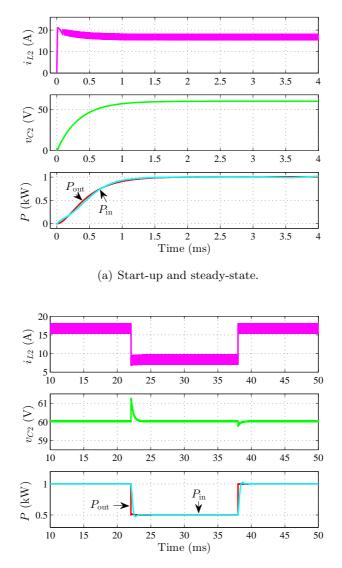

| 6.3 Start-up and steady-state of the buck converter operating as instanta-                                                                  |

| neous CPL under the power reference sliding function $S_{P2}(x)$ 115                                                                        |

| 6.4 Numerical simulation of the transient response of the buck converter in                                                                 |

| front of changes of step type in $P_{\rm ref}$                                                                                              |

| $6.5$ PSIM <sup><math>\odot</math></sup> schematic circuit diagram of the buck converter with the sliding                                   |

| surface $S_{v2}(x)$                                                                                                                         |

| 6.6 Buck converter behavior as an instantaneous CPL under sliding function                                                                  |

| $S_{v2}(x)$                                                                                                                                 |

| 6.7 Schematic circuit of the implemented experimental prototype of the buck                                                                 |

| converter under sliding function $S_{P2}$                                                                                                   |

| 6.8 Schematic circuit of the implemented experimental prototype of the buck                                                                 |

| converter under sliding function $S_{v2}$                                                                                                   |

| 6.9 Cascade connection of two converters employing SMC: boost converter                                                                     |

| (source) and buck converter (load)                                                                                                          |

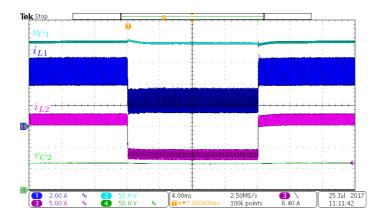

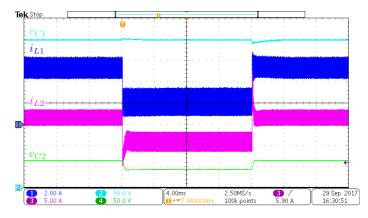

| 6.10 Measured transient response of the boost-buck cascade connection for                                                                   |

| load changes of step-type in the power from 1 kW to 0.5 kW and back                                                                         |

| to 1 kW                                                                                                                                     |

| 6.11 Block diagram of dc-dc switching converter with CPL characteristic $124$                                                               |

| 6.12 Schematic circuit diagram of converter candidates to operate as CPL. a)                                                                |

| boost converter, b) Ćuk converter, c) transformerless SEPIC converter,                                                                      |

| d) BOF converter and e) buck converter with input filter $\ldots \ldots \ldots 126$                                                         |

| 6.13 | Behavior of the conversion gain $M(D)$ of the SEPIC converter with                               |     |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | respect to $D$                                                                                   | 134 |

| 6.14 | $\mathrm{PSIM}^{\textcircled{C}}$ schematic circuit diagram of the boost converter with the pro- |     |

|      | posed SMC                                                                                        | 141 |

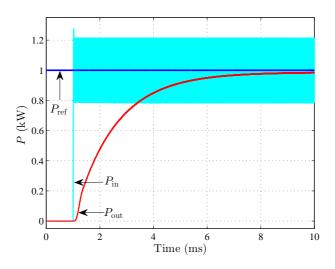

| 6.15 | Numerical simulation of the boost converter operating as an instanta-                            |     |

|      | neous CPL                                                                                        | 142 |

| 6.16 | $\mathrm{PSIM}^{\textcircled{C}}$ schematic circuit diagram of the Ćuk converter with the pro-   |     |

|      | posed SMC.                                                                                       | 143 |

| 6.17 | Numerical simulations of the Ćuk converter behavior as an instantaneous                          |     |

|      | CPL                                                                                              | 145 |

| 6.18 | $\mathrm{PSIM}^{\textcircled{C}}$ schematic circuit diagram of the SEPIC converter with the pro- |     |

|      | posed SMC.                                                                                       | 146 |

| 6.19 | SEPIC converter behavior as an instantaneous CPL                                                 | 147 |

| 6.20 | Schematic circuit diagram of the implemented control                                             | 148 |

| 6.21 | Waveforms of the input, reference and output powers of the proposed                              |     |

|      | converters operating as instantaneous CPLs during the start-up and in                            |     |

|      | steady-state                                                                                     | 150 |

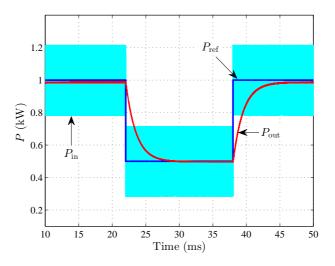

| 6.22 | Transient response of input, reference and output powers of the proposed                         |     |

|      | converters in front of changes on $P_{\text{ref}}$                                               | 151 |

# List of Tables

| 2.1 | Summary of parameter values for the buck converter with CPL 24          |

|-----|-------------------------------------------------------------------------|

| 2.2 | Summary of parameter values for the boost converter with CPL 26         |

| 3.1 | The used parameter values for the boost converter supplying a constant  |

|     | power                                                                   |

| 3.2 | Different combinations of $K_L$ and $K_C$ corresponding to Fig. 3.12 46 |

| 3.3 | Summary of components used for the boost converter                      |

| 6.1 | Used parameter values for the buck converter                            |

| 6.2 | Summary of components used for the experimental prototype of the buck   |

|     | converter operating as CPL                                              |

| 6.3 | Used parameter values for the boost converter                           |

| 6.4 | Summary of components used for the experimental prototype of the con-   |

|     | verters operating as CPLs                                               |

#### LIST OF TABLES

# Nomenclature: acronyms, parameters, symbols and variables

#### Acronyms

- ADC Analog-Digital Converter

- BOF Boost with Output Filter

- CCM Continuous Conduction Mode

- CMC Current-Mode Control

- CPL Constant Power Load

- DCM Discontinuous Conduction Mode

- DPWM Didital Pulse Width Modulation

- DSMC Digital Sliding-Mode Control

- DSP Digital Signal Processor

- EP Equilibrium Point

- EPL Equilibrium Point Locus

- ESM Existence Sliding-Mode

- ESR Equivalent Series Resistance

#### Nomenclature: acronyms, parameters, symbols and variables

| EV   | Electric vehicle                     |

|------|--------------------------------------|

| IC   | Integrated Circuit                   |

| LHP  | Left Half-plane                      |

| PCB  | Print Circuit Board                  |

| PD   | Proportional Derivative              |

| PI   | Proportional Integral                |

| POPI | Power Output is equal to Power Input |

| РР   | Polypropylene                        |

| PRS  | Parametric Region of Stability       |

| PWM  | Pulse Width Modulation               |

| RHP  | Right Half-plane                     |

| SMC  | Sliding-Mode Control                 |

| VMC  | Voltage-Mode Control                 |

#### Parameters

- C Capacitance

- *L* Inductance

- *R* Resistance

#### Symbols

- D Diode

- $D_a$  Auxiliary start-up diode

- Q MOSFET

#### Variables

#### Nomenclature: acronyms, parameters, symbols and variables

| D                       | The steady-state of the duty cycle                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------|

| d                       | The duty cycle in continuous-time                                                                           |

| $d_e$                   | The duty cycle in discrete-time                                                                             |

| $i_{\rm CPL}$           | The current of the CPL                                                                                      |

| $\hat{i}_L$             | The incremental value of the continuous-time variable of the inductor current $i_L$                         |

| $\overline{i}_L$        | Continuous-time variable representing the average value of the inductor current $i_L$ in a switching cycle  |

| $i_L$                   | Continuous-time variable of the inductor current                                                            |

| $i_L[n]$                | The sample of the continuous-time variable of the inductor current                                          |

| $I_L^*$                 | The steady-state average value of the inductor current                                                      |

| $i_{\rm ref}$           | The inductor current reference in continuous-time                                                           |

| $i_{\rm ref}[n]$        | The inductor current reference in discrete-time                                                             |

| Р                       | The power of the CPL                                                                                        |

| $\hat{P}$               | The estimated power                                                                                         |

| $P_{\min_{\text{CCM}}}$ | The minimum power value delivered by the converter in CCM operation                                         |

| $T_{\rm OFF}$           | The non conduction time of the switch Q                                                                     |

| $T_{\rm on}$            | The conduction time of the switch Q                                                                         |

| $u_{eq}$                | The equivalent control                                                                                      |

| $\hat{v}_C$             | The incremental value of the continuous-time variable of the capacitor voltage $v_C$                        |

| $\overline{v}_C$        | Continuous-time variable representing the average value of the capacitor voltage $v_C$ in a switching cycle |

#### Nomenclature: acronyms, parameters, symbols and variables

$v_C$ Continuous-time variable of the capacitor voltage $v_C[n]$ The sample of the continuous-time variable of the capacitor voltage $V_C^*$ The steady-state of the capacitor voltage $V_g$ The input voltage $V_{ref}$ The capacitor voltage reference

## Chapter 1

## Introduction

Multiconverter systems are usually employed in modern electric vehicles (EV) [1-5], sea and undersea vehicles [6-10] or dc micro-grids [11-14] involving a great number of interconnected converters [15]. The key element in these systems is a dc bus, which performs the power distribution to supply both dc and ac loads using the energy provided by the different dc sources, *i.e.* batteries, fuel cells, photovoltaic generators and ultra-capacitors.

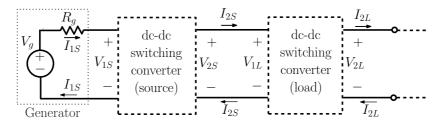

Besides the series and parallel connections in both converter ports or in only one of them, and the particular case of paralleling operation due to interleaving, cascade connection is a relevant example of association. It consists in connecting the output port of the first converter to the input port of the second one. The first stage is called source converter while the second one is denominated load converter, as is illustrated in Fig. 1.1.

Figure 1.1: Cascade connection of power converters.

#### Chapter 1. Introduction

### 1.1 Constant Power Load Definition

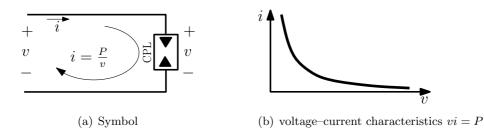

A particular case of the cascade connection is characterized by the operation of the load converter absorbing constant power or, equivalently, by the operation of the source converter supplying a constant power load (CPL) [1, 3, 13, 15–18].

A CPL can be defined as one-port device with a voltage-current characteristics given by

$$vi = P, \qquad P \in \mathbb{R}^+, \ i \in \mathbb{R}^+, \ v \in \mathbb{R}^+$$

(1.1)

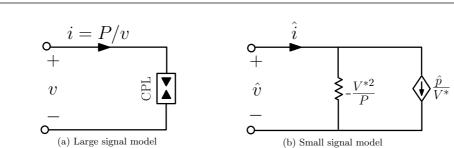

The symbol of a CPL is a power sink as shown in Fig. 1.2(a), where the current absorbed by the sink is expressed as i = P/v. Fig. 1.2(b), in turn, depicts the corresponding voltage-current characteristics of the CPL.

Figure 1.2: CPL definition.

#### 1.2 Risk of Instability

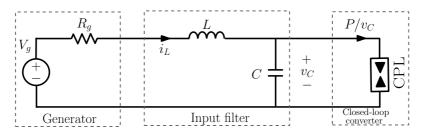

It is well-known that a dc-dc switching converter with ideal regulation at the output, *i.e.*, infinite bandwidth and 100% power conversion efficiency can result in unstable behavior when combined with an input filter [19, 20]. This phenomenon was reviewed in [16] by modelling for the first time an ideally regulated high efficiency power converter by means of a CPL. This case is reproduced in this section for the sake of illustrating the risk of instability that emerges in the supply of a CPL.

Fig. 1.3 depicts a model of a high efficient converter in closed-loop combined with a second order LC input filter. The resistance  $R_q$  represents the losses. The state

#### 1.2 Risk of Instability

equations of the system in Fig. 1.3 can be expressed as follows

$$\frac{di_L}{dt} = \frac{1}{L} \left( V_g - R_g i_L - v_C \right) \tag{1.2}$$

$$\frac{dv_C}{dt} = \frac{1}{C} \left( i_L - \frac{P}{v_C} \right) \tag{1.3}$$

The coordinates of the equilibrium point of (1.2)-(1.3) are given by

$$I_L^* = \frac{P}{V_C^*} \tag{1.4}$$

$$V_C^* = \frac{V_g}{2} \pm \sqrt{\left(\frac{V_g}{2}\right)^2 - R_g P}$$

(1.5)

Figure 1.3: Model of an ideally regulated high efficient converter with input filter.

Note from (1.5) that,

Case 1

$$\left(\frac{V_g}{2}\right)^2 > R_g P$$

implies two equilibrium points (1.6)

Case 2

$$\left(\frac{V_g}{2}\right)^2 = R_g P$$

implies one equilibrium point (1.7)

Case 3

$$\left(\frac{V_g}{2}\right)^2 < R_g P$$

implies no equilibrium point (1.8)

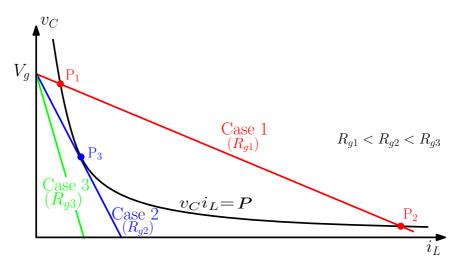

The above conditions can be interpreted geometrically in the plane  $i_L - v_C$  by representing the equations (1.2)-(1.3) in the equilibrium as illustrated in Fig. 1.4.

Equations (1.2) and (1.3) can be expressed in equilibrium as follows

$$v_C = V_g - R_g i_L \tag{1.9}$$

$$v_C i_L = P \tag{1.10}$$

#### Chapter 1. Introduction

Equations (1.9) and (1.10) are plotted in Fig. 1.4 to illustrate conditions (1.6)-(1.8) for different values of  $R_g$ . Note that condition (1.6) corresponds to Case 1, condition (1.7) to Case 2 and condition (1.8) to Case 3.

Figure 1.4: Intersection of CPL characteristic curve and load line.

Besides, determining the existence of equilibrium point in (1.2)-(1.3), the study of their stability has to be subsequently considered. Let  $v_C = V_C^* + \hat{v}_C$  and  $i_L = I_L^* + \hat{i}_L$ . Then, linearizing equations (1.2)-(1.3) around the equilibrium point given by (1.4)-(1.5) results in the following small-signal model

$$\frac{d\hat{i}_L}{dt} = -\frac{R_g}{L}\hat{i}_L - \frac{1}{L}\hat{v}_C + \frac{1}{L}\hat{V}_g$$

(1.11)

$$\frac{d\hat{v}_C}{dt} = \frac{1}{C}\hat{i}_L + \frac{P}{CV_C^{*2}}\hat{v}_C \tag{1.12}$$

The characteristic equation corresponding to (1.11)-(1.12) is given by

$$s^{2} + s\left(\frac{R_{g}}{L} - \frac{P}{CV_{C}^{*2}}\right) + \frac{1}{LC} = 0$$

(1.13)

Therefore, the small-signal dynamics (1.11)-(1.12) will correspond to a stable system if the following condition is satisfied

$$R_g > \frac{L}{C} \frac{P}{V_C^{*2}} \tag{1.14}$$

#### 1.3 Dc-dc Switching Converters in CCM Loaded with a CPL

On the other hand, from (1.6)-(1.7), the existence of equilibrium point requires

$$R_g \leqslant \frac{V_g^2}{4P} \tag{1.15}$$

Finally, conditions (1.14) and (1.15) can be written as a single expression

$$\frac{L}{C}\frac{P}{V_C^{*2}} < R_g \leqslant \frac{V_g^2}{4P} \tag{1.16}$$

Note that constraint (1.16) can be expressed in terms of the maximum allowed power  $P_{\text{max}}$  for a given set of values of L, C,  $V_g$ ,  $R_g$  and  $V_C^*$  as follows

$$P_{\max} = \min\left(\frac{V_C^{*2}R_g}{L/C}, \frac{V_g^2}{4R_g}\right)$$

(1.17)

It can be concluded from the analysis above that the cascade connection of an input filter and a tightly regulated high efficient converter is prone to instability for power values higher than a certain bound  $P_{\rm max}$ .

### 1.3 Dc-dc Switching Converters in CCM Loaded with a CPL

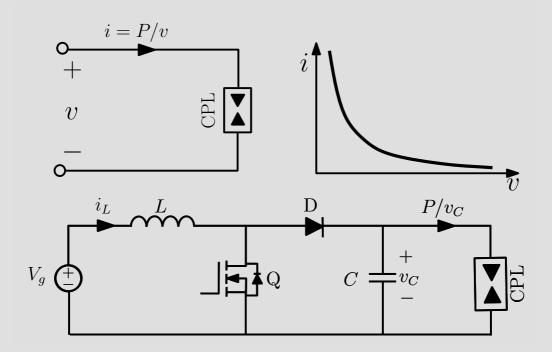

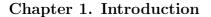

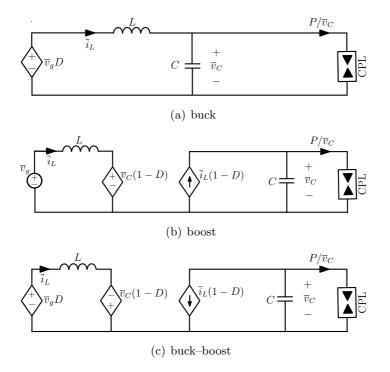

Instead of modelling an ideally regulated high efficient converter by means of a CPL, it seems now pertinent to refine our approach by exploring the behavior of the converter configurations. In other words, we analyze in this section the effect of the CPL in the ON and OFF behavior of the converter in continuous conduction mode (CCM). With this aim, Fig. 1.5 illustrates the canonical converters loaded with a CPL. UNIVERSITAT ROVIRA I VIRGILI NONLINEAR CONTROL OF DC-DC SWITCHING CONVERTERS WITH CONSTANT POWER LOAD Blanca Areli Martínez Treviño

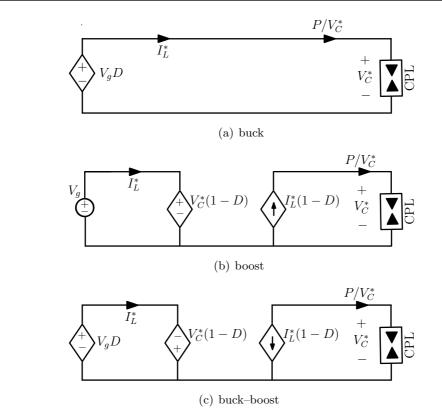

Figure 1.5: Elementary converters loaded with CPL.

By simple analysis, it is found that the output voltage of the buck converter can be expressed as

$$\frac{d^2 v_C}{dt^2} - \frac{P}{v_C^2 C} \frac{dv_C}{dt} + \frac{v_C}{CL} = \frac{V_g}{CL} u \tag{1.18}$$

where u is a binary signal, such that u = 1 during the conduction time of switch Q  $(T_{\text{ON}})$  and u = 0 during the non conduction time of the same switch  $(T_{\text{OFF}})$ . It can be observed that (1.18) is a nonlinear differential equation, which results in an unbounded behavior of voltage  $v_C$  due to the negative nonlinear damping term  $-P/v_C^2C$ .

#### 1.3 Dc-dc Switching Converters in CCM Loaded with a CPL

Similarly, the output voltage dynamics in the boost converter can be expressed as

$$\frac{d^2 v_C}{dt^2} - \frac{P}{v_C^2 C} \frac{dv_C}{dt} + \frac{(1-u)^2 v_C}{CL} = \frac{(1-u)V_g}{CL}$$

(1.19)

Finally, the differential equation describing the output voltage behavior in the buck– boost converter is given by

$$\frac{d^2 v_C}{dt^2} - \frac{P}{v_C^2 C} \frac{dv_C}{dt} + \frac{(1-u)^2 v_C}{CL} = \frac{-(1-u)uV_g}{CL}$$

(1.20)

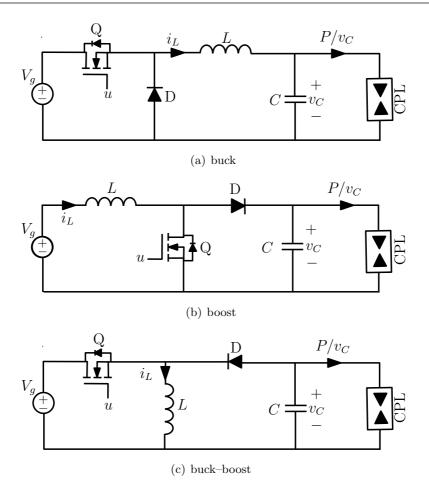

From (1.18), (1.19), (1.20) it can be concluded without loss of the generality that the behavior of the dc-dc switching converters in both ON and OFF states is unstable. Fig. 1.6 illustrates the unstable behavior of the canonical converters in ON and OFF states by showing the trajectories of the state-vector in the plane  $i_L - v_C$ .

It can be expected that the combination of both ON and OFF trajectories in any converter irrespective of the duty cycle value will result in an open unbounded trajectory.

Figure 1.6: ON and OFF trajectories corresponding to the elementary dc-dc converters with CPL.

#### Chapter 1. Introduction

### 1.4 Transfer Functions of Unstable System

The nonlinear nature of the capacitor voltage dynamics, due to its connection with the CPL, precludes the use of matrix-based analysis techniques such as the state-space averaging method [21]. This technique is based on the description of dc-dc switching converters with resistive load as piecewise-affine system because they can be expressed as follows

$$\dot{\mathbf{x}} = \mathbf{A}_i \mathbf{x} + \mathbf{B}_i V_q, \qquad i = 1, 2 \tag{1.21}$$

where **x** is the state-vector and i = 1 for ON state and i = 2 for OFF state.

Nonetheless, the CPL can be linearized around its operating point of voltage  $V^*$ and power P. Hence, from (1.1) the following expression is obtained

$$\Delta i = \frac{d(\frac{P}{v})}{dv} \Delta v + \frac{d(\frac{P}{v})}{dP} \Delta P \tag{1.22}$$

Solving the above equation, the linearizing model of a CPL is given by

$$\hat{i} = -\frac{P}{V^{*2}}\hat{v} + \frac{\hat{p}}{V^{*}} \tag{1.23}$$

The equivalent model of the CPL is depicted in Fig. 1.7. Then, the resulting negative incremental resistance can be used in a mathematical description similar to (1.21) while the current source can be considered as an external perturbation. As a result, this approach leads to modelling dc-dc switching converters with negative resistance load [22, 23]. The underlying idea is to take advantage of the state-space average predictions by assuming that a constant value of the output voltage and the inductor current only makes sense if the converter is appropriately regulated, *i.e.*, if it operates in closed-loop with a correct feedback law that can ensure the steady-state values of the state variables required in the dynamic modelling.

1.4 Transfer Functions of Unstable System

Figure 1.7: Linearization of a CPL.

Therefore, we will derive next transfer functions that represent small-signal unstable dynamic behavior in open-loop around the mentioned steady-state values, which would be ensured by the insertion of an appropriate control loop.

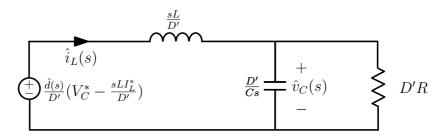

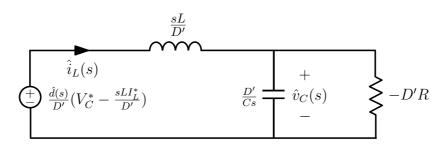

To illustrate the procedure, Fig. 1.8 shows the starting point, which is the averaged dynamic model of a boost converter with resistive load R in the case of duty cycle variations ( $\hat{d} \neq 0$ ) and constant input voltage ( $\hat{v}_g = 0$ ) [24]. Parameters  $I_L^*$  and  $V_C^*$  are the steady-state values of  $i_L$  and  $v_C$  respectively.

Figure 1.8: Small-signal average dynamic model of a boost converter with resistive load and control variations.

The model for the CPL case will be obtained by substituting R in Fig. 1.8 by -R as shown in Fig. 1.9, where the value of R is given by  $V_C^{*2}/P$  as illustrated in Fig. 1.7(b), and  $I_L^*$  is expressed as

$$I_L^* = \frac{P}{V_g} = \frac{P}{V_C^{*2}D'}$$

(1.24)

#### Chapter 1. Introduction

**Figure 1.9:** Circuit model of the small-signal dynamic behavior of a boost converter with CPL for control variations.

By simple analysis of the circuit of Fig. 1.9, the control to output voltage transfer function  $G_{vd}(s)$ , and the control to inductor current transfer function  $G_{id}(s)$  can be expressed as follows

$$G_{vd}(s) = \frac{\hat{v}_C(s)}{\hat{d}(s)} = \frac{V_C^*}{D'} \frac{1 - sL\frac{P}{V_C^{*2}D'^2}}{1 - \frac{LP}{D'^2V_C^{*2}}s + \frac{LC}{D'^2}s^2}$$

(1.25)

$$G_{id}(s) = \frac{\hat{i}_L(s)}{\hat{d}(s)} = \frac{V_C^*}{D'^2} \frac{Cs}{1 - \frac{LP}{D'^2 V_C^{*2}} s + \frac{LC}{D'^2} s^2}$$

(1.26)

It is worth mentioning that both transfer functions have poles in the right half-plane (RHP) while they differ as in the positive resistance load case in the existence or not of RHP zeros. Thus, (1.25) is as expected a non-minimum phase transfer function while (1.26) is a minimum phase transfer function.

#### 1.5 Motivation

Several methods have been proposed to cope with the mentioned CPL instability. Passive damping added to one of the filter elements in the cascade connection of a voltage source, an LC filter, and a CPL is used in [25] to stabilize the system without requiring the modification of the source or the load control. An active damping method based in the insertion of a virtual resistor and based on a supercapacitor energy storage system to compensate the negative incremental impedance of the CPL is successfully employed in [26] and [27] respectively. Feedback linearization is reported in [28] in the context of a medium voltage dc bus for power distribution on ships to compensate the nonlinearity introduced by the CPL. Active compensation has been also explored in the case of a source converter of boost type by using current control to introduce damping into the system dynamics [29, 30].

In solutions based on linear controllers, the starting point is an unstable transfer function relating either the control to output voltage or the control to inductor current. The transfer function is unstable because it is derived by simple substitution of the resistive load corresponding to a conventional supplying case by the negative incremental resistance of the CPL as it has been explained in Section 1.4 of this document. We recall that the steady-state values of the state variables required in the transfer function are the ones imposed by the closed loop behavior of the system provided that an appropriate controller stabilizes the converter. Nonetheless, the hypothesis of stable closed-loop steady-state is not achieved in some cases in spite of introducing some control loops. For example, the introduction of an inner current loop for the average value regulation of the inductor current stabilizes a boost converter with CPL but it fails in a buck converter with the same type of load as demonstrated in [31]. Only the additional introduction of an outer loop allows the system stabilization in the latter case.

In [32], a robust control approach has been considered for the elementary power switching converters with a CPL. In [33] a robust controller based on linear programming is proposed to regulate the output of buck converters loaded by another buck converter acting as a CPL.

Passivity-based control has been also explored in a buck converter with CPL [34] leading to a simple linear PD control, which provides virtual damping without affecting the system efficiency.

Sliding-mode control (SMC) [35–44] has been also studied in [45] to regulate a boost converter feeding a CPL connected in parallel with a resistive load. A switching surface made up of a linear combination of the capacitor voltage error and the difference between the inductor current and its high frequency component is used with the aim of

#### Chapter 1. Introduction

regulating the output voltage in front of load changes of step type. Simulation results have shown a good performance of the proposed control and the existence of bifurcations when the gain of the current error is used as a parameter. An SMC-based pulse width modulation (PWM) approach is employed in [46] with a nonlinear switching surface in the output voltage regulation of a boost converter supplying a CPL. The previous nonlinear switching surface is modified in [47] by including a linear term proportional to the voltage error to improve the output voltage regulation. While the first approach operates at constant switching frequency, the second one results in a highly variable switching frequency due to the action of an ideal comparator in the control loop. In the context of an island dc micro-grid, SMC-based PWM is used again satisfactorily to regulate a 380 V dc bus with multiple photovoltaic generators, several boost converters and a battery bank [48]. The same approach is used in [49] for the case of a buck-boost converter feeding a composite load (constant resistance, constant current and constant power), which is dominated by CPL, showing robustness in front of input voltage and load disturbances. A sliding-mode duty-ratio control to operate a constant switching frequency is proposed in [9, 50] for a buck converter with CPL in a ship dc bus power distribution system. Switching surfaces based either on the current error or on a linear combination of current and voltage error are used to regulate the dc bus voltage in the different modes of the system.

Moreover, also in the case of dc micro-grids, active stabilization techniques based on a combination of load shedding, additional resistive loads and other circuits have been used in [11]. Stabilization has been also achieved in the same micro-grid context by the inclusion of external circuitry emulating a capacitor as reported in [51].

On the other hand, the direct cascade connection of two buck converters where the second stage acts as a CPL, has been analyzed by means of boundary [52] or synergetic control [53] to eventually derive sufficient stability conditions and mitigate the instability effect produced by the CPL.

All contributions on the CPL subject are based on continuous-time models, the exception being the work reported in [54], where a discrete-time approach is used in the analysis of a buck converter with a fourth order output filter supplying a CPL with the aim of identifying slow-scale and fast-scale instabilities.

To summarize, most of the existing contributions are theoretical approaches exploring how to counteract the inherent instability of the CPL. Their main goal has been demonstrating the stabilizing effect of the proposed strategies without showing other important aspects such as rejection to input voltage changes or load variations, inrush current minimization and practical implementation of the control.

### 1.6 Objectives

The main goal of this research is to describe analytically the cascade connection of converters under constant power supply conditions, and propose simple control solutions that can cope with the potential instability caused by the CPL. With this aim, the use of different strategies such as linear control, SMC, digital SMC (DSMC), and nonlinear PWM control is studied in the regulation of a boost converter supplying a CPL.

The thesis is organized as follows;

Chapter 2 reexamines the analysis of the elementary converters in open-loop in the boundary between CCM and DCM carried out in reference [55].

In Chapter 3, the SMC of a boost converter feeding a CPL is exhaustingly covered by a continuous-time approach leading to an analogue implementation.

A discrete-time approach for sliding-mode control using a PWM resulting in a digital implementation is presented in Chapter 4.

Chapter 5 introduces two analogue PWM-based nonlinear controllers as alternative solutions to regulate the output voltage in constant switching frequency operation. First, the use of a virtual mesh is developed to both stabilize the converter and indirectly regulate the output voltage. Then, a mechanism to estimate the power of the CPL is presented.

Chapter 6 addresses the implementation of converters with CPL behavior by presenting a general systematic procedure of synthesis.

Finally, the conclusions of the thesis are summarized in Chapter 7.

UNIVERSITAT ROVIRA I VIRGILI NONLINEAR CONTROL OF DC-DC SWITCHING CONVERTERS WITH CONSTANT POWER LOAD Blanca Areli Martínez Treviño

Chapter 1. Introduction

## Chapter 2

## Open-loop dc-dc Converters with CPL in the Boundary CCM-DCM

### 2.1 Introduction

It has been shown in the introductory chapter that there is an upper bound for the power that a tightly regulated converter with input filter can supply. Beyond that value, stability problems or inexistence of equilibrium point can arise. Also, it has been demonstrated that the output voltage exhibits a nonlinear unstable dynamics that results in unbounded trajectories in both ON and OFF states in any converter. Thus, it has been conjectured that the combination of ON and OFF trajectories in open-loop operation would result in an open unbounded trajectory irrespective of the duty cycle.

Nonetheless, it was demonstrated in [55] that a stable behavior could be obtained in open-loop operation when the converters were working in the boundary between CCM and DCM. Like in the resistive load case, the boundary was derived in terms of the switching period, inductance value and a function of the duty cycle. However, the expression of the boundary was determined by a value of the power  $P_{\min_{CCM}}$ , which established the minimum value of the CPL power to operate in CCM for a given value of the input voltage  $V_g$ .

We can observe again that an upper bound of the power emerges to separate stable and unstable behavior, or equivalently DCM and CCM operations.

The analysis reported in [55] is reviewed in this chapter under the optics of an averaged model of the switching converter [24].

### 2.2 Average Circuit Model of the Elementary Converters with CPL in CCM

The converters shown in Fig. 1.5 can be modelled as depicted in Fig. 2.1. It has to be pointed out that both control and state variables are continuous-time functions representing the average value in a switching cycle [24] of the respective variables illustrated in Fig. 1.5. Assuming that an equilibrium point can be reached, the circuits depicted in Fig. 2.1 can be represented as illustrated in Fig. 2.2. It can be observed in all cases the POPI nature of the steady-state model as it can be expected.

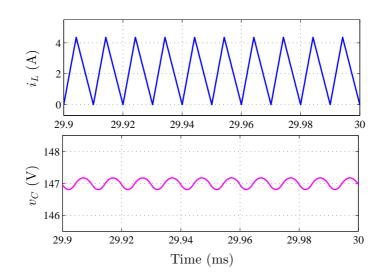

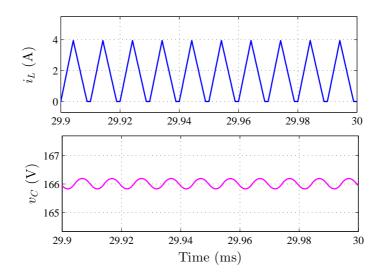

Figure 2.1: Averaged circuit model of elementary converters with CPL.

2.2 Average Circuit Model of the Elementary Converters with CPL in CCM

Figure 2.2: Steady-state model corresponding to the circuits in Fig. 2.1.

For the buck converter:

$$P_{\rm DC_{in}} = V_g D I_L^* = V_g D \frac{P}{V_C^*} = V_C^* \frac{P}{V_C^*} = P = P_{\rm DC_{out}}$$

(2.1)

For the boost converter

$$P_{\rm DC_{in}} = V_g I_L^* = (1 - D) V_C^* I_L^* = V_C^* \frac{P}{V_C^*} = P = P_{\rm DC_{out}}$$

(2.2)

For the buck-boost converter

$$P_{\rm DC_{in}} = V_g D I_L^* = -(1-D) V_C^* I_L^* = V_C^* \frac{P}{V_C^*} = P = P_{\rm DC_{out}}$$

(2.3)

### 2.3 Boundary CCM-DCM

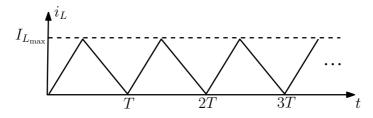

In the boundary between CCM and DCM the inductor current  $i_L$  of any elementary converter behaves in steady-state as illustrated in Fig. 2.3.

Figure 2.3: Steady-state inductor current  $i_L$  in the boundary CCM-DCM for any elementary converter.

The steady-state average value  $I_L^*$  of inductor current in any converter is related to the maximum value  $I_{L_{\text{max}}}$  as follows

$$I_L^* = \frac{I_{L_{\max}}}{2} \tag{2.4}$$

### 2.4 Minimum Power of the CPL for CCM Operation

#### 2.4.1 Buck Converter

From (2.4) the following expression is obtained for the buck converter

$$I_L^* = \frac{I_{L_{\max}}}{2} = \frac{V_g D (1-D)T}{2L} = \frac{V_g D^2 (\frac{1}{D}-1)}{2L}T = \frac{V_g D^2 (\frac{V_g}{V_C^*}-1)}{2L}T = \frac{V_g D^2 T}{2L} \frac{(V_g - V_C^*)}{V_C^*}$$

(2.5)

Hence, the power delivered by the buck converter to the CPL in the boundary CCM-DCM will be

$$P_{\min_{CCM}} = V_C^* I_L^* = \frac{V_g D^2 T (V_g - V_C^*)}{2L} = \frac{V_g^2 D^2 T}{2L} (1 - D)$$

(2.6)

#### 2.4 Minimum Power of the CPL for CCM Operation

#### 2.4.2 Boost Converter

Similarly, expression (2.4) becomes in the boost converter

$$I_L^* = \frac{V_g DT}{2L} \tag{2.7}$$

The power delivered by the converter to the CPL in the boundary CCM-DCM is

$$P_{\min_{CCM}} = V_C^* I_L^* (1-D) = \frac{V_C^* V_g D (1-D) T}{2L} = \frac{V_g^2 D T}{2L}$$

(2.8)

#### 2.4.3 Buck-Boost Converter

Note that expression (2.7) also applies for the buck-boost converter, so the value of  $P_{\min_{\text{CCM}}}$  will be

$$P_{\rm min_{\rm CCM}} = -V_C^* I_L^* (1-D) = V_g D I_L^* = \frac{V_g^2 D^2 T}{2L}$$

(2.9)

#### 2.4.4 Comparison of Minimum Values of Power

Expressions (2.6), (2.8) and (2.9) can be compared taking the minimum value of power in the buck-boost as a reference case. Defining

$$P_{\min_{\text{CCM(buck-boost)}}} = \frac{V_g^2 D^2 T}{2L} \triangleq P_{\text{critical}}, \qquad (2.10)$$

it can be observed that

$$P_{\min_{\text{CCM(buck)}}} = \frac{V_g^2 D^2 T}{2L} (1 - D) = P_{\text{critical}} (1 - D) < P_{\text{critical}}$$

(2.11)

and

$$P_{\min_{\text{CCM(boost)}}} = \frac{V_g^2 DT}{2L} = \frac{P_{\text{critical}}}{D} > P_{\text{critical}}$$

(2.12)

### 2.5 Stability of the Equilibrium Point in the Boundary CCM-DCM

#### 2.5.1 Buck Converter Case

We consider now the dynamic behavior of the buck converter shown in Fig. 2.1(a). The dynamics of the output port can be expressed as

$$\bar{i}_L = \frac{Cd\bar{v}_C}{dt} + \frac{P}{\bar{v}_C}$$

(2.13)

From (2.4), the dynamic behavior of  $i_L$  in continuous-time becomes as follows

$$\bar{i}_L = \frac{V_g D^2 T}{2L} \frac{(V_g - \bar{v}_C)}{\bar{v}_C}$$

(2.14)

Introducing (2.14) in (2.13) leads to

$$\frac{V_g D^2 T}{2L} \left( \frac{V_g - \overline{v}_C}{\overline{v}_C} \right) - \frac{P}{\overline{v}_C} = \frac{C d\overline{v}_C}{dt}$$

(2.15)

In equilibrium

$$\frac{d\overline{v}_C}{dt} = 0, \qquad v_C = V_C^* \tag{2.16}$$

Hence,

$$\frac{V_g D^2 T}{2L} \left( V_g - V_C^* \right) = P \tag{2.17}$$

or equivalently,

$$V_C^* = V_g - \frac{2LP}{V_g D^2 T}$$

(2.18)

Observe that the existence of equilibrium point in (2.18) implies that

$$V_g > \frac{2LP}{V_g D^2 T} \tag{2.19}$$

Equivalently

$$P < \frac{V_g^2 D^2 T}{2L} \tag{2.20}$$

Note that (2.20) is exactly condition (2.11). Therefore, there always will be an equilibrium point in a buck-converter feeding a CPL in the boundary CCM-DCM.

#### 2.5 Stability of the Equilibrium Point in the Boundary CCM-DCM

To analyze the stability of the equilibrium point we will assume in (2.15),  $\overline{v}_C = V_C^* + \Delta v_C$ , so that  $|\Delta v_C| < V_C^*$ .

Therefore, (2.15) becomes

$$\frac{V_g D^2 T}{2L} \left( \frac{V_g - V_C^* - \Delta v_C}{V_C^* + \Delta v_C} \right) - \frac{P}{V_C^* + \Delta v_C} = C \frac{d(\Delta v_C)}{dt}$$

(2.21)

After a simple manipulation, (2.21) becomes

$$\frac{d(\Delta v_C)}{dt} = -\frac{V_g D^2 T}{2LC} \frac{\Delta v_C}{V_C^* + \Delta v_C}$$

(2.22)

It can be observed in (2.22) that

$$\Delta v_C > 0$$

implies  $\frac{d(\Delta v_C)}{dt} < 0$  (2.23)

$$\Delta v_C < 0 \quad \text{implies} \quad \frac{d(\Delta v_C)}{dt} > 0,$$

(2.24)

As consequence, it can be concluded that the equilibrium point (2.18) exists and is stable.

#### 2.5.2 Boost Converter Case

The output port dynamics of the boost converter is given by

$$\bar{i}_L(1-D) = C \frac{d\bar{v}_C}{dt} + \frac{P}{\bar{v}_C}$$

(2.25)

Following a similar procedure to the one developed in the buck converter case, the dynamic behavior of variable  $\bar{i}_L$  will be given by

$$\bar{i}_L = \frac{V_g DT}{2L} \tag{2.26}$$

On the other hand, we can also write

$$\bar{i}_L(1-D) = \frac{V_g^2 T}{2L} \frac{D}{\bar{v}_C} = \frac{V_g^2 T D^2}{2L(\bar{v}_C - V_g)}$$

(2.27)

Hence, (2.25) becomes

$$\frac{V_g^2 T}{2L} \frac{D^2}{\overline{v}_C - V_g} = C \frac{d\overline{v}_C}{dt} + \frac{P}{\overline{v}_C}$$

(2.28)

In equilibrium condition (2.16) applies. Hence,

$$\frac{V_g^2 T D^2}{2L} \frac{V_C^*}{V_C^* - V_g} = P \tag{2.29}$$

Solving for  $V_C^*$  in (2.29), we obtain

$$V_C^* = \frac{PV_g 2L}{2LP - V_q^2 T D^2}$$

(2.30)

The existence of equilibrium point given by (2.30) requires that

$$P > \frac{V_g^2 T D^2}{2L},\tag{2.31}$$

which is exactly condition (2.12). Therefore, there exists an equilibrium point in a boost converter supplying a CPL in the boundary CCM-DCM.

Assuming in (2.28)  $\overline{v}_C = V_C^* + \Delta v_C$ , such that  $|\Delta v_C| < V_C^* - V_g$ , we derive from (2.28)

$$\frac{V_g^2 T}{2L} \frac{D^2}{V_C^* + \Delta v_C - V_g} = C \frac{d(\Delta v_C)}{dt} + \frac{P}{V_C^* + \Delta v_C}$$

(2.32)

After a simple manipulation, we obtain

$$C\frac{d(\Delta v_C)}{dt} = -\frac{\Delta v_C (2LP - V_g^2 T D^2)}{2L(V_C^* + \Delta v_C - V_g)(V_C^* + \Delta v_C)}$$

(2.33)

Note that again conditions (2.23) and (2.24) are fulfilled, so the equilibrium point given by (2.30) is stable.

#### 2.5.3 Buck-boost Converter Case.

In the boundary, the dynamics of the output capacitor voltage in the buck-boost converter is given by

$$\bar{i}_L(1-D) = -C\frac{d\bar{v}_C}{dt} - \frac{P}{\bar{v}_C}$$

(2.34)

where the dynamic behavior of variable  $\bar{i}_L$  is also given by expression (2.26).

Therefore, we can write

$$\bar{i}_L(1-D) = \frac{V_g}{2L}D(1-D) = \frac{-V_g^2 D^2 T}{2L\bar{v}_C}$$

(2.35)

#### 2.5 Stability of the Equilibrium Point in the Boundary CCM-DCM

Introducing (2.35) in (2.34) leads to

$$\frac{V_g^2 T}{2L} \frac{D^2}{\overline{v}_C} = C \frac{d\overline{v}_C}{dt} + \frac{P}{\overline{v}_C}$$

(2.36)

Equivalently,

$$C\overline{v}_C \frac{d\overline{v}_C}{dt} = \frac{V_g^2 D^2 T}{2L} - P \tag{2.37}$$

Defining  $z(t) = \frac{1}{2}C\overline{v}_C^2$ , we derive

$$\frac{dz}{dt} = \frac{V_g^2 T D^2}{2L} - P = P_{\text{critical}} - P_{\text{min}_{\text{CCM}}}$$

(2.38)

From (2.10), we conclude that the right term of equation (2.38) is zero.

Hence,

$$\frac{dz}{dt} = 0 \tag{2.39}$$

Therefore

$$z(t) = \frac{1}{2}C\bar{v}_C(0)$$

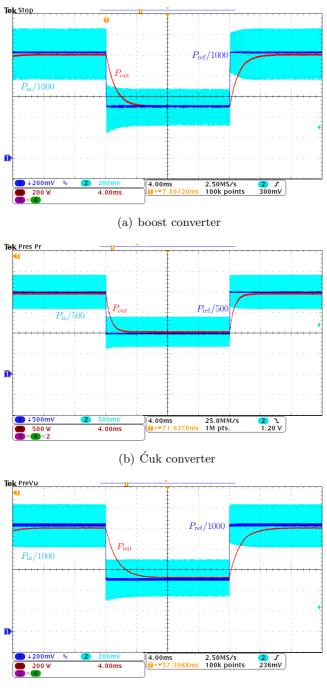

(2.40)