# Real-time digital signal processing for new wavelength-to-the-user optical access networks

### Saeed Ghasemi

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) i el repositori cooperatiu TDX (<a href="http://www.ttdx.cat/">http://www.ttdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA** La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual **únicamente para usos privados enmarcados** en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="framing">framing</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutionalrepositionalrepositions and the cooperative repository TDX (<a href="http://www.tdx.cat/?locale-attribute=en">http://www.tdx.cat/?locale-attribute=en</a>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

#### PhD Thesis

# Real-Time Digital Signal Processing for new Wavelength-to-the-user Optical Access Networks

Author:

Saeed Ghasemi

Advisor: Prof. Josep Prat Gomà

Thesis presented in fulfilment for the degree of:

Doctor of Philosophy in

Signal Theory and Communications

At the:

Optical Communications Group (GCO)

Signal Theory and Communications Department (TSC)

Barcelona, September 2019

The work described in this thesis was performed in the Optical Communications

Group (GCO) at the Signal Theory and Communications (TSC) department of

the Universitat Politecnica de Catalunya (UPC). It was supported by FPI-Mineco

from Ministry of Economy, Industry, and Competitiveness of Spain under grant

BES-2016-077129, and Spanish project FLIPER under grant TEC2015-70835.

Saeed Ghasemi

"Real-Time Digital Signal Processing for new Wavelength-to-the-user Optical

Access Networks"

Copyright © 2019 by Saeed Ghasemi

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system, or transmitted in any form or by any means without the prior

written consent of the author.

Printed in Barcelona, Spain.

ISBN:

Reg:

## Abstract

Nowadays, optical access networks provide high capacity to end users with growing availability of multimedia contents that can be streamed to fixed or mobile devices. In this regard, one of the most flexible and low-cost approaches is Passive Optical Network (PON) that is used in Fiber-to-the-Home (FTTH). Due to the growing of the bandwidth demands, Wavelength Division Multiplexing (WDM), and later on ultra-dense WDM (udWDM) PON, with a narrow channel spacing, to increase the number of users through a single fiber, has been deployed.

The udWDM-PON with coherent technology is an attractive solution for the next generation optical access networks with advanced digital signal processing (DSP). Thanks to the higher sensitivity and improved channel selectivity in coherent detection with efficient DSP, optical networks support larger number of users in longer distances.

Since the cost is the main concern in the optical access networks, this thesis presents DSP architectures in coherent receiver (Rx), based on low-cost direct phase modulated commercial DFB lasers. The proposals are completely in agreement with consept of wavelength-to-the-user, where each client in optical network is dedicated to an individual wavelength.

Next, in a 6.25 GHz spaced udWDM grid with the optimized DSP techniques and phase-shift-keying (PSK) modulation format, the high sensitivity is achieved in real-time field-programmable-gate-array (FPGA) implementations.

Moreover, this thesis reduces hardware complexity of optical carrier recovery (CR) with two various strategies. First, based on differential  $m^{th}$ -power frequency estimator (FE) by using look-up-tables (LUTs) and second, LUT-free CR architecture, with optimizing the power consumption and hardware resources, as well as improving the channel selectivity in terms of speed and robustness.

Furthermore, by designing very simple but efficient clock recovery, a symbol-rate DSP architecture, which process data using only one sample per symbol (1-sps), for polarization diversity (POD) structure, becomes possible. It makes the DSP independent from state-of-polarization (SOP), even in the case of low-cost optical front-end and low-speed analog-to-digital converters (ADCs), keeps the performance high as well as sensitivity in real-time implementations on FPGA.

# Acknowledgements

First of all, I would like to express my appreciation and gratitude to my supervisor Prof. Josep Prat for giving me opportunity to join his team at GCO to pursue my doctoral study and develop my PhD thesis in high-level national and international research projects. His excellent supervision, guidance and patient as well as deep knowledge and practical experience, had positive influence on my study. When I faced to difficult problems which seemed unsolvable, his valuable advice, sometimes just few words, always directed me to the solution. Working with him made me stronger, not only in research, but also for the next journey of life.

A special thanks to Dr. Victor Polo, the manager of the lab for his assistance in practical experiments and nice organization of the devices and instruments. Moreover, I would like to express my warm appreciation to Jeison Tabares for his support during my PhD study. He always answered my technical questions very clear and perfect with his deep knowledge, and I learned a lot from him. Similarly, I would like to thank Juan Camilo Velasquez for his thoughtful helps in my study. Furthermore, I would like to thank the rest of GCO group, Josep Segarra, Vicent Sales, and the colleagues who left the group, among them Ivan Cano, Marc Domingo and Guangyong Chu. Besides, thanks to Rafael Montero, Samael Sarmiento and Ruben Rumipamba for their great friendship.

I would like to express my thanks to my parents Abdolali and Mastaneh, my brothers Babak and Masoud, who gave their supports during all the years of my life and study.

Finally, I want to thank FPI-Mineco from Ministry of Economy, Industry, and Competitiveness of Spain under grant BES-2016-077129, and Spanish project FLIPER under grant TEC2015-70835, for their financial support.

Last but not least, I would like to express my deepest gratitude to my beloved wife Fatima, for her kind support all the late nights and early mornings, with her absolute and unconditional love. She is my best friend and her lovely smile is my inspiration. I owe her everything.

# Contents

| Abstract.   | v                                                              |

|-------------|----------------------------------------------------------------|

| Acknowle    | edgementvii                                                    |

| List of Fig | guresxiv                                                       |

| List of Ta  | blesxix                                                        |

| Abbreviat   | ions & Acronymsxxi                                             |

| Symbols.    | xxiv                                                           |

| СНАРТЬ      | ER 1. INTRODUCTION1                                            |

| 1.1         | Thesis Objectives                                              |

| 1.2         | Thesis Outline5                                                |

| BIBLIO      | GRAPHY6                                                        |

| СНАРТЕ      | ER 2. STATE OF THE ART: OPTICAL ACCESS NETWORKS10              |

| 2.1         | Active and Passive Optical Networks                            |

| 2.1.1       | Time Division Multiplexing PON (TDM-PON)10                     |

| 2.1.2       | Wavelength Division Multiplexing PON (WDM-PON)11               |

| 2.1.3       | Ultra Dense Wavelength Division Multiplexing PON (udWDM-PON)12 |

| 2.2         | Coherent Detection                                             |

| 2.2.1       | Heterodyne Detection                                           |

| 2.2.2       | Homodyne Detection                                             |

| 2.3         | Anatomy of Digital Coherent Receivers                          |

| 2.3.1       | Optical Front-End                                              |

| 2.3.2       | Analog-To-Digital Conversion                                   |

<u>Contents</u> <u>x</u>

| 2.3.3   | Digital Signal Processing                            | 22     |

|---------|------------------------------------------------------|--------|

| 2.3.3.1 | Deskew and Orthogonalization                         | 23     |

| 2.3.3.2 | Static Equalization                                  | 24     |

| 2.3.3.3 | Adaptive Equalization                                | 25     |

| 2.3.3.4 | Clock Recovery                                       | 28     |

| 2.3.3.5 | Carrier Recovery                                     | 29     |

| 2.3.3.6 | Symbol Estimation and Decoding                       | 30     |

| 2.4     | Conclusion                                           | 31     |

| BIBLIO  | GRAPHY                                               | 31     |

| СНАРТ   | ER 3. DSP FOR INTRADYNE OPTICAL PSK RECEIVERS IN     | UDWDM- |

| PON     |                                                      | 37     |

| 3.1     | DSP for Intradyne Optical PSK Receivers              | 38     |

| 3.1.1   | Deskew                                               | 38     |

| 3.1.2   | Clock Recovery                                       | 43     |

| 3.1.2.1 | Clock Recovery without Interpolation                 | 43     |

| 3.1.2.2 | Clock Recovery with Interpolation                    | 44     |

| 3.1.3   | Normalization                                        | 46     |

| 3.1.4   | Proposed Carrier recovery (LUT-Based)                | 46     |

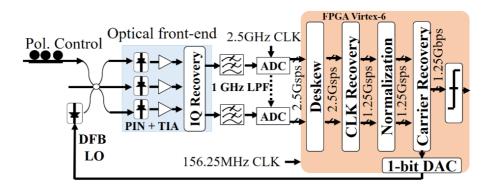

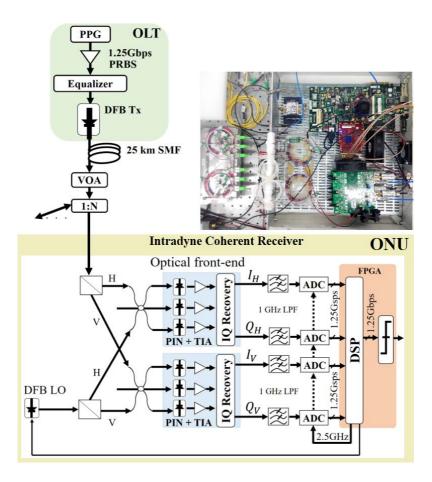

| 3.2     | Field Trial Setup                                    | 52     |

| 3.2.1   | Real-Time 1.25 Gbps Intradyne Setup                  | 54     |

| 3.2.2   | Field-Trial Results for Real-Time Intradyne Receiver | 56     |

| 3.3     | Real-Time Experimental Setup with Proposed CR        | 57     |

| 3.4     | Results with Proposed CR                             | 58     |

| 3.5     | Conclusion                                           | 65     |

<u>Contents</u> <u>xi</u>

| BIBLIO | GRAPHY                                            | 67 |

|--------|---------------------------------------------------|----|

| CHAPTI | ER 4. OPTIMIZED CARRIER RECOVERY FOR INTRADYN     | Œ  |

| OPTICA | L DPSK RECEIVER                                   | 72 |

| 4.1    | Proposed LUT-Free Carrier Recovery Architecture   | 73 |

| 4.2    | Hardware Resources                                | 76 |

| 4.3    | Real-Time Experimental Setup                      | 78 |

| 4.4    | Results                                           | 79 |

| 4.5    | Conclusion                                        | 84 |

| BIBLIO | GRAPHY                                            | 85 |

|        | ER 5. SYMBOL-RATE POLARIZATION INDEPENDENT DSP FO |    |

|        | OYNE OPTICAL M-PSK RECEIVERS IN UDWDM-PON         |    |

| 5.1    | Symbol-Rate DSP Architecture                      | 39 |

| 5.1.1  | Proposed Symbol-Rate Clock Recovery               | 39 |

| 5.1.2  | Proposed Symbol-Rate DSP                          | 93 |

| 5.2    | Experimental Results                              | 94 |

| 5.3    | Conclusion                                        | 97 |

| BIBLIO | GRAPHY                                            | 98 |

| CHAPTI | ER 6. CONCLUSIONS10                               | 01 |

| 6.1    | General Conclusion 10                             | 01 |

| 6.2    | Technical Conclusion                              | )2 |

| 6.3    | Future Works                                      | )3 |

| BIBLIO | GRAPHY10                                          | 04 |

<u>Contents</u> xii

| APPENDIX A. PUBLICATION LIST107 |                         |     |  |

|---------------------------------|-------------------------|-----|--|

| A.1                             | Jurnal Publications     | 107 |  |

| A.2                             | Conference Publications | 107 |  |

| A.3                             | Submitted Publications. | 108 |  |

# **List of Figures**

| 1.1  | Nielsen's law prediction for internet bandwidth, growing 50 % per year2     |

|------|-----------------------------------------------------------------------------|

| 2.1  | TDM-PON architecture                                                        |

| 2.2  | WDM-PON architecture                                                        |

| 2.3  | udWDM-PON application                                                       |

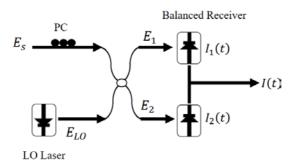

| 2.4  | Coherent detection architecture                                             |

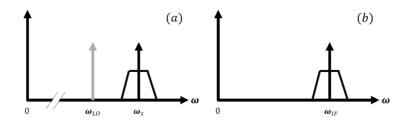

| 2.5  | Spectra of (a) the optical signal, and (b) the down-converted IF signal15   |

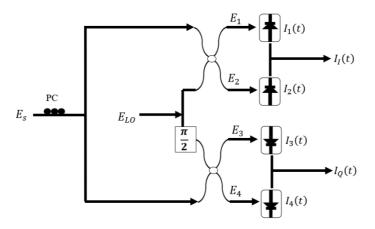

| 2.6  | Phase-diversity homodyne receiver using 90° optical hybrids16               |

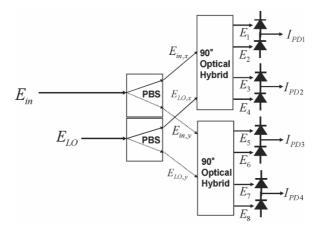

| 2.7  | Polarization diversity scheme of the intradyne receivers using 90° optical  |

|      | hybrids [8]                                                                 |

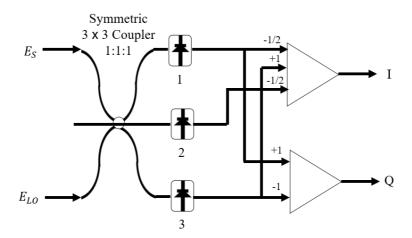

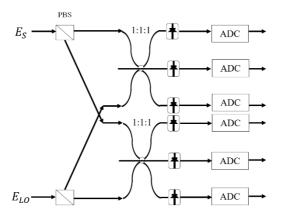

| 2.8  | Schematic of symmetric 3×3 coupler based 90° hybrids19                      |

| 2.9  | Schematic of symmetric 3×3 coupler and single-ended photo-detector20        |

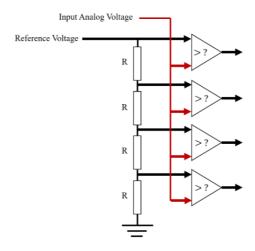

| 2.10 | Flash ADC type21                                                            |

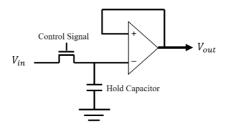

| 2.11 | Track-and-hold circuit                                                      |

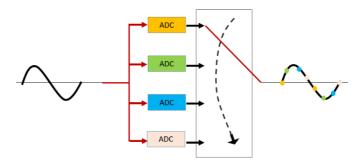

| 2.12 | Time-interleaving process to increase the analog-to-digital sampling rate22 |

| 2.13 | A conventional DSP for the coherent receivers                               |

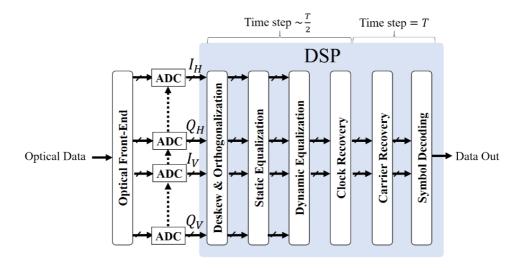

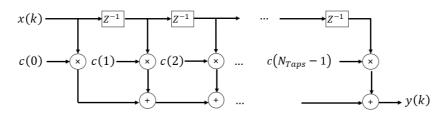

| 2.14 | FIR filter scheme in static equalization                                    |

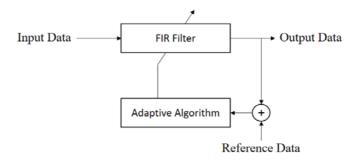

| 2.15 | Structure of an adaptive equalization                                       |

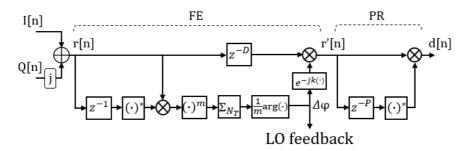

| 2.16 | Conventional CR based on differential mth-power for FE and differential     |

|      | demodulation for PR                                                         |

| 3.1  | SP coherent Rx and its DSP for PSK data                                     |

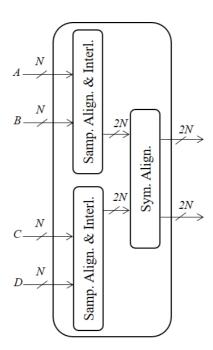

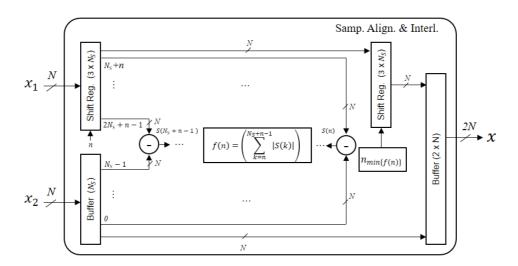

| 3.2  | Deskew architecture; Samp. Align. & Interl.: Sample Alignment and           |

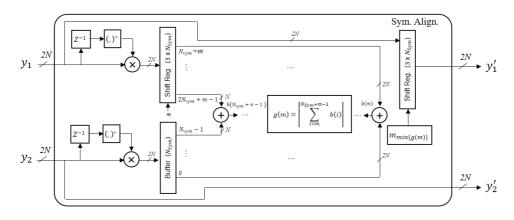

|      | Interleaving, Symb. Align.: Symbol Alignment39                              |

| 3.3  | Sample Alignment and Interleaving block for PSK data41                      |

| 3.4  | Symbol Alignment block for PSK data                                         |

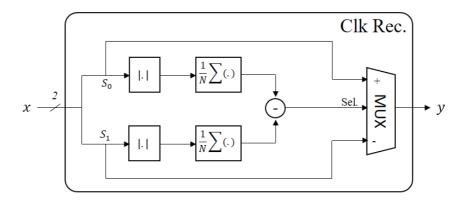

| 3.5  | Clock recovery block based on 2-sps for PSK data44                          |

<u>List of Figures</u> xv

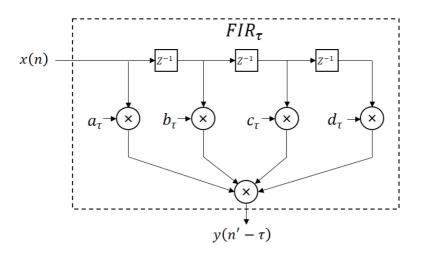

| 3.6  | FIR filter structure for interpolation                                                   |

|------|------------------------------------------------------------------------------------------|

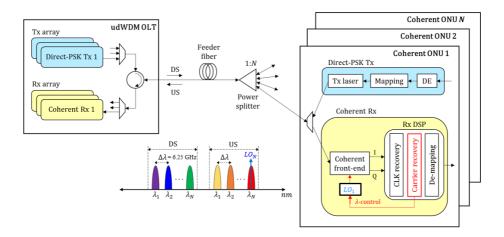

| 3.7  | Network architecture for the udWDM-PON application scenario; DE:                         |

|      | differential encoding                                                                    |

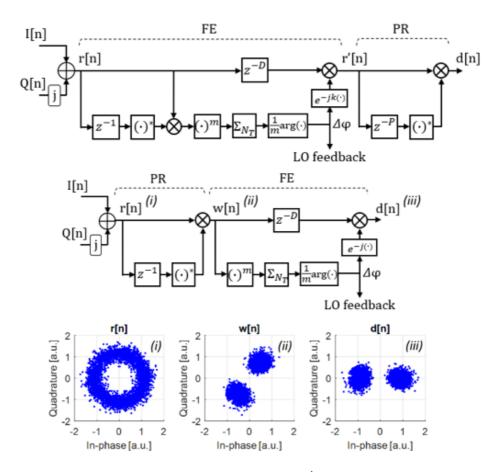

| 3.8  | Conventional CR based on differential mth-power for FE and differential                  |

|      | demodulation for PR (upper). Proposed CR that optimizes the architecture by              |

|      | reusing the 1-symbol complex correlation required for both the FE and the PR             |

|      | (middle). Evolution of the constellation for DPSK data along the proposed CR             |

|      | (lower)                                                                                  |

| 3.9  | Implemented the conventional (upper), and proposed CR architecture (lower)               |

|      | on the FPGA51                                                                            |

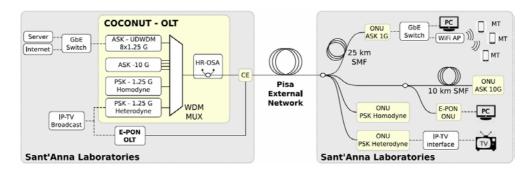

| 3.10 | Schematic representation of the field trial setup; Gray areas represent the              |

|      | equipment placed in the lab, High-Resolution Optical Spectrum analyzer (HR-              |

|      | OSA), CE: Co-existence Element, PC: Personal Computer; AP: Access Point;                 |

|      | MT: Mobile Terminal; TV: Television [10]53                                               |

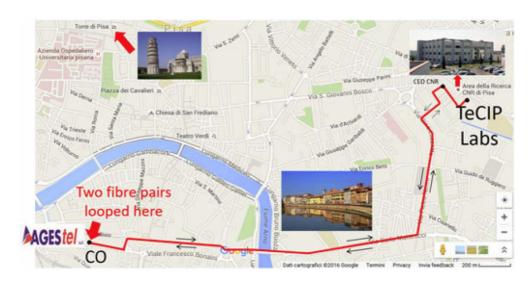

| 3.11 | Map of the dark fiber deployment in loop configuration connecting the Scuola             |

|      | Superiore Sant'Anna laboratories to the Pisa city center [10]54                          |

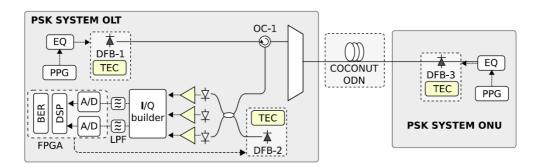

| 3.12 | PSK Intradyne system setup. OC: Optical Circulator; TEC: Thermo-Electric                 |

|      | Cooler; EQ: Equalizer; LPF: Low-Pass Filter; ODN: Optical Distribution                   |

|      | Network [10]55                                                                           |

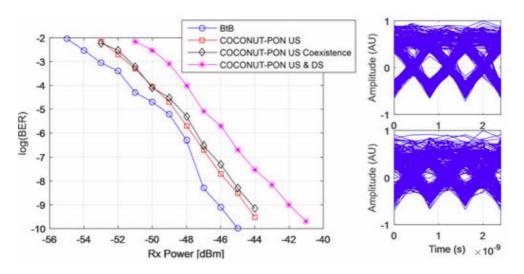

| 3.13 | US DPSK system performance [10]57                                                        |

| 3.14 | Experimental setup for real-time evaluation of the proposed CR with DPSK                 |

|      | data at 1.25 Gbps                                                                        |

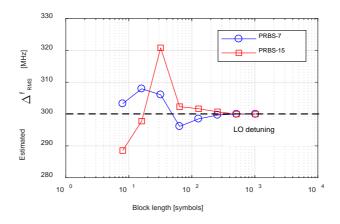

| 3.15 | RMS of the estimated $\Delta f$ against the block length $N_T$ for averaging. The RMS    |

|      | value is calculated over 100 estimations for each value of $N_T$                         |

| 3.16 | BER versus received power for DPSK at 1.25 Gbps, for the case of proposed                |

|      | (prop.) and conventional (conv.) CR, with different total spectral linewidth $\Delta\nu$ |

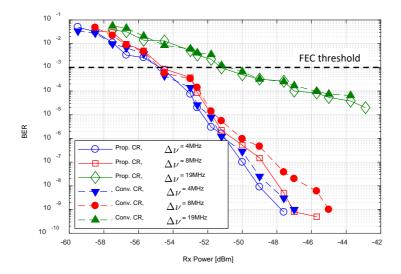

|      | 60                                                                                       |

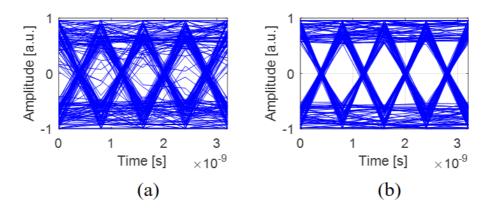

| 3.17 | Normalized DPSK eye diagram after CR for (a) 10-3 and (b) 10-9 BER60                     |

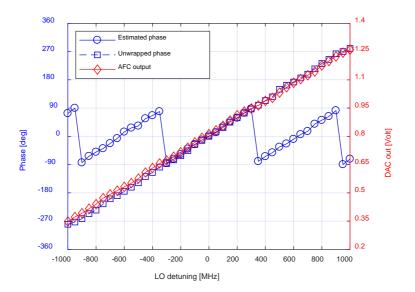

| 3.18 | Estimated phase $\Delta \varphi$ for frequency error correction, and output of the 1-bit |

|      | DAC for LO feed-back, as a function of the LO detuning61                                 |

<u>List of Figures</u> xvi

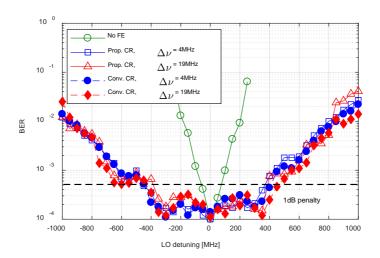

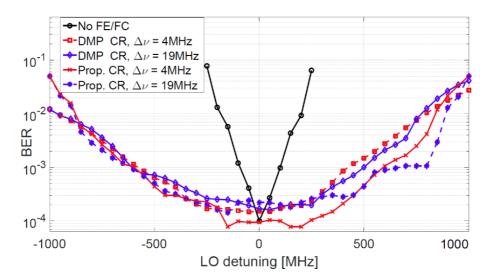

| 3.19 | BER versus LO detuning for CR with/out FE, for the case of proposed (prop.)          |

|------|--------------------------------------------------------------------------------------|

|      | and conventional (conv.) CR, with different total spectral linewidth $\Delta \nu$ 62 |

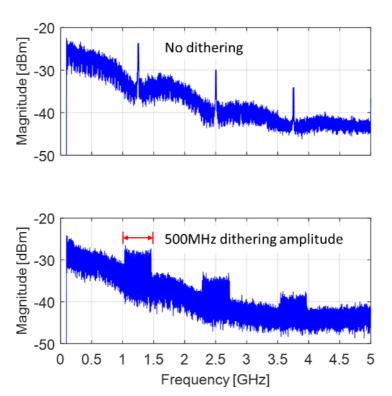

| 3.20 | DPSK photodetected spectra at 1.25 Gbps for DFB Tx laser without optical             |

|      | frequency dithering (upper), and with $\pm 250$ MHz amplitude of the frequency       |

|      | dithering (lower)63                                                                  |

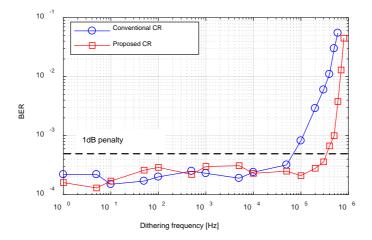

| 3.21 | BER against frequency of the optical dithering for $\pm 250$ MHz amplitude of the    |

|      | dithering, with conventional and proposed CR architectures65                         |

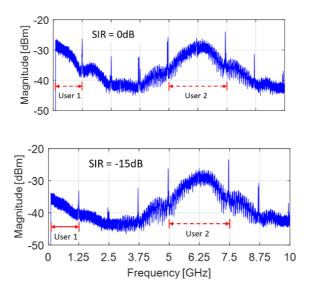

| 3.22 | Photodetected spectra of two 1.25 Gbps DPSK users spaced by 6.25 GHz, for            |

|      | both users emitting at the same optical power (upper) and with 15 dB optical         |

|      | power difference (lower); SIR: signal-to-interference ratio                          |

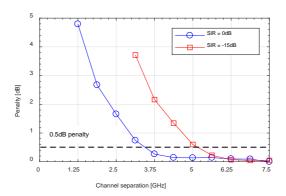

| 3.23 | Sensitivity penalty at BER = 10 <sup>-4</sup> versus channel separation between DPSK |

|      | users at 1.25 Gbps, for the two differential link loss scenarios depicted in         |

|      | Figure 3.22                                                                          |

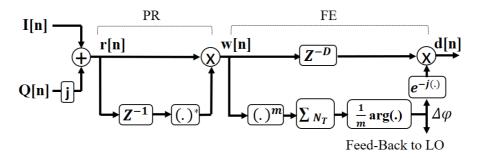

| 4.1  | DMP CR architecture presented in [5]73                                               |

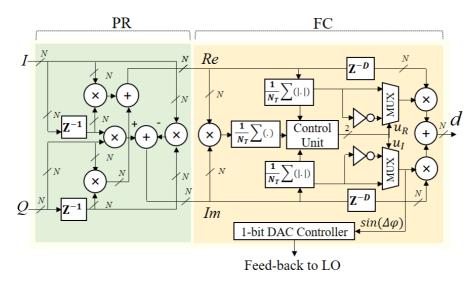

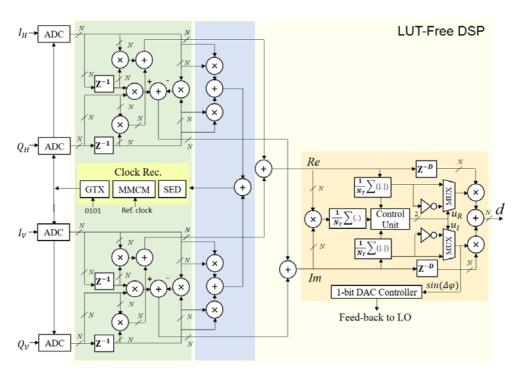

| 4.2  | Hardware architecture for the proposed LUT-free CR77                                 |

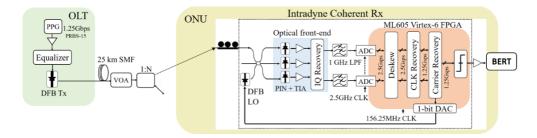

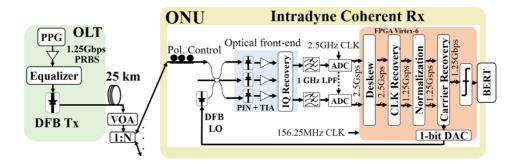

| 4.3  | Experimental setup for real-time evaluation of the proposed LUT-free CR with         |

|      | DPSK data at 1.25 Gbps79                                                             |

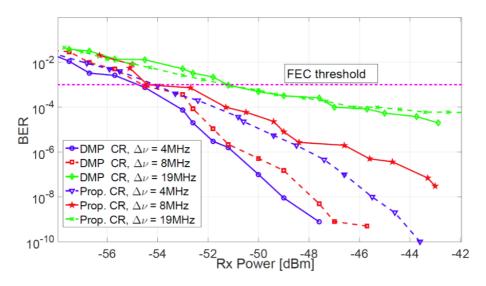

| 4.4  | BER versus received power for DPSK at 1.25 Gbps, for the proposed (Prop.)            |

|      | and DMP CR, with different total spectral linewidth $\Delta \nu$ 81                  |

| 4.5  | BER versus LO detuning with/out FE/FC, for the proposed (Prop.) and DMP              |

|      | CR with different total spectral linewidth $\Delta \nu$ 81                           |

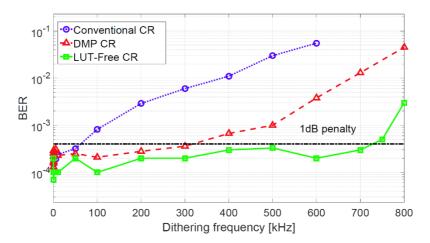

| 4.6  | BER vs. frequency of the optical dithering for ±250 MHz amplitude of the             |

|      | dithering, with conventional, DMP and LUT-free CR architectures82                    |

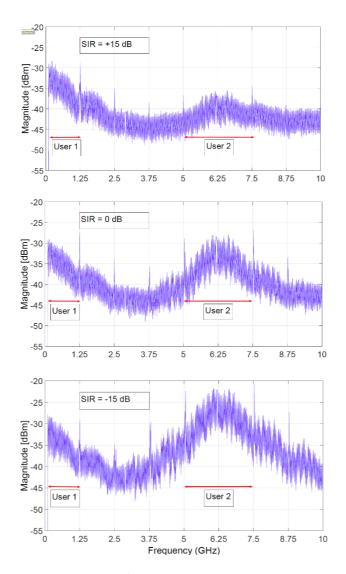

| 4.7  | Photodetected spectra of two 1.25 Gbps DPSK users spaced by 6.25 GHz, for            |

|      | User 1 emitting 15 dB higher than the interferer User 2 (upper), both users          |

|      | emitting at the same optical power (middle), and User 1 emitting 15 dB lower         |

|      | than the interferer User 2 (lower).; SIR: signal-to-interference ratio83             |

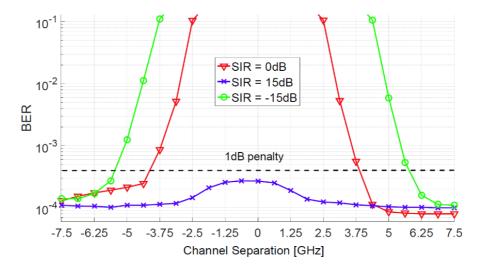

| 4.8  | BER of user 1, vs. spectral separation of two 1.25 Gbps DPSK users spaced            |

|      | by 6.25 GHz, for SIR = 0dB, SIR = 15dB, and SIR = -15 dB84                           |

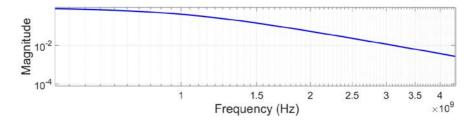

| 5.1  | HLf: low-pass 4 <sup>th</sup> -order Bessel filter90                                 |

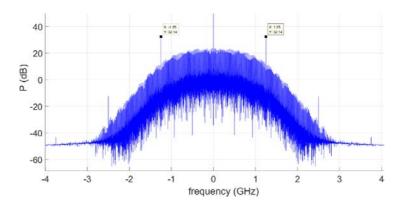

| 5.2  | Spectrum of the $P$ , with line spectral lines at $R_b$ = 1.25 Gbps, for DPSK signal |

| -    | at 1.25 Gbps                                                                         |

|      |                                                                                      |

<u>List of Figures</u> xvii

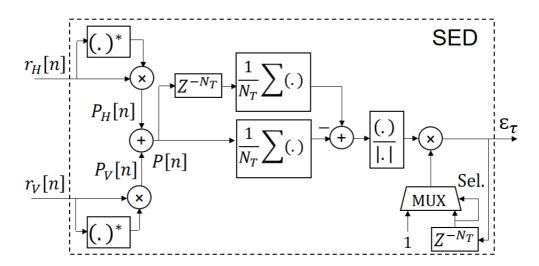

| .3 Sampling-phase error detector (SED) by using 1-sps for POD coherent F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PSK  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92   |

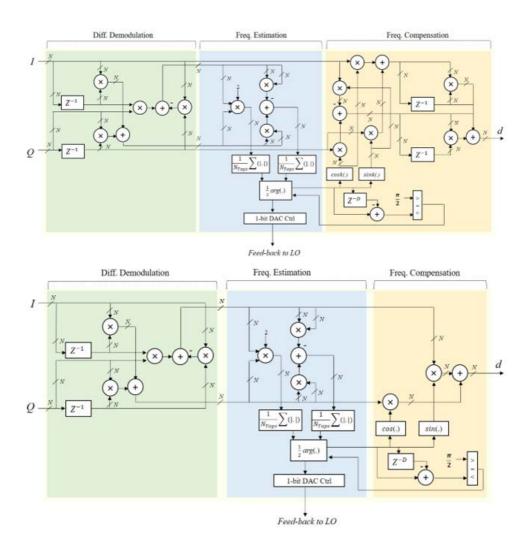

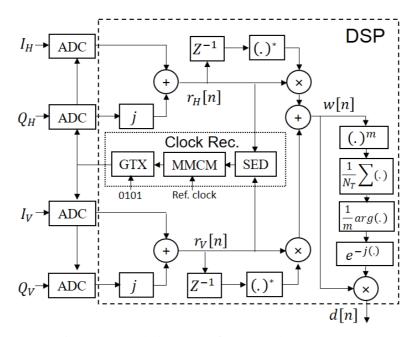

| .4 Symbol-rate DSP for POD coherent PSK Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93   |

| .5 Symbol-rate LUT-Free DSP based on LUT-Free CR architecture, implement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nted |

| on the FPGA for DPSK data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94   |

| .6 Experimental setup for real-time evaluation of the symbol-rate DSP of the P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OD   |

| coherent Rx with DPSK data at 1.25 Gbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95   |

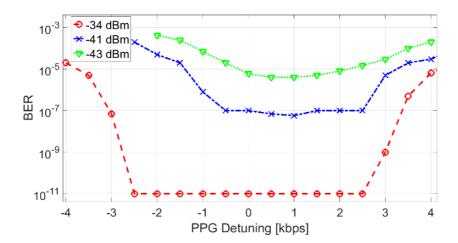

| .7 BER vs. PPG detuning to evaluate 1-sps clock recovery used in the syml                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bol- |

| rate DSP of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherent Rx, for DPSK data at 1.25 Gbps with difference of the POD coherence of the POD | rent |

| optical powers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97   |

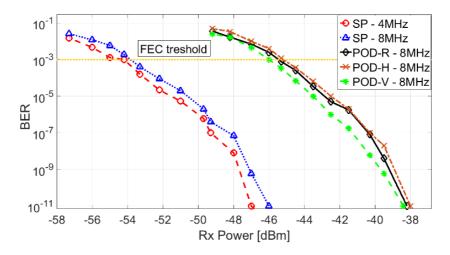

| .8 BER vs. optical power for SP coherent Rx, and different SOPs for P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OD   |

| coherent Rx by the symbol-rate DSP with $\Delta \nu = 4$ MHz and 8 MHz for DF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PSK  |

| data at 1.25 Gbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97   |

## **List of Tables**

| 3.1 | Hardware Resources for conventional and proposed CR architectures52     |

|-----|-------------------------------------------------------------------------|

| 4.1 | Decision rules based on $Re, Im$ and $\Delta \varphi$                   |

| 4.2 | Hardware Resources in terms of Adders, Multipliers, number of required  |

|     | process clocks and LUT for the DMP and proposed CR, implemented on      |

|     | Virtex-6 FPGA                                                           |

| 4.3 | Hardware Resources in terms of FFs, LUT-FF, SRL, DSP, Carry4, and power |

|     | consumption on Virtex-6 FPGA                                            |

## **Abbreviations & Acronyms**

ADC - Analog-to-Digital Converter

ASIC - Application-Specific Integrated Circuit

AFC - Automatic Frequency Control

BD - Balanced Detector

BER - Bit Error Rate

BERT - Bit Error Rate Tester

Carry4s - Carry Logics with Look Ahead

CD - Chromatic Dispersion

Clk Rec - Clock Recovery

CMA - Constant Modulus Algorithm

CR - Carrier Recovery

DAC - Digital-to-Analog Converter

DFB - Distributed Feed-Back

DMP - Differential *M*<sup>th</sup> -Power

DS - Downstream

DSP - Digital Signal Processing

ECL - External Cavity Laser

EQ - Equalizer

EPON - Ethernet PON

FASN - Full-Service Access Network

FC - Frequency Compensation

FE - Frequency Estimator

FEC - Forward-Error Correction

FF - Flip Flops

FFT - Fast Fourier Transform

FIR - Finite-Impulse Response

FPGA - Field-Programmable-Gate-Array

FTTH - Fiber-To-The-Home

FTTx - Fiber-To-The-x

FWHM - Full-Width at Half Maximum

GPON - Gigabit-capable PON

GVD - Group Velocity Dispersion

I - In-Phase

IF - Intermediate Frequency

ITU - International Telecommunication Union

LMS - Leas Mean Square

LO - Local Oscillator

LOSPR - LO-to-Signal-Power-Ratio

LTI - Linear Time-Invariant

LUT - Look-Up Table

LUT-FF - Lookup Table Flip Flop pairs

MM - Mueller-Muller

MMCM - Mixed Mode Clock Manager

MMSE - Minimum Mean Squared Error

MUX - Multiplexer

NGPON - Next Generation PON

NRZ-PRBS - Non-Return-to-Zero Pseudo Random Binary Sequences

OLT - Optical Line Terminal

ONU - Optical Network Unit

OOK - On-Off Keying

OPLL - Optical Phase-Locked Loop

P2P - point-to-point

Q - Quadrature

RAM - Random Access Memory

RC - Resistor-Capacitor

Ref - Reference

RF - Radio Frequency

RMS - Root Mean Square

Rx - Receiver

SIR - Signal-to-Interference

SMF - Single Mode Fiber

SOP - State-Of-Polarization

SRL - Shift Register Lookup table

SED - Sampling-Phase Error Detector

*R*b - Symbol Rate

*Rs* - Sample Rate

SP - Single Polarization

TDM - Time Division Multiplexing

TED - Timing Error Detector

TIA - Trans-Impedance Amplifier

Tx - Transmitter

TWDM - Time and Wavelength Division Multiplexing

ud - ultra-dense

udWDM - ultra-dense Wavelength Division Multiplexing

US - Upstream

VCO - Voltage-Controlled Oscillator

VOA - Variable Optical Attenuator

WDM - Wavelength Division Multiplexing

## **Symbols**

$T_{ADC}$  - ADC Sampling Period

$DS_I$  - Amount of Shifting

$\omega_{LO}$  - Angular Frequency of Local Oscillator

$\omega_s$  - Angular Frequency of Transmitted Signal

$N_T$  - Averaging Length

$\phi_c$  - Carrier Phase

$u_{I/R}$  - Coefficients to Recover the Sign of Phase Shift

A<sub>LO</sub> - Complex Amplitude of Local Oscillator

A<sub>s</sub> - Complex Amplitude of Transmitter

*I* - Cost Function

$z^{-P}$  - Delay in Symbols

D - Dispersion Parameter

*e* - Electron Charge

$h_{xx/xy/yx/yy}$  - Equalizer Coefficient of xx/xy/yx/yy

ε - Error Function

$\epsilon_{LMS/CMA}$  - Error Function of LMS/CMA algorithm

L - Fiber Length

au - Fractional Delay  $\Delta f$  - Frequency Error

=)

$E_P$  - Gardner Power-Based TED

$E_G$  - Gardner TED

$r_H$  - Horizontal Signal

*Im* - Imaginary

*h* - Impulse Response of Radio Frequency

Symbols xxv

$\omega_{IF}$  - Intermediate Frequency

μ - Iteration Factor

$\Delta v$  - Linewidth

*P<sub>LO</sub>* - Local Oscillator Power

$E_{LO}$  - Local Oscillator Signal

*b* - Mathematical Function

*f* - Mathematical Function

*g* - Mathematical Function

$\omega_b$  - Modulation Bandwidth

*m* - Number of Constellation Points

$N_{Tans}$  - Number of Filter Taps

$N_S$  - Number of Samples

$N_{Sym}$  - Number of Symbols

$\delta$  - Phase Difference

$\phi_{pn}$  - Phase Noise

$\phi_{LO}$  - Phase of the Local Oscillator

$\phi_s$  - Phase of the Received Signal

$\Delta \varphi$  - Phase Shift

*ħ* - Planck's Constant

*P<sub>H</sub>* - Power of Horizontal Signal

$P_V$  - Power of Vertical Signal

$\alpha_p$  - Power Ratio

$\eta$  - Quantum Efficiency

Re - Real

*P<sub>s</sub>* - Received Power

*R* - Responsitivity

*k* - Sample Index

$R_S$  - Sample Rate

<u>Symbols</u> xxvi

$\epsilon_{\tau}$  - Sampling-Phase Error

c - Speed of Light

$R_b$  - Symbol Rate

$E_s$  - Transmitted Signal

$r_V$  - Vertical Signal

$\lambda$  - Wavelength

# **Chapter 1. Introduction**

Optical communication was introduced by Charles Kuen Kao in 1960s, when he discovered certain physical properties of glass which laid the basis for high-speed data transmission [1]. Kao realized that a string of thin fiber is capable of carrying huge amount of information over long distance with few light energy, an alternative for copper in telecommunication technology. For stablishing a new perspective in the information and communication age, he received Nobel Prize in Physics in 2009.

Nowadays, optical access networks provide high capacity to end users with growing availability of multimedia contents that can be streamed to fixed and mobile devices. In this regard, one of the most flexible and low-cost approaches is Passive Optical Network (PON) that is used in Fiber-to-the-x (FTTx), where x = H, for home, B for building, C for curb and N for node [2]. Usually, a PON has a point to multipoint topology, to make connection between Optical Line Terminal (OLT), and Optical Network Unit (ONU) in the customer side.

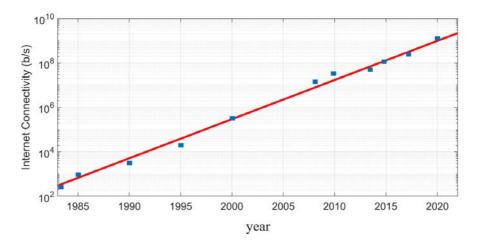

FTTH increases the user bandwidth to tenths/hundreds of Mbps bidirectionally, as Jacob Nielsen in 1998 predicted that average bandwidth per user increases 50 % per year [3]. Figure 1.1 shows the Nielson's law for bandwidth demand per year.

With the fiber reaching the user premises, and the bandwidth demands exponentially increasing even beyond 100 Mbps per user that today PON systems can hardly offer, telecom operators require an unconstrained upgrade path and set the next generation PON systems. They will benefit from the huge potential bandwidth of the installed

Chapter 1. Introduction 2

fiber. Different upgrading technologies are being proposed by industry, research institutions and standard organizations, mostly defined by their point-to-multi-point multiplexing form. But the current time division multiplexing (TDM) equipment, mostly based on GPON or EPON, will not be able to deal with the expected demands of the following years. It is so that wavelength division multiplexed PONs (WDM-PONs) will have to be sooner or later deployed [4]. Certainly, WDM-PONs enable service providers to offer dedicated wavelengths straight to business as well as to residential customers, using the existing optical backbone. However, there are two key requirements that will make the WDM-PON successful. First, applying the low-cost devices is mandatory, i.e. devices that can be low-cost to a wide percentage of end users, especially at the end-user side, but also at the central office that must be identical and have a typical cost level of consumer electronics. Secondly, whole upgrading of TDM-PONs must be attained, with compatibility with existing network infrastructure [5].

Figure 1.1: Nielsen's law prediction for internet bandwidth, growing 50 % per year.

The standardization of next generation optical access networks operating at over 10-Gbit/s has started to consider more flexible network configuration using WDM and to respond to those demands, Time and Wavelength Division Multiplexing (TWDM-PON) merge as one of the most promising PON solutions in which each wavelength

is shared between multiple ONUs by using TDM mechanism to provide high capacity and supply the bandwidth demand of broadband services. Recently, the FSAN access standardization group has started working on a new international standard, the ITU-T G.989: General requirements for 40-Gigabit-capable passive optical networks (NG-PON2) that, for the first time, considers WDM as the upgrade path, although with very few channels [6]. It has been suggested that optical coherent technologies, similar to those recently developed for the core networks, could be used to enhance the power budget [7], [8]. However, the expensive optical and electronic components do not simply reduce in cost to be low-cost for access networks.

#### 1.1 Thesis Objectives

The scope of this thesis is to focus on two aspects. First is to design, develop and implement a DSP for coherent system with high-sensitivity and fine wavelength selectivity. Then, without losing the performance and high-spectral efficiency, to reduce hardware and DSP complexity and costs as well as the required electronics. This thesis aims to design a new class of DSP for coherent receivers enabling the use of:

- Low-cost lasers such as distributed feed-back (DFB) lasers, rather than expensive low linewidth tuneable external cavity laser (ECL) [9].

- Direct laser modulation analogue processing for reliable and low-latency realtime operation.

- Low-cost receiver front-end optical couplers such as 3×3, rather than 90° hybrids [10], [11].

This new class of DSP initially was designed, developed and implemented in the COCONUT project [12], which demonstrated a low power consumption in comparison with other coherent technologies [13], [14]. Then, was extended and improved with higher performance, lower power consumption, more sensitivity, and higher speed of signal processing [15], [16], [17], [18] as well as simpler electronics

Chapter 1. Introduction

with lower speed analog-to-digital converter (ADC) [19]. Therefore, the main objectives of this thesis are classified as follows:

#### o General Objectives

- Implementation of the wavelength-to-the-user concept as the enabler for the more general goal of offering gigabits-to-the-user flexibly.

- Improvement of electrical bandwidth utilization efficiency, since the user transmits, receives and processes only the own information; this does not happen in current TDM-PON networks.

- Lower energy consumption, due to the fact that it is proportional to the bit rate

and we do not have to share it, and optical spectrum efficiency, because of optical

channels at 6.25 GHz spacing, thanks to the coherent detection, instead of the

current 100 GHz or 50 spacing. In this manner, we can increase the number of

channels and users in about one order of magnitude.

- Longer distance reach, thanks to the much better receiver sensitivity of coherent detection and their capability of fully compensating the dispersion effects of the optical fiber by DSP; distances longer than 100 Km at 1.25 Gbps, will be validated for the rural and wide metro scenarios.

- Higher number of users as the splitting ratio can be increased due to the 10-20 dB sensitivity improvement and the higher wavelength selectivity mentioned due to the coherent homodyne detection. The number of users can be increased from 64 to 256 at least.

- To reduce hardware cost as complex optical devices will be avoided, and simple conventional DFB lasers and receiver front-end based on 3×3 couplers.

#### Specific Objectives

• The DPSK signal at 1.25 Gbps will be detected by the phase-diversity receiver based on a  $3\times3$  coupler, and the sensitivity of -55 dBm at BER =  $10^{-3}$ , with an

ultra-narrow channel spacing of only 3 GHz. This will enable us to safely use a 6.25 GHz spacing.

- To propose new carrier recovery (CR) architectures in the DSP subsystems for dynamic compensation of local oscillator (LO) frequency drifts, phase noise and dispersion effects; we will develop and implement two different kinds of CRs, for field programmable gate array (FPGA) implementations in real-time signal processing.

- To propose a novel DSP architecture for low-cost polarization-independent detection using a simple clock recovery; we will demonstrate a symbol-rate DSP for coherent intradyne M-PSK receivers that uses only one sample per symbol (1-sps) data processing.

- To examine our proposals in the real-time experimental set up with FPGA

implementation of the proposed DSP algorithms and subsystems; all the

applications will be implemented in the real-time and completely practical

scenarios, rather than simple simulations.

#### 1.2 Thesis Outline

All the mentioned objectives and concepts in this thesis will be analysed in 6 chapters as follows:

In chapter 2, a general idea of state-of-the-art of optical access networks, including an ultra-dense (ud) WDM-PON architecture for future optical access networks will be discussed. Then, coherent detection with the main subsystems including optical front end, and the DSP will be introduced. This chapter provides an overview of the DSP subsystems for the coherent receivers, and explains the task of each block with different schemes and algorithms from previous works.

Chapter 3, presents implemented DSP subsystems for the coherent receivers and proposes an optimized CR with real-time FPGA implementation to evaluate the performance of the proposal.

Chapter 1. Introduction 6

In chapter 4, another optimized CR for optical intradyne receivers with DPSK data will be proposed and will be implemented on FPGA for real-time evaluation.

Chapter 5 will propose a symbol-rate DSP based on proposed architectures for polarization-diversity (POL) PSK receivers, which makes data processing using only 1-sps. The real-time FPGA implementation will assess the proposed DSP and will show that there is not any penalty between the processing based on 1-sps and 2-sps.

Finally, the conclusion chapter will summarize the work and a prospective future research line to continue this topic will be presented.

# **Bibliography**

- [1] K. a. G. A. Hockham, "Dielectric-fiber surface waveguides for optical frequencies," in *Proceedings of the IEE*, 1966.

- [2] F. P. GUIde, Testing Passive Optical Networks, Canada: EXFO Electro-Optical Engineering Inc., 2009.

- [3] 2016. [Online]. Available: https://www.nngroup.com/articles/law-of-bandwidth/.

- [4] F. Cavaliere, F. Ponzini, M. Presi and E. Ciaramella, "Migration towards high speed optical access enabled by WDM techniques," in *Asia Communications and Photonics conference and Exhibition (ACP)*, Shanghai, China, 2009.

- [5] J. Prat, I. N. Cano, M. Presi, I. Tomkos, D. Klonidis, G. Vall-llosera, R. Brenot, R. Pous, G. Papastergiou, A. Rafel and E. Ciaramella, "Technologies for Cost-Effective udWDM-PONs," *Journal of Lightwave Technology*, vol. 34, no. 2, pp. 783-791, 2016.

- [6] I.-T. G.989.1, "General requirements of 40-Gigabit-capable passive optical networks," 2013.

- [7] Y. C. Chung, "Recent advancement in WDM PON technology," in 2011 37th European Conference and Exhibition on Optical Communication (ECOC), Geneva, 2011.

[8] H. Rohde, S. Smolorz, J. S. Wey and E. Gottwald, "Coherent Optical Access Networks," in *Optical Fiber Communication Conference (OFC)*, Los Angeles, 2011.

- [9] V. Sales, J. Segarra, V. Polo, J. C. Velásquez and J. Prat, "UDWDM-PON using low-cost coherent transceivers with limited tunability and heuristic DWA," *IEEE/OSA Journal of Optical Communications and Networking*, vol. 8, no. 8, pp. 582 599, 2016.

- [10] C. Xie, P. J. Winzer, G. Raybon, A. H. Gnauck, B. Zhu, T. Geisler and B. Edvold, "Colorless coherent receiver using 3×3 coupler hybrids and single-ended detection," in 37th European Conference and Exhibition on Optical Communication, Geneva, Switzerland, 2011.

- [11] S. Narikawa, H. Sanjoh, N. Sakurai, K. Kumozaki and T. Imai, "Coherent WDM-PON using directly modulated local laser for simple heterodyne transceiver," in *31st European Conference on Optical Communication (ECOC)*, Glasgow, UK, 2005.

- [12] "European Project COCONUT (FP7)," [Online]. Available: http://ictcoconut.eu.

- [13] A. Rafel and N. Parkin, "Cost analysis of coherent-based TRx PON network," in *European Conference on Optical Communication (ECOC)*, Valencia, Spain, 2015.

- [14] G. Vall-llosera, A. Rafel, N. Parkin, M. Angelou, D. Klonidis, I. Cano, M. Presi, G. Papastergiou, I. Tomkos, J. Prat and E. Ciaramella, "COCONUT cost, power consumption and migration analysis: A route towards NG-PON3," in 17th International Conference on Transparent Optical Networks (ICTON), Budapest, Hungary, 2015.

- [15] S. Ghasemi, J. Tabares, V. Polo and J. Prat, "Optimized Differential Detection-Based Optical Carrier Recovery for Intradyne PSK Receivers in udWDM-PON," in *Optical Fiber Communications Conference and Exposition (OFC)*, San Diego, CA, USA, 2018.

- [16] S. Ghasemi, J. Tabares, V. Polo and J. Prat, "LUT-Free Carrier Recovery for Intradyne Optical DPSK Receivers in udWDM-PON," in *European Conference on Optical Communication (ECOC)*, Rome, Italy, 2018.

- [17] S. Ghasemi, J. Tabares, V. Polo and J. Prat, "LUT-Free Carrier Recovery for Intradyne Optical DPSK Receivers in udWDM-PON," *Journal of Lightwave Technology*, vol. 37, no. 6, pp. 1608 - 1613, 2019.

Chapter 1. Introduction 8

[18] J. Tabares, S. Ghasemi, V. Polo and J. Prat, "Simplified Carrier Recovery for Intradyne Optical PSK Receivers in udWDM-PON," *Journal of Lightwave Technology*, vol. 36, no. 14, pp. 2941 - 2947, 2018.

[19] S. Ghasemi, J. Tabares and J. Prat, "Symbol-rate Digital Signal processing for Low-Complexity Polarization Diversity Intradyne optical PSK Receivers," in *European Conference on Optical Communication (ECOC)*, Dublin, Ireland, Sep. 2019.

# **Chapter 2.** State of the Art: Optical Access Networks

## 2.1 Active and Passive Optical Networks

There are two major types of network architectures in optical access, active optical network (AON) and passive optical network (PON). AON is also known as active Ethernet or point-to-point (P2P) Ethernet [1], that each user has his own dedicated OLT on an optical connector. An AON, uses electrically powered switching devices, such as switch aggregator or router to manage signal distribution and route data to specific parts [2]. On the other hand, a PON only uses fiber and passive components such as optical splitters to separate and collect optical signals as they move through the network and it is point-to-multipoint solution. In this regard, being low-cost with efficient energy consumption is its advantages over AON, while higher bandwidth per port is possible by AON, due to dedicated port to each user.

# 2.1.1 Time Division Multiplexing PON (TDM-PON)

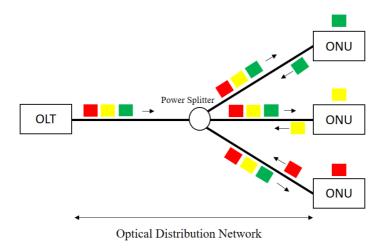

Gigabit-capable PON (GPON) and Ethernet PON (EPON), are the low-cost solutions in the PONs, and based on time division multiplexing (TDM), on-off keying (OOK) modulation format in direct detection optical transceivers. In 2000s, International Telecommunication Union (ITU)-T and full-service access network (FASN) defined next generation PONs (NGPONs), which is also low cost and compatible with

existing technology [3]. Figure 2.1 shows the TDM-PON architecture, where different packet colours are corresponding to each ONU. The current TDM equipment, mostly based on GPON or EPON, will not be able to handle the expected demands of the internet connectivity for the following years. It is so that Wavelength Division Multiplexing PONs (WDM-PONs) was eventually deployed [4].

Figure 2.1: TDM-PON architecture.

#### 2.1.2 Wavelength Division Multiplexing PON (WDM-PON)

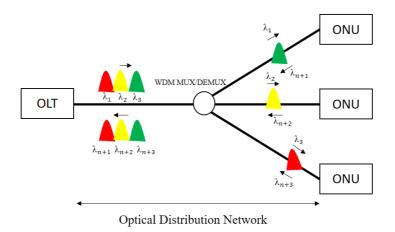

The advanced applications need more transmission requirements, thus, other options to TDM-PON is WDM-PON. The WDM-PON is a technology and an innovative concept for access and backhaul networks that significantly can enhance the carrier infrastructures. It applies different wavelengths over a physical point-to-multipoint fiber that contains only passive components (PONs). Then, each wavelength is dedicated to an individual home or user, provides customers with the benefit of low fiber counts, resulting in low-cost services. Figure 2.2 shows the WDM-PON architecture, with different wavelengths that are dedicated to each user.

All the concept and research as well as system implementations in this thesis are based on WDM-PON.

Figure 2.2: WDM-PON architecture.

# 2.1.3 Ultra-Dense Wavelength Division Multiplexing PON (udWDM-PON)

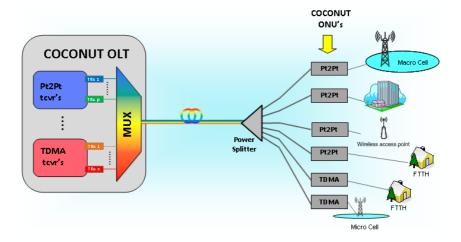

A significant step to upgrade the WDM-PON is ultra-dense WDM (udWDM) PON, with a narrow channel spacing, is a developing access network that allows increasing the number of optical carriers (channels) through a single fiber and large number of connected users to the network. In udWDM-PON each user is assigned by two wavelengths to cover both upstream (US) and downstream (DS) directions. The udWDM method can be used in infrastructure of current PONs, and different applications such as mobile back-haul and fixed-line users, over the same fiber. Figure 2.3 shows an udWDM-PON architecture, with coherent transmission, elastic spectrum and flexible hardware through the European COCONUT project [5].

The coherent technologies are commonly applied in core networks, and can be used to enhance the power budget and capacity of PONs. The main problem is that expensive optical and electronic components do not simply implemented for access networks, whereas the coherent system must be commercially compatible with cost-effective devices and electronics [6], [7]. In the following, the coherent detection system with the basic theories and the principle subsystems to be applied in udWDM-PON, will be discussed.

Figure 2.3: udWDM-PON application.

#### 2.2 Coherent Detection

The main supporting technology for the udWDM-PON is coherent transmission to achieve high spectral efficiency whereas the power efficiency is being maximized using in-phase (I) and quadrature (Q) signals in the two fields of polarization. Figure 2.4 shows the architecture of the coherent receiver to get the electric fields of the modulated signal from the transmitter (Tx) and the LO.

Figure 2.4: Coherent detection architecture.

where  $E_s$  and  $E_{LO}$  are the incoming signal from transmitter side and the field of the LO, respectively, in the time domain and are written by:

$$E_s(t) = A_s(t)e^{j(\omega_s(t) + \phi_s(t) + \phi_{pn}(t))}$$

(2.1)

$$E_{LO}(t) = A_{LO}(t)e^{j(\omega_{LO}(t) + \phi_{LO}(t))}$$

(2.2)

where  $A_s(t)$  is the complex amplitude,  $\omega_s(t)$  angular frequency,  $\phi_s(t)$  the phase of the received signal, and  $\phi_{pn}(t)$  is the phase noise.  $A_{LO}(t)$  is the constant complex amplitude,  $\omega_{LO}(t)$  angular frequency, and  $\phi_{LO}(t)$  the phase of the LO. The complex amplitudes  $A_s(t)$  and  $A_{LO}(t)$  are related to the signal power  $P_s(t) = |A_s(t)|^2/2$  and  $P_{LO}(t) = |A_{LO}(t)|^2/2$ , where  $P_s(t)$  and  $P_{LO}(t)$  are received power and LO power, respectively [8].

To maximize the signal photocurrents and suppress the dc components, coherent receiver uses balance detection by using a 3-dB optical coupler that mixes the LO signal with the received signal, resulting 180° phase shift between the two signals. When the received and LO signals are co-polarized, the electric fields on two photodiodes (upper and lower) are written as:

$$E_1(t) = \frac{1}{\sqrt{2}} [E_s(t) + E_{LO}(t)]$$

(2.3)

$$E_2(t) = \frac{1}{\sqrt{2}} [E_s(t) - E_{LO}(t)] \tag{2.4}$$

and the output photocurrents in electrical domain are given by:

$$I_{1}(t) = \frac{R}{2} \Big[ P_{s}(t) + P_{LO}(t) + 2\sqrt{P_{s}(t)P_{LO}(t)} \cos\{ (\omega_{s}(t) - \omega_{LO}(t))t + \phi_{s}(t) + \phi_{pn}(t) - \phi_{LO}(t) \} \Big]$$

(2.5)

$$I_{2}(t) = \frac{R}{2} \Big[ P_{s}(t) + P_{LO}(t) - 2\sqrt{P_{s}(t)P_{LO}(t)} \cos\{ (\omega_{s}(t) - \omega_{LO}(t))t + \phi_{s}(t) + \phi_{pn}(t) - \phi_{LO}(t) \} \Big]$$

(2.6)

where R is the responsitivity of the photodiode and is given by:

$$R = \frac{e\eta}{\hbar\omega_s(t)} \tag{2.7}$$

where e indicates the electron charge,  $\eta$  the quantum efficiency of the photodiode, and symbol  $\hbar$  stands for Planck's constant. Consequently, the balanced detector (BD) photocurrent output is obtained by:

$$I(t) = I_1(t) - I_2(t)$$

$$= 2R\sqrt{P_s(t)P_{LO}(t)}\cos\{(\omega_s(t) - \omega_{LO}(t))t + \phi_s(t) + \phi_{pn}(t)$$

$$- \phi_{LO}(t)\}$$

(2.8)

The phase of LO  $(\phi_{LO}(t))$  varies in time due to the phase noise, while the power  $(P_{LO}(t))$  remains constant [8].

#### 2.2.1 Heterodyne Detection

In a heterodyne receiver,  $\omega_{IF}(t)\gg \frac{1}{2}\omega_b(t)$ ; where  $\omega_b(t)$  is the modulation bandwidth of the optical carrier determined by the symbol rate, and  $\omega_{IF}(t)$ , intermediate frequency (*IF*), equals to  $\omega_s(t)-\omega_{LO}(t)$ .

Based on Eq. (2.8), the I(t) is down-converted to the IF signal including the amplitude and the phase information, as shown in Figure 2.5 [8].

Figure 2.5: Spectra of (a) the optical signal, and (b) the down-converted IF signal.

Due to band-limitation and complexity in filter design, besides the low sensitivity of the heterodyne receivers, this thesis aims to study and implement homodyne receivers, which is the second type of the receivers in the coherent detection system.

#### 2.2.2 Homodyne Detection

Homodyne detection is in the case that angular frequency of the LO is completely tuned with the received signal, resulting in  $\omega_{IF}(t) = 0$ . Thus, the Eq. (2.8) in homodyne will be given by:

$$I(t) = I_1(t) - I_2(t) = 2R\sqrt{P_s(t)P_{LO}(t)}\cos\{\phi_s(t) - \phi_{LO}(t)\}$$

(2.9)

In the homodyne detection to decode the encoded data, an optical phase-locked loop (OPLL) is needed for  $\phi_{LO}(t)$  to track the  $\phi_s(t)$ . There are several OPLLs designs are well known such as those are presented in [9], [10] and also based on subcarrier OPPL [11].

While the Eq. (2.9) only provides the in-phase component, to detect the quadrature component another LO with  $90^{\circ}$  phase shifted is required. This, can be achieved by a  $90^{\circ}$  optical hybrid as shown in Figure 2.6.

Figure 2.6: Phase-diversity homodyne receiver using 90° optical hybrids.

The electric fields of the output of the 90° optical hybrid can be written as:

$$E_1(t) = \frac{1}{2} [E_s(t) + E_{LO}(t)]$$

(2.10)

$$E_2(t) = \frac{1}{2} [E_s(t) - E_{LO}(t)]$$

(2.11)

$$E_3(t) = \frac{1}{2} [E_s(t) + jE_{LO}(t)]$$

(2.12)

$$E_4(t) = \frac{1}{2} [E_s(t) - jE_{LO}(t)]$$

(2.13)

Accordingly, the photocurrents from BPs are given by: