# Universitat de les Illes Balears

**DOCTORAL THESIS**

2021

# CONTRIBUTIONS ON USING EMBEDDED MEMORY CIRCUITS AS PHYSICALLY UNCLONABLE FUNCTIONS CONSIDERING RELIABILITY ISSUES

Abdel Rahman Naser Abed Alrazzaq Alheyasat

# Universitat de les Illes Balears

# DOCTORAL THESIS 2021

**Doctoral Program in Electronic Engineering**

# **CONTRIBUTIONS ON USING EMBEDDED MEMORY CIRCUITS AS**

# PHYSICALLY UNCLONABLE FUNCTIONS CONSIDERING RELIABILITY ISSUES

Abdel Rahman Naser Abed Alrazzaq Alheyasat

Supervisors:

Dr. Bartomeu Alorda Ladaria Dr. Gabriel Torrens Caldentey

Tutor:

Dr. Bartomeu Alorda Ladaria

Doctor by the Universitat de les Illes Balears

# **ACKNOWLEDGMENTS**

Writing fast is surely not my talent, but luckily now only this one page remains incomplete. So, let me take the opportunity to thank all of those who have been influential during the course of this thesis.

Before all others, I am grateful to my promotor *Dr. Bartomeu Alorda Ladaria* who graciously offered me a position as PhD student, and for welcoming me to the research group *Electronic System Group* of University of the Balearic Islands in May 2018. Without your advice none of this work can be done.

I am also much thankful to *Dr. Gabriel Torrens Caldentey* for introducing me to the related topics and simulations of this thesis and for guiding me from the beginning of this project until the last word of this thesis. His remarks have certainly improved the quality of this thesis.

Special thanks to *Dr. Sebastián Antonio Bota Ferragut* for his help in the beginning and his ideas and guidance during my PhD study. Finally, I express my gratefulness to the facility members of the *Doctorate School* for their Intellectual support throughout the course of this work.

Abdel Rahman Alheyasat

# **DEDICATION**

# (وآخر دعواهم أن الحمد لله رب العالمين)

To my parents (Naser, Ghada) and my beloved wife and daughter (Eng-Rand, Rand), who offered me unconditional love and support during the course of this thesis.

Un agradecimiento especial a Maria Guadalupe "Lupe", su amable hospitalidad durante mi estudio en Mallorca es algo que nunca olvidaremos en toda nuestra vida. Muchas gracias mamá mallorquina!

# **ABSTRACT**

Moving towards Internet-of-Things (IoT) era, hardware security becomes a crucial research topic, because of the growing demand of electronic products that are remotely connected through networks. Novel hardware security primitives based on manufacturing process variability are proposed to enhance the security of the IoT systems. As a trusted root that provides physical randomness, a physically unclonable function is an essential base for hardware security.

SRAM devices are becoming one of the most promising alternatives for the implementation of embedded physical unclonable functions as the start-up value of each bit-cell depends largely on the variability related with the manufacturing process. Not all bit-cells experience the same degree of variability, so it is possible that some cells randomly modify their logical starting value, while others will start-up always at the same value. However, physically unclonable function applications, such as identification and key generation, require more constant logical starting value to assure high reliability in PUF response. For this reason, some kind of post-processing is needed to correct the errors in the PUF response.

Unfortunately, those cells that have more constant logic output are difficult to be detected in advance. This work characterizes by simulation the start-up value reproducibility proposing several metrics suitable for reliability estimation during design phases. The aim is to be able to predict by simulation the percentage of cells that will be suitable to be used as PUF generators. We evaluate the metrics results and analyze the start-up values reproducibility considering different external perturbation sources like

several power supply ramp up times, previous internal values in the bit-cell, and different temperature scenarios. The characterization metrics can be exploited to estimate the number of suitable SRAM cells for use in PUF implementations that can be expected from a specific SRAM design.

# **RESUM**

En l'era de la Internet de les coses (IoT), garantir la seguretat del hardware ha esdevingut un tema de recerca crucial, en especial a causa de la creixent demanda de productes electrònics que es connecten remotament a través de xarxes. Per millorar la seguretat dels sistemes IoT, s'han proposat noves solucions hardware basades en la variabilitat dels processos de fabricació. Les funcions físicament inclonables (PUF) constitueixen una font fiable d'aleatorietat física i són una base essencial per a la seguretat hardware.

Les memòries SRAM s'estan convertint en una de les alternatives més prometedores per a la implementació de funcions físicament inclonables encastades. Això és així ja que el valor d'encesa de cada una de les cel·les que formen els bits de la memòria depèn en gran mesura de la variabilitat pròpia del procés de fabricació. No tots els bits tenen el mateix grau de variabilitat, així que algunes cel·les canvien el seu estat lògic d'encesa de forma aleatòria entre enceses, mentre que d'altres sempre assoleixen el mateix valor en totes les enceses. No obstant això, les funcions físicament inclonables, que s'utilitzen per generar claus d'identificació, requereixen un valor lògic d'encesa constant per tal d'assegurar una resposta fiable del PUF. Per aquest motiu, normalment es necessita algun tipus de postprocessament per corregir els possibles errors presents en la resposta del PUF. Malauradament, les cel·les que presenten una resposta més constant són difícils de detectar a priori.

Aquest treball caracteritza per simulació la reproductibilitat del valor d'encesa de cel·les SRAM, i proposa diverses mètriques per estimar la fiabilitat de les cel·les durant les fases

de disseny de la memòria. L'objectiu és ser capaç de predir per simulació el percentatge de cel·les que seran adequades per ser utilitzades com PUF. S'avaluen els resultats de diverses mètriques i s'analitza la reproductibilitat dels valors d'encesa de les cel·les considerant diverses fonts de pertorbacions externes, com diferents rampes de tensió per a l'encesa, els valors interns emmagatzemats prèviament en les cel·les, i diferents temperatures. Es proposa utilitzar aquestes mètriques per estimar el nombre de cel·les SRAM adients per ser implementades com a PUF en un disseny d'SRAM específic.

## **RESUMEN**

En la era de la Internet de las cosas (IoT), garantizar la seguridad del hardware se ha convertido en un tema de investigación crucial, en especial a causa de la creciente demanda de productos electrónicos que se conectan remotamente a través de redes. Para mejorar la seguridad de los sistemas IoT, se han propuesto nuevas soluciones hardware basadas en la variabilidad de los procesos de fabricación. Las funciones físicamente inclonables (PUF) constituyen una fuente fiable de aleatoriedad física y son una base esencial para la seguridad hardware.

Las memorias SRAM se están convirtiendo en una de las alternativas más prometedoras para la implementación de funciones físicamente inclonables empotradas. Esto es así, puesto que el valor de encendido de cada una de las celdas que forman los bits de la memoria depende en gran medida de la variabilidad propia del proceso de fabricación. No todos los bits tienen el mismo grado de variabilidad. Así pues, algunas celdas cambian su estado lógico de encendido de forma aleatoria entre encendidos, mientras que otras siempre adquieren el mismo valor en todos los encendidos. Sin embargo, las funciones físicamente inclonables, que se utilizan para generar claves de identificación, requieren un valor lógico de encendido constante para asegurar una respuesta fiable del PUF. Por este motivo, normalmente se necesita algún tipo de posprocesado para corregir los posibles errores presentes en la respuesta del PUF. Desafortunadamente, las celdas que presentan una respuesta más constante son difíciles de detectar a priori.

Este trabajo caracteriza por simulación la reproductibilidad del valor de encendido de celdas SRAM, y propone varias métricas para estimar la fiabilidad de las celdas durante

las fases de diseño de la memoria. El objetivo es ser capaz de predecir por simulación el porcentaje de celdas que serán adecuadas para ser utilizadas como PUF. Se evalúan los resultados de varias métricas y se analiza la reproductibilidad de los valores de encendido de las celdas considerando varias fuentes de perturbaciones externas, como diferentes rampas de tensión para el encendido, los valores internos almacenados previamente en las celdas, y diferentes temperaturas. Se propone utilizar estas métricas para estimar el número de celdas SRAM adecuadas para ser implementadas como PUF en un diseño de SRAM específico.

# **Table of Contents**

| Title                                        | Page  |

|----------------------------------------------|-------|

| ACKNOWLEDGMENTS                              |       |

| DEDICATION                                   | 11    |

| ABSTRACT                                     |       |

| TABLE OF CONTENTS                            | ıx    |

| LIST OF FIGURES                              | XIII  |

| LIST OF TABLES                               | Xvii  |

| LIST OF ABBREVIATIONS AND SYMBOLS            | XVIII |

| CHAPTER 1: INTRODUCTION                      | 1     |

| 1.1 Motivation                               | 2     |

| 1.2 Objectives and Major Contributions       | 5     |

| 1.3 Thesis Outline                           | 7     |

| CHAPTER 2: BACKGROUND                        | 9     |

| 2.1 Physical Unclonable Function (PUF)       | 9     |

| 2.1.1 Definition of a PUF                    | 10    |

| 2.1.2 PUF Application                        | 11    |

| 2.1.2.1 Cryptographic Key Generation         | 11    |

| 2.1.2.2 Low-Cost Authentication              | 13    |

| 2.1.2.3 True Random Number Generation (TRNG) | 14    |

| 2.1.3 PUF Classification                     | 14    |

| 2.1.3.1 Extrinsic based PUFs                 | 15    |

| 2.1.3.2 Intrinsic based PUFs                 | 15    |

| 2.2 SRAM-PUF                                                        | 16 |

|---------------------------------------------------------------------|----|

| 2.2.1 SRAM Cell Architecture                                        | 16 |

| 2.2.2 SRAM SUV as Source for SRAM PUF                               | 18 |

| 2.2.3 State of Art on SRAM-PUF Reliability Enhancement              | 20 |

| 2.2.3.1 Error Correcting Codes (ECCs)                               | 21 |

| 2.2.3.2 Majority Voting Methods                                     | 22 |

| 2.2.3.3 Post-Fabrication Burn-in Enhancement                        | 23 |

| 2.2.4 Direct and Indirect Preselection Approaches                   | 24 |

| 2.2.4.1 Our Approach                                                | 25 |

| CHAPTER 3: METRICS METHODOLOGY FOR IMPROVING SRAM-PUF               |    |

| RELIABILITY                                                         | 27 |

| 3.1 Simulation Environment Setup                                    | 27 |

| 3.2 Reliability Metrics based on Inherent-Cell Mismatch             | 30 |

| 3.2.1 Threshold Voltage Distance Between the Individual Transistors | 30 |

| 3.2.2 Switching Voltage Point Distance between Inverters            | 36 |

| 3.2.3 Summary                                                       | 40 |

| 3.3 Reliability Metrics Based on SNM Concept                        | 41 |

| 3.3.1 SNM Concept                                                   | 41 |

| 3.3.2 Proposed Metric                                               | 42 |

| 3.3.2.1 SNM Distance (SNM <sub>d</sub> ) Metric                     | 43 |

| 3.3.2.2 VTCs Intersection Distance (INTd) Metric                    | 46 |

| 3.3.3 Correlation with Previous Metric in literature (PSNM ratio)  | 48 |

|--------------------------------------------------------------------|----|

| 3.3.4 Correlation with Inherent-Cell Mismatch                      | 50 |

| 3.4 Voltage Noise Injection Methodology as Reliability Metrics     | 52 |

| 3.4.1 Metric Methodology                                           | 53 |

| 3.4.1.1 Noise Injection at Ground of the cell                      | 53 |

| 3.4.1.2 Noise Injection at Storage Nodes of the cell               | 56 |

| 3.4.1.2 Noise Injection at Cell Power Supply Nodes                 | 58 |

| 3.4.2 Correlations Between Noise Injection Locations               | 60 |

| 3.4.3 Correlation with Inherent-Cell Mismatch                      | 63 |

| 3.5 Dynamic Start-up Behavior as Reliability Metrics               | 66 |

| 3.5.1 Graphical Representation of SUV                              | 66 |

| 3.5.2 SRAM Separatrix as Reliability Metrics                       | 73 |

| CHAPTER 4: EXPLORING EXTERNAL AND INTERNAL PERTURBATIONS           |    |

| IMPCACT                                                            | 81 |

| 4.1 Simulation Setup                                               | 82 |

| 4.2 Impact of Power Supply Ramp-Up Time (RUT) on Start-Up Behavior | 83 |

| 4.2.1 RUT Test Methodology and Impact Explanation                  | 84 |

| 4.2.2 Proposed Metrics Robustness Considering RUT Variations       | 89 |

| 4.3 Impact of Previously Stored Value (PSV) on Start-Up Behavior   | 93 |

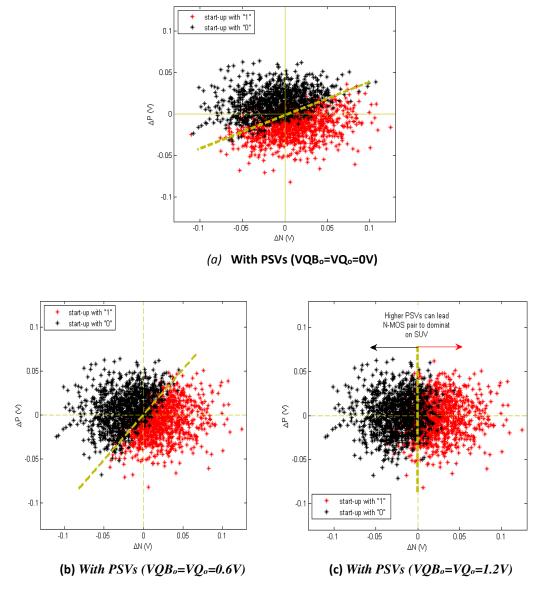

| 4.3.1 PSV Test Methodology and Impact Explanation                  | 94 |

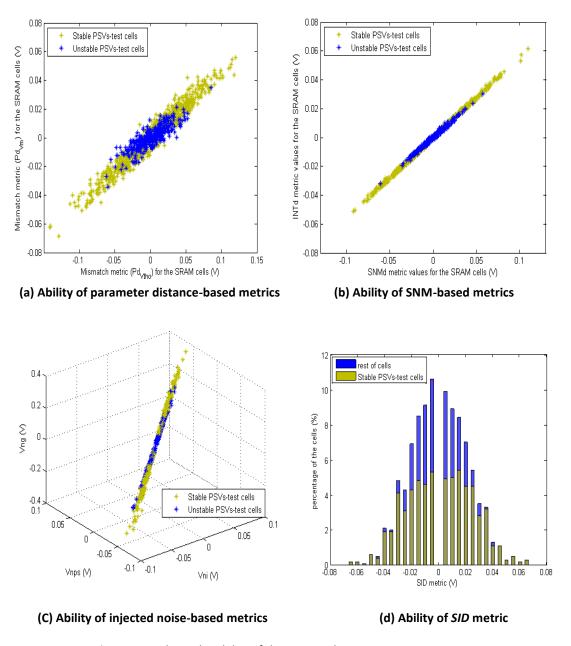

| 4.3.2 Proposed Metrics Robustness Considering PSV Variations       | 97 |

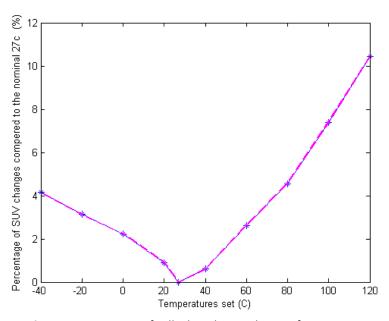

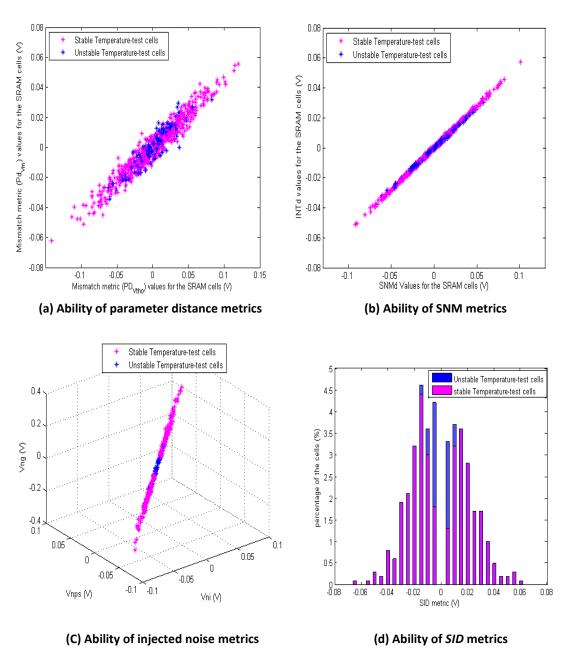

| 4.4 Impact of Temperature on Start-Up Behavior and Robustness of Metrics 98     |

|---------------------------------------------------------------------------------|

| 4.5 Impact of Internal Noise on Start-Up Behavior and Robustness of Metrics 101 |

| CHAPTER 5: REPRODUCIBILITY CHARACTERIZATION AND PROPOSED                        |

| METRICS DISCUSSION107                                                           |

| 5.1 Strong SRAM Cells to Improve PUF reliability                                |

| 5.2 Selection of Strong Cells Using Mismatch Metrics                            |

| 5.2.1 Parameter Distance-Based Metrics Discussion                               |

| 5.2.2 SNM-Based Metrics Discussion                                              |

| 5.2.3 Voltage Noise Injection-Based Metrics Discussion                          |

| 5.2.4 SRAM Separatrix-Based Metrics Discussion                                  |

| 5.2.5 Summary                                                                   |

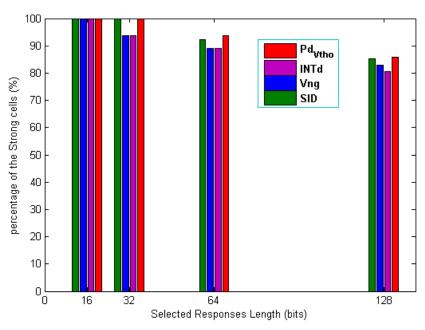

| 5.3 Influence of Selected PUF Response Length                                   |

| CHAPTER 6: CONCLUSION AND FUTURE WORK123                                        |

| 6.1 Conclusions                                                                 |

| 6.2 Future Work                                                                 |

| REFERENCES 126                                                                  |

# **LIST OF FIGURES**

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

| Figure 2.1: Diagram of embedded PUF-based key generator                                  |

| Figure 2.2: Illustration of object authentication scheme based on PUF [10]               |

| Figure 2.3 (a): 6T SRAM cell schematic in hold mode                                      |

| Figure 2.3 (b): Latch voltage transfer characteristics                                   |

| Figure 2.4: Start-up behavior for 50 cells when the power supply is ramped up 19         |

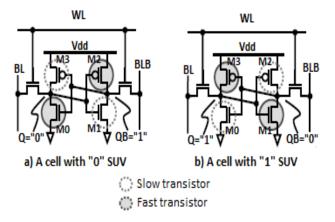

| Figure 3.1: 6T SRAM Cell showing transistors contribution to SUV                         |

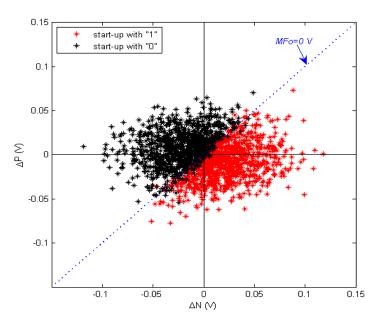

| Figure 3.2: Distribution of Mismatch Parameter between N-MOS and P-MOS                   |

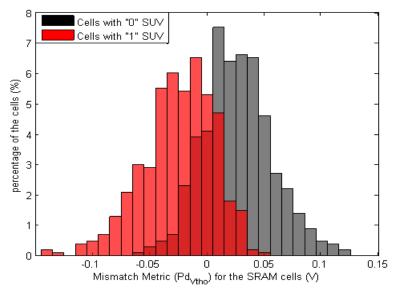

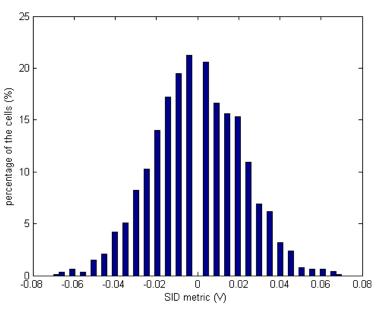

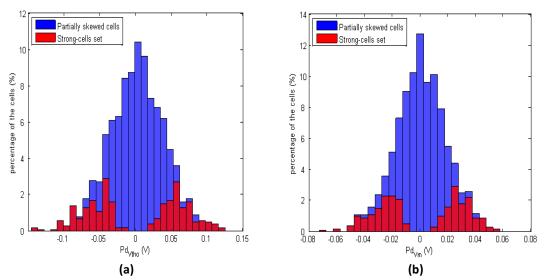

| Figure 3.3: Histograms of Mismatch Metric ( $Pd_{Vtho}$ ) values depending on the SUV 34 |

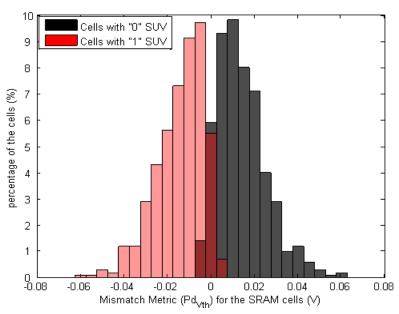

| Figure 3.4: Histograms of Mismatch Metric ( $Pd_{Vth}$ ) values including the Weighting  |

| Factors (w=0.76)                                                                         |

| Figure 3.5: Graphical technique to obtain Mismatch Metric ( $Pd_{Vm}$ ) values by using  |

| VTCs for the cell's inverters                                                            |

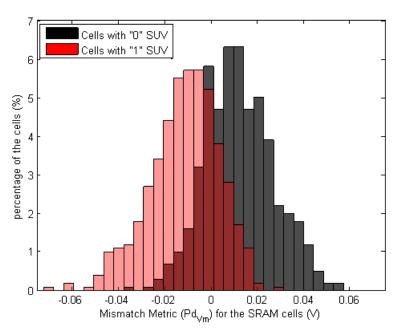

| <b>Figure 3.6:</b> Histograms of Novel Mismatch Metric ( $Pd_{Vm}$ ) values depending on |

| the SUV                                                                                  |

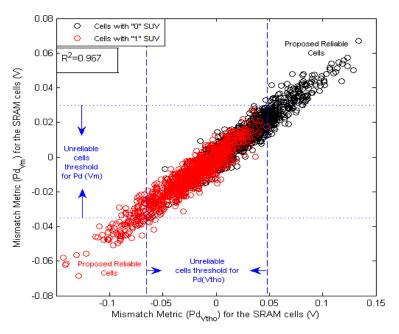

| <b>Figure 3.7:</b> The Relationship between $Pd_{Vtho}$ and $Pd_{Vm}$                    |

| Figure 3.8: Static Noise Margin definition using VTCs curves                             |

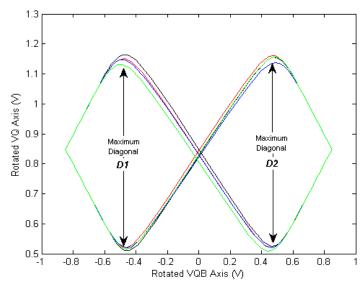

| Figure 3.9: 45° rotated VTCs                                                             |

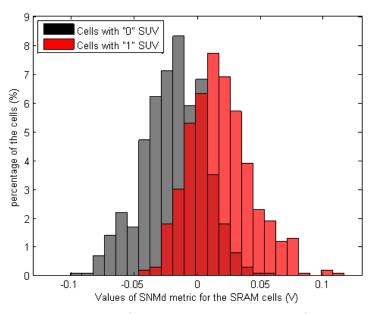

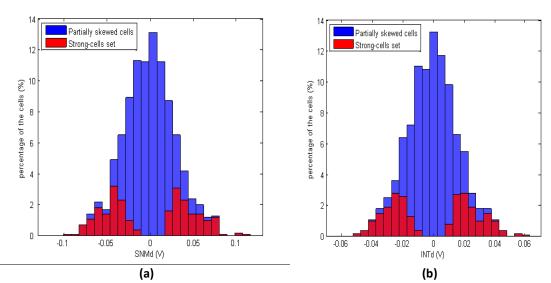

| <b>Figure 3.10:</b> Histogram of $SNM_d$ values considering the reference SUV            |

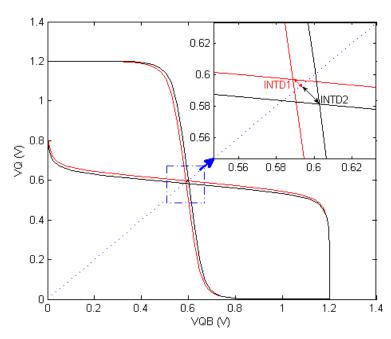

| Figure 3.11: Intersection Distance metric (INTd) definition using VTCs curves            |

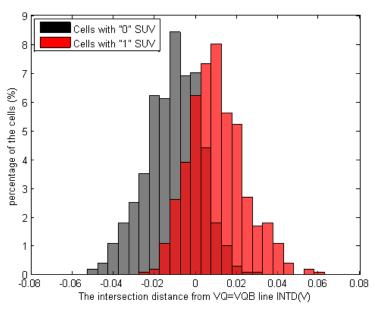

| <b>Figure 3.12:</b> Histogram of <i>INTd</i> values considering the reference SUV | 48 |

|-----------------------------------------------------------------------------------|----|

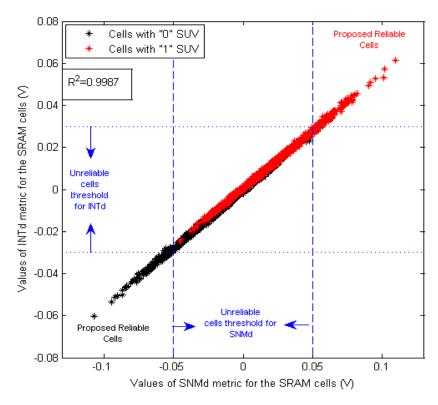

| Figure 3.13: Correlation between values of SNM-based metrics                      | 49 |

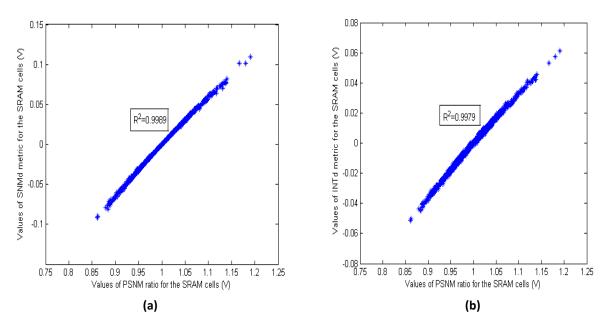

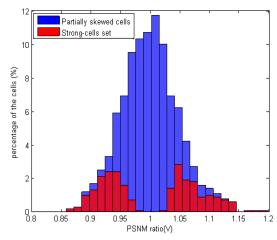

| Figure 3.14: Correlation between our proposed metrics and PSNM ratio              | 50 |

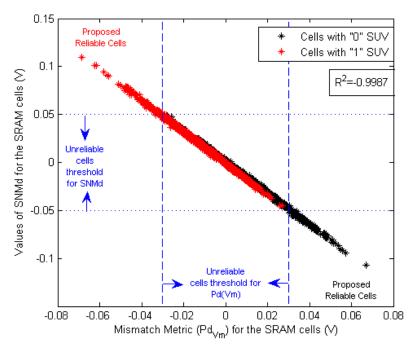

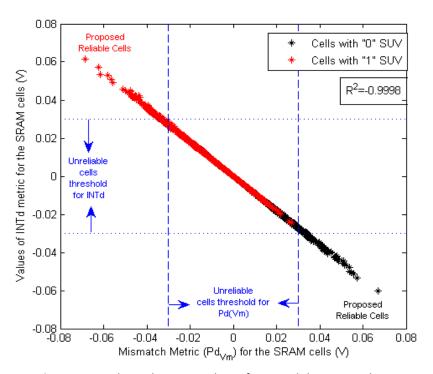

| <b>Figure 3.15:</b> Correlation between values of $SNM_d$ and the mismatch metric | 51 |

| Figure 3.16: Correlation between values of <i>INTd</i> and the mismatch metric    | 51 |

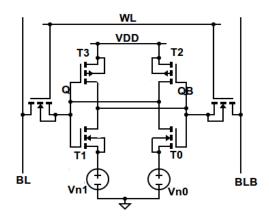

| Figure 3.17: 6T SRAM cell with noise injection at the ground nodes                | 54 |

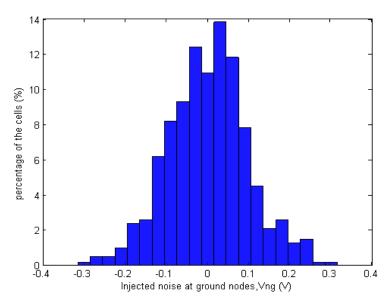

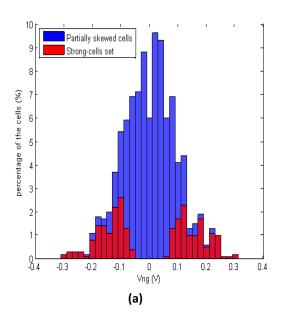

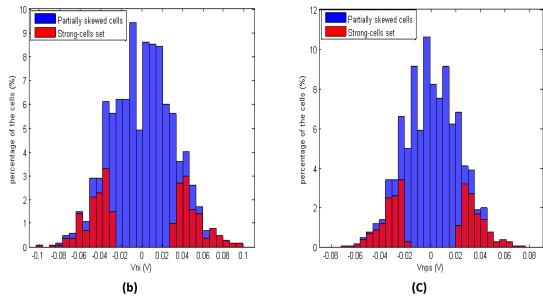

| <b>Figure 3.18:</b> The histogram distribution of $Vn_g$ metric                   | 56 |

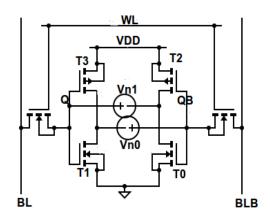

| Figure 3.19: 6T SRAM cell with noise injection between storage nodes              | 57 |

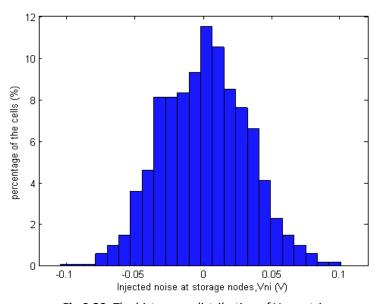

| <b>Figure 3.20:</b> The histogram distribution of <i>Vn<sub>i</sub></i> metric    | 57 |

| Figure 3.21: 6T SRAM cell with noise injection at power supply nodes              | 59 |

| <b>Figure 3.22:</b> The histogram distribution of $Vn_{ps}$ metric                | 59 |

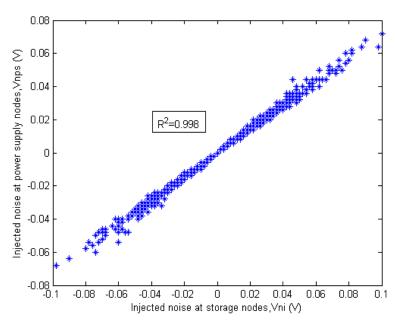

| <b>Figure 3.23:</b> The relation between $Vn_g$ and $Vn_{ps}$ metrics             | 60 |

| <b>Figure 3.24:</b> The relation between $Vn_i$ and $Vn_g$ metrics                | 61 |

| <b>Figure 3.25:</b> The relation between $Vn_i$ and $Vn_{ps}$ metrics             | 62 |

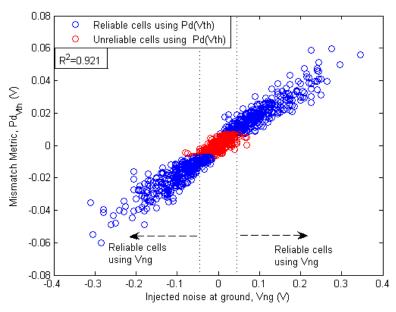

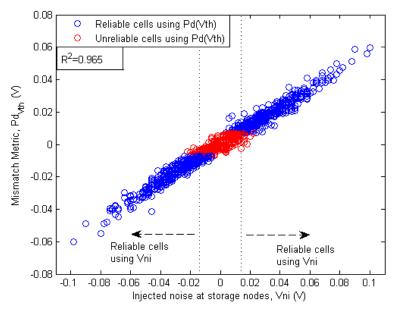

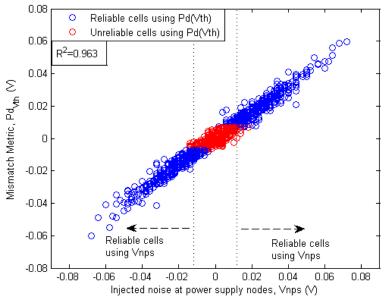

| <b>Figure 3.26:</b> The relation between $Vn_g$ metric and inherent mismatch      | 64 |

| <b>Figure 3.27:</b> The relation between $Vn_i$ metric and inherent mismatch      | 65 |

| <b>Figure 3.28:</b> The relation between $Vn_{ps}$ metric and inherent mismatch   | 65 |

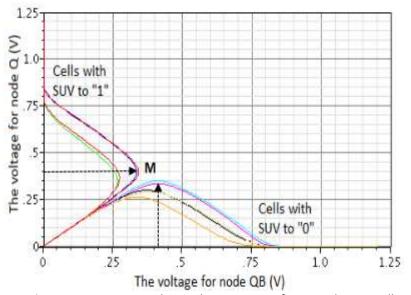

| Figure 3.29: Q versus QB voltages during start-up for several SRAM cells          | 67 |

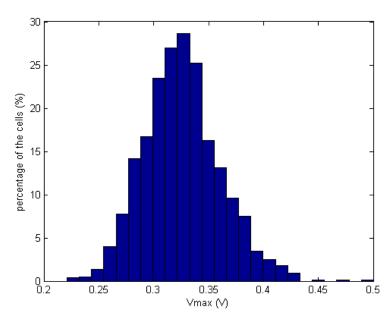

| Figure 3.30: The histogram distribution of Vmax indicator                         | 69 |

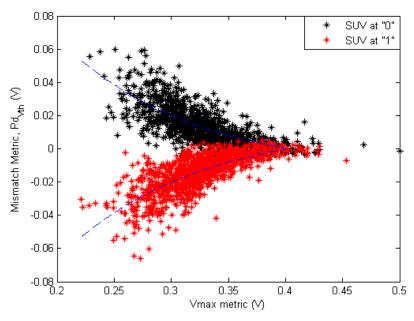

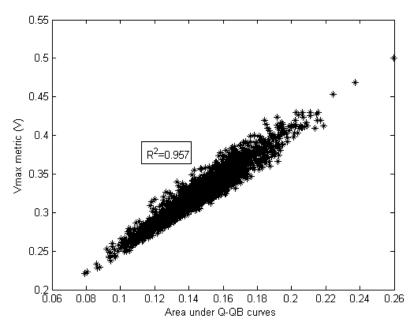

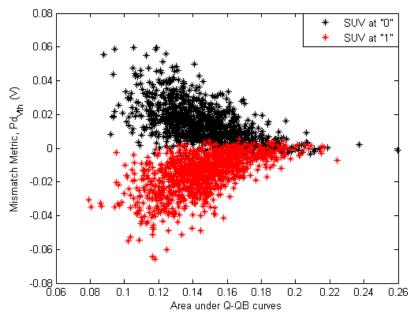

| Figure 3.31:  | The relation between the graphical indicator <i>Vmax</i> and Mismatch      |              |

|---------------|----------------------------------------------------------------------------|--------------|

|               | metric                                                                     | 59           |

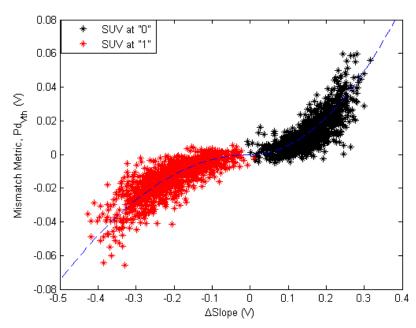

| Figure 3.32:  | The relation between the graphical indicator $\Delta Slope$ and Mismatch   |              |

|               | metric                                                                     | 71           |

| Figure 3.33:  | The relation between Area(Q-QB) and Vmax indicators                        | 72           |

| Figure 3.34:  | The relation between Area (Q-QB) and Mismatch metric                       | 72           |

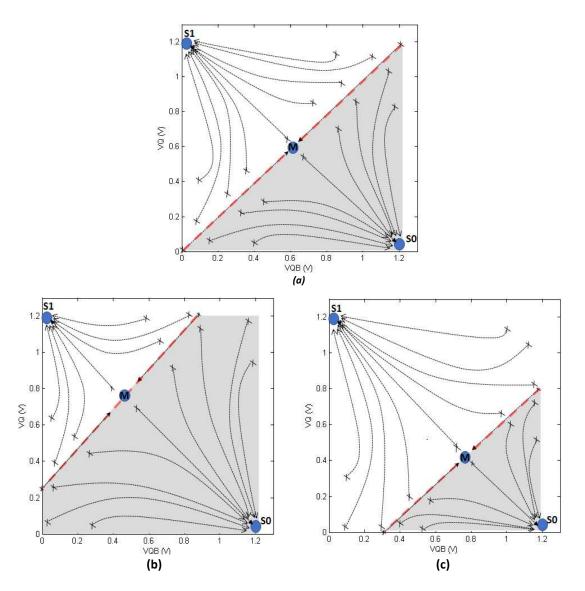

| Figure 3.35:  | The Phase-space of SRAM memory evolution at start-up stage                 | 74           |

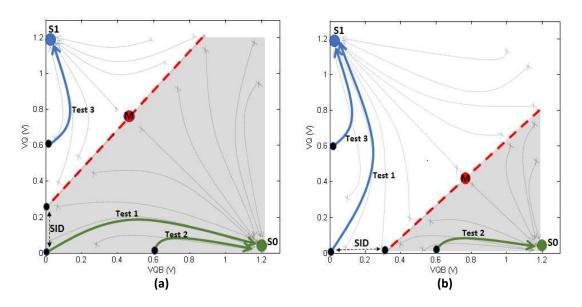

| Figure 3.36:  | The Phase-space of memory cells evolution and the definition of <i>SID</i> | , <b>,</b> , |

|               | metric                                                                     |              |

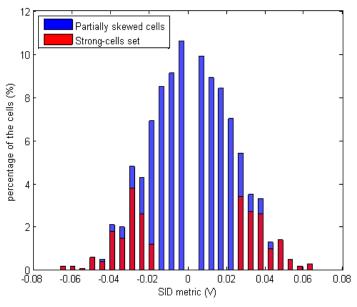

| Figure 3.37:  | The histogram distribution of separatrix metric (SID)                      | 79           |

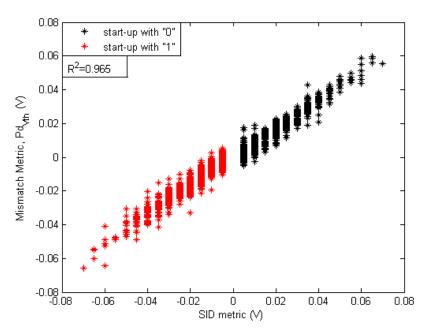

| Figure 3.38:  | The relation between the separatrix metric (SID) and mismatch              | 30           |

| Figure 4.1:   | ST SRAM cell including two random noise sources                            | 33           |

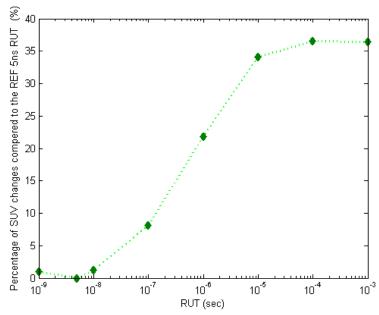

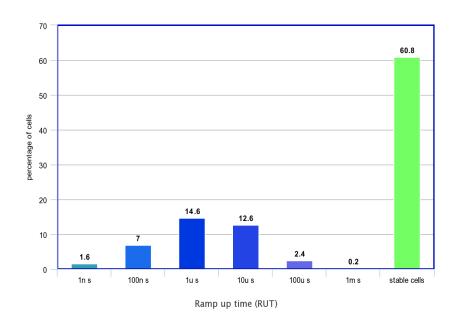

| Figure 4.2: p | percentage of cells that change the SUV at 5ns for several RUTs            | 34           |

| Figure 4.3: p | percentage of stable cells and unstable cells that change their SUV at     |              |

| S             | specific RUT value                                                         | 35           |

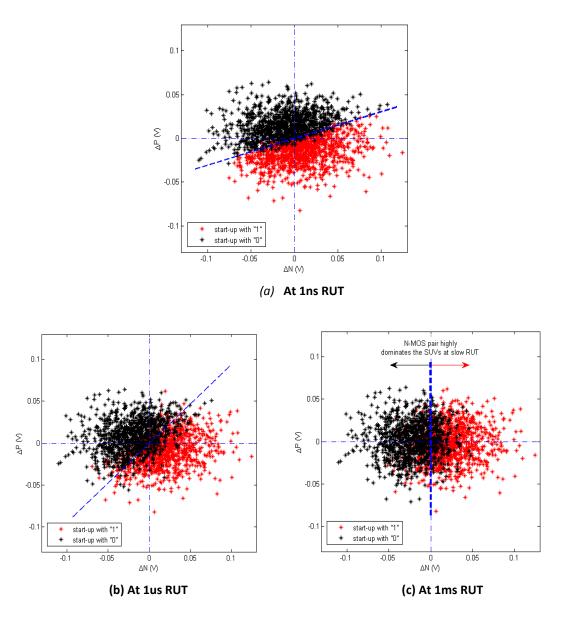

| Figure 4.4:   | Distribution of Vth variation of P-MOS and N-MOS transistors showing       |              |

|               | the SUVs at different RUTs                                                 | 37           |

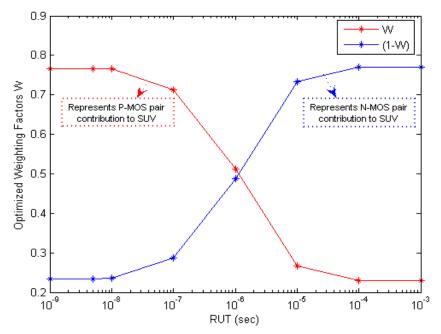

| Figure 4.5:   | The relation between P-MOS and N-MOS contributions to SUV with             |              |

| _             | respect to RUT                                                             | 39           |

| Figure 4.6: F | Proposed parameter distance-based metrics relation indicating the          |              |

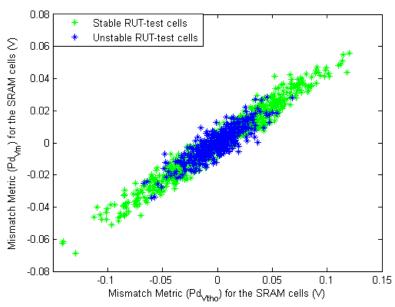

| _             | Stable-RUT cells                                                           | 90           |

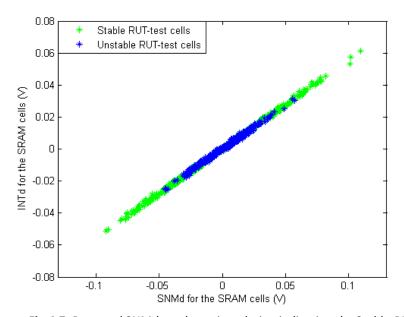

|               | Proposed SNM-based metrics relation indicating the Stable-RUT cells        |              |

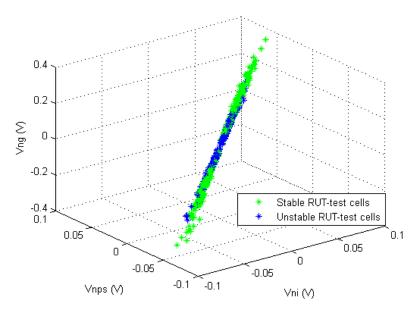

| Figure 4.8:   | Proposed injected noise-based metrics relation indicating the              |              |

| S             | Stable RUT cells                                                           | €2           |

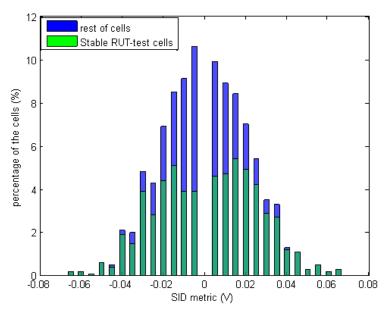

| Figure 4.9:   | The histogram of Proposed SID metric indicating the percentage of          |              |

|               | Stable PLIT cells                                                          | 22           |

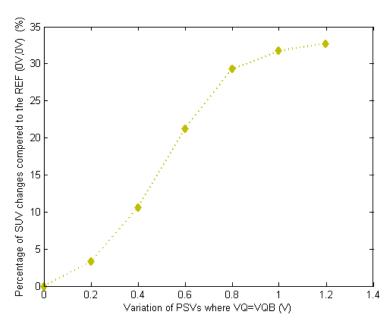

| Figure 4.10: percentage of cells that change the SUV for PSVs variation                       |     |

|-----------------------------------------------------------------------------------------------|-----|

| compared to reference (0 V, 0 V)                                                              | 95  |

| Figure 4.11: Distribution of Vth variation of P-MOS and N-MOS transistors                     |     |

| and their contributions to the SUVs at different PSVs                                         | 96  |

| Figure 4.12: Studying the ability of the metrics against PSVs impact                          | 98  |

| Figure 4.13: Percentage of cells that change the SUV for temperature                          |     |

| variations compared to nominal 27°                                                            | 99  |

| Figure 4.14: Studying the ability of the metrics against Temperature impact                   | 101 |

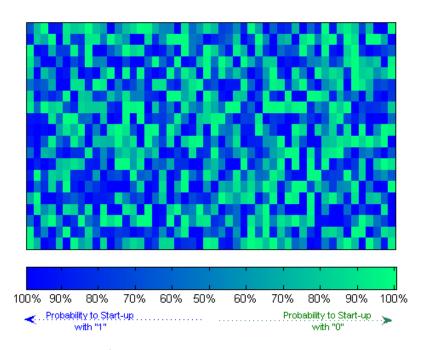

| Figure 4.15: Visualization of the SRAM array with the probability to                          |     |

| start-up to a preferred SUV                                                                   | 103 |

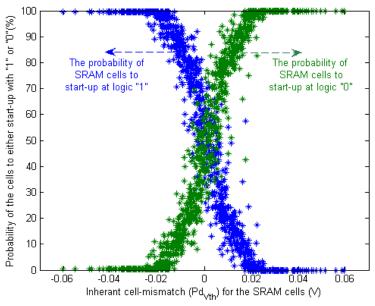

| Figure 4.16: The relation between inherent cell-mismatch and the probability                  |     |

| of the cell to start-up to a preferred SUV                                                    | 104 |

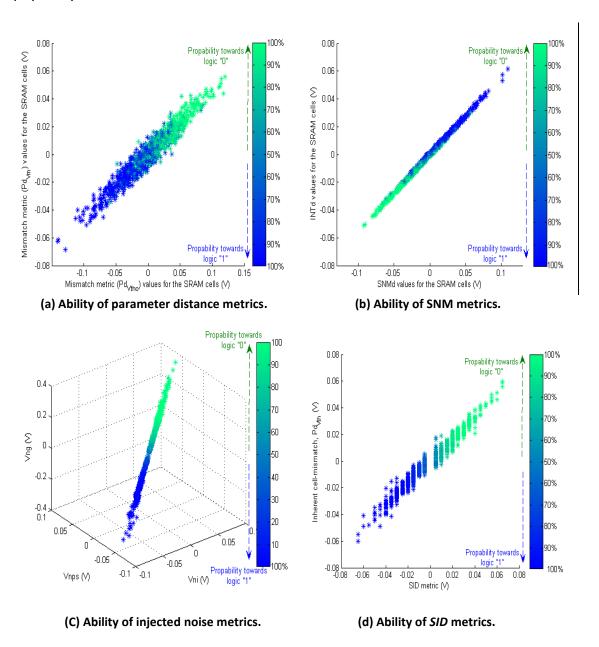

| Figure 4.17: The performance of the proposed metrics in classifying cells                     |     |

| repeatability considering the modeled internal noise                                          | 106 |

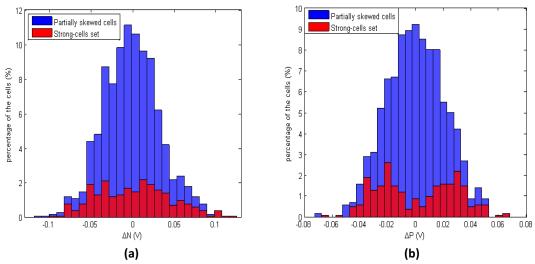

| Figure 5.1: The histograms for literature ( $\Delta N$ and $\Delta P$ ) methodologies showing |     |

| strong cells distribution                                                                     | 111 |

| Figure 5.2: The histograms for the parameter distances showing strong cells                   |     |

| distribution                                                                                  | 112 |

| Figure 5.3: The histogram distribution for literature PSNM ratio identifying                  |     |

| the strong cells                                                                              | 115 |

| Figure 5.4: The histograms for the proposed SNM metrics showing strong                        |     |

| cells distribution                                                                            | 115 |

| Figure 5.5: The histograms for the injected noise-based metrics showing strong                |     |

| cells distribution                                                                            | 118 |

| Figure 5.6: The histogram distribution for dynamic SID metric identifying                     |     |

| the strong cells                                                                              | 119 |

| Figure 5.7: Percentage of strong cells identified by each best metric approach                |     |

| considering different response lengths                                                        | 121 |

# **LIST OF TABLES**

| able                                                                              | Page |

|-----------------------------------------------------------------------------------|------|

| able 5.1: Number of cells stable, repeatable and strong identified by Parameter   |      |

| distances metrics selecting 64 PUF-bits                                           | 113  |

| able 5.2: Number of cells stable, repeatable and strong identified by SNM-based   | l    |

| metrics selecting 64 PUF-bits                                                     | 116  |

| able 5.3: Number of cells stable, repeatable and strong identified by injected no | ise  |

| based metrics selecting 64 PUF bits                                               | 118  |

# LIST OF ABBREVIATIONS AND SYMBOLS

Internet of Things.

PUF Physically Unclonable Function.

SRAM Static Random-Access Memory.

SUV SRAM cell Start-Up Value.

SNM Static Noise Margin.

DNMs Dynamic Noise Margins.

VTCs Voltage Transfer Characteristics.

ICs Integrated Circuits.

CRPs Challenge-Response Pairs.

NVM Non-Volatile Memory.

POWFs Physical One-Way Functions.

ECCs Error Correction Codes.

TRNG True Random Number Generation.

RUT Ramp-Up Time.

PSVs Previously Stored Values.

IBS Index Based Syndrome.

BTI Bias Temperature Instability.

FPGA Field-Programmable Gate Array

ASIC Application-Specific Integrated Circuit.

SA sense-amplifier.

Vdd SRAM Ramp-Up Voltage.

WL Word-line.

BL Bit-Line.

lpsvt Low Power Standard Threshold Voltage CMOS.

lphvt Low Power High Threshold Voltage CMOS.

lpsvt Low Power Low Threshold Voltage CMOS.

Vpwl Voltage Piecewise linear.

OCEAN Open Command Environment for Analysis.

r<sub>SUV</sub> SUV reproducibility.

ΔP Threshold voltage difference between P-MOS

transistors.

ΔN Threshold voltage difference between N-MOS

transistors.

*Pd<sub>Vtho</sub>* Threshold Voltage Parameter Distance metric.

Pd<sub>Vm</sub> Inverter Switching Point Parameter Distance

metric.

$SNM_d$  SNM Distance.

INT<sub>d</sub> VTCs Intersection Distance

| $Vn_g$          | Voltage Noise injection at Ground nodes of the |

|-----------------|------------------------------------------------|

|                 | cell                                           |

| Vni             | Voltage Noise injection between the internal   |

|                 | storage nodes of the cell.                     |

| Vp <sub>s</sub> | Voltage Noise injection at the power supply    |

|                 | nodes of the cell.                             |

| SID             | Separatrix Intersection Distance.              |

# **CHAPTER 1**

# INTRODUCTION

The Internet of Things (IoT) is an innovation with industrial, commercial and consumer applications. The IoT allows a massive number of devices to be connected remotely with an affordable price. This innovation can provide many benefits, like a more efficient and eco-friendly industry, and make daily life more convenient. Unfortunately, alongside with all the advantages the IoT comes with, the security of the communication systems is a serious challenge. In addition, this problem gets worse due to the fast growth of the number of IoT devices. As a consequence, a massive amount of data is collected and being transferred between the IoT devices. The data communicated through IoT networks can contain important information that might lead to threats to user's privacy if the security is compromised and data is leaked. Therefore, communication networks between devices must be highly secure, which is specifically challenging because of the large number of devices and the resource limitation of many IoT devices. It is difficult to reliably protect most IoT devices, as most of them cannot afford robust cryptographic systems within the restricted budget for both power consumption and manufacturing cost.

This chapter introduces the motivation of this work in Section 1.1. The achieved objectives and major contributions of the thesis are explained in Section 1.2. Finally, Section 1.3 presents the outlines of the thesis.

## 1.1 Motivation

The digital revolution that happened over the past decades allowed that transferring enormous amount of data across the world at high speed has become something normal. This uprising has demanded the usage of applications that need a large amount of online connections. From the essential online banking, to the entertainment of online gaming; from restraining the access to an administration facility, to supporting full access to a laboratory and research facility. Nearly each application utilized nowadays needs such interconnections. The data which is exchanged through these nets could be anything varying from user personal information to accounts with massive amount of money. Consequently, in order to protect the authenticity and confidentiality of these interconnections it is compulsory to consider some degree of security to be included in the systems. The information exchanged in these systems needs to be protected from theft while allowing them to be productive and accessible only by the intended users. However, the Information Security of IoT is the field where all techniques and tools are dedicated to protecting systems information.

The common practice is to utilize cryptographic methods such as signing algorithms, encryption, and decryption, to secure the transported and stored information. The cryptographic algorithms implemented for these methods are available for the public, nevertheless the secret key generated by them is securely saved into the device. Based on that, it is important to ensure the security of the generated key. The classical security systems that are available in the market rely on storing the secret key or the crucial information in a Non-Volatile Memory (NVM). Smart Cards, Credit Card and TV channels Card are examples for the application of these classical systems. However, the main

goals of these systems are to stop cloning and theft of service [1]. These methods, even though secure, cannot be protected against some of the adversary's attacks. As the secret key generated from these systems is stored permanently somewhere in the device, and hence, any person that can access the device and knows how the security is implemented can attack this system. Therefore, security solutions should improve to become more secure against these threats.

New hardware security solutions should be developed to compensate for the growing privacy and security risks in the IoT systems. Recent approach to overcome the drawbacks of the classical security system is the use of embedded physical unclonable functions (PUFs). The main idea of a PUF is to generate a secret key from unclonable and unpredictable physical features related to the variability related to the manufacturing process technology of Integrated Circuit (IC) of IoT devices. Taking profit form this process variation, PUF can generate a unique and unclonable fingerprint for each IC.

Therefore, to secure the communications between IoT devices, the secret key generation scheme based on PUF can be a more secure and lightweight method to generate a unique non-stored key for the devices. This key is generated whenever needed without requiring storing it in the device. These properties present the PUFs as an ideal candidate for hardware security of IoT [2]. However, the main issue in PUF implementation is to assure that the generated key is always the same under different operational and environmental conditions.

There are different approaches to introduce PUF solutions in IoT devices. However, SRAM devices are gaining attention because its presence is very common in many IoT devices and the start-up value (SUV) of each individual bit-cell depends to a greater or

lesser extent on the variability of the IC manufacturing process [3]. Remember that the SUV defines the logical value that the cell acquires by itself when it is polarized from 0V to its nominal value Vdd, before any data is written in it. Depending on how the variability affects each bit-cell transistor, we will have suitable-PUF SRAM cells whose SUV will always be the same, with a value that is unclonable and unpredictable a priori, on the other hand, other cells present an SUV that can be different in each star-up process. However, achieving acceptable reliability of SRAM-based PUF output usually requires some additional intervention, since not all cells in a memory can be suitable for that application [78].

In the literature, a huge amount of works has proposed and evaluated different SRAM methodologies using specific laboratory equipment to estimate the impact on reliability and robustness of bit-cells designs when process variation, temperature, and other factors are also involved [61, 79-80], but there are few works related to estimate the suitability of a given SRAM design to be used in PUF applications. One reason lies in the difficulty of simulating the different external processes involved in determining the SUV of a given symmetrical bit-cell affected by process variations with certain start-up conditions that are not fully known. Although it is completely unpredictable to know a priori the position of the suitable cells, or what their starting value will be, due to what has been previously commented, it will be very useful to have some indication in the design stage what percentage of suitable cells to expect, or if an optimization of the bit-cell design is possible to increase that value, or if it is advisable to use additional help modules.

# 1.2 Objectives and Major Contributions

SRAM-PUFs are becoming a popular solution. The reliability of this PUF by performing constant SUVs under internal noise and different environmental conditions is considered the main challenge [4]. Understanding several parameters that influence the SUV, and quantifying their influence is crucial for designing robust and reliable security systems based on SRAM-PUF. Therefore, this thesis aims to characterize the reliability of SRAM bit-cell in terms of its SUV reproducibility against external perturbations and internal noise. The impact of internal parameters (such as Threshold Voltage), and the external parameter (such as Temperature) are also investigated.

In this line, this work is focused in the characterization of the percentage of cells of a given SRAM cell design that are suitable to be used as PUFs. These cells should show more constant SUVs under different simulated perturbations. This is performed by electrical simulation and thus the percentage of suitable cells can be obtained at an early stage of the design phase. To achieve this, the SUVs of SRAM cells are simulated and a series of metrics based on Monte Carlo simulations involving process variation implemented using 65nm CMOS commercial technology, are proposed to contribute in quantifying the strength of the cell start-up behavior to the impact of the process variability, then, by correlating the distribution of each metric with the corresponding SUV of each SRAM cell. These metric based evaluations may be used at the design stages to adapt and change the SRAM implementation design to match the predicted number of PUF-suitable cells to the needs of the PUF. Of conversely, the PUF design can be modified to adapt to the expected SRAM performance.

Finally, some of these proposed metrics and other contents of this thesis have been published in a well-known conferences:

- Alheyasat, A., Torrens, G., Bota, S. and Alorda, B., 2019, November. Weak and Strong SRAM cells analysis in embedded memories for PUF applications. In 2019 XXXIV Conference on Design of Circuits and Integrated Systems (DCIS) (pp. 1-6). IEEE. (The main contributions and results of this paper are included in Subsections 2.1.1, 2.2.2 and 3.2.1 of this thesis).

- 2. Alheyasat, A., Torrens, G., Bota, S. and Alorda, B., 2020, October. Bit-Cell Selection Analysis for Embedded SRAM-Based PUF. In 2020 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 1-4). IEEE. (The main contributions and advanced results of this paper are presented in the following subsections of this thesis: 3.2.1, 3.4.1.1, 3.4.1.2, 3.4.3)

- 3. Alheyasat, A., Torrens, G., Bota, S. and Alorda, B., 2020, November. Selection of SRAM Cells to Improve Reliable PUF implementation using Cell Mismatch Metric. In 2020 XXXV Conference on Design of Circuits and Integrated Systems (DCIS) (pp. 1-6). IEEE. (Subsection 3.5.1 and Section 4.5 of this thesis are mainly based on the content of this conference paper)

Additionally, the last conference paper (Selection of SRAM Cells to Improve Reliable PUF implementation using Cell Mismatch Metric) is invited for publication in "Special Issue on Innovation in Computing, Engineering Science & Technology organized by Advances in Science, Technology and Engineering Systems Journal (ASTESJ)" and the Manuscript has been submitted with title "Selection of SRAM Cells to improve Reliable PUF implementation using Separatrix and Mismatch metrics". However, the main content

and construction of this thesis have been based on Article Manuscript that have been submitted to "Integration - Journal - Elsevier" with title of "SRAM-cells Reproducibility Characterization for Physical Unclonable Function Applications" and it is under review process.

#### 1.3 Thesis Outline

Chapter 2 provides an overview of the literature and the important background related to the work in this thesis. The definition of PUFs and the common application, such as cheap identification, authentication, cryptographic key generation and true random number generator, are discussed. The PUF classifications based on the location of physical process variation is summarized to finish the first part of this chapter. The principle of SUV as Source for SRAM-PUF will be discussed in the second part, where the process variation and mismatch are presented as a reason behind the entropy of SUV. Then, we present a state of the art of some techniques to enhance the reliability of SRAM-PUF. Finally, we introduce the preselection methods where the reliable SRAM cells can be detected and selected to increase the PUF reproducibility.

Chapter 3 presents the main contribution of the thesis. We characterize the SUV reproducibility proposing several mismatch metrics suitable to estimate reliability during design phases. The evaluation of the proposed metrics is based on a Monte Carlo simulations methodology. These metrics can be categorized based on the parameter they are based on: Inherent Mismatch-based metrics, Static Noise Margin (SNM) based metrics, Voltage Noise injection-based metrics and some metrics based on the dynamic start-up behavior.

Chapter 4 describes the other main contribution, which is exploring the potential influences of external and internal perturbations on the start-up behavior of SRAM cells, and hence on the reliability of PUF cell under these perturbations. Firstly, we characterize the impact of power supply Ramp-Up Time (RUT) on the SRAM-PUF. Similarly, the influence of Previously Stored Values (PSVs) into SRAM cells will be studied. We also analyze how the ambient temperature affect the SUV of the cells. These three perturbations are used to distinguish between the stable and unstable cells. Additionally, we present the impact of internal noise on start-up behavior to achieve the probability of memory cells to have a repeatable SUV under the induced voltage noise. Finally, all the proposed metrics in chapter 3 will be studied under these perturbations. Chapter 5 correlates both obtained results in Chapter 3 and 4 and their implications in terms of SRAM cell characterization. In other words, this chapter studies the robustness of the metrics in identifying the suitable PUF cells. Firstly, we define the most reliable SRAM cells, denoted as Strong cells, that tolerate all the perturbations described in Chapter 4. Secondly, we present and compares the ability of proposed metrics in identifying the Strong cells, also we describe the methodology of selecting those cells. Using the metrics, we explore the influence of selected cells length on the reliability of PUF operation in the last section. Where we finally present the methodology to estimate the percentage of suitable cells for PUF application.

Chapter 6 concludes the findings and contributions of the work in this thesis. It also suggests some recommendations for future work.

# **CHAPTER 2**

# **BACKGROUND**

The growing demand of IoT devices and applications increases the challenges in systems security. As a trusted root for these IoT devices, the embedded PUFs in the integrated circuits (ICs) are crucial for securing the devices and communication systems of IoT. By taking the advantage of random process variations, which are inherently produced during the manufacturing, PUFs can produce unique and unpredictable bits that can be used for various security applications.

This chapter presents an overview of the literature and subject background. In section 2.1 we discuss the definition of PUFs and its common application. Also, the PUF classifications to either extrinsic or intrinsic PUFs will be summarized. Section 2.2 explains the principle of SUV as Source for SRAM-PUF, discussing reasons behind the process variation and mismatch. Finally, we present a state of art on some techniques and preselection methods to enhance the reliability of SRAM-PUF, presenting the same goal where our approach is briefly introduced.

# 2.1 Physical Unclonable Function (PUF)

PUF is an emerging technology that provides a promising security solution with a relatively low complexity and cost. It operates by mapping a set of responses that corresponds to a set of challenges. Challenge-Response Pairs (CRPs) correlation are mainly determined by the inherent process variations in a silicon chip. These process variations are caused by uncontrollable manufacturing variations in the chip process.

These deviations are unpredictable and unique between different dies and wafers.

Hence, a PUF can be implemented to provide a unique and unpredictable CRPs.

Additionally, the randomness and complexity of inherent process variations makes a PUF physically and practically impossible to clone [5].

#### 2.1.1 Definition of a PUF

PUF is basically used to provide a signature from a physical device, so the definitions of PUF may change based on the purpose it is utilized for. Generally, a PUF can be defined by the words it contains from as follows [4]: *Physical* means it is not purely a mathematical function, but a physical object, and its output generated from physical interaction. *Unclonable* indicates how hard to predict or replicate its output. And *Function* means that it has an input (Challenge) to produce output (Response) based on physical parameters.

Recently, PUFs are becoming more popular in the area of semiconductor security. As semiconductor manufacturing processes have intrinsic variations. A circuit fabricated in silicon shows slightly different electrical behavior from one sample to another even though the wafer mask and design are identical. This is the basis of PUF, which in turn allows to improve the security level of several IC-based systems. The operation of a PUF is based on applying a challenge and measure its response. For each challenge, there should be a valid response to have an authenticated operation. In 2001, the concept of Physical One-Way Functions (POWFs) was proposed by Pappu for the first time [2]. Using challenge-response setup, the physical object can be exposed to many challenges, all of which generate an unpredictable response that is unique between different objects.

### 2.1.2 PUF Application

Security applications can rely on silicon implemented PUFs due to the unique and inherent features of each IC that are derived from process variations. The first application is Cryptographic Key Generation [6-8], which draws out the keys from the unique bits generated by embedded PUF. The second application is the device Authentication [9-10], which saves the unique PUF feature of each chip and it uses them later on to check if a chip can be authenticated or not. Finally, an important base block for many cryptographic security systems is the True Random Number Generator (TRNG), that can be based on the noise properties of PUFs [11-14].

#### 2.1.2.1 Cryptographic Key Generation

To improve the cryptographic key generation and storage applications, an alternative method based on PUFs can be exploited. Generally, Memory-based PUFs such as SRAM-PUF is typically applied for generating cryptographic keys [15 -16].

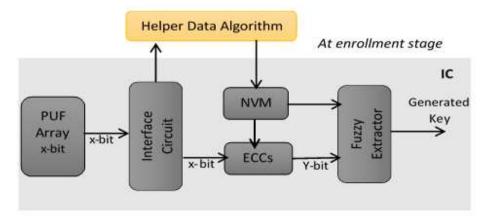

The principle of key generation based on PUF is summarized in Fig. 2.1. Firstly, a PUF array, that include entropy created from process variation, is readout using an interface circuit to convert the PUF output to digital bits, then these output bits are directed to the helper-data algorithm [6]. This algorithm usually operates off-chip to produce a sequent of helper data that will be used in the field to generate the key. The helper-data is then stored into an embedded NVM, where the data can be read without the ability to write, and this data is later-on utilized to reconstruct the required key for cryptographic application [7].

However, outputs from these PUF array are noisy because of environmental condition variations and ageing [17]. Therefore, direct PUF implementation for the cryptographic

Fig.2.1: Embedded PUF-based key generator.

key generation is not feasible; as this security application necessitates that the generated key is highly stable [8]. Based on that, there are two core functions that should be added to the PUF-based key generation scheme; the Error Correction Codes (ECCs) and fuzzy extractor in Fig. 2.1. The ECCs are needed to correct the noisy PUF readouts. While the purpose of the fuzzy extractors is to counteract the impact of non-uniformity of PUF bits, ensuring that the generated key will be in line with the specification required by this application. Next section (section 2.2) provides more details about these techniques.

Using PUF for cryptographic key generation has many advantages compared to traditional key generation using a secure NVM. Mainly, the feature of physical security is changed from NVM to the PUF, that is more immunized against physical attacks because it is very hard to measure the inherent process variations.

Unfortunately, using ECCs requires to increase area overheads as the bit error rate rises from noisy PUF [18-19]. This increase in the area overhead can reduce the interest of PUFs as a low-cost security object. As a motivation, we propose a bit-selection metric methodology in Chapter 3 to identify a subset of most reliable cells that has very low bit

error rate. Selecting only these cells for key generation can reduce the need for ECCs and hence the needed area overhead for such security application.

#### 2.1.2.2 Low-Cost Authentication

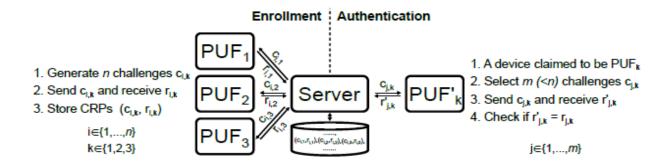

As another well-known application, the object authentication based on PUF is becoming more popular. The authors in [10] propose a lightweight object authentication structure implementing the so-called "strong PUF", their method relies on the well-known challenge-response authentication technique in [20]. The object authentication in these works consists of two stages as shown in Fig.2.2, the enrollment stage and the authentication stage.

In the enrollment stage, the server will randomly produce many challenges for each device that have the same embedded PUF. The devices will receive these challenges and they will send the responses to the server matching to each challenge, these CRPs will be stored as authentication references. Note that the enrollment stage should be done in a secure environment.

In the authentication stage, to verify if a device is registered in the server database, the server will select one of the challenges from the database and direct it to the device that requests authentication. Corresponding to the arrived challenge, the device will

Fig.2.2: Illustration of object authentication scheme based on PUF [10].

generate a response and send it back to be verified. This process may be repeated many times. If the server received enough verified responses, the device will be authenticated; else the device will be rejected.

As the remote connection between the devices and the server may have a public communication channel, the server should delete the used CRPs immediately after the authentication process; avoiding replay attack.

#### 2.1.2.3 True Random Number Generation (TRNG)

In this section, we will mention the possibility of implementing a PUF for random number generation [11-12,14]. Process variation can result in two kinds of PUF bit behavior. The *static* bit behavior, this behavior is related to the PUF circuits that are highly mismatched under the impact of process variations. Some designs may have well-matched elements, such as SRAM cell. These designs can work as a TRNG because they can be highly affected by internal circuit noise and very small variations in operating conditions. This is a *variable* bit behavior, that causes errors in the response of PUF.

Most often PUF designers assume that errors in the response are not useful. Alternatively, these errors can be used as a source of random numbers. However, the authors in [13] combined both behaviors to create a circuit that achieves both as a PUF and an RNG functions. This design provides the main two requirements for any cryptographic security systems: key and random number generation.

#### 2.1.3 PUF Classification

The PUFs can be classified based on the location of the physical randomness to *Extrinsic* based PUFs or *Intrinsic* based PUFs [21].

#### 2.1.3.1 Extrinsic based PUFs

Extrinsic based PUFs use the randomness that is explicitly shown in a physical system. To produce this randomness, the user or the manufacturer can have different choices of materials or size of particles; but the randomness distribution and their end location are out of control. Thus, these PUFs still have unique and random response. The main benefit of these types of PUFs that provide an extrinsic randomness, their parameters can be controlled and optimized in such a way to improve the uniqueness and reliability for these PUFs. The main examples of these types of PUF are the *Coating-PUFs* [22] and *Optical PUFs* [23]. The coating-PUF is based on the random sized dielectric particles that contained in the protective opaque coating at the top layer of an IC, while the optical-PUF is based on a transparent medium like glass, where light scattering particles are explicitly brought in. The position of light scattering particles in the medium is totally unpredictable providing a unique unpredictable property for this PUF.

#### 2.1.3.2 Intrinsic based PUFs

Different from Extrinsic based PUFs, the *Intrinsic* based PUFs utilize the randomness that exist intrinsically in them to function. This intrinsic randomness is a result of process variation throughout the fabrication process that is uncontrollable and naturally random. Recently, such type of PUF has been more popular and attractive, as they can be implemented without needing any modifications to PUF circuit and manufacturing process. Another benefit of intrinsic based PUFs is that most of these PUFs provide a digital output ("1" or "0" response) reducing the need for quantization process before implementing them in security application. Mainly, there are three types of Intrinsic based PUFs [21]: *Silicon-PUFs* operates based on the random variations in transistor gate and wire delays in a circuit [24], *Buttery-PUFs* is mainly used to protect the Intellectual

Property (IP) in FPGAs that do not have integrated memories by creating structures within the FPGA matrix which behave similarly to an SRAM bit-cell during the power-up phase[25], and SRAM-PUF [26] that have utilized for this thesis work.

#### 2.2 SRAM-PUF

A PUF instance can be contained within an IoT devices using two main approaches: adding a specialized primitive designed to offer the unclonable function, or reusing a non-specific and pre-existing circuit. Following the second approach, SRAM circuits were proposed for PUF implementation as its possible to take benefit of the positive feedback loop inherent of SRAM bit-cells to generate a unique, stable and unclonable binary response. As these memories are widely included in digital systems, power consumption and costs requirements can be minimized while creating embedded security resources for IoT systems.

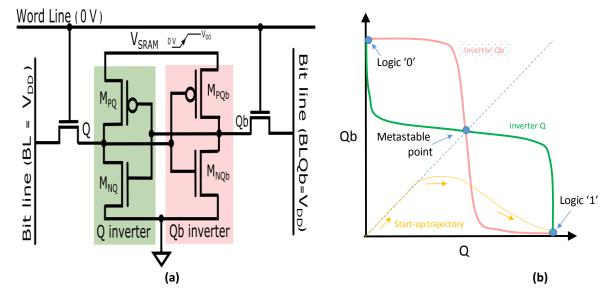

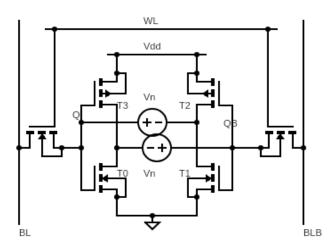

#### 2.2.1 SRAM Cell Architecture

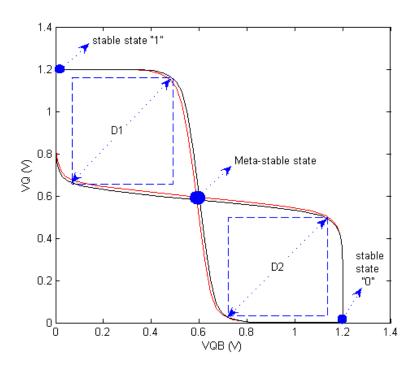

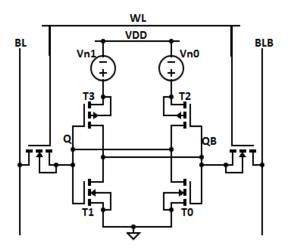

A six transistors (6T) memory cell topology is very common to use among different SRAM cell topologies (such as 7T, 8T, 10T). Although, this work uses 6T memory cell, the same methodologies, that will be explained, can be extrapolated to rest cell topologies. The 6T cell consists of two access transistors controlled by the word-line (WL), and two cross-feedback inverters creating a latch circuit, see Fig 2.3 (a). The 6T-SRAM cell has three equilibrium points: two stable points corresponding to logic '0' and logic '1', and a third meta-stable point corresponding to the cross point of the voltage transfer characteristics (VTC) plot of the latch as in Fig 2.3 (b). The SRAMs are intended to work in three modes: Hold operation (as in Fig 2.3 (a) when WL=0 V, then the internal nodes are isolated), Read and Write operations. For stable operation, depending on which

combination, a logic "1" or "0" is stored. One of the internal nodes (Q and QB nodes, see

Fig 2.3 (a)) should be at low voltage (0 V) and the other at high voltage (Vdd).

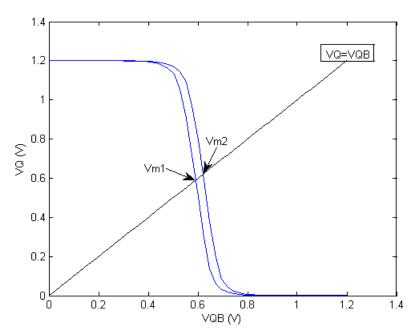

**Fig.2.3:** (a) 6T SRAM cell schematic in hold mode. (b) Latch voltage transfer characteristics; the dashed line represents the transient start-up behavior (assuming the final output is logic '1').

To read logic '0' and logic '1' from SRAM cell, the read operation is done by firstly pre-charging the bit-lines ( $BL_Q$ ,  $BL_{Qb}$ ). A pre-charge circuit is implemented to control the bit-lines ensuring the same voltage at both bit-lines. When both the bit-lines have the same voltage, the Word Line of the selected cell is activated. Depending on the stored value in the cell, one of the bit-lines will remain the voltage and the other one will be discharged. The voltage difference between bit-lines is detected and amplified by a sense amplifier to evaluate the read output.

The write operation is achieved by pulling one of the bit-lines ( $BL_Q$ ,  $BL_{Qb}$ ) to low level and the other to high level. The write driver is implemented to pull down either  $BL_Q$  or  $BL_{Qb}$  based on the value that is intended to be written into the cell. Then, the Word Line of the selected cell is activated. The feedback of the cross-coupled inverters will oppose to the write process. Despite of that, each of the internal nodes ends up having the same voltage logical level of the bit-line value it is connected to through pass transistors.

An ideal 6T-cell is designed to keep the data during read accesses and permit modifying the stored logic value during write operations, independently of the stored content (logic '0' or logic '1'). Thus, the two inverters of the SRAM cell should be as identical as possible to produce symmetrical performance during both write and read operations.

In Hold-operation configuration (see Fig 2.3 (a)), the word line is set to a low voltage level and both the internal nodes are isolated from the bit-lines. Using this setup, in addition to controlling the cell voltage supply ( $V_{SRAM}$ ), allows SRAM circuit to operate as a PUF; as it will be discussed in the next section.

#### 2.2.2 SRAM SUV as Source for SRAM PUF

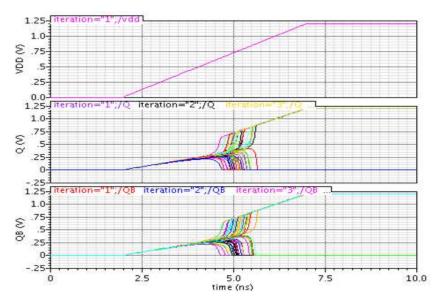

At power-up, the internal nodes of the cells are discharged (Q = 0V and Qb = 0V, see Fig 2.3 (a)), setting the Word Line to low voltage, these nodes are isolated from the bit-lines as the access transistors are in the cut-off region. Once the power is ramping up, at first, the voltages of the internal nodes increase equally. Through this period, the memory cell stays in its meta-stable point until the supply voltage exceeds a certain threshold value (different for each cell), from this moment, the effect of the feedback, together with the influence of the mismatch between inverters, will cause the cell to transition towards one of the two stable states as shown in Fig.2.4. Therefore, for a perfectly symmetrical SRAM cell, the final state will only be determined by the noise and environmental conditions, which are unknown. Fig.2.4 shows start-up behavior during ramping-up of the power supply voltage for 50 memory cells, these curves are obtained using Monte Carlo simulation to mimic the mismatch inside the cell and the process variation between the proposed cells.

The SRAM PUF primitive is based on the circumstance that, even though the cell design is symmetrical, the manufacturing process variations generates mismatch between cross-coupled inverters reducing the intrinsic symmetry of the cell, and leading it to one of the two stable states with more probability than the other [27]. The variation in the final SUV of the cells in Fig. 2.4 is mainly caused by the non-controlled physical variations that are inherently produced in each cell during their manufacturing process. Hence, the response of a set of SRAM cells will be unpredictable, unique, and unclonable.

Fig.2.4: Start-up behavior for 50 cells when the power supply is ramped up.

Based on that, implementing an SRAM PUF in a circuit only needs to control the power supply of the SRAM core cells. So, the needs to modify the SRAM are minimal and thus it can be applied to any non-specific embedded memories.

Designing SRAM requires the cell to be as symmetric as possible aiming to decrease any bias to a preferred value. Highly symmetrical cells, which are less affected by process variability, will be characterized by varying their SUV between different start-ups. If a cell is started-up N times, it will choose  $n_1$  times a logical '1' SUV, and  $n_0$  times a logical '0' SUV. Then, the probability that the cell has a logical '1' SUV (or to logical '0') is

presented in the following equations:

$$p_1 = \frac{n_1}{N} {(2.1)}$$

$$p_0 = \frac{n_0}{N} = 1 - p_1 \tag{2.2}$$

From here, we can define the SUV reproducibility of a cell as:

$$r_{SUV} = |p_1 - p_0| (2.3)$$

For reliable PUF implementation, it is essential to select those cells that have significant inherent-mismatch to achieve  $r_{SUV}$  to be one or near one. These cells are typically denoted as strong cells from a PUF point of view. However, applying SRAM for TRNG applications requires that cells that are highly symmetrical with  $r_{SUV}$  around zero.

# 2.2.3 State of Art on SRAM-PUF Reliability Enhancement

Knowing the SUV reproducibility distribution at early design stages is essential to decide if a proposed memory scheme is suitable for specific application that requires PUF implementation. Additionally, the early knowledge of the percentage of strong cells will be useful to decide whether the SRAM-PUF can be implemented as it is without modification, or if it will be necessary to apply some reliability techniques. Among the available reliability techniques, we can find the inclusion of error correction codes [28-33], or Majority Voting techniques [4, 34-36]. Applying some of them implies the acceptance of some drawbacks like increasing the design complexity, or increasing power consumption and response time. Another method that can be used to improve SUV reproducibility is based on taking advantage of long period degradation mechanisms of the devices. These mechanisms, known as Burn-in Enhancement, aim to

increase the mismatch within cells and can, hence, producing more reproducible PUF data [38-40]. The next sections will discuss these methods and techniques and their feasibility.

#### 2.2.3.1 Error Correcting Codes (ECCs)

As mentioned previously, PUF outputs are noisy because of environmental condition variations and ageing [17]. Therefore, direct PUF implementation for applications such key generation is normally not feasible. Several methodologies for ECC have been proposed, and most of them have a drawback of an extra cost overhead when being physically implemented.

Some recent designs of ECC for PUF-based key generation suggested the usage of 2-D Hamming Codes [10] [28]. The 2-D Hamming Code reformats the PUF response into a matrix having rows and columns. These codes are applied to generate redundant data for each column and row of the matrix. This data as well as parity bits is utilized to correct these errors in the noisy PUF responses. The main disadvantage of this code is that the generated matrix for PUF cannot contain more than two errors within one row to have a successful operation.

A more improved ECC technique for PUFs uses Bose-Chaudhuri-Hocquenghem (BCH) codes [29]. The implementation of this technique was able to correct 30 errors in a 255 PUF-bits response. Unfortunately, this implementation exposed 192 bits to be used as a Helper Data, so it limited the key size to 63 bits.

Some other approaches for improving PUFs error correction have been proposed.

Index-Based-Syndrome (IBS) [28] is more immunized to data leak than conventional ECCs that utilize bitwise XOR-masks. Other enhancements involve soft decision data to

be included within Helper Data Algorithm to reduce the number of PUF bits needed to generate one bit for secure key generation [3]. To reduce the complexity of ECC, the authors in [30] introduce two stage coding that consist of using a syndrome generation based on XOR-mask and repetition coding, more details about these coding will be described in the next section.

As all the previously mentioned methods focus on ECC itself, other researches recommend reducing ECC overhead which is the main drawback this technique. The required Helper Data to produce a secret key increases with increasing the errors in the PUF response exposing more data about the PUF response. Therefore, to ensure a secure key generation, the number of response bits have to be increased to correct as much as possible the errors in the response and reducing the need to expose more data. The area overhead needed for ECC, associated with the increment in the number of PUF response bits, grows linearly with the error rate [31]. The area overhead can be reduced as the PUF reliability increases. Such as in PUF implementation based on FPGA, reducing the error rate from 10% to 3% can save up to 40% of the area overhead [32]. Similarly, ASIC applications using PUFs demonstrate that 60% of area is saved as the error rate decreases from 20% to 5% [33].

#### 2.2.3.2 Majority Voting Methods

Majority voting has been proposed as a useful technique to enhance the reliability of a PUF cell [34-35]. This technique could effectively improve PUF reliability If the response is highly affected by environmental and transient noise.

Majority voting can be divided into two types: space majority voting or temporal majority voting. In temporal majority voting, each bit in the PUF response is challenged

several times and the final output of this bit is defined as the majority of the outputs [35]. Implementing this method, the error rate could be effectively reduced [34]. However, it is only useful for correcting the error rate up to 8% [36]. The main drawback of this type of majority voting is the extra runtime. In addition, its reliability cannot be assured, because some PUF bit-cells might either vary its output under environmental conditions, but others might be well-matched bit-cell, in such case, the majority is near to even [37].

On the other hand, the space Majority voting, also denoted as repetition coding, produces one reliable bit voting between a few unreliable PUF cells. The drawback is that it requires extra area, power, and more PUF cells [4].

#### 2.2.3.3 Post-Fabrication Burn-in Enhancement

The post-fabrication burn-in technique is based on using a mechanism to degrade the devices for long-terms. The idea of this technique is to intentionally take advantage of specific aging effects, and induce them into the PUF circuit. This is done by providing additional run time while the circuit is subjected to temperature and voltage stress, with the goal to cause a time-based variability in addition to the pre-existing variability generated by process variations. Once these time-based variabilities are produced in the planned direction, they can increase mismatch inside the cells, and thus can produce more reliable PUF outputs.

As an example, exploring the Bias Temperature Instability (BTI) degradation in the SRAM-PUFs is explained in [38], where the process variation is only considered for P-MOS transistors. As the SRAM PUF keeps storing the SUVs in the cells, the transistors will display the stress condition. P-MOS transistor that have higher threshold voltage

(*Vth*) will be affected more by the stress, and its *Vth* will decrease as long as the same stress condition is applied. As the higher *Vth* is decreasing, the mismatch between the P-MOS pair will also decrease; which reduces the reproducibility of this PUF, and makes it less immunized against noise. To solve this issue, the authors of [38] also proposed a solution. The method is to store the opposite of the SUVs by re-programming the whole SRAM-PUF array aiming to increase the mismatch in the cells, and thus their reliability.

It is important to mention that It needs long time for these BTI stresses to be effective under nominal conditions, and hence, this method requires to be accelerated by increasing the temperature and voltage. This process still needs many hours up to days to produce a good result.

The burn-in enhancement methods are also proposed for specific PUF implementations. A method is presented in [39], implementing a sense-amplifier PUF (SA-PUF) including burn-in function to explore the HCI degradation mechanism. Another method is the hybrid-PUF that uses BTI mechanism for burn-in improvement [34, 40].

PUF implementations using these burn-in methods have resulted in improving the stability of the generated data. Besides their advantage, the main drawback is the required time and cost, as discussed in [38].

# 2.2.4 Direct and Indirect Preselection Approaches

To overcome some of the drawbacks of the previous methods, PUF-bit preselection approaches have been proposed [18,41-44]. In these approaches, the unreliable PUF-bits are identified in the PUF array and then masked out from the PUF response. However, these methods can be divided into direct and indirect PUF-bit preselection. In case of direct preselection, during the testing stage, the PUF-bit array is challenged

several times under wide range of operational and environmental conditions, such as different power supply and temperatures variations. The cells that display unstable behavior are directly marked and their pattern in the array is saved, to be excluded from PUF response. The disadvantage of this type of preselection that it requires massive tests and thus it will be expensive in test time, also it will be not totally reliable as its impossible to predict all the operational and environmental conditions. In the works [34, 40], results show that implementing this method can improve reliability of PUF response, especially when increasing the number of the PUF test preformed at different conditions, as it may detect more unstable cells.

The indirect PUF-bit preselection method is based on a test that indirectly detects the unstable PUF-bits; this test is done for each of the PUF bits [4]. If a PUF-bit passes the test, it will be classified as stable and could be implemented to generate the PUF response. The indirect preselection may detect all the unstable PUF-bit, but it may classify some of the stable PUF-bits as unstable, decreasing the number of suitable bits in the response [44]. The preselection pattern of those stable cells can be saved in NVM, as in [18] and [45-46].

#### 2.2.4.1 Our Approach

Tacking profit of the indirect preselection approaches, we propose a metric-based methodology obtained by simulation to characterize the reproducibility of SUV (r<sub>SUV</sub>) for SRAM-PUF implementation. The simulated metrics are evaluated based on internal SRAM parameters affected by process variation and mismatch. The proposed metrics can be simulated under any single operational and temperature conditions. The idea of our metric methodology is to assign a value for each SRAM cell in the proposed memory to represent how reliable the cell will be under the impact of internal and external

perturbations. Such that, the cells that have higher values of a metric are considered more reliable and its SUV will be more reproducible under these perturbations. Including only this type of cells in the PUF will improve the quality of its response. By contrast, lower metric values will expose the cells that have low reproducibility in their SUVs. Even though these cells should be ignored and masked out for PUF applications such key generation, some of them could be useful as a source of randomness for TRNG applications, however, this fact is out of the scope of this thesis and it has not been studied. The next chapter will provide the detailed methodology of these metrics.

# **CHAPTER 3**

# METRICS METHODOLOGY FOR IMPROVING

# **SRAM-PUF RELIABILITY**

SRAM PUFs use the start-up value (SUV) of an SRAM cell for PUF application such as cryptographic key generation as discussed in previous chapter. The reliability and the stability of this start-up behavior is a crucial issue that requires to be ensured when using SRAM cells as a PUF. This chapter uses several simulation-based metrics to investigate the parameters affecting the reliability of SUV based SRAM PUFs. Additionally, we characterize the SUV reproducibility proposing several mismatch metrics suitable for reliability estimation during design phases.

# 3.1 Simulation Environment Setup

The proposed metrics are applied to the common 6T SRAM design using Cadence Environment, see the schematic in chapter 2 in Fig.2.3 (a). The Virtuoso Schematic Editor is utilized to draw the circuit and Spectre Simulator is used to simulate the proposed SRAM design implemented on commercial 65nm CMOS technology. This technology provides three types of transistor based on threshold voltage parameter, such as Low Power Standard Threshold Voltage CMOS (Ipsvt), Low Power High Threshold Voltage CMOS (Iphvt) and Low Power Low Threshold Voltage CMOS (Ipsvt); while in this work the Ipsvt CMOS is used. However, the SRAM cell Schematic is powered utilizing a Voltage Piecewise linear (Vpwl) source, as obtaining the SUV of SRAM cell (see section

2.2) requires controlling the source ramp-up voltage and time. Similarly, both Bit-Lines (BL, BLB) and Word-Line (WL) are controlled by same type of voltage source. The Vpwl source allows us to adjust the magnitude and the speed of ramp-up voltage (Vdd) and to turn on and off the BL, BLB, WL.

AL the simulations in this chapter utilize Monte Carlo analysis provided by Spectre Simulator to mimic the inherent mismatch between the transistors inside SRAM cell, also we applied Process Variation feature to mimic different SRAM cells. In this work, we propose 1000 cells SRAM array represented by 1000 Monte Carlo iterations. To have a fixed Monte Carlo iteration order for all simulations in this thesis, the location of the simulated transistors on the Schematic is fixed through this work simulations, as we observed that changing only the transistor location can highly affect the distribution of Monte Carlo; such that a new random parameter values are generated for each iteration. In the following sections, we introduce the new metrics methodology where some of them are evaluated implementing DC-Monte Carlo Simulations while the rest of metrics by Transient-Monte Carlo Simulations. Based on that, the chapter simulations are divided into:

#### 1-DC Monte Carlo Simulations

Section.3.2 presents two metrics to model the inherent-cell mismatch. A metric based on the threshold voltage differences is proposed. In this sense, the Spectre Simulator provides three types of threshold voltage to be calculated: Model *Vth*, Transient *Vth* and DC *Vth*. However, the Model *Vth* is utilized for this metric calculation, as it has a fixed value regardless the type of simulation. The other metric is based on the distance between VTCs for the individual inverters of the SRAM cell. The DC Simulation is mainly

utilized to draw the VTCs, as proposed in [47], for both inverters; where the voltage switching points are calculated. Similarly, the metrics in *Section.3.3* are based on the SNM concept and are evaluated using the same DC-VTCs methodology to draw the SNM-based butterfly diagram.

#### 2- Transient Monte Carlo Simulations

The SUV for each cell is evaluated using transient simulation. At power-up, the cell remains in retention operation, that is, the access transistors are cut-off (WL = 0 V) and the memory cell is isolated from the bit-lines. In this sense, we found that starting-up the cell either with discharged bit-lines (BL=0 V, BLB=0 V) or with fully charged bit-lines (BL=Vdd, BLB=Vdd) will slightly affect the final SUV for the cells in the proposed memory; as only 0.24% of the cells have different SUV for both cases.

This chapter uses a reference SUVs set for the proposed SRAM array to validate the prediction ability of the proposed metrics. While the internal nodes of the memory cell are discharged by setting the initial nodes conditions to Q = 0 V and QB = 0 V, this reference SUV is obtained by ramping the cell power supply from 0 V to 1.2 V in 5ns under nominal temperature (27° C).

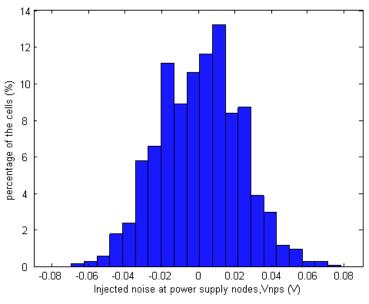

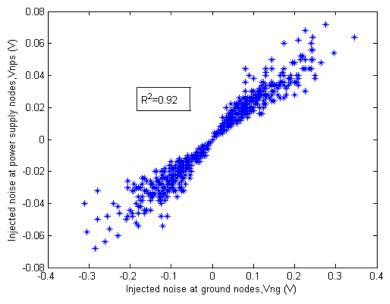

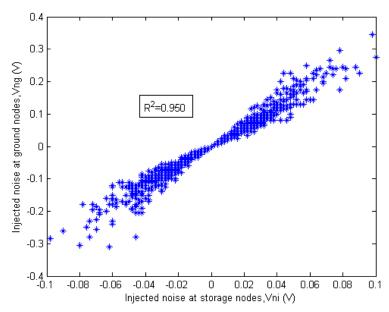

Using similar Transient simulations settings, we obtained the metrics in *Section.3.4* and *Section.3.5*. But, in *Section.3.4*, two Vpwl sources are utilized to inject voltage noise at different locations of SRAM cell aiming to estimate inherent-cell mismatch. While in *Section.3.5*, the *SID* metric methodology is based on varying the initial nodes conditions from the reference values (VQ=0 V, VQB=0V).

Finally, the resulting data from both type of simulations are collected and organized using Open Command Environment for Analysis (OCEAN) Script. This tool is a powerful

programming language that can automate the simulations within Cadence. It is a subset of SKILL language and uses this language to configure the design environment. Then all the resulting data are transferred to MATLAB environment, where we analyzed them to produce the results and figures in this chapter.

# 3.2 Reliability Metrics based on Inherent-Cell Mismatch

All SRAM cells have inherent mismatch caused by fabrication process variations. In this work, the mismatch in SRAM cell is calculated based on two different transistors and inverters parameters. Generally, the mismatch metric is based on Parameter distance (*Pd*) defined as the difference between some parameter values, S, that accounts for the trend that an inverter has in attaining one of the two possible logic states.

$$Pd = S(inv_Q) - S(inv_{QB})$$

(3.1)

This section introduces two mismatch metrics based on selecting the S to be related to: firstly, the transistors *Threshold Voltage* parameter. Secondly, the inverters *Switching Voltage Point*.

#### 3.2.1 Threshold Voltage Distance Between the Individual Transistors

There are several transistor parameters that may contribute to SUV behavior. When power is applied to the memory, the SRAM cells will reach a final SUV that depends primarily on threshold voltage (*Vth*) mismatch of the constituent transistors [48], [49], [50]. In [49], the authors apply *Vth* mismatch to define the adequate cells for PUF application. Their definition of the mismatch only considers the *Vth* mismatch of N-MOS transistors while the mismatch in P-MOS transistors is neglected. However, the *Vth*

mismatch of N-MOS transistors is controlled by the transistor area; a smaller area generates higher mismatch. On the other hand, the work in [50] only considers the process variation and mismatch in P-MOS transistors to select SRAM cells to be used as a TRNG. In this work, both P-MOS and N-MOS Vth mismatch are implemented to define the Threshold Voltage Parameter Distance ( $Pd_{Vtho}$ ).

Firstly, Monte Carlo simulation is applied to mimic the process variation and mismatch and then a DC simulation in Spectre simulator is utilized to observe and save the Vth for the transistors (Mp3, Mp2, Mn0, Mn1), see Fig.3.1. Secondly, the SUV for each cell of the memory is obtained by transient simulation under the reference conditions as discussed in Section 3.1.