UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING OF MULIPLE GATE MOS DEVICES. Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

# **COMPACT MODELING OF MULTIPLE GATE MOS DEVICES**

A Thesis Presented to

The University of Rovira i Virgili

Department of Electronic, Electrical and Automatic Engineering

Ву

### HAMDY MOHAMED ABD ELHAMID

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical and Electronics Engineering

### Advisor

**Professor Benjamin Iniguez**

University of Rovira i Virgili

Tarragona-Spain 2007

## **Contents**

| List of symbols                                                                        | 1    |

|----------------------------------------------------------------------------------------|------|

| List of figures                                                                        | 3    |

| List of publications                                                                   | 6    |

| Acknowledgement                                                                        | 9    |

|                                                                                        |      |

| CHAPTER ONE: Multiple Gate MOS Devices Structures and Performances                     |      |

| 1-A Introduction                                                                       |      |

| 1-B FABRICATING CHALLENGES                                                             |      |

| 1-C Modeling Challenges                                                                | 21   |

| <b>CHAPTER TWO</b> : Short Channel Effects (SCEs) in Undoped Multiple Gate MOS Devices |      |

| (2-A) PART (I): SHORT CHANNEL EFFECTS (SCES) IN UNDOPED CYLINDRICAL GATE ALL           |      |

| Around MOSFET                                                                          |      |

| 2A-1 Introduction                                                                      |      |

| 2A-2 Potential Model Derivation                                                        |      |

| 2A-3 Threshold voltage derivation                                                      |      |

| 2A-4 Threshold Voltage and its sensitivity                                             | 40   |

| 2A-5 Subthreshold swing model                                                          | 42   |

| (2-A) PART (II): SHORT CHANNEL EFFECTS (SCES) IN UNDOPED CYLINDRICAL GATE ALL          |      |

| AROUND MOSFET INCLUDING DIBL EFFECTS                                                   | 44   |

| 2A-6 Potential Model Derivation                                                        | 44   |

| 2A-7 Virtual Cathode: Value and position                                               | 49   |

| 2A-8 Inversion charge and Threshold voltage                                            | 51   |

| 2A-9 Subthreshold Swing model                                                          |      |

| (2-B) SHORT CHANNEL EFFECTS (SCES) IN UNDOPED DOUBLE GATE MOSFET                       | 58   |

| 2B-1 Introduction                                                                      | 58   |

| 2B-2 Potential Model Derivation                                                        | 60   |

| 2B-3 Virtual Cathode: Value and position                                               | 68   |

| 2B-4 Inversion charge and Threshold voltage                                            | 69   |

| 2B-5 Subthreshold Swing model                                                          | 73   |

| (2-C) A 3-D ANALYTICAL PHYSICALLY-BASED MODELS FOR SHORT CHANNEL EFFECTS IN            |      |

| UNDOPED FINFETS                                                                        | 76   |

| 2C-1 Introduction                                                                      | 76   |

| 2C-2 Potential Model Derivation                                                        | 78   |

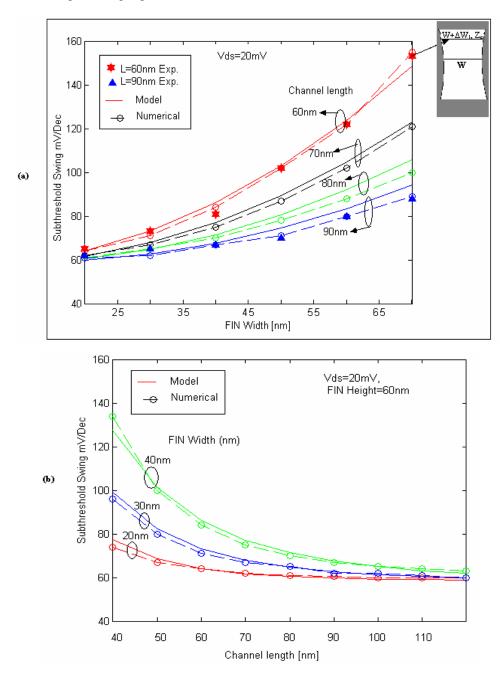

| 2C-3 Subthreshold Swing Model                                                          |      |

| 2C-4 Threshold Voltage Model                                                           |      |

| (2D) SCALABILITY LIMITS OF SURROUNDING GATE MOSFETS AND DOUBLE GATE MOSFET             | \[S  |

|                                                                                        |      |

| CHAPTER THREE: Current Transport in Undoped Multiple Gate MOS Devices                  |      |

| (3A) EXPLICIT CONTINUOUS MODEL FOR LONG CHANNEL UNDOPED MULTIPLE GATE MOSI             | FETS |

| (ST) EXELECT CONTINUOUS MODEL FOR EGING CHARNEL CINDOLED MODIL EL GATE MODE            |      |

| 3A-1 Introduction                                                                      |      |

| 3A-2 GAA Model and results.                                                            |      |

| 31.2 Girl Model and results                                                            |      |

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING OF MULIPLE GATE MOS DEVICES. Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

|                                                                           | 3   |

|---------------------------------------------------------------------------|-----|

| SCEs in undoped multiple gate MOS                                         |     |

| 3A-4 DG MOSFET Model                                                      | 131 |

| (3B) BALLISTIC AND QUASI BALLISTIC TRANSPORT IN                           | 135 |

| UNDOPED MULTIPLE GATE MOS DEVICES                                         | 135 |

| 3B-1 Introduction                                                         | 135 |

| 3B-2 Ballistic and Quasi Ballistic Transport In DG and GAA MOSFETs        | 138 |

| 3B-3 Quasi Ballistic Transport in undoped FinFET devices                  | 151 |

| <b>CHAPTER FOUR</b> : Conclusions and recommendations for the future work |     |

| 4-1 Summary                                                               | 157 |

| 4-2 RECOMMENDATIONS FOR THE FUTURE WORK                                   | 159 |

| APPENDIX (2A-1)                                                           | 161 |

| APPENDIX (2A-2)                                                           | 165 |

| APPENDIX (2-B)                                                            | 170 |

| APPENDIX (2-C)                                                            | 180 |

REFERENCES ......211

### LIST OF SYMBOLS

k – Boltzmann constant

n – free electron concentration

$n_i$  – intrinsic electron density, 1.45\*10<sup>10</sup> cm<sup>-3</sup> at 300 K

q – electron charge

$t_{ox}$  – gate oxide thickness

$t_{Si}$  – silicon film thickness

$E_g$  – silicon band gap, 1.12 eV at 300 K

$I_D$  – drain current

L – channel length

$N_A$  – channel doping concentration (of acceptors)

$N_{D/S}$  – source/drain doping concentration (n+ type)

$Q_{TH}$  – a real density of free carriers under threshold conditions

S – subthreshold swing

T – absolute temperature

$V_{bi,i}$  – junction built-in voltage between the source/drain and intrinsic silicon

$V_{DS}$  – drain-to-source voltage

$V_{GS}$  – gate-to-source voltage

$V_{TH}$  – threshold voltage

$V_{TH,long}$  – long channel threshold voltage

$\Delta V_{TH}$  – threshold voltage roll-off

$\beta$  – reciprocal of thermal voltage, q/(kT), 38.68  $V^{-1}$  at 300 K

$\varepsilon_0$  – dielectric constant of vacuum,  $8.854*10^{-12} F*m^{-1}$

$\varepsilon_{Si}$  – relative dielectric constant of silicon, 11.9

$\varepsilon_{ox}$  – relative dielectric constant of silicon oxide, 3.9

$\phi_B$  – difference between Fermi level and intrinsic level in silicon

$\phi_F$  – difference between Fermi level and electron quasi-Fermi level

$\lambda_{Di}$  – intrinsic Debye length, 48.49  $\mu m$  at 300 K.

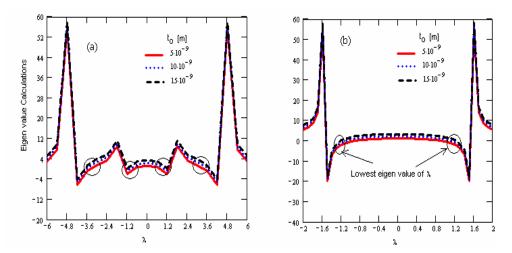

$\lambda_j$  – eigenvalues, j=1, 2, 3, ...

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING OF MULIPLE GATE MOS DEVICES. Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

5

### SCEs in undoped multiple gate MOS

- $\lambda_I$  lowest-order eigenvalue, length scale

- $\chi$  electron affinity in silicon, 4.05 eV

- φ electrostatic potential referenced to Fermi level

- $\phi_{\it ms}$  work function difference between gate material and silicon channel

- r back scattering coeffeicent

- $\eta$  fermi energy level

- g<sub>d</sub>- transconductance

- g<sub>d</sub> -channel conductance

- v thermal velocity

6

SCEs in undoped multiple gate MOS

# **LIST OF FIGURES**

| Fig. 1The existing gate configuration for thin-film SOI MOSFETs                                |

|------------------------------------------------------------------------------------------------|

| Fig. 2 Schematic and TEM cross section of a FinFET                                             |

| Fig. 3 Cross-sectional views of the optimized cubical-channel MOSFETs                          |

| Fig.4 TEM view of a single and four channel wrap-around-gate MOSFET                            |

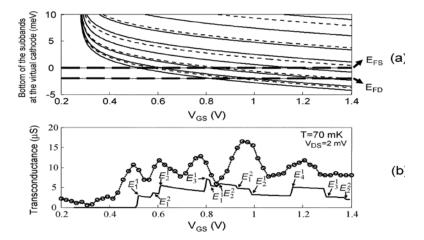

| Fig. 5. Bottom of subbands and transconductance characteristics of GAA MOSFET23                |

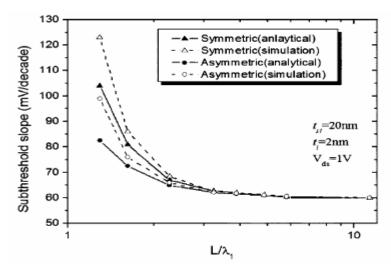

| Fig. 6. Analytical solutions of the subthreshold for symmetric and asymmetric DG MOSFETs24     |

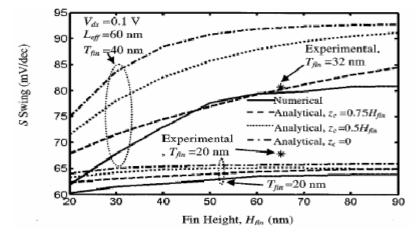

| Fig. 7. Comparison of subthreshold swing from numerical and analytical25                       |

|                                                                                                |

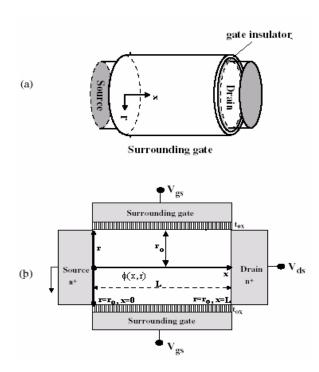

| Fig. 2A-1GAA MOSFET: Structure, and cross section                                              |

| Fig.2A-2 GAA MOSFET: Potential along the channel at low drain-source voltage34                 |

| Fig.2A-3 GAA MOSFET: Threshold voltage vs silicon thickness at low Vds                         |

| Fig. 2A-4 GAA MOSFET: Threshold voltage vs the channel length at low drain-source voltage38    |

| Fig. 2A-5 GAA MOSFET: Subthreshold swing at low drain-source voltage                           |

| Fig. 2A-6 GAA MOSFET: Surface potential distribution along the channel at high Vds45           |

| Fig.2A-7 GAA MOSFET: Virtual cathode position vs. Drain-Source Voltage                         |

| Fig. 2A-8 GAA MOSFET: Threshold voltage vs. channel radius, for different Vds48                |

| Fig. 2A-9 GAA MOSFET: Threshold voltage                                                        |

| Fig. 2A-10 GAA MOSFET: Threshold Voltage Roll-off vs. channel length                           |

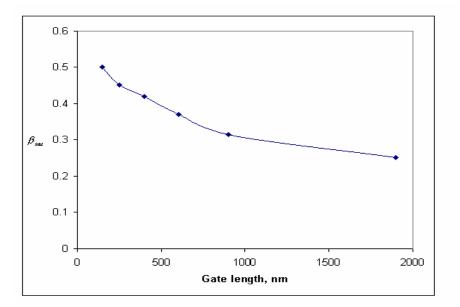

| Fig. 2A-11 GAA MOSFET: Drain Induced Barrier Lowering coefficient vs. channel length50         |

| Fig. 2A-12 GAA MOSFET: Subthreshold swing at low drain-source voltage                          |

| Fig. 2A-13 GAA MOSFET: Subthreshold swing for Gate All Around MOSFET at high $V_{\text{ds}}52$ |

| Eig 2D 1 DC MOSEET, Davies structure and areas section                                         |

| Fig. 2B-1 DG-MOSFET: Device structure, and cross section                                       |

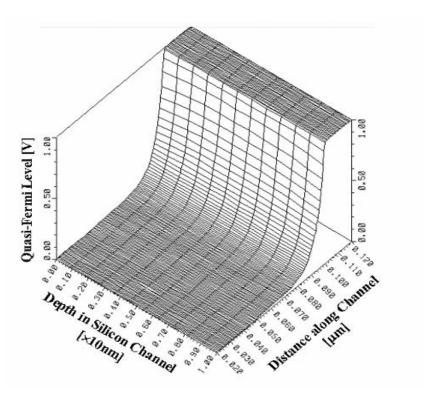

| Fig. 2B-2 DG MOSFET: Quasi Fermi Potential for DG MOSFET                                       |

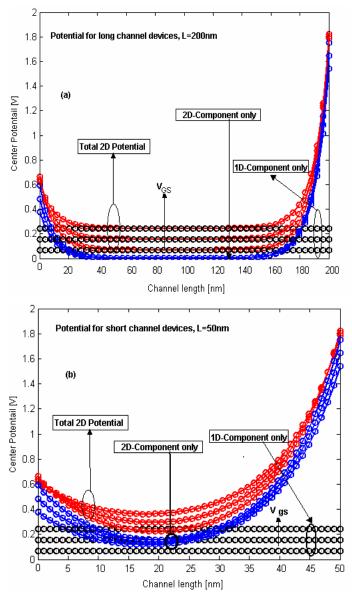

| Fig. 2B-3 DG MOSFET: Center potential distribution along the channel                           |

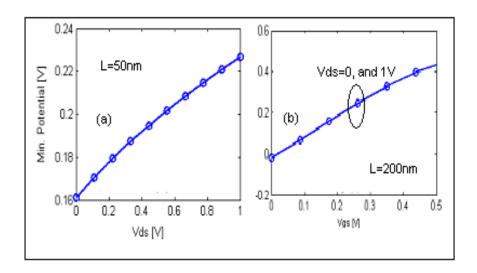

| Fig. 2B-4 DG MOSFET: Minimum potential                                                         |

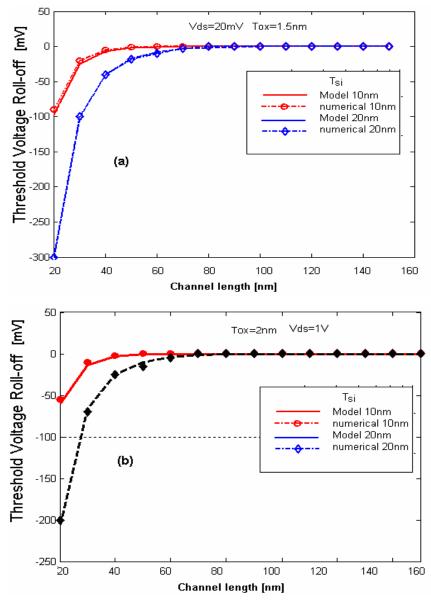

| Fig. 2B-5 DG MOSFET: Threshold Voltage Roll-off vs. channel length                             |

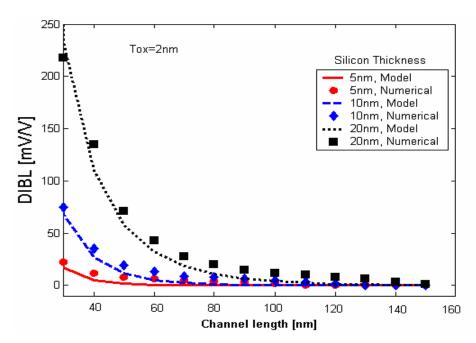

| Fig. 2B-6 DG MOSFET: Drain Induced Barrier Lowering coefficient                                |

| Fig. 2B-7 DG MOSFET: Virtual cathode position vs. channel length                               |

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING OF MULIPLE GATE MOS DEVICES. Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

| SCEs in undoped multiple gate MOS                                                      |     |

|----------------------------------------------------------------------------------------|-----|

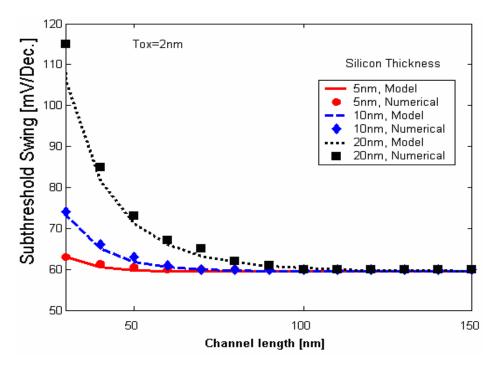

| Fig.2B-8 DG MOSFET: Subthreshold swing                                                 | 69  |

| Fig. 2C-1 FinFET: Cross section for this work.                                         | 72  |

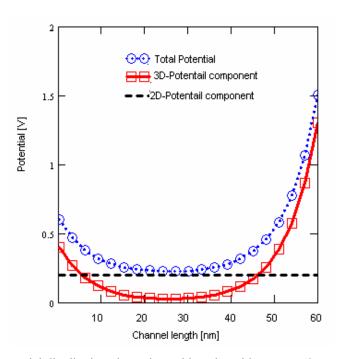

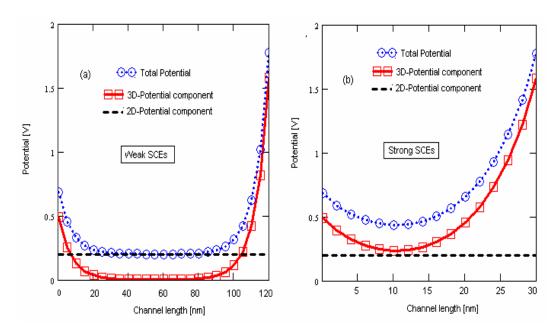

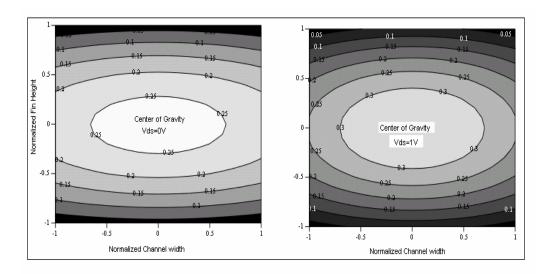

| Fig. 2C-2 FinFET: 3-D potential distribution along channel length.                     | 77  |

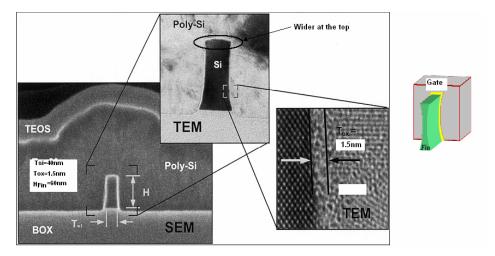

| Fig. 2C-3 FinFET: SEM, and TEM image                                                   | 80  |

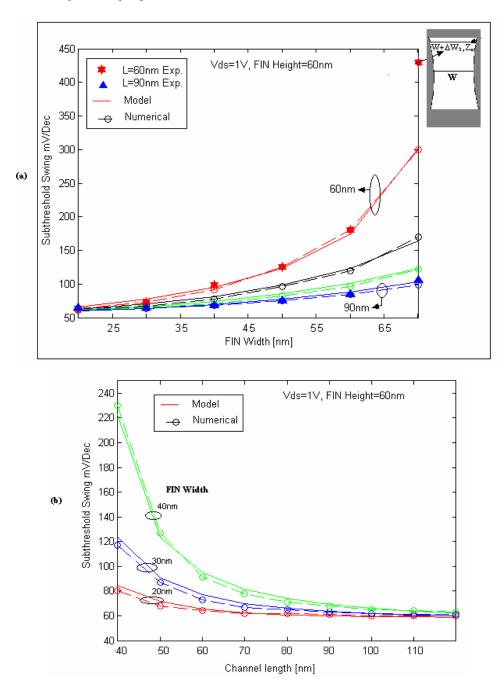

| Fig. 2C-4 FinFET: Subthreshold swing at low drain-source voltage                       | 81  |

| Fig. 2C-5 FinFET: Subthreshold swing at high drain-source voltage                      | 82  |

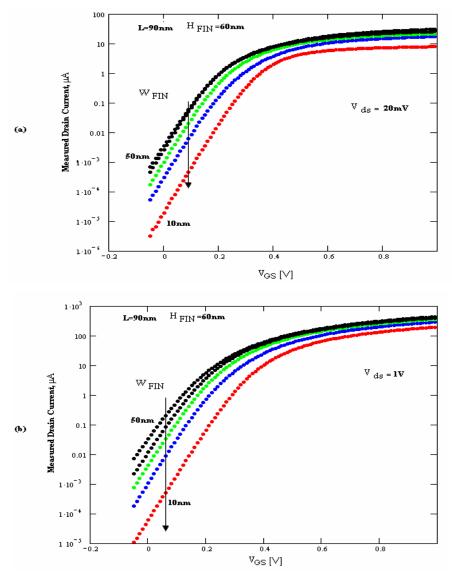

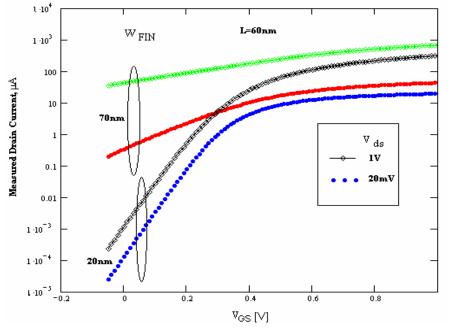

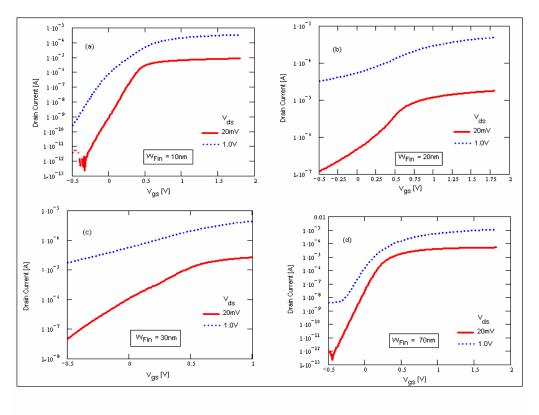

| Fig. 2C-6 FinFET: Measured drain current.                                              | 84  |

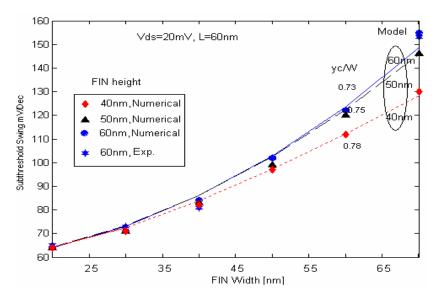

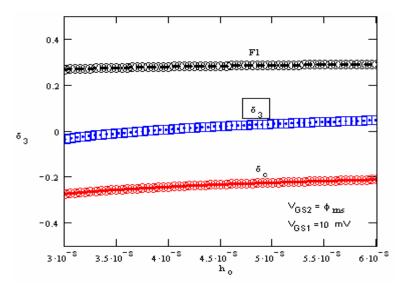

| Fig. 2C-7 FinFET: Subthreshold swing versus Fin height.                                | 85  |

| Fig. 2C-8 FinFET: Measured drain current in Logarithmic-scale                          | 85  |

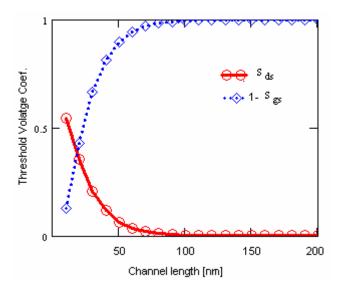

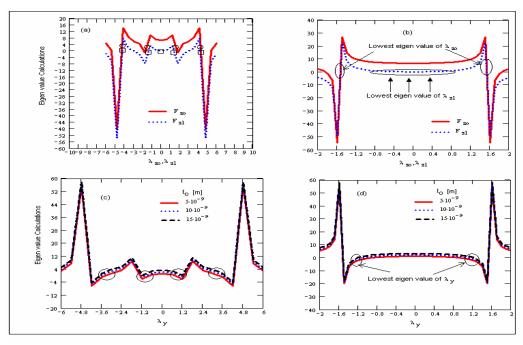

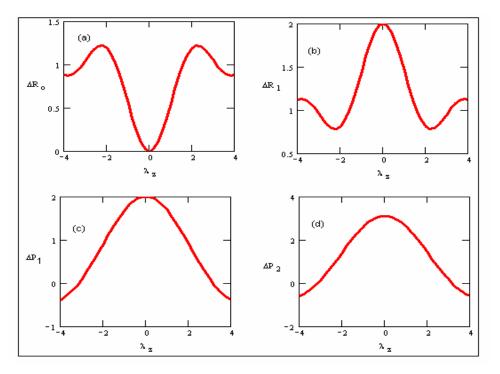

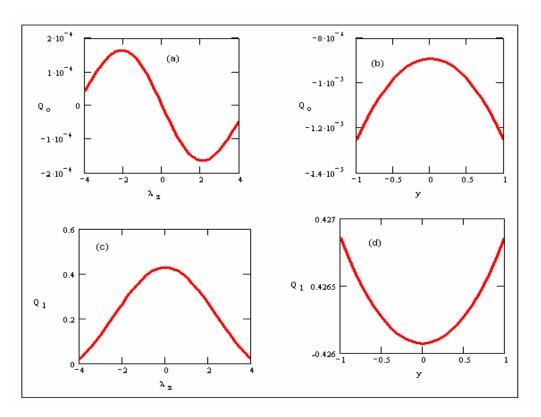

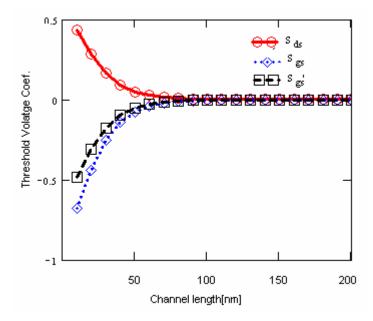

| Fig. 2C-9 FinFET: Threshold Voltage coefficients calculations for long channel devices | 88  |

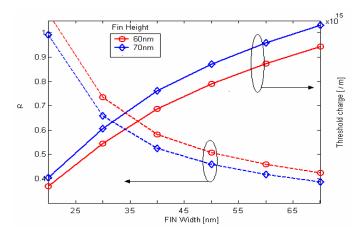

| Fig. 2C- 10 FinFET: Extracted threshold charge value                                   | 89  |

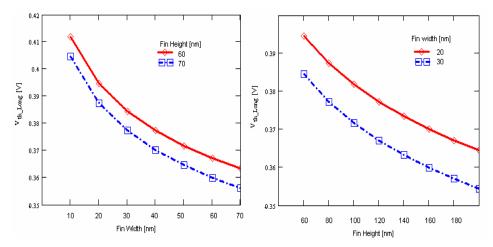

| Fig. 2C- 11 FinFET: Long channel threshold voltage                                     | 89  |

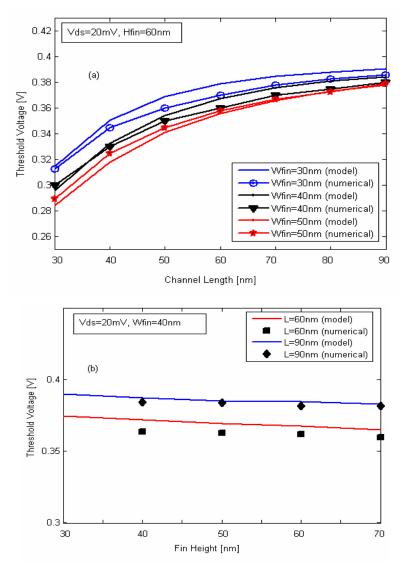

| Fig. 2C-12 FinFET: Threshold voltage for short channel devices                         | 90  |

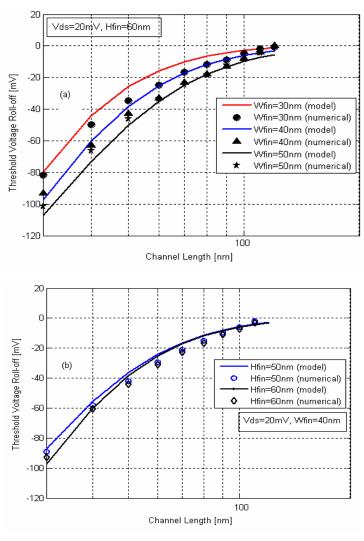

| Fig. 2C- 13 FinFET: Threshold voltage roll-off                                         | 91  |

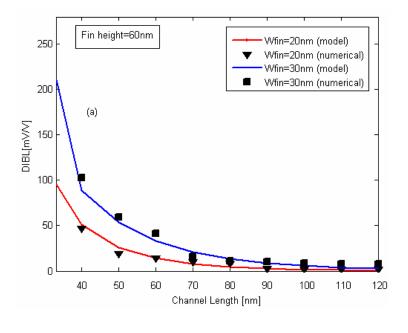

| Fig. 2C-14 FinFET: DIBL vs. channel length for different                               | 92  |

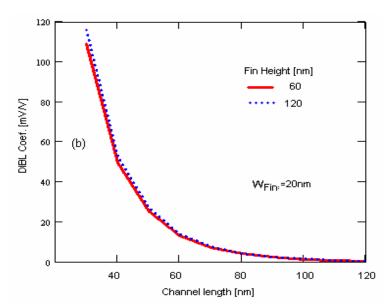

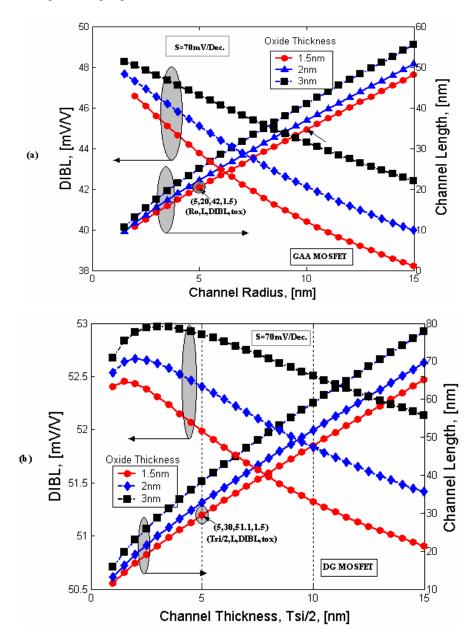

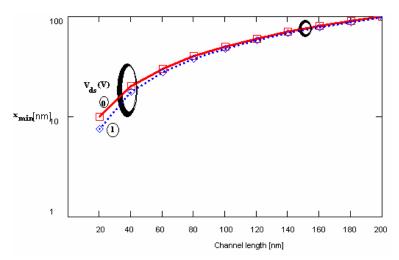

| Fig. 2D- 1 Channel length vs. oxide thickness for a) GAA MOSFET, and b) DG MOSFET.     | 95  |

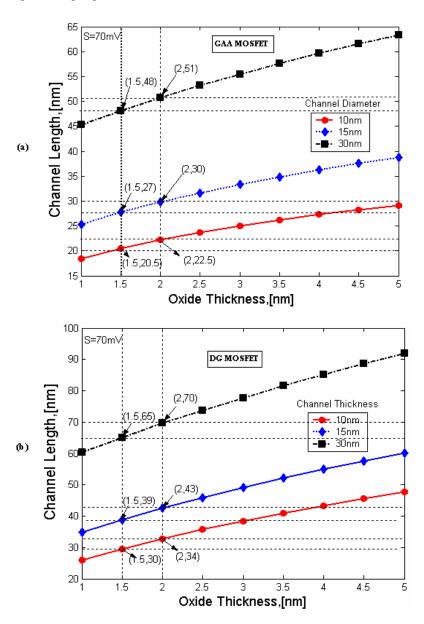

| Fig. 2D- 2 DIBL and channel length vs. channel radius/thickness                        | 96  |

| Fig. 3A-1 GAA MOSFET: Cross section                                                    | 101 |

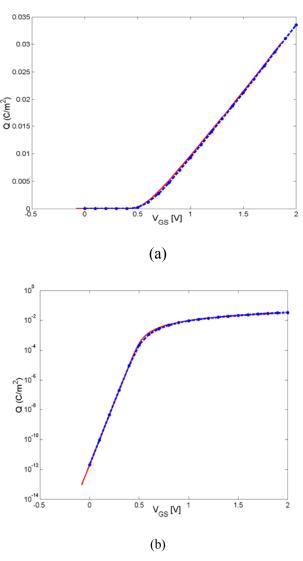

| Fig. 3A-2 GAA MOSFET: Channel charge density per unit area                             | 106 |

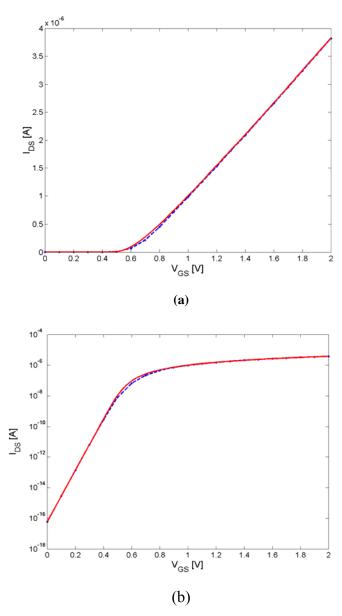

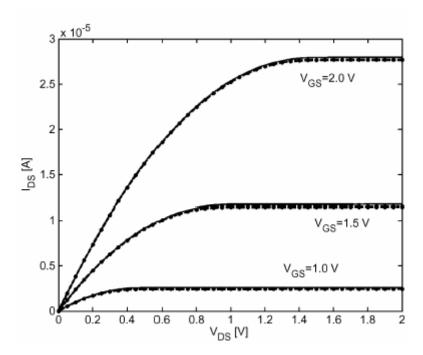

| Fig. 3A-3 GAA MOSFET: Transfer characteristic.                                         | 107 |

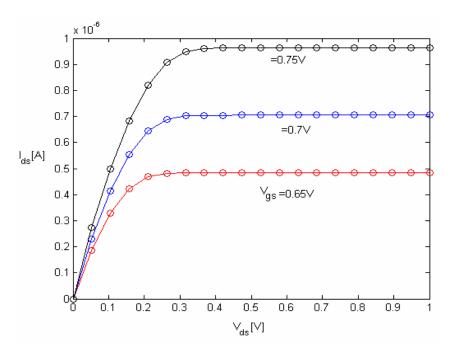

| Fig. 3A-4 GAA MOSFET: Output characteristics.                                          | 108 |

| Fig. 3A-4 FinFET: 3D potential components vs. channel length                           | 115 |

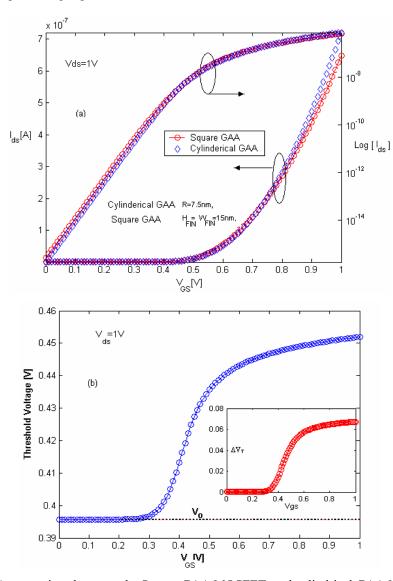

| Fig. 3A-5 Comparison between the Square GAA MOSFET, and cylindrical GAA MOSFET         | 116 |

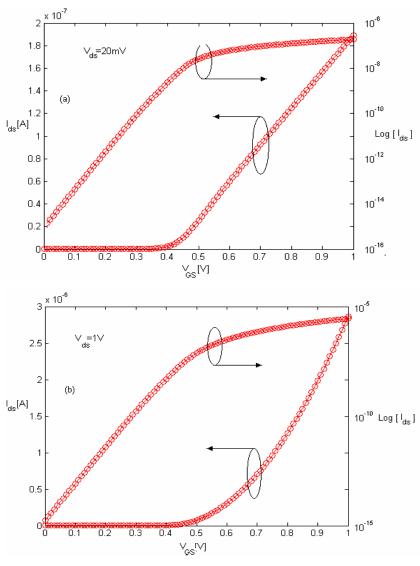

| Fig. 3A-6 FinFET: Transfer characteristic in linear and logarithmic scale              | 117 |

| Fig. 3A-7 FinFET: Output characteristics.                                              | 118 |

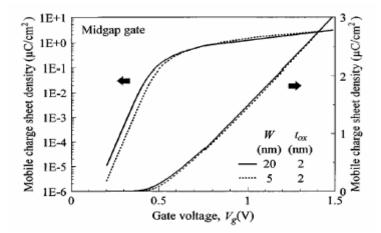

| Fig. 3A-8 DG MOSFET: Sheet density of mobile charge.                                   | 119 |

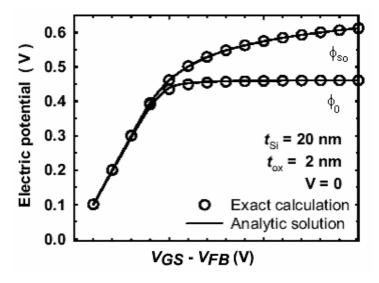

| Fig. 3A-10 DG MOSFET: Potential at the channel surface and channel center              | 119 |

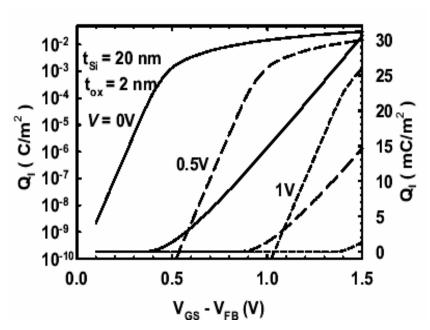

| Fig. 3A-11 DG MOSFET: Carrier charge per unit area induced in the channel              | 120 |

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING OF MULIPLE GATE MOS DEVICES. Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

| 5 / 2.21 1. 2011 2007                                                                             | 8   |

|---------------------------------------------------------------------------------------------------|-----|

| SCEs in undoped multiple gate MOS                                                                 |     |

| Fig. 3A-12 DG MOSFET: Output characteristics.                                                     | 120 |

|                                                                                                   |     |

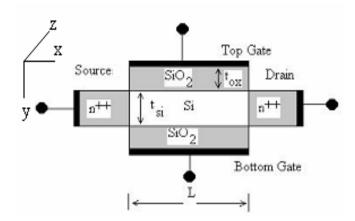

| Fig. 3B-1 Cross section of the symmetrical DG-MOSFET considered in this section                   | 125 |

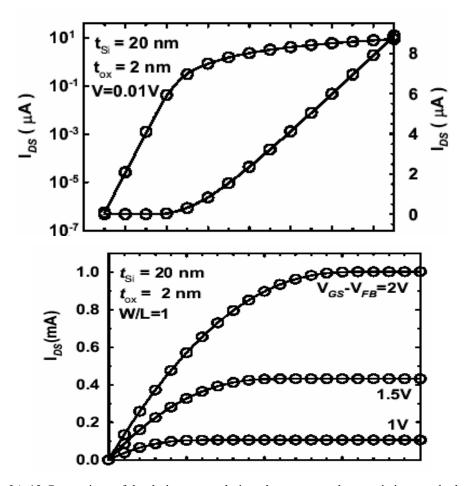

| Fig. 3B-2 a) Transfer characteristic of a quantum well DG-MOSFET                                  | 127 |

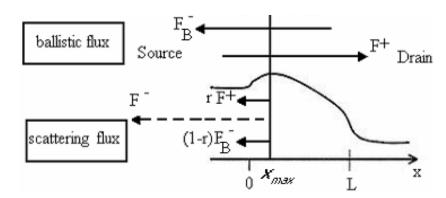

| $Fig.~3B-3~Simple~one~flux~representation~of~channel~transport~in~nanoscale~MOSFETs.~\dots \\$    | 131 |

| Fig. 3B-4 DG MOSFET: Quasi ballistic current                                                      | 133 |

| Fig. 3B-5 DG MOSFET: Carrier velocity.                                                            | 134 |

| $Fig.\ 3B-6\ DG\ MOSFET: Channel\ conductance\ for\ scattering\ model,\ and\ ballistic\ model\ .$ | 135 |

| Fig. 3B-7. DG MOSFET: Ballistic current                                                           | 136 |

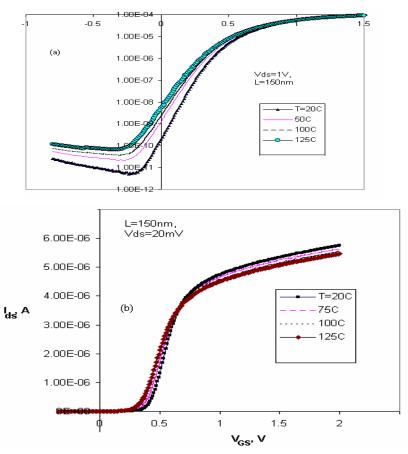

| Fig. 3B-8 FinFET: Measured drain current at different temperature values                          | 139 |

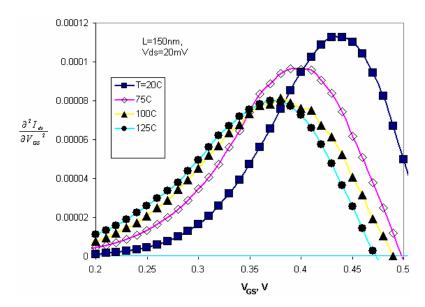

| Fig. 3B-9 FinFET: measured transconducatnce curve at different temperature values                 | 140 |

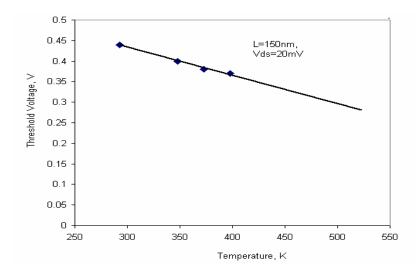

| Fig. 3B-10 FinFET: Extracted threshold voltage vs the temperature                                 | 140 |

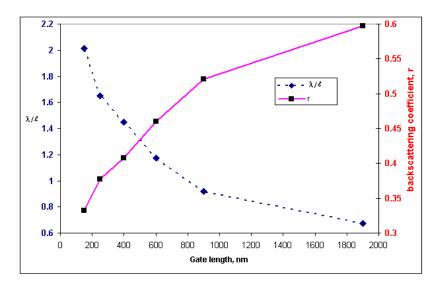

| Fig. 3B-11FinFET: Extracted backscattering coefficient vs. channel lengths                        | 141 |

### LIST OF PUBLICATIONS

### International Journals

- 1- **Hamdy Abd-Elhamid**, Jaume Roig, Valeria Kilchytska, Denis Flandre, Benjamin Iñiguez " A 3-D Analytical Physically-Based Model for SCEs in Undoped FinFETs," IEEE TRANSACTIONS ON ELECTRON DEVICES, submitted

- 2- Hamdy Abd-Elhamid, Jaume Roig, , Valeria Kilchytska, Denis Flandre, Benjamin Iñiguez " A 3-D Analytical Physically-Based Model for the Subthreshold Swing in Undoped FinFETs", IEEE TRANSACTIONS ON ELECTRON DEVICES, submitted

- 3- Hamdy Abd-Elhamid, Benjamin Iñiguez, and Jaume Roig "Two-Dimensional Analytical Threshold Voltage and Subthreshold Swing Models of Undoped Symmetric Double Gate MOSFETs", IEEE TRANSACTIONS ON ELECTRON DEVICES, inpress,m April 2007

- 4- **Hamdy Abd-Elhamid**, Benjamin Iñiguez, and Jaume RoigAnalytical predictive modeling for the study of the scalability limits of multiple gate MOSFETs", Solid-State Electronics, Vol. 51, Issue 3, March 2007, Pages 414-422.

- 5- Hamdy Abd-Elhamid, Benjamin Iñiguez, and Jaume Roig, "Analytical Model of the Threshold Voltage and Subthreshold Swing of Undoped Cylindrical Gate All Around Based MOSFETs", IEEE TRANSACTIONS ON ELECTRON DEVICES, Vol. 54, No.3, March 2007

- 6- Hamdy Abd-Elhamid, Benjamin Iñiguez, David Jiménez, Jaume Roig, Josep Pallarès, and Lluís F. Marsal, "Two-Dimensional Analytical Threshold Voltage Roll-Off and Subthreshold Swing Models For Undoped Cylindrical

Gate All Around MOSFET," Solid-State Electronics, vol. 50, no. 5, pp. 805-812, May 2006..

- 7- Benjamin Iñíguez, David Jiménez, Jaume Roig, <u>Hamdy Abd Elhamid</u>, Lluís F. Marsal, and Josep Pallarès "EXPLICIT CONTINUOUS MODEL FOR LONG CHANNEL UNDOPED SURROUNDING GATE MOSFETS", IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 52, NO. 8, AUGUST 2005

- 8- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, David Jiménez, Josep Pallarès, and Lluís F. Marsal "A simple model of the nanoscale double gate MOSFET based on the flux method" physica status solidi (c) Volume 2, Issue 8, Date: May 2005, Pages: 3086-3089

#### •International Conferences

- 9-(Invited) <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, and Jaume Roig "3-D Analytical Models for the Short-Channel Effect Parameters in Undoped FinFET Devices", Workshop on compact modelling, WCM, May 20-24, 2007 <u>Santa Clara Convention Center</u>, California, U.S.A.

- 10- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, and Jaume Roig "A 2-D Short Channel Effects Model For Undoped Double Gate MOSFET, Euro-SOI, Leuven, Belgium. 17-19 January, 2007

- 11- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, and Jaume Roig" NATO International Advanced Research Workshop "Nanoscaled Semiconductor-on-Insulator Structures and Devices" 15-19 October 2006, Sudak, Crimea, Ukraine

- 12- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, and Jaume Roig, MOS Modeling and Parameter Extraction Working Group MOS-AK/ESSDERC/ESSCIRC

Workshop Compact Modeling for Emerging Technologies, September 2006 Montreux Convention and Exhibition Center "scalability limits of multiple gate MOS devices"

- 13- **Hamdy Abd-Elhamid**, Benjamin Iñiguez, David Jiménez, Jaume Roig, Josep Pallarès, and Lluís F. Marsal "*Threshold voltage, and subthreshold swing for GAA MOSFET*", Euro-SOI, Grenoble, France. 19-21 March, 2006

- 14- Benjamin Iñiguez, <u>Hamdy Abd-Elhamid</u>, "Noise in SOI MOSFETs and Gate-All- Around Transistors" 18th International Conference on Noise and Fluctuations-ICNF 2005, Salamanca, Spain, 19-23 Sept. 2005.

- 15- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, David Jiménez, Josep Pallarès, and Lluís F. "Compact Modelling for Surrounding Gate MOSFETs" International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES 2005), Krakow (Poland), June 2005.

- 16- (Invited) Benjamin Iñiguez, <u>Hamdy Abd-Elhamid</u>, David Jiménez, "Compact Model of Multiple-gate SOI MOSFETs" ES 2005 NSTI Nanotechnology Conference and Trade Show Nanotech, Workshop on compact modelling, WCM, 2005 May 8-12, 2005 Anaheim Marriott & Convention Center Anaheim, California, U.S.A.

- 17- **Hamdy Abd-Elhamid**, Benjamin Iñiguez, David Jiménez, Josep Pallarès, and Lluís F. "*Quasi Ballistic Model of double gate MOSFET*", First Workshop of the Thematic Network on Silicon on Insulator technology, devices and circuits Granada, SPAIN. 19-21 January, 2005

- 18- <u>Hamdy Abd-Elhamid</u>, Benjamin Iñiguez, David Jiménez, Josep Pallarès, and Lluís F. "*Double Gate MOSFET Compact Model Including Scattering*" Conference on Electron Devices (CDE), Tarragona, Spain, 02-05 Feb., 2005

12

SCEs in undoped multiple gate MOS

### **ACKNOWLEDGMENTS**

The completion of this thesis would not have been possible without the assistance and support of many people. First and foremost, I would like to express my sincerest gratitude to my advisor and mentor, Professor Benjamin Iniguez for his guidance and support throughout my years at URV, DEEEA. In ways more than one, he has made me realize my fullest potential, and encouraged me to attain the highest level of professionalism. I would especially like to thank him for giving me the freedom to pursue my research interests. He always provided timely and warm encouragement and support in difficult times. He gave me every

Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

opportunity to advertise my work at important conferences. I especially thank him for his prompt reading and careful critique of my thesis.

I would especially like to thank Dr. Jaume of for developing me by the whole simulation results through the thesis.

My most rewarding experience was the summer I spent at Microelectronics Lab., UCL, Belgium. I would especially like to thank Prof. Denis Flandre, and Dr. Valeria for giving me the opportunity to characterizing and implementing the FinFET model.

I would like to thank Professor Hall Steve in particular, for allowing me to participate in his research group at University of Liverpool, England for two months.

I would like to thank Professor Tor Feljidy for the many discussions we had about my research, for the numerous suggestions and feedback, for his detailed comments on this thesis.

I would like to thank Professor Jamal el din of McMaster University for his fruitful and insightful discussions on SCEs model of GAA MOSFETs.

I would also like to thank Dr. David of UBC for many great discussions, especially for the ballistic models of quantum wire and quantum well.

Special thanks go to Professor Joseph, and Luis Marsal for their advice and encouragement on matters relating to academic and non-academic issues.

My sincere thanks and acknowledgements are due to my wife, my son, "Ahmed", my daughter, "Hana", my parents and my brothers: Dr. Hamada, and Eng. Arfat. I would like to give thanks to my friends Michael, Elizabith, and Lucas for their moral support. The support of the staff from the Department of Electrical and Electronics Engineering, URV is also greatly appreciated

## **CHAPTER ONE**

## Multiple Gate MOS Devices Structures and Performances

### 1-A Introduction

Thin film MOSFETs are very attractive for sub-100 nm CMOS applications because of their steep subthreshold slope and a low body effect coefficient. SOI

ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

15

microprocessors with a 22% speed improvement over bulk have been reported recently [1]. Fully depleted MOSFETs with a gate length of 50 nm and a switching speed less than a picosecond [2] have been reported. To minimize short channel effects and to maintain full depletion if the doping concentration in the channel region is increased, the silicon film thickness must be scaled down with gate length. While devices made in films thicker than 20 nm have excellent mobility and current drive characteristics [2], significant mobility degradation is observed in devices made using a silicon film thickness less than 10 nm [3]. If a metal gate is used instead of N polysilicon the doping concentration in the film can be reduced, which allows for fully depleted operation in thicker silicon films. This decrease of doping concentration, however, degrades the short channel characteristics and subthreshold slope through an increase of penetration of the drain electric field lines in the channel region [4], [5]. To prevent the electric field lines originating at the drain from terminating under the channel region, special multiple-gate structure devices have been reported. Such multiple-gate devices include double-gate and triple-gate structures such as the quantum wire [6], the FinFET [7] and II-channel SOI MOSFET [8], and quadruple-gate devices such as the gate all-around (GAA) device [9], the DELTA transistor [10], Omega MOSFETs [11], and Pi-gate SOI MOSFETs [12]. It is well known that the double-gate (top and bottom gate) silicon-on-insulator (SOI) MOSFET and the gate-all-around device are the most suitable device structures for suppressing short-channel effects such as DIBL and subthreshold slope degradation [9], [12-15]. Unfortunately the process proposed to fabricate such devices is incompatible with standard CMOS or even SOI CMOS manufacturing. The Pi-gate SOI

MOSFET structure was first introduced in [12].

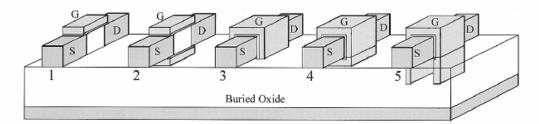

Different multiple gate structures have been proposed: double-gate MOSFET, FinFET, surrounding-gate MOSFET. Fig. 1.1 shows the existing gate configuration for thin-film SOI MOSFETs: 1) single gate; 2) double gate; 3) triple gate; 4) quadruple gate (or GAA). The new proposed gate structure is a triple-gate MOSFET where the gate electrode extends to some depth in the buried oxide on both sides of the device. The gate is in the shape of the uppercase Greek (Pi) letter. The gate extension in the buried oxide shields the back of the channel region from the electric field lines from the drain almost as perfectly as an actual back gate would.

Fig. 1.1 the existing gate configuration for thin-film SOI MOSFETs.

Their main advantage is an excellent electrostatic control of the channel, which reduces the short channel effects. On the other hand, since the conduction takes place in a volume instead of just one surface, these devices present higher mobility than conventional bulk MOSFETs because there is less scattering; their operation can even be near the ballistic limit for very short channel devices.

In multiple gate devices, the use of a very thin film allows to downscale the devices without the need of using high channel doping densities and gradients. In fact, undoped films can be used: the full depletion of the thin film prevents punch-through from happening. Besides, the absence of dopant atoms in the channel increases the mobility by suppressing impurity scattering. On the other hand,

unwanted dispersion of the characteristics is avoided; this dispersion results from the random microscopic fluctuations in ultra-small devices.

Multiple gate nanoscale devices have many advantages in circuit performance. A very high packaging density is possible because of the small size of these devices, caused by the short channel and the thin film. Because of the higher mobility, transconductance can be higher, which gives more current gain and allows a higher operating frequency. Therefore, multiple gate nanoscale devices have a big potential for RF and microwave applications. The analog performance is also very good. Voltage gain is much higher than in conventional bulk MOSFETs, and especially in moderate inversion: the reduction of short channel effects leads to a higher Early voltage (I-V<sub>ds</sub> characteristics are flatter in saturation), and on the other hand the g<sub>m</sub>/I<sub>d</sub> characteristics have higher values than in conventional MOSFETs. Regarding digital applications, the small subthreshold swing of multiple gate devices keeps a high ratio between on current and off current even for devices with channel lengths of the order of nm.

## 1-B Fabricating challenges

Anyway, multiple gate structures present some difficulties in fabrication. In double-gate MOSFETs, the alignment of the top and the bottom gates to each other and to source/drain doping is critical for the device performance; misalignment can cause an additional overlap capacitance between gate and source or drain, as well as an additional series resistance.

Because of its intrinsic self-aligned process, FinFET devices seem to be the first multiple-gate devices that will appear in the market. Devices with channel lengths

of 18 nm have been successfully fabricated. FinFETs work as double-gate devices when the width of the silicon fin is much smaller that its height.

In triple-gate structures an inversion channel forms not only at the planar sides of the device, but also in the corners where two such sides meet. It has been shown that premature inversion can be reached at the corners, which degrades the subthreshold characteristics and creates an undesirable kink in the transconductance versus gate

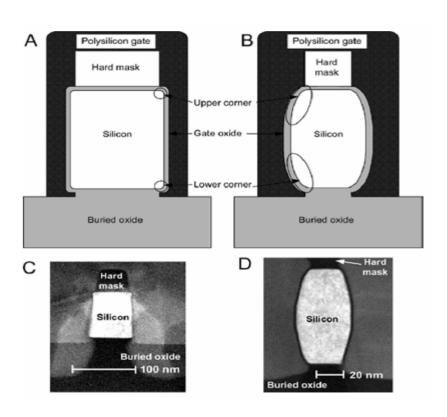

voltage curve [16]. The FinFET is a double-gate device, since the top of the silicon fin is covered by a hard mask. However, due to processing conditions a slight lateral over-etch of the hard mask can occur. As a result, the top corners of the fins can be exposed to gate oxidation and become the weak point in the gate oxide as well as the host of corner inversion. Similarly, a slight over-etch of the buried oxide below the fin will expose the

bottom corners, in which channels can form as well. Premature corner inversion is an undesirable effect. It can be avoided by reducing channel doping or by rounding the corners of the fins [16]. In [17], hydrogen anneal prior to gate oxidation was proposed to round the corners and thereby reduce leakage currents, as shown in Fig. 1.2. Table 1.1 indicate the improvements taken place in DIBL, threshold voltage, and subthreshold slope due to smoothening the corners.

Fig. 1.2 Schematic and TEM cross section of a FinFET without (A, C) and with (B, D) hydrogen annealing [17].

|          | V <sub>TH</sub> (mV)  | V <sub>TH</sub> (mV) | DIBL | S                                 | S                                |

|----------|-----------------------|----------------------|------|-----------------------------------|----------------------------------|

|          | V <sub>D</sub> =0.05V | V <sub>D</sub> =1.2V | (mV) | (mV/dec)<br>V <sub>D</sub> =0.05V | (mV/dec)<br>V <sub>D</sub> =1.2V |

| Device A | 185                   | 50                   | 135  | 87                                | 117                              |

| Device B | 250                   | 115                  | 135  | 81                                | 91                               |

| Device C | 0.05                  | 015                  | 65   | 66                                | 70                               |

Table 1.1 Threshold voltage, DIBL and subthreshold slope in the n-FinFETs, [17]

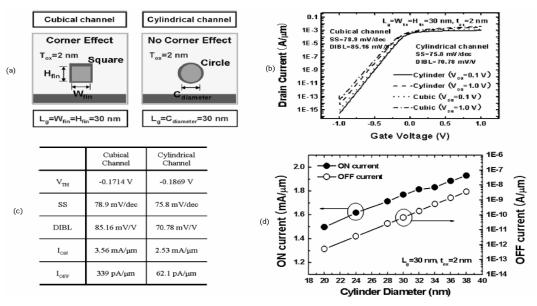

Through the previous simulation results for the GAA MOSFETs, the design optimization for proper suppression of short-channel effects yields the following device parameters[18-19]:

the gate length, the fin width, and the fin height were all 30 nm, and the gate-oxide thickness was 2 nm. As a result, the performance of GAA MOSFETs had been improved with a cubical channel.

To study short-channel behavior of corner-effect-free GAA MOSFETs, the simulation for ideal cylindrical-channel MOSFETs was performed as shown in Fig. 1.3. In the case of ideal cylindrical-channel MOSFETs, the main device parameter is the cylinder diameter. The cylinder diameter was set to be 30 nm, which was the same as the fin width in the cubical-channel MOSFETs. Fig. 1.3b shows the transfer characteristics of the cubical-channel MOSFETs and the ideal cylindrical-channel MOSFETs. The results of the simulation were summarized in Table 1.2. In cylindrical-channel MOSFETs, the OFF current was remarkably reduced because the channels were equally affected by the gate electric field while the electric field was out of balance inside the channel in the cubical-channel MOSFETs. SS as well as DIBL in the ideal cylindrical-channel MOSFETs were smaller than those in cubical-channel MOSFETs with corner effects.

Fig. 1.3. a) Cross-sectional views of the optimized cubical-channel MOSFETs and ideal cylindrical-channel MOSFETs without corner effects. In the case of ideal cylindrical-channel MOSFETs, the main device parameter is the cylinder diameter. The cylinder diameter was set to be 30 nm, which is the same as the fin width in the optimized cubical-channel MOSFETs. b) Transfer characteristics of cubical-channel GAA MOSFETs and ideal cylindrical-channel MOSFETs. c) The SS as well as DIBL in the ideal cylindricalchannel MOSFETs are smaller than that in cubical-channel MOSFETs. d) In cylindrical-channel MOSFETs, the OFF current is remarkably reduced[18].

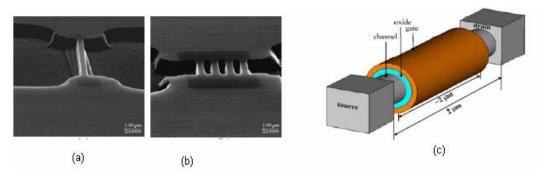

Fig.1.4 TEM view of (a) a single and (b) four channel wrap-around-gate MOSFET, (c) A cross-sectional view of the n-channel nanowire MOSFET [19]

Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

The cylindrical surrounding gate MOSFET, in Fig. 1.4, allows a more drastic

reduction of the short-channel effects. In this device, a gate electrode surrounds

the pillar silicon island, which can be formed by conventional trench process

techniques.

For designers, one of the main challenges is to have appropriate threshold voltage

values for integrated circuits; if the device films are not doped, threshold voltage

control will rely on successfully using metal gates and engineering the work-

function.

Another challenge for device engineers is to reduce parasitics, such as the series

resistance and the fringing capacitance. It has been proposed to reduce the series

resistance by using metal sources/drains, since the resistivity of metal is two

orders of magnitude smaller than that of heavily doped silicon.

1-C Modeling challenges

The multi-gate devices that control the channel from multiple sides and very thin

body devices are new to circuit and system designers. These devices need to be

modeled to understand and predict the functionality of the circuits. Compact

device models are used in circuit design. New compact models that accurately

model these novel devices, and are computationally efficient, are in development.

There are new physical effects that now need to be incorporated into these device

models.

The use of multiple gate devices in circuit design is critically dependent on the

availability of accurate models for these devices, valid for DC, AC, transient and

noise analysis. Using appropriate models, circuit simulation allows to design

circuits with devices of adequate dimensions. Circuit simulation requires accurate models of the current and the terminal charges (from which capacitances are obtained) of the devices. These models should be based on expressions with a sufficiently high order of continuity.

Lack of continuity between the different operating regimes leads to convergence problems in circuit simulation. In conventional MOSFETs, there have been a trend to move from piecewise models (with continuity problems) to unified models with an infinite order of continuity. Smoothening functions are often used to assure the continuity between different operating regimes. For the same reasons, multiple-gate MOSFETs will need unified highly continuous models.

For proper modeling of nanoscale MOSFET for VLSI circuit simulation, accurate and physics-based compact models are required. The modeling principles for these devices are somewhat different from conventional bulk MOSFETs, since volume conduction should be considered. For undoped double-gate and surrounding-gate MOSFETs the depletion charge does not need to be included in Poisson's equation, which allows exact analytic solutions of the potential without the charge-sheet approximation, valid for all operating regimes. The gradual channel approximation (which assumes that the quasi Fermi potential stays constant along the direction perpendicular to the channel) is used. A compact expression of the channel current is obtained assuming that transport is based on drift-diffusion.

Accurate models for undoped double-gate [20-23] and surrounding-gate MOSFETs [20],[24-25] have been recently developed using the above principles, showing good agreement with three dimensional numerical simulations. These models assume that the electrostatic control of the channel is so good that shortchannel effects can be neglected. The inclusion of short-channel effects in

ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

multiple gate MOSFET models, using physical equations and without decreasing the order of continuity of the devices, is still a modeling challenge.

For devices with channel lengths shorter than 50 nm, the drift-diffusion mechanism may not be the dominant transport mechanism. Ballistic or quasiballistic transport may occur. Adequate models for nanoscale devices must consider the balllistic or quasi-ballistic regime[26-44]. So far, several models have been developed for multiple gate MOSFETs in the ballistic regime, in particular double-gate and surrounding gate MOSFETs. In these models it has been assumed that the electrostatic control of the channel is strong enough, so that short channel effects can be neglected. Next step in ballistic regime modeling will be the consideration of the short-channel effects.

Anyway, the main modeling challenge regarding transport is the development of a transport model formulation that makes the current tend to the expression in the ballistic regime for nanometer channel lengths and to the expression in the driftdiffusion limit for longer channel lengths.

On the other hand, for films smaller than 10 nm, quantum confinement in the film may not be negligible. The subband contributions should be considered in the drain current equation. The quantum effects affect the distribution of charge in the film and as a consequence, the threshold voltage (increase of the threshold voltage in an n-channel device). Some recent models which consider the band structure of silicon have been recently presented. At very low temperatures, quantum confinement of the charge becomes more important, and this affects the shape of the transconductance characteristics [25], see Fig. 1.5

Fig. 1.5. Bottom of subbands and transconductance characteristics of a cylindrical surrounding gate MOSFET with a 65 nm diameter Si film Dotted line: measurements [25] Solid line: model.  $V_{ds} = 2 \text{ mV}.$

A succession of peaks and valleys are observed, which correspond, respectively, when the bottom of the subbands cross the quasi-Fermi energy levels at the source and drain. The location of peaks and valleys has been accurately predicted. These models should be still completed with the inclusion of short channel effects.

In the other hand, most of the work done to study the SCEs for the multiple gate MOS devices has neglected the mobile charge density term when solving electrostatic potential. However, it is important in the near threshold regime. For the Double Gate MOSFETs, Linag et. al [45], developed a 2D potential model neglecting the effect of mobile charge term. However they did not introduce any explicit threshold voltage model nor a subthreshold swing model (see Fig. 1.6). Chen et. al [46], have considered the effect of the conduction path to calculate the SCEs for the DG MOSFETs, but the model is not able to calculate the DIBL effect. [47-48] have studied the SCEs for the doped GAA MOS devices, but neglecting the mobile charge. Pie et. al [49], introduced subthreshold swing model

and the threshold voltage roll-off in the FinFET but for high doped channel devices. The model does not provide a good fitting with the numerical simulation, as shown in Fig. 1.7.

Fig. 1.6. Analytical solutions of the subthreshold slopes for symmetric and asymmetric DG MOSFETs (solid curves) compared with 2-D numerical simulation results (dashed curves)[45]

Fig. 1.7 Comparison of subthreshold swing from numerical and analytical solutions for both linear (V = 0.1 V) and saturation (V = 1.5 V) regions. [49]

Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

In this thesis we study the three undoped multiple gate MOS devices, i.e., Double Gate MOSFETs, Cylindrical Gate All Around MOSFET, and Tri-Gate FETs. In this work we have modeled the SCEs for the whole three devices considering the mobile charge density. The SCEs effects that have been studied through this thesis are: Threshold voltage, Subthreshold swing, Threshold voltage roll-off, and DIBL effect. The SCEs have been verified with numerical simulation results from DESSIS, and the allowable experimental results that were done in the Microelectronics Laboratory (DICE) in the Microelectronics Laboratory, Université catholique de Louvain, Belgium.

The thesis organized as: Chapter (2) modeling of SCEs for the undoped three devices, Chapter (3) studies the current transport (Drift-Diffusion, Ballistic, and Quasi Ballistic) for the three devices. Finally chapter (4) summarizes the work done and the future points that needs to studied.

#### 27

## **CHAPTER TWO**

## **Short Channel Effects (SCEs) in Undoped Multiple Gate MOS Devices**

#### In this Chapter

This chapter is aimed to study the physics insight of the Multiple Gate MOS Devices; Gate All Around MOSFETs, Double Gate MOSFETs, and FinFETs.

The chapter is divided into four parts based on the device structures,

Section 2A) is divided into two main Parts, in both parts an analytical, physicallybased, models for the threshold voltage and the subthreshold swing of undoped cylindrical Gate All Around (GAA) MOSFETs have been derived based on an analytical solution of the two-dimensional (2-D) Poisson equation (in cylindrical coordinates) with the mobile charge term included. In (2A-1), The model was not able to calculate the DIBL effects, it was only valid for low drain-source voltages, as it was done before by Chen., et. al[46] for the Double Gate MOSFET. In (2A-2), the model has been modified by solving the 2-D Poisson equation taking into account the variations of drain-source voltage, therefore the model was finally able to calculate the all SCEs including DIBL effects.

In section 2B) we have studied the Short Channel Effects in the Undoped Double Gate MOS Devices, by introducing new models for subthreshold swing, Threshold Volatge, Roll-Off and DIBL effects.

Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

28

SCEs in undoped multiple gate MOS

Section 2C) A 3-D analytical model for the undoped FinFET devices, has been studied. We introduced for the first time new models for subthreshold swing, threshold voltage, DIBL, and roll-off.

Section 2D) A comparison have been done between the DG, and GAA MOSFET performances at low subthreshold swing value (S=70mV/Dec), and from this comparison we have predicted the device dimensions to verify this subthreshold swing value.

For the whole device structures, we have taken into account the mobile charge density when solving 2D Poisson equation (in DG MOS Devices), or 3-D Poisson equation (in GAA MOS Devices, and FinFET Devices).

We have verified the GAA, and DG MOS device models by comparison with the numerical simulation results. For the FinFET devices we have validated the subthreshold swing model with both numerical and expermintalas results done at the Microelectronics Laboratory, Université catholique de Louvain, Belgium. The rest of FinFET models have been verified by comparison with the numerical simulation results.

## (2-A) Part (I): Short Channel Effects (SCEs) In Undoped Cylindrical Gate All Around MOSFET

In this section

The Poisson equation in cylindrical coordinates for undoped cylindrical GAA MOSFETs at low drain-source voltage values has been solved, and from the electrostatic potential we have developed new models for threshold voltage, subthreshold swing, and threshold voltage roll-off [50-53].

#### 2A-1 Introduction

The Gate All Around (GAA) MOSFET is considered one the most promising devices for downscaling below 50nm[54-58]. By surrounding the channel completely (Fig. 2A-1a), the gate gains increased electrostatic control of the channel and short-channel effects can be drastically suppressed. Apart from the benefit of allowing a shorter a channel, the GAA MOSFETs can achieve a higher packing density due to their enhanced current drive compared to planar MOSFETs. The downscaling of device dimensions has been the primary factor leading to improvements in IC performance and cost, which contributes to the rapid growth of the semiconductor industry.

However, even in GAA MOSFET devices, Short Channel Effects (SCE), such as the threshold voltage roll-off, the DIBL and the subthreshold swing degradation, cannot be neglected for channel lengths below 100nm [59].

The threshold voltage roll-off is a consequence of the charge sharing effect and typically considered one of the main indications of the short channel effect ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

(GCE) A d : 4 (GCE : d 1d 1 11

(SCE). Another important SCE is the subthreshold swing degradation, which leads to a higher off-state current.

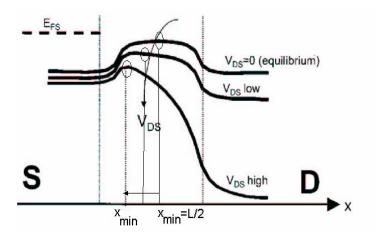

30

The DIBL (*drain-induced barrier lowering*) effect occurs when the barrier height for channel carriers at the edge of the source is reduced due to the influence of drain electric field, upon application of a high drain voltage. As the voltage drop between the source and drain increases, the depletion region under the drain can lower the potential barrier of the source-to-channel junction. If the barrier between the source and channel is decreased, electrons are more freely injected into the channel region. Therefore the threshold voltage is lowered and the gate has less control of the channel.

Compact and accurate models of the threshold voltage (including DIBL) and the subthreshold swing are needed in order to ease the use of these devices in nanoscale integrated circuits.

Most of the existing GAA MOSFET models are based on one-dimensional (1-D) analysis, and are suitable only for *long*-channel devices [58][63-64]. As consequence, they are unable to reproduce the roll-off as the channel length is reduced.

A two-dimensional analysis is necessary to derive threshold voltage and subthreshold swing models that properly account for the channel length dependence. A few 2-D models of the threshold voltage for doped [60-61] and undoped [62] GAA MOSFETs have been presented; however, all of them neglect the effect of the mobile charge density, which can be important in the near-threshold regime (in particular for undoped devices).

In this section, we present 2-D models for the threshold voltage (including the DIBL effect), and subthreshold swing of a cylindrical undoped GAA MOSFET

ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

including the effect of the mobile charge density. The dependences of channel length, thickness and drain-source voltage are accounted for.

An appropriate definition of the threshold voltage for these devices has been used. In bulk MOSFET, it is usually defined as the gate voltage at which the surface potential is equal to two times the Fermi level (band bending difference at the surface between the Fermi level, and the intrinsic level of silicon in the neutral region). Nevertheless, this definition is not adequate for DG and GAA MOSFETs (in particular for undoped devices), where there is inversion or accumulation in the whole film, and not only at the surface. In DG MOSFETs the threshold voltage has been instead defined as the gate voltage at which the minimum sheet density of carriers, Q<sub>inv</sub>, reaches a value Q<sub>TH</sub> which can be identified as the onset of the turn-on condition[46],[65]. We have applied the same definition to GAA MOSFETs.

We observed a quite good agreement with the results obtained from 3-D numerical simulations with DESSIS-ISE for different channel lengths/thickness and from low to high drain-source voltage values. The structure of the section is the following: subsection (2A-2) explains the derivation of the potential model from the solution of the 2D Poisson's equation. In subsection (2A-3), the derivation of the expression of the location of the minimum potential is explained. In subsection (2A-4), the derivation of the threshold voltage model, using the value of the minimum potential, is presented and its dependence with the silicon thickness, channel length and compared with 3D numerical simulation results. Subsection (2A-5), presents the model of subthreshold swing.

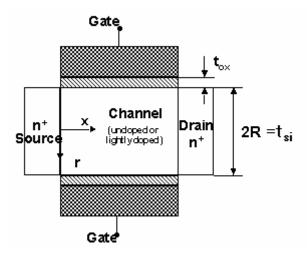

### 2A-2 Potential Model Derivation

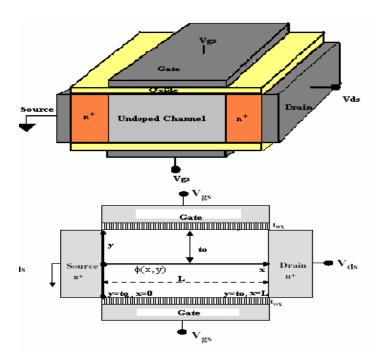

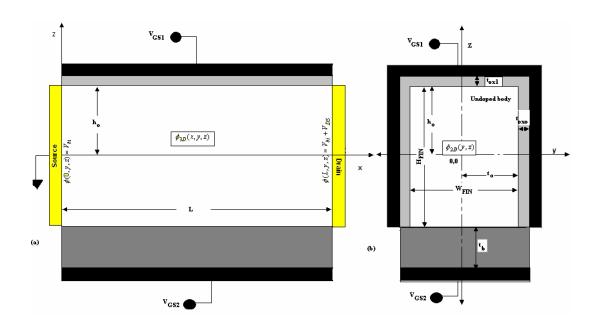

Fig. 2A-1 shows the cross section of the symmetrical GAA-MOSFET considered in this work. In order to illustrate the behaviour of the compact model we have assumed a GAA-MOSFET with Si-SiO<sub>2</sub> interface parallel to (100) plane. The channel is undoped ( $\cong 10^{16} \text{cm}^{-3}$ ), the n<sup>+</sup> source and drain are highly doped, and all calculations have been done at room temperature.

**Fig. 2A-1**. Cylindrical GAA-MOSFET considered in this work, a) 3-D device structure, and b) Cross section.

The channel electrostatics under threshold condition is governed by the Poisson equation with only the inversion charge term included:

$$\nabla^2 \phi(r, x) = \frac{q}{\varepsilon_{si}} n \tag{2A-1}$$

where  $\phi$  is the electrostatic potential referenced to the Fermi level in the source [66-67], the electron density is given as

$$n = n_i e^{(\phi - \phi_F)/V_T} \tag{2A-2}$$

where  $n_i$  is intrinsic electron density in silicon,  $V_T$  is the thermal voltage, and  $\phi_F$ is the non-equilibrium quasi- Fermi level referenced to the Fermi level in the source, satisfying the following boundary conditions:

$$\phi_F(0,r) = 0 \tag{2A-3}$$

$$\phi_F(L,r) = V_{DS}, \qquad (2A-4)$$

$V_{ds}$  being the drain voltage.

The boundary conditions for  $\phi$  are given as:

$$C_{ox}(V_{GS} - \phi_{ms} - \phi(x, \pm \frac{t_{si}}{2})) = \pm \varepsilon_{Si} \frac{\partial \phi(x, r)}{\partial r} \bigg|_{r = \pm \frac{t_{Si}}{2}}$$

(2A-5)

$$\phi(0,r) = V_{bi} \tag{2A-6}$$

$$\phi(L,r) = V_{bi} + V_{ds} \tag{2A-7}$$

where  $V_{GS}$  is the gate voltage,  $\phi_{ms}$  is the gate work function referenced to intrinsic silicon, and  $V_{bi}$  is the built-in voltage given as  $(V_T \cdot ln(N_{S/D}/ni), \sim 0.6V)$ , where  $N_{S/D}$ is the source/drain doping density. Equation (2A-5) arises from the continuity of the normal component of the displacement vector across interfaces. The sourceand drain-side boundary conditions (2A-6) and (2A-7) are idealized assuming negligible depletion regions inside source/drain, which is justified when the source and drain junctions are abrupt and source/drain are several orders of

magnitude more heavily doped than the channel as in undoped devices.

Determination of the potential  $\phi$  requires Eq.(2A-1) to be coupled with a transport equation (for example, the drift-diffusion equation[75]) for the quasi-Fermi level  $\phi_F$ . Numerical simulations shown that  $\phi_F$  is virtually constant in the channel depth direction and varies only in the channel length direction. While it incurs most of its change near the drain, it stays close to zero in the mid-channel and near-source regions, where the conduction-determining potential barrier (or virtual cathode) is located. Based on these observations,  $\phi_F(x,r)$  is approximated to first order as a 1-D  $\delta$ -function, i.e., is assumed to be zero everywhere except at the end of channel (x=L) where it reaches V<sub>ds</sub>. Such an approximation is implemented by modifying (2A-1) and (2A-7) as follows:

$$\frac{1}{r}\frac{\partial}{\partial r}r\frac{\partial}{\partial r}\phi(x,r) + \frac{\partial^{2}}{\partial x^{2}}\phi(x,r) = \frac{q}{\varepsilon_{si}}n_{i}e^{\phi(x,r)/V_{T}}$$

(2A-8)

$$\phi(L,r) = V_{bi}$$

(2A-9)

Although this 1-D  $\delta$ -function approximation of  $\phi_F$  makes subsequent solutions independent of  $V_{ds}$  and the final result not able of directly calculating drain induced barrier lowering (DIBL)[46], it is valid to calculate the threshold voltage at low  $V_{ds}$  values, and therefore, determine the threshold voltage roll-off. Therefore, the problem is formulated as to solve the 2-D Poisson Eq.(2A-8) for the potential with boundary conditions given in (2A-5), (2A-6), and (2A-9). That is,  $\phi(x,r)$  is to be written in the following form:

$$\phi(x,r) = \phi_1(x) + \phi_2(x,r)$$

(2A-10)

35

SCEs in undoped multiple gate MOS

where  $\phi_1(x)$  is the solution to 1-D Poisson equation:

$$\frac{d^2\phi_1(x)}{dx^2} = \frac{q}{\varepsilon_{Si}} n_i e^{\frac{\phi_1(x)}{V_T}}$$

(2A-11)

with boundary conditions:

$$\phi_1(0) = V_{bi} \tag{2A-12}$$

$$\phi_1(L) = V_{bi} \tag{2A-13}$$

And  $\phi_2(x, r)$  is the solution to residual 2-D equation,

$$\frac{1}{r}\frac{\partial}{\partial r}r\frac{\partial}{\partial r}\phi_2(x,r) + \frac{\partial^2}{\partial x^2}\phi_2(x,r) = \frac{q}{\varepsilon_{si}}n_i e^{\phi(x,r)/V_T}$$

(2A-14)

with boundary conditions:

$$C_{ox}\left[V_{GS} - \phi_{ms} - \phi_2(x, \pm \frac{t_{si}}{2}) - \phi_1(x)\right] = \pm \varepsilon_{Si} \frac{\partial \phi_2(x, r)}{\partial r}\bigg|_{r = \pm \frac{t_{Si}}{2}}$$

(2A-15)

$$\phi_2(0,r) = 0 \tag{2A-16}$$

$$\phi_2(L, r) = 0 \tag{2A-17}$$

where  $C_{ox}$  is an effective oxide capacitance (per unit area) for the cylindrical geometry, given by [67] as:

$$C_{ox} = \varepsilon_{ox} / \left( \frac{t_{Si}}{2} \log(1 + 2t_{ox} / t_{Si}) \right)$$

(2A-18)

The 1-D equation (2A-11) can be solved [76-78] as:

$$\phi_1(x) = \phi_{0m} + V_T \ln \left\{ \sec^2 \left[ B \left( \frac{x}{L} - \frac{1}{2} \right) \right] \right\}$$

(2A-19)

where:

$$\phi_{0m} = V_{bi} - 2V_T \ln \frac{2 + \frac{L}{\lambda_i} e^{\frac{V_{bi}}{2V_T}}}{\pi}$$

(2A-20)

and

$$B = \frac{\pi}{1 + 2\frac{L}{\lambda_i}e^{\frac{-V_{bi}}{2V_T}}}$$

(2A-21)

$\lambda_i$  being the intrinsic Debye length given as:

$$\lambda_i = \sqrt{2V_T \varepsilon_{Si} / q n_i} \tag{2A-22}$$

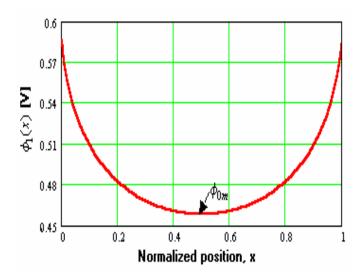

Fig.2A-2 shows the solution of 1-D Poisson equation in Eq.(2A-19), The minimum potential value,  $\phi_{0m}$ , takes place very close to the middle of the channel length.

Fig.2A-2 The potential along the channel (normalized) of 1-D Poisson solution, Eq.(2A-19). The channel length is 20nm.

The residual 2-D equation is solved by variable separation, which is a suitable method for solving both Laplace and Poisson equations (a solution guide was introduced in Appendix 2A-1):

$$\phi_2(x,r) = f_1(x) \cdot f_2(r) \tag{2A-23}$$

For  $0 \le r \le t_{Si}/2$  and  $0 \le x \le L$ ,  $f_1(x)$ , and  $f_2(r)$  are given as:

$$f_{1}(x) = \begin{cases} 4\sin(\gamma \cdot x) - 2\cos(\gamma \cdot x) \left[ \tan(\frac{\gamma}{2} \cdot x_{\min}) + \tan(\frac{\gamma}{2} (x - x_{\min})) - \frac{1}{2} \left( -x_{\min} \right) \right] - \frac{1}{2} \\ \tan(\frac{\gamma}{2} \cdot x_{\min}) \cdot \tan(\frac{\gamma}{2} (x - x_{\min})) \cdot \sin(\gamma \cdot x) \end{cases}$$

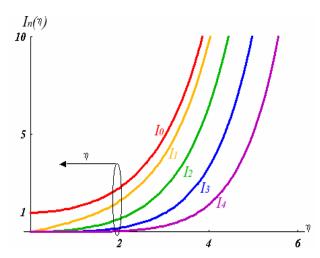

$$\left\{ \frac{V_{GS} - \phi_{ms} - \phi_{om}}{\frac{C_{Si}}{C_{ox}}} 2\eta \cdot I_{1}(\eta) + I_{0}(\eta) \right\} \cdot \frac{\sin(\beta)}{3} \cdot \left[ 1 - \ln(\eta/2) \right]$$

$$(2A-24)$$

$$f_2(r) = I_0(2\eta \cdot r) \cdot (1 - \ln(\eta \cdot r)) \tag{2A-25}$$

where  $I_0$ , and  $I_1$ , are the zeroth order modified Bessel function of the first kind, and the first order modified Bessel function of the first kind.  $\gamma(=2B/L)$  is the separation factor and  $\eta = B \cdot t_{Si} / 2 \cdot L$ . The total potential can be obtained by substituting both Eq.(2A-19), and Eq.(2A-23) in Eq.(2A-10). We have observed that the model exhibits the expected symmetry of the potential along the GAA MOSFET axis.

## 2A-3 Threshold voltage derivation

The minimum point at which the potential reaches its minimum value at low  $V_{ds}$  is approximately at the middle of the channel. The determination of the minimum

potential is necessary for the threshold voltage calculation. We rewrite Eq.(2A-10) at the minimum potential value as:

$$\phi_{\min}(x, r) = \phi_{1\min}(x) + \phi_{2\min}(x, r)$$

(2A-26)

where:

$$\phi_{1\min}(x) = \phi_1(x = 0.5) = \phi_{om} \tag{2A-27}$$

and

$$\phi_{2\min}(x,r) = \alpha \cdot \phi_2(x = 0.5, r) \tag{2A-28}$$

where  $\alpha (\cong 0.6-0.75)$  is constant and can be calculated from the fact that  $d\phi_{min}/dV_{GS}|_{L\to\infty} = 1$  [65].

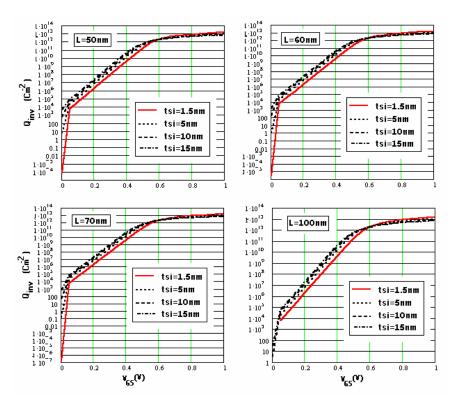

The threshold voltage is defined as the gate voltage at which the minimum sheet density of carriers,  $Q_{inv}$ , reaches a value  $Q_{TH}$  adequate for identifying the turn-on condition[65],[46]. The numerical simulation results indicates that  $Q_{TH} \approx 1.2 \cdot 10^{12} \ cm^{-2}$  (Appendix 2A-1). The minimum sheet density of the channel carriers  $Q_{inv}$  is obtained by integrating their spatial density throughout the entire channel thickness at the channel location where the potential is minimum as:

$$Q_{inv} = \int_{-t_{Si}/2}^{t_{Si}/2} n_i e^{\phi_{min}/V_T} dr = 2 \int_{0}^{t_{Si}/2} n_i e^{\phi_{min}/V_T} dr$$

(2A-29)

One step is sufficient to solve the last integration numerically as:

$$Q_{inv} \approx n_i \cdot t_{si} \cdot e^{[\phi_{om} + \Lambda \cdot (V_{GS} - \phi_{ms} - \phi_{om}) \cdot I_0(\eta)]/V_T}$$

(2A-30)

where

$$\Lambda = \left(\frac{4}{3}\alpha\right) \left[ \frac{C_{si}}{C_{ox}} 2\eta \cdot I_1(\eta) + I_0(\eta) \right]^{-1}$$

(2A-31)

where  $e^{\Lambda \cdot I_0(0)/V_T} \approx 0$ , and  $C_{si}$  is the silicon capacitance per unit channel thickness.

Applying (2A-30) at the threshold voltage condition we find an explicit expression for the threshold voltage as:

$$V_{TH} = \phi_{ms} + \phi_{OM} + \left(V_T \ln \left(\frac{Q_{TH}}{n_i \cdot t_{si}}\right) - \phi_{om}\right) / \left[\Lambda \cdot I_0(\eta)\right]$$

(2A-32)

Therefore, we have obtained a compact threshold voltage model for GAA MOSFETs.

If the channel length is long enough (at  $\alpha (\cong 0.6)$ ), the parameter  $\Lambda$  is saturated at 0.8, and Eq.(2A-32) can be written as:

$$V_{TH} = \phi_{ms} + \left(\frac{5}{4}V_T \ln \left(\frac{Q_{TH}}{n_i \cdot t_{si}}\right) - \frac{\phi_{om}(4I_0(\eta) - 5)}{4}\right) / I_0(\eta)$$

(2A-33)

From (2A-33) we can observe that, as expected, for long channel devices the threshold voltage does not depend on the channel length.

We want to remark that quantum effects, which can be important for Si film thicknesses smaller than 10 nm, have not been considered in this work; they lead to a reduction of the channel charge density and an increase of the threshold voltage [69]; however, the quantum correction to the threshold voltage is much smaller in lightly doped devices than in highly doped ones [70]. Another effect caused by quantum confinement in thin Si films is a small reduction of the subthreshold swing [71]; however, as the Si film thickness is decreased, the excellent gate control of the channel makes the electron distribution unimportant and therefore, the quantum correction to the subthreshold swing becomes negligible.

# 2A-4 Threshold Voltage and its sensitivity

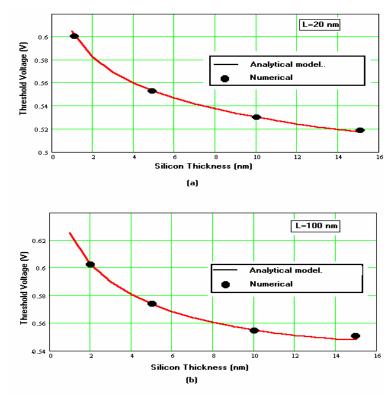

A good agreement with the numerical simulation results (for more details about numerical simulation see appendix 2A-1) was obtained for different channel lengths. Fig.2A-3 shows the plot of the calculated values of the threshold voltage versus the silicon film thickness for two channel lengths. Good agreement is obtained with 3-D numerical simulations (using DESSIS-ISE). For L=100 nm the long-channel approximation, Eq(2A-33) has been applied.

Fig.2A-3 Plots of the threshold voltage versus the Silicon thickness. Comparison between the calculated values of the threshold voltage obtained from a) Eq.(2A-32), and b) Eq.(2A-33), and the values obtained from 3-D numerical simulation results (DESSIS-ISE).

The threshold roll-off,  $\Delta V_{TH}$ , is defined as the difference between the threshold voltage of a device with a certain channel length and the long-channel threshold voltage (which is independent of the channel length). From Eq.(2A-32), and Eq.(2A-33) we find:

$$\Delta V_{TH} = \left(V_T \ln \left(\frac{Q_{TH}}{n_i \cdot t_{si}}\right) - \phi_{om}\right) \cdot \frac{(1 - 1.25/\Lambda)}{I_0(\eta)}$$

(2A-34)

This roll-off model was compared with 3-D numerical simulation results (obtained with DESSIS-ISE). As shown in Fig. 2A-4, close agreement was observed.

Fig. 2A-4 Plots of the threshold voltage versus the channel length. Solid lines: analytical model. Black circles: 3-D numerical simulation results (DESSIS-ISE).

## 2A-5 Subthreshold swing model

The point at which the potential reaches to its minimum value can be obtained directly results to be, from (2A-19):

$$x_{\min} = \frac{L}{2} \tag{2A-35}$$

The resulting value of the minimum total potential is, from (2A-10):

$$\phi_{\min} = \phi_{0m} - \cos(2x_m B) \frac{(V_{GS} - \phi_{ms} - \phi_{om})I_0(2\eta \cdot r)}{\frac{C_{Si}}{C_{or}} 2\eta \cdot I_1(\eta) + I_0(\eta)}$$

(2A-36)

Eq.(2A-36) gives the location of the virtual cathode value. The dependence of the virtual cathode value on the biasing values, and the device dimensions are noticed through Eq.(2A-36).

To find an expression for the subthreshold swing, we assume that the subthreshold drain current,  $I_{ds}$ , is proportional to the total amount of free electrons diffusing over the virtual cathode [72]:

$$I_{ds} \alpha \int_{0}^{t_{si}/2} n_{i} e^{(\phi_{\min} - \phi_{F})/V_{T}} dr$$

(2A-37)

The subthreshold swing, S, can be expressed as:

$$S = \frac{\partial V_{GS}}{\partial \log I_D} = \begin{bmatrix} \int_{r=0}^{r_o} n_m(r) \frac{\partial \phi_{\min}}{\partial V_{GS}} dr \\ \int_{r=0}^{r_o} n_m(r) dr \end{bmatrix}^{-1} V_T \ln(10)$$

(2A-38)

where  $n_m(r)$  is denoted as:

$$n_m(r) = n_i \cdot e^{\phi_{\min}/V_T} \tag{2A-39}$$

Using Eq.(2A-36) in Eq.(2A-38), and taking the value of  $n_m(r)$  and  $\frac{\partial \phi_{min}}{\partial V_{GS}}(r)$  at

r=t<sub>Si</sub>/2 (to have an approximate solution of the integral) the final subthreshold swing is obtained as:

$$S = -\frac{2\frac{C_{Si}}{C_{ox}}\eta \cdot I_{1}(\eta) + I_{0}(\eta)}{I_{0}(\eta)\cos(2x_{m}B)}V_{T} \cdot \ln(10)$$

(2A-40)

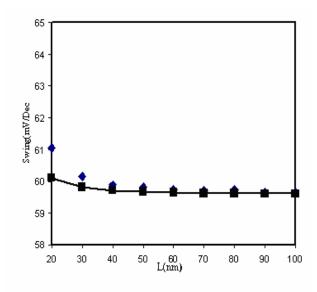

Therefore, a closed form expression for the subthreshold swing has been introduced in Eq.(2A-40). The minus sign in Eq.(2A-40) will be reversed by the sign of the cosine function to be positive, where B, is closer to  $\pi$ . A good agreement is observed in Fig. 2A-5 compared with the 3-D simulation results for different channel lengths. The model introduced in Eq.(2A-40), produces a maximum relative error of about 0.015 for very short channel lengths.

Hamdy Mohamde Abd El Hamid ISBN: 978-84-690-8295-9 / D.L: T. 1514-2007

SCEs in undoped multiple gate MOS

Fig. 2A-5 The subthreshold swing for Gate All Around MOSFET with t<sub>si</sub>=5nm, and t<sub>ox</sub>=1.5nm. Diamond points:3-D numerical simulation results (DESSIS-ISE); lines: analytical model.

# (2-A) Part (II): Short Channel Effects (SCEs) In Undoped Cylindrical Gate All Around MOSFET **Including DIBL Effects**

#### In this section

The model introduced in the Sec.(2.A-1), was not able to calculated the Short Channel Effects SCEs for high drain-source voltage values which limits the model accuracy. In this section, analytical, physically-based, models for the threshold voltage, the subthreshold swing and DIBL of undoped cylindrical Gate All Around (GAA) MOSFETs have been derived based on an analytical solution of the two-dimensional (2-D) Poisson equation (in cylindrical coordinates) including the mobile charge term, by using new techniques that allow to consider the effect of drain-source voltage[80-81].

#### 2A-6 Potential Model Derivation

We shall solve again the Poisson Equation [in Eq. (2A-1)], with complete boundary conditions or,

$$C_{ox}(V_{GS} - \phi_{ms} - \phi(x, r_0)) = \varepsilon_{Si} \frac{\partial \phi(x, r)}{\partial r} \bigg|_{r=r_0}$$

(2A-5)

$$\phi(0,r) = V_{bi} \tag{2A-6}$$

$$\phi(L,r) = V_{bi} + V_{ds} \tag{2A-7}$$

The drain current can be written as,

45

SCEs in undoped multiple gate MOS

$$I_{ds} = q \cdot \mu \cdot n(r, x) \cdot \frac{d\phi_F}{dx} = q \cdot \mu \cdot n_i \cdot e^{[\phi(x, r) - \phi_F]} \frac{d\phi_F}{dx}$$

(2A-41)

or

$$I_{ds} = q \cdot n_{i} \cdot \mu \frac{\int_{0}^{V_{ds}} e^{-\phi_{F}/V_{T}} d\phi_{F}}{\int_{0}^{L} e^{-\phi(x,r)/V_{T}} dx}$$

(2A-42)

where  $\mu$  is the electron low field mobility, and  $r_o=tsi/2$ . In subthreshold the quasi-Fermi potential can be considered to have its value at the source end in most of the channel [46]; in fact, this is only the region which significantly contributes to the integral in the denominator on the right-hand side of (2A-9) [68]. Therefore, for practical purposes, in the 2-D Poisson's equation we can use the expression of the electron density with  $\phi_F=0$  (value of quasi-Fermi potential at the source)

$$n = n_i e^{\phi(x,r)/V_T} \tag{2A-43}$$

The potential can be written as the sum of two terms:  $\phi_o(r)$ , which is the solution of the 1D Poisson's equation in the radial direction, and  $\phi_I(x,r)$ , which is the solution of the remnant 2D differential equation:

$$\phi(x,r) = \phi_0(r) + \phi_1(x,r) \tag{2A-44}$$

Therefore,  $\phi_0(x)$  is the solution of:

$$\nabla^2 \phi_0(r) = \frac{q}{\varepsilon_{si}} n \tag{2A-45}$$

where

$$n = n_i e^{\phi_0(r)/V_T}$$

(2A-46)

The boundary conditions of  $\phi_0(r)$  are:

46

SCEs in undoped multiple gate MOS

$$\left. \frac{\partial \phi_0}{\partial r} \right|_{r=0} = 0 \tag{2A-47}$$

and

$$\frac{\varepsilon_{ox}}{t_1} \cdot \left[ V_{GS} - \phi_{ms} - \phi_0(r_0) \right] = \varepsilon_{si} \cdot \frac{\partial \phi_0}{\partial r} \bigg|_{r_s}$$

(2A-48)

where from [25][67],

$$t_1 = r_0 \ln(1 + t_{ox} / r_0) \tag{2A-49}$$

$\phi_1(x,r)$  is the solution of the remnant 2D Poisson's equation:

$$\nabla^2 \phi_1(x, r) = \frac{q}{\varepsilon_{si}} n_i e^{\phi(r, x)/V_T} - \frac{q}{\varepsilon_{si}} n_i e^{\phi_0(r)/V_T}$$

(2A-50)

or

$$\nabla^{2} \phi_{1}(x, r) = \frac{q}{\varepsilon_{si}} n_{i} e^{\phi_{0}(r)/V_{T}} \left[ e^{\phi_{1}(r, x)/V_{T}} - 1 \right]$$

(2A-51)

Assuming  $\phi_I(r,x)/V_T$  is small, Eq.(2A-51) can be reduced to be a Laplace equation form. Therefore,  $\phi_1(x,r)$  can be considered the solution of:

$$\frac{1}{r}\frac{\partial}{\partial r}r\frac{\partial}{\partial r}\phi_1(x,r) + \frac{\partial^2}{\partial x^2}\phi_1(x,r) = 0$$

(2A-52)

where the boundary conditions of  $\phi_1(x,r)$  can be written as:

$$\phi_1(0,r) = V_{bi} - \phi_0(r)$$

(2A-53)

$$\phi_1(L,r) = V_{ds} + V_{bi} - \phi_0(r) \tag{2A-54}$$

and

$$\frac{\varepsilon_{ox}}{t_1} \cdot \phi_1(r_0, x) = \varepsilon_{si} \cdot \frac{\partial \phi_1(r_0, x)}{\partial r} \bigg|_{r_0}$$

(2A-55)

The solution for the 1-D potential term  $\phi_0(r)$  is given by [58][67]:

$$\phi_0(r) = V_T \cdot \ln \left[ \frac{32}{\delta} \frac{B_n}{\left(4B_n - r^2\right)^2} \right]$$

(2A-56)

The solution of (2A-52) with the boundary conditions (2A-53)-(2A-55) is (for details about the solving procedure see Appendix 2A-2):

$$\phi_1(r,x) = \left[ C_0 \cdot e^{\lambda \frac{x}{r_0}} + C_1 \cdot e^{-\lambda \frac{x}{r_0}} \right] \cdot J_0(\lambda \cdot r)$$

(2A-57)

where

$$\delta = \frac{q}{\varepsilon_{si} \cdot V_T} n_i \cdot r_0^2 \tag{2A-58}$$

and

$$C_0 = \frac{1}{N^2} \cdot \left[ S_1 \cdot (V_{DS} + V_{bi}) - (S_2 + 1) \cdot V_A \right]$$

(2A-59)

$$C_1 = \frac{1}{N^2} \cdot [S_2 \cdot V_A - S_1 \cdot V_B]$$

(2A-60)

where  $S_1$ , and  $S_2$  can be considered scaling factors depending on the device dimensions.  $V_A$ , and  $V_B$  being the biasing effects due to drain and gate-source potentials their values listed below:

$$S_1 = \frac{J_1(\lambda)}{\lambda} \tag{2A-61}$$

$$S_2 = \frac{1 - e^{\lambda \frac{L}{r_0}}}{2 \sinh\left(\lambda \frac{L}{r_0}\right)} \tag{2A-62}$$

$$V_A = J_0 \left(\frac{\lambda}{2}\right) \cdot \left[\frac{\phi_{s0}}{2} + V_T\right] \tag{2A-63}$$

48

SCEs in undoped multiple gate MOS

$$V_{B} = \frac{V_{bi} \left(1 - e^{\lambda \frac{L}{r_{0}}}\right) + V_{ds}}{2 \sinh\left(\lambda \frac{L}{r_{0}}\right)}$$

(2A-64)

And

$$N^{2} = \frac{J_{0}(\lambda)^{2}}{2} \cdot \left[ 1 + \frac{(C_{r})^{2}}{\lambda^{2}} \right]$$

(2A-65)

$$C_r = \frac{\varepsilon_{ox} \cdot t_2}{t_1 \cdot \varepsilon_{si}} \tag{2A-66}$$

$$\lambda \frac{J_1(\lambda)}{J_0(\lambda)} = C_r \tag{2A-67}$$

$\phi_{s0}$  is the surface potential of long-channel devices (1D surface potential, obtained from (2A-56) using r=r<sub>0</sub>), t<sub>2</sub>, and t<sub>1</sub> are device radius, and the modified oxide thickness given by[25][67].  $J_0$ , and  $J_1$  are the zeros of Bessel function type zero, and one respectively. The constant  $B_n$ , in Eq.(2A-56) can be calculated from the boundary condition of Eq.(2A-48). The total potential is calculated by using the expressions of (2A-56) and (2A-57) in (2A-44).

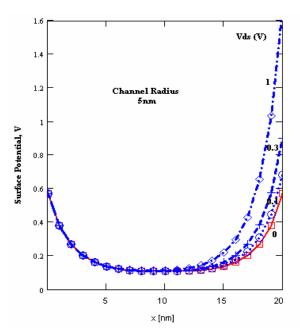

A good agreement has been found between the model we have introduced and the classical 3D numerical simulation results for both low, and high drain-source voltage values as shown in Fig.2A-6 (for  $V_{GS}$ =0.1V).

**Fig. 2A-6**. The surface potential distribution along the channel, for silicon radius is 5nm, and L is 20nm.

## 2A-7 Virtual Cathode: Value and position

The virtual cathode, or the minimum potential can be calculated from the total potential as:

$$\phi_{\min}(r) = \phi_0(r) + \phi_1(x, r)\Big|_{\min}$$

(2A-68)

$\phi_1(x,r)|_{\min}$  is the minimum potential along the longitudinal direction, and can be calculated from

$$\phi_1(x,r)\big|_{\min} = \phi_1(x_{\min},r)$$

(2A-69)

Where

$$\left. \frac{\partial \phi_1(x,r)}{\partial x} \right|_{x_{\min}} = 0 \tag{2A-70}$$

Using Eq.(2A-70) in Eq.(2A-44) we obtain the following expression of  $x_{min}$ ,

$$x_{\min} = \frac{L}{2} - \frac{r_0}{2 \cdot \lambda} \cdot \ln \left[ \frac{S_1 \cdot \left[ V_{bi} \cdot \left( 1 - e^{-L\frac{\lambda}{r_0}} \right) + V_{ds} \right] - \left( 1 - e^{-L\frac{\lambda}{r_0}} \right) \cdot V_A}{S_1 \cdot \left[ V_{bi} \cdot \left( 1 - e^{-L\frac{\lambda}{r_0}} \right) - V_{ds} \cdot e^{-L\frac{\lambda}{R_0}} \right] - \left( 1 - e^{-L\frac{\lambda}{r_0}} \right) \cdot V_A} \right]$$

(2A-71)

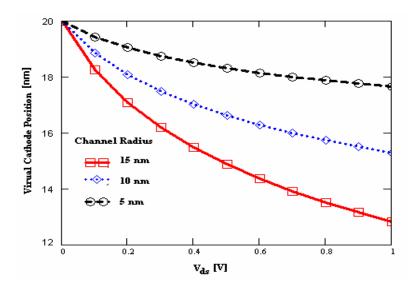

where the second term of Eq. (2A-71) is the modified term due to drain-source voltage (see Fig. 2A-7).

At zero drain-source voltage

$$x_{\min} = \frac{L}{2} \tag{2A-72}$$

However, at high drain-source voltage value the virtual cathode becomes closer to source end.

Fig.2A-7 Virtual cathode position vs. Drain-Source Voltage. The channel length is 40nm.

## 2A-8 Inversion charge and Threshold voltage

Use the same definition for the inversion charge that introduced before in Eq. (2A-29), or

$$Q_{inv} = 2 \int_{0}^{r_0} n_i e^{\phi \left[ x_{\min}, \frac{r}{r_0} \right] / V_T} dr$$

(2A-73)

The integral in (2A-73) can be approximated by its value at  $0.5r_0$  [21][46]. After some mathematical manipulations, one obtains:

$$V_{TH} = \phi_{ms} + \frac{1}{1 - S_{gs}} \cdot \left( V_T \ln \left( \frac{Q_{TH}}{2n_i \cdot r_o} \right) - S_{ds} \right)$$

(2A-74)

$Q_{TH}$  is the value at which the mobile charge density will reach its threshold value, and found numerically to be  $\sim 10^{12} \text{cm}^{-2}$ .

In Eq.(2A-74):

$$S_{ds} = \frac{J_0\left(\frac{\lambda}{2}\right)}{N^2} S_1 \cdot \frac{\left[V_{bi} \cdot \left[\sinh\left(\left[L - x_{\min}\right]\frac{\lambda}{r_0}\right) + \sinh\left(x_{\min}\frac{\lambda}{r_0}\right)\right] + V_{ds} \cdot \sinh\left(x_{\min}\frac{\lambda}{r_0}\right)\right]}{\sinh\left(L\frac{\lambda}{r_0}\right)}$$

(2A-75)

$$S_{gs} = \frac{J_0 \left(\frac{\lambda}{2}\right)^2}{2 \cdot N^2} \cdot \left[ e^{x_{\min} \frac{\lambda}{r_0}} - 2 \cdot e^{\frac{L \lambda}{2 r_0}} \cdot \frac{\sinh \left(x_{\min} \frac{\lambda}{r_0}\right) \cdot \sinh \left(\frac{L \lambda}{2 r_0}\right)}{\sinh \left(L \frac{\lambda}{r_0}\right)} \right]$$

(2A-76)

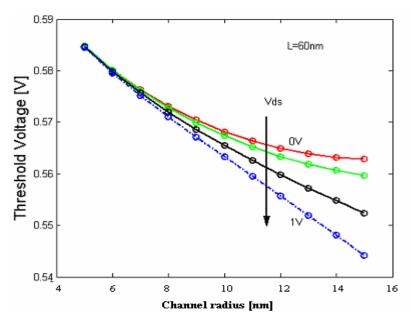

Fig.2A-8 shows threshold voltage for different drain- source voltage values. As the radius increases the threshold voltage tends to be independent of it at low  $V_{ds}$ . However, due to the DIBL we observe a decrease of the threshold voltage at higher values of radius when  $V_{ds}$  is higher enough.

In devices where the channel is long with respect to the channel radius,  $S_{gs}$ , and

$S_{ds}$  are close to zero. Therefore, the long channel threshold voltage can be written as:

$$V_{TH} = \phi_{ms} + \left(V_T \ln \left(\frac{Q_{TH}}{2n_i \cdot r_o}\right)\right)$$

(2A-77)

Eq. (2A-33) will go to Eq. (2A-77) as  $\alpha$  goes to 0.75

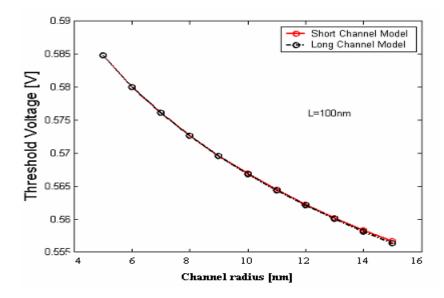

Fig.2A-9 shows that the short-channel threshold voltage model in Eq. (2A-74), will tend to the expression of Eq. (2A-77) for long channel devices.

Eq.(2A-74), and Eq.(2A-77) are the threshold voltage models for both short, and long channel devices. The threshold voltage roll-off is obtained as the difference between the threshold voltage at a given length, and the long-channel threshold voltage Eq.(2A-77)

$$\Delta V_{TH} = V_T \ln \left( \frac{Q_{TH}}{2n_i \cdot r_o} \right) \left[ \frac{1}{1 - S_{gs}} - 1 \right] - S_{ds}$$

(2A-78)

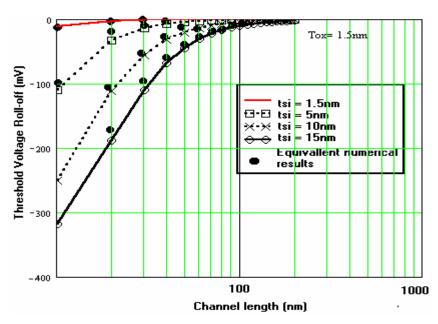

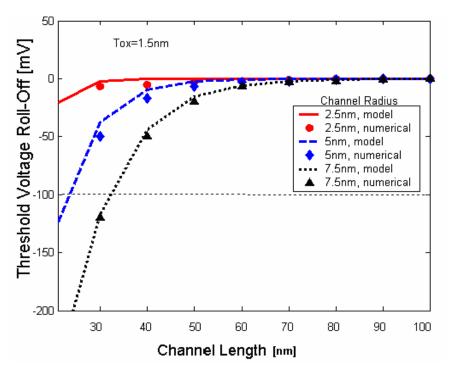

Therefore, we have obtained a complete scalable threshold voltage model for GAA MOSFETs. The threshold voltage roll-off at low drain-source voltage value (10mV), i.e. Eq.(2A-78), is shown in fig. 2A-10. Good agreement is observed for channel lengths down to 30nm.

**Fig. 2A-8** Threshold voltage vs. channel radius, for different drain-source voltage value. The channel length is 60nm.

Fig. 2A-9 Threshold voltage calculated using the long-channel model (2A-77) and the general model (2A-74).  $V_{ds}$ =10mV

$\begin{tabular}{ll} \textbf{Fig. 2A-10} Threshold\ Voltage\ Roll-off\ vs.\ channel\ length\ for\ different\ channel\ radius,\ tox=1.5nm, \\ V_{ds}=10mV. \end{tabular}$

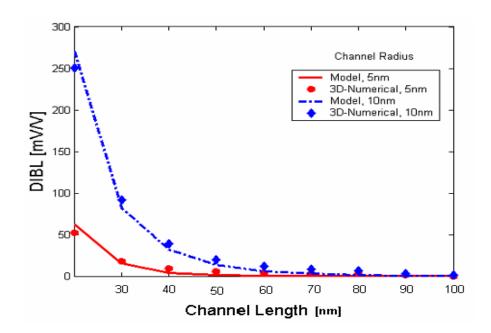

The DIBL, is obtained from the difference between the threshold voltage at high drain-source voltage value (e.g., 1V) and the threshold voltage value at low drain-source voltage (0.1V), using (2A-74) (see Fig. 2A-11). The threshold voltage value at low drain-source voltage is:

$$V_{TH0} = \phi_{ms} + \frac{1}{1 - S_{gso}} \cdot \left( V_T \ln \left( \frac{Q_{TH}}{2n_i \cdot r_o} \right) - S_{dso} \right)$$

(2A-79)

where

$$S_{gso} = \frac{J_0 \left(\frac{\lambda}{2}\right)^2}{2 \cdot N^2} \cdot \left[ 1 + 2 \frac{\sinh\left(\frac{L}{2} \frac{\lambda}{r_0}\right)^2}{\sinh\left(L \frac{\lambda}{r_0}\right)} \right] \cdot e^{-\frac{L}{2} \frac{\lambda}{r_0}}$$

(2A-80)

$$S_{dso} = 2 \frac{J_0\left(\frac{\lambda}{2}\right)}{N^2} \cdot \left[ \frac{\sinh\left(\frac{L}{2} \frac{\lambda}{r_0}\right)}{\sinh\left(L \frac{\lambda}{r_0}\right)} \right] \cdot V_{bi}$$

(2A-81)

Finally, the DIBL is obtained as:

$$DIBL = V_T \ln \left( \frac{Q_{TH}}{2n_i \cdot r_o} \right) \left[ \frac{1}{1 - S_{gSO}} - \frac{1}{1 - S_{gS}} \right] - \left[ \frac{S_{dso}}{1 - S_{gSO}} - \frac{S_{ds}}{1 - S_{gSO}} \right]$$

(2A-82)

**Fig. 2A-11** Drain Induced Barrier Lowering coefficient vs. channel length, for different channel radius, tox=2nm.

#### 2A-9 Subthreshold Swing model

To find an expression for the subthreshold swing, we apply the definition in Eq. (2A-38), or

$$S = \frac{\partial V_{GS}}{\partial \log I_D} = \begin{bmatrix} \int_{r=0}^{r_o} n_m(r) \frac{\partial \phi_{\min}}{\partial V_{GS}} dr \\ \int_{r=0}^{r_o} n_m(r) dr \end{bmatrix}^{-1} V_T \ln(10)$$

(2A-83)

Where  $n_m(r)$  is denoted as:

$$n_m(r) = n_i \cdot e^{\phi_{\min}/V_T} \tag{2A-84}$$

The integral in (2A-83) can be approximated by its value at  $0.5r_0$ . After some mathematical manipulations, one obtain:

$$Swing = \frac{V_T}{1 - S_{gs}} \cdot \ln(10)$$

(2A-85)

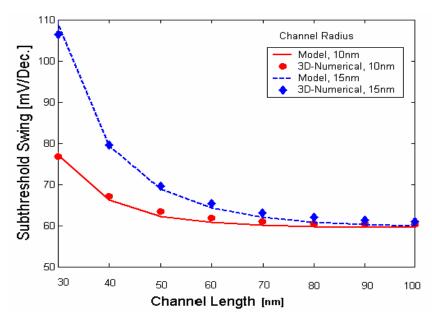

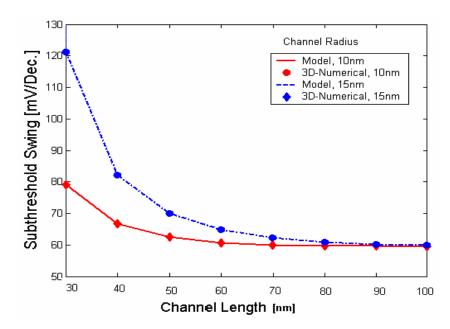

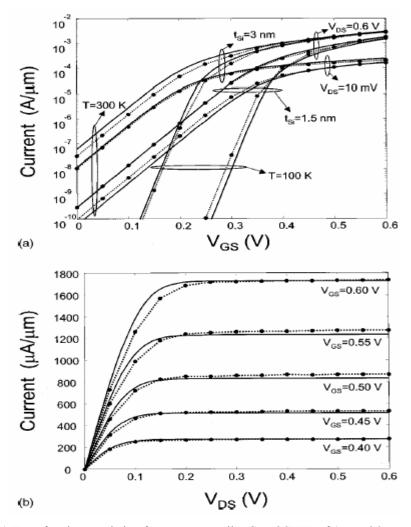

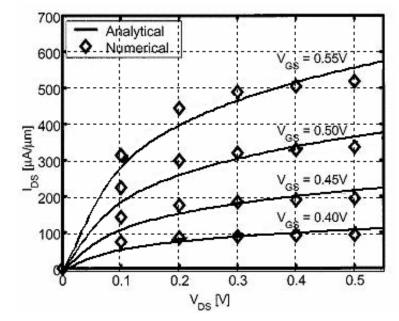

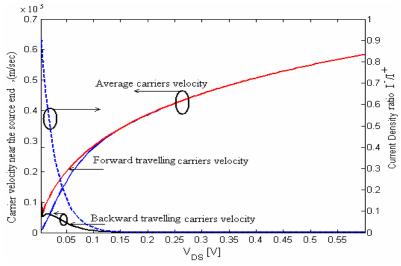

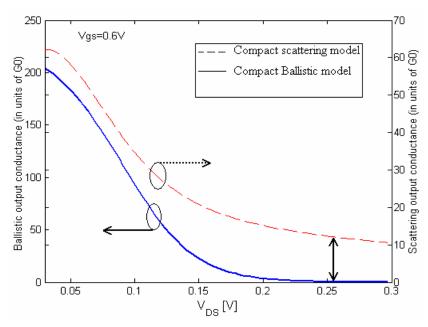

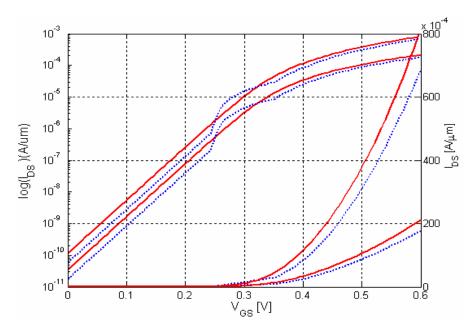

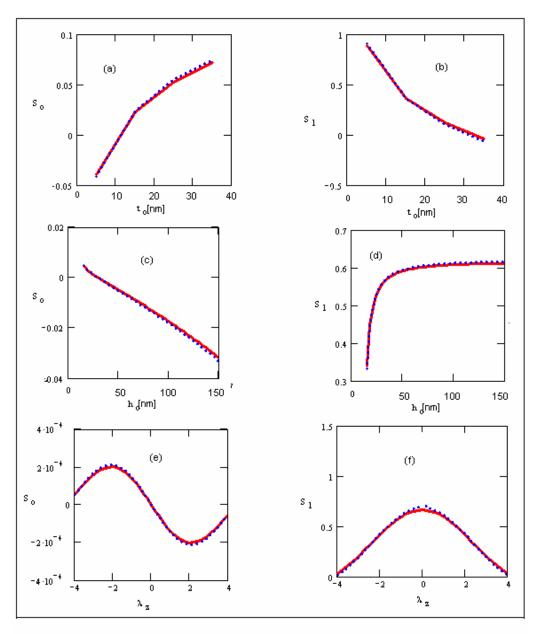

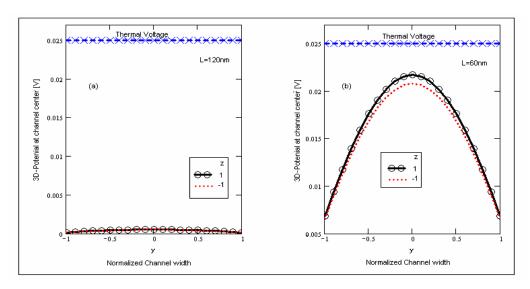

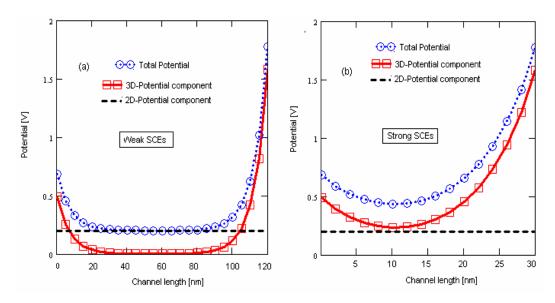

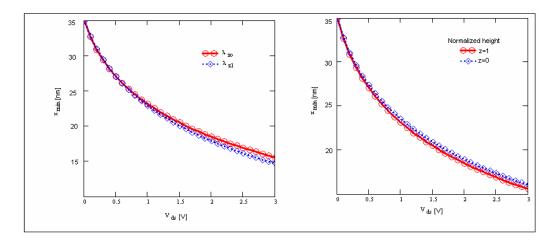

Therefore, a closed form expression for the subthreshold swing is obtained (2A-85). In Figs. 2A-12 and 2A-13 a good agreement is observed between our model (2A-85) and 3-D simulation results for different channel lengths, at low and high drain-source voltage, respectively.