# **TESI DOCTORAL**

Titol: SCINTILLATOR PAD DETECTOR: VERY FRONT END ELECTRONICS

Realitzada per Sonia Luengo Alvarez

en el Centre ETSEEI d'Enginyeria i Arquitectura La Salle

i en el Departament d'Electrònica

Dirigida per Dr. Xavier Vilasis-Cardona

C. Claravall, 1-3 08022 Barcelona Tel. 936 022 200 Fax 936 022 249 E-mail: <u>urlsc@sec.url.es</u> www.url.es

# 'Scintillator Pad Detector: Very Front End Electronics'

PhD Student: Sonia Luengo

PhD Advisor: Xavier Vilasis-Cardona

PhD Program: 'Communication and Information Technologies and their Management'

Electronics Department

Enginyeria i Arquitectura La Salle

Universitat Ramon Llull

July 2008

# A mi familia,

Por la ayuda que me han dado durante todos estos años y por la paciencia que han tenido en los momentos más difíciles.

### A mis amigos,

Porque no hace falta decirles nada para que estén ahí, siempre que los necesito.

### A mis compañeros,

Porque entre todos hemos diseñado una parte de un Detector Europeo del debemos estar orgullosos.

# **Abstract**

High Energy Physics Laboratory in La Salle is a member of a Credited Research Group by La Generatitat. This group is formed by a part of the ECM department, a part of the Electronics department at UB (University of Barcelona) and La Salle's group. Together, they are involved in the design of a subdetector at LHCb Experiment at CERN: the SPD (Scintillator Pad Detector).

The SPD is a part of LHCb Calorimeter. That system provides high energy hadrons, electrons and photons candidates for the first level trigger.

The SPD is designed to identify charged tracks for this first level trigger. This detector is a plastic scintillator layer, divided in about 6000 cells of different size to obtain better granularity near the beam. Charged particles will produce, and photons will not, ionization on the scintillator. This ionization generates a light pulse that is collected by a Wavelength Shifting (WLS) fibber that is twisted inside the scintillator cell. The light is transmitted through a clear fibber to the readout system.

For cost reduction, these 6000 cells are divided in groups using a MAPMT of 64 channels for receiving information in the readout system. The signal outing the SPD PMTs is rather unpredictable as a result of the low number of photostatistics, 20-30 photoelectrons per MIP, and the due to the response of the WLS fibber, which has low decay time. Then, the signal processing must be performed by first integrating the total charge and later subtracting to avoid pile-up as a result of working at 40MHz clock.

This PhD is focused on the VFE (Very Front End) of SPD Readout System. It is performed by a specific ASIC (designed by the UB group) which integrates the signal, makes the pile-up compensation, and compares the level obtained to a programmable threshold (distinguishing electrons and photons), an FPGA which programs the ASIC thresholds, pile-up subtraction and mapping the channels in the detector and finally LVDS serializers, in order to send information to the first level trigger system.

Not only mechanical constraints had to be taken into account in the design of the card as a result of the little space for the readout electronics but also, on one hand, the radiation quote expected in the environment and on the other hand, the distance

between the VFE electronics and the racks were information is sent and the signal range that this kind of experiments usually have.

# Resumen

El Laboratorio de Altas Energías de la Salle es un miembro de un grupo acreditado por La Generalitat. Este grupo está formado por parte del departamento de Estructura i Constituents de la Matèria de la Facultad de Física de la Universidad de Barcelona, parte del departamento de Electrónica de la misma Facultad y el grupo de La Salle. Todos ellos están involucrados en el diseño de un subdetector en el experimento de LHCb del CERN: El SPD (Scintillator Pad Detector).

El SPD es parte del Calorímetro de LHCb. Este sistema proporciona posibles hadrones de alta energía, electrones y fotones para el primer nivel de trigger.El SPD está diseñado para distinguir entre electrones y fotones para el trigger de primer nivel. Este detector está formado por una lámina centelleadora de plástico, dividida en 6000 celdas de diferente tamaño para obtener una mejor granularidad cerca del haz. Las partículas cargadas que atraviesen el centelleador generarán una ionización del mismo, a diferencia de los fotones que no la generarán. Esta ionización generará, a su vez, un pulso de luz que será recogido por una WLS que está enrollada dentro de las celdas centelleadoras. La luz será transmitida al sistema de lectura mediante fibras claras.

Para reducción de costes, estas 6000 celdas están divididas en grupos, utilizando un MAPMT (fotomultiplicadores multiánodo) de 64 canales para recibir la información en el sistema de lectura. La señal de salida de los fotomultiplicadores es irregular debido al bajo nivel de fotoestadística, unos 20-30 fotoelectrones por MIP, y debido también a la respuesta de la fibra WLS, que tiene un tiempo de bajada lento. Debido a todo esto y a la alta frecuencia del experimento (40MHz), el procesado de la señal, se realiza primero mediante la integración de la carga total y finalmente por la substracción de la señal restante fuera del período de integración.

Esta Tesis está enfocada en el sistema de lectura de la electrónica del VFE del SPD. Éste, está formado por un ASIC (diseñado por el grupo de la UB) encargado de integrar la señal, compensar la señal restante y comparar el nivel de energía obtenido con un umbral programable (que distingue entre electrones y fotones), y una FPGA que programa estos umbrales y compensaciones de cada ASIC, y mapea cada uno de los canales recibidos en el detector y finalmente usa serializadores LVDS para enviar la información de salida al trigger de primer nivel.

En el diseño de este tipo de electrónica se deberá tener en cuenta, por un lado, restricciones del tipo mecánico: el espacio disponible para la electrónica en sí, es limitado y escaso, por otro lado, el nivel de radiación que deberá soportar es

considerable y se tendrá que comprobar que todos los componentes usado superen un cierto test de radiación, y finalmente, también se deberá tener en cuenta la distancia que separa los VFE de los racks dónde la información es enviada y el tipo de señal con el que se trabaja en este tipo de experimentos: mixta y de poco rango.

### Resum

El Laboratori d'Altes Energies de La Salle és un membre d'un grup acreditat per la Generalitat. Aquest grup està format per part del Departament d'Estructura i Constituents de la Matèria de la Facultat de Física de la Universitat de Barcelona, part del departament d'Electrònica de la mateixa Facultat i pel grup de La Salle. Tots ells estan involucrats en el disseny d'un subdetector en l'experiment de LHCb del CERN: el SPD (Scintillator Pad Detector).

El SPD és part del Calorímetre de LHCb. Aquest sistema proporciona possibles hadrons d'alta energia, electrons i fotons pel primer nivell de trigger.

El SPD està format per una làmina centellejeadora de plàstic, dividida en 600 cel.les de diferent tamany per obtenir una millor granularitat aprop del feix. Les partícules carregades que travessin el centellejador generaran una ionització del mateix, a diferència dels fotons que no la ionitzaran. Aquesta ionització, generarà un pols de llum que serà recollit per una WLS que està enrotllada dins de les cel.les centellejadores. La llum serà transmesa al sistema de lectura mitjançant fibres clares.

Per reducció de costos, aquestes 6000 cel.les estan dividides en grups, usant MAPMT (fotomultiplicadors multiànode) de 64 canals per rebre la informació en el sistema de lectura. El senyal de sortida dels fotomultilplicadors és irregular degut al baix nivell de fotoestadística, uns 20-30 fotoelectrons per MIP, i degut també a la resposta de la fibra WLS, que té un temps de baixada lent. Degut a tot això, el processat del senyal, es realitza primer durant la integració de la càrrega total i finalment per la correcció de la cua que conté el senyal provinent del PMT.

Aquesta Tesi està enfocada en el sistema de lectura de l'electrònica del VFE del SPD. Aquest, està format per un ASIC (dissenyat pel grup de la UB) encarregat d'integrar el senyal, compensar el senyal restant i comparar el nivell d'energia obtingut amb un llindar programable (fa la distinció entre electrons i fotons), una FPGA que programa aquests llindars i compensacions de cada ASIC i fa el mapeig de cada canal rebut en el detector i finalment usa serialitzadors LVDS per enviar la informació de sortida al trigger de primer nivell.

En el disseny d'aquest tipus d'electrònica s'haurà de tenir en compte, per un costat, restriccions de tipus mecànic: l'espai disponible per l'electrònica és limitat i escàs, i per un altre costat, el nivell de radiació que deurà suportar és considerable i s'haurà de comprobar que tots els components superin un cert test de radiació, i finalment, també s'haurà de tenir en compte la distància que separa els VFE dels

racks on la informació és enviada i el tipus de senyal amb el que es treballa en aquest tipus d'experiments: mixta i de poc rang.

# Table of Contents

| Table of C  | Contents                                      | 1  |

|-------------|-----------------------------------------------|----|

| List of Ta  | bles                                          | 5  |

| List of Fig | gures                                         | 7  |

| Chapter 1   | . Introduction                                | 13 |

| Chapter 2   | . Context                                     | 17 |

| 2.1. L      | IFAELS                                        | 17 |

| 2.2. L      | НС                                            | 17 |

| 2.3. L      | HCb (Large Hadron Beauty Collider) Experiment | 18 |

| 2.3.1.      | VERTEX LOCATOR (VELO)                         | 20 |

| 2.3.2.      | MAGNET                                        | 21 |

| 2.3.3.      | RICH DETECTORS                                | 22 |

| 2.3.4.      | TRACKING SYSTEM (TT, T1, T2, T3)              | 22 |

| 2.3.5.      | CALORIMETERS (SPD/PS, ECAL, HCAL)             | 23 |

| 2.3.6.      | MUON SYSTEM (M1, M2, M3, M4, M5)              | 24 |

| 2.3.7.      | TRIGGER & DATA STORAGE                        | 25 |

| 2.3.8.      | FRONT-END ELECTRONICS ARCHITECTURE            | 26 |

| 2.3.9.      | ONLINE SYSTEM                                 | 26 |

| Chapter 3   | Electronics in particle physics               | 31 |

| 3.1. R      | adiation Environment                          | 32 |

| 3.1.1.      | Cumulative Effects                            | 32 |

| 3.1.2.      | Single Event Effects                          | 33 |

| 3.1.3.      | Safety Factors                                | 34 |

| 3.1.4.      | Material Activation                           | 39 |

| 3.1.5.      | Figures                                       | 41 |

| 3.2. Si     | ignal Characteristics                         | 43 |

| 3.3. L      | VDS Signals                                   | 44 |

| 3.3.1.      | Introduction                                  | 44 |

| 3.3.2.      | Why use low-swing differential?               | 45 |

| 3.3.3.      | Termination                                   | 46 |

| 3.3    | .4. Saving Power                    | 47  |

|--------|-------------------------------------|-----|

| 3.3    | .5. Configurations                  | 48  |

| 3.3    | .6. Economical interface            | 48  |

| Chapte | er 4. Calorimeter – SPD             | 53  |

| 4.1.   | Calorimeter                         | 53  |

| 4.2.   | SPD/PS Detector                     | 56  |

| 4.3.   | Photomultipliers -MAPMT             | 61  |

| 4.4.   | Pulseshape characteristics          | 62  |

| 4.5.   | L0 Calorimeter Triggers             | 64  |

| 4.6.   | Readout Electronics                 | 66  |

| 4.6    | .1. PS/SPD FE Board                 | 67  |

| 4.6    | .2. PS VFE Board                    | 69  |

| 4.6    | .3. Control Board                   | 71  |

| 4.6    | .4. LV Regulation Board             | 73  |

| 4.6    | .5. VFE Units                       | 74  |

| 4.7.   | Grounding and Shielding             | 80  |

| 4.7    | .1. Grounding                       | 80  |

| 4.7    | .2. Electromagnetic Compatibility   | 82  |

| Chapte | er 5. VFE Electronics Solution      | 85  |

| 5.1.   | VFE Requirements                    | 85  |

| 5.1    | .1. Mechanics requirements          | 86  |

| 5.1    | .2. Electronics requirements        | 88  |

| 5.1    | .3. Radiation requirements          | 88  |

| 5.2.   | VFE functional solution             | 89  |

| 5.2    |                                     |     |

| 5.2    | .2. FPGA Design                     | 93  |

| 5.2    | .3. PCB Layout and Design           | 96  |

| 5.3.   | Prototype History                   | 101 |

| 5.3    |                                     |     |

| 5.3    | .2. VFE Unit First Design           | 102 |

| 5.3    | .3. VFE Complete Unit First Design  | 103 |

| 5.3    | .4. VFE Complete Unit Second Design | 105 |

| 5.4.   | Final Design                        | 106 |

| 5.4.1.     | ECS (Experiment Control System) link (Transceivers, Control Unit)  | 107 |

|------------|--------------------------------------------------------------------|-----|

| 5.4.2.     | Light-Electrical Signal Converter: Photomultiplier                 | 112 |

| 5.4.3.     | Analog-Digital Converter (ASIC, Threshold, Subtractor DAC, OpAmps) | 113 |

| 5.4.4.     | Output Adaptation (LVDS Serializers)                               | 119 |

| 5.4.5.     | Final PCB                                                          | 124 |

| Chapter 6. | Tests and Results                                                  | 131 |

| 6.1. In    | troduction                                                         | 131 |

| 6.2. Da    | nta Adcquisition Board (DAb)                                       | 132 |

| 6.3. Pr    | ototype Tests and Results                                          | 133 |

| 6.3.1.     | Laboratory Tests                                                   | 133 |

| 6.3.2.     | Validation Protocol                                                | 143 |

| 6.3.3.     | Test Beam Tests                                                    | 144 |

| 6.3.4.     | Cooling tests                                                      | 149 |

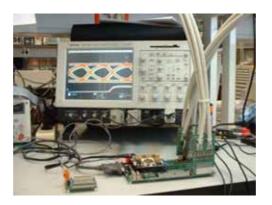

| 6.3.5.     | LVDS Tests_                                                        | 150 |

| 6.4. La    | aboratory Series Tests                                             | 160 |

| 6.4.1.     | Series production                                                  | 160 |

| 6.4.2.     | Noise and Offset Tests                                             | 160 |

| 6.4.3.     | Burn in Tests                                                      | 166 |

| 6.4.4.     | Signal Tests                                                       | 168 |

| 6.4.5.     | Stability Tests                                                    | 173 |

| 6.5. Pi    | t Series Tests                                                     | 178 |

| 6.5.1.     | Mounting at Pit                                                    | 178 |

| 6.5.2.     | Noise and Offset Tests                                             | 179 |

| 6.5.3.     | Signal Led Tests                                                   | 181 |

| 6.5.4.     | Commissioning Tests                                                | 184 |

| Chapter 7. | Conclusions                                                        | 187 |

| Chapter 8. | Publications                                                       | 193 |

| 8.1. In    | troduction                                                         | 193 |

|            | ook contributions                                                  |     |

| 8.3. Co    | ontributions to Conferences                                        | 196 |

| 8.4. Co    | ontribution to Journals                                            | 199 |

| 8.5 Ot     | ther                                                               | 200 |

| References           | 205 |

|----------------------|-----|

| Appendix 1: Mappings | 209 |

| Bottom Mapping       | 209 |

| Bottom Half Mapping  | 210 |

| Top Mapping          | 211 |

| Ton Half Manning     | 212 |

# List of Tables

| Table 1   | Radiation quotes for Calorimeter.                                                | 41      |

|-----------|----------------------------------------------------------------------------------|---------|

| Table 2   | Configuration inside boxes                                                       | 59      |

| Table 4   | Power Consumption measured with a differential probe.                            | 136     |

| Table 5   | Different output impedance at LVDS link.                                         | 153     |

| Table 6   | Cable characteristics at LVDS link                                               | 153     |

| Table 7   | Cable Results for LVDS link                                                      | 155     |

| Table 8   | Summary of compensations for Lanmark.                                            | 157     |

| Table 9   | Results of compensation of Proto                                                 | 158     |

| Table 10  | Summary of compensations for Proto                                               | 159     |

| Table 11  | Book1:LHCb RICH, Technical Design Report                                         | 194     |

| Table 12  | Book2: LHCb Muon System, Technical Design Report                                 | 194     |

| Table 13  | Book3: LHCb Vertex Locator, Technical Design Report                              | 194     |

| Table 14  | Book4: LHCb Outer Tracker, Technical Design Report                               | 194     |

| Table 15  | Book5: LHCb Inner Tracker, Technical Design Report                               | 195     |

| Table 16  | Book6: LHCb Reoptimized Detector Design and performance, Technical Design Re     | port195 |

| Table 17  | Book7: LHCb Trigger System, Technical Design Report                              | 195     |

| Table 18  | Book 8: Calorimetry in High Energy Physics                                       | 195     |

| Table 19  | Beaune Conference                                                                | 196     |

| Table 20  | Heidelberg Conference                                                            | 196     |

| Table 21  | Geneva Conference                                                                | 197     |

| Table 22  | Chicago Conference                                                               | 197     |

| Table 23  | Valencia Conference                                                              | 198     |

| Table 24  | Journal 1: LHCb Calorimeters, Technical Design Report                            | 199     |

| Table 25  | Journal 2: SPD Very Front End Electronics                                        | 199     |

| Table 26  | Journal3: Guiding a mobile robot with Cellular Neural Networks                   | 200     |

| Table 27  | Journal 4: Fabric Tactil Panel                                                   | 200     |

| Table 28  | Journal 5: Determining position inside non-industrial buildings using ultrasound |         |

| transduce | rs                                                                               | 200     |

| Table 29  | Granada Conference                                                               | 201     |

| Table 30  | Padeborn Conference                                                              | 201     |

| Table 31  | Barcelona Conference                                                             | 202     |

| Table 32  | Singapore Conference                                                             | 202     |

| Table 33  | Patent 1: Alfombra con Detector de Presencia                                     | 203     |

| Table 34  | Patent 2: Sistema de localizacion                                                | 203     |

| Table 35  | Patent 3: Rugosímetro                                                            | 203     |

# List of Figures

| Figure 1.    | Aerial view of CERN accelerator complex                                             | 13  |

|--------------|-------------------------------------------------------------------------------------|-----|

| Figure 2.    | Different points of detectors                                                       | 19  |

| Figure 3.    | View of LHCb Detector                                                               | 20  |

| Figure 4.    | General architecture of LHCb Online System                                          | 28  |

| Figure 5.    | Relative activity in the SPD-PS lead, averaged over the lead thickness. 10 years of |     |

| operation d  | and 2 years cooling time.                                                           | 40  |

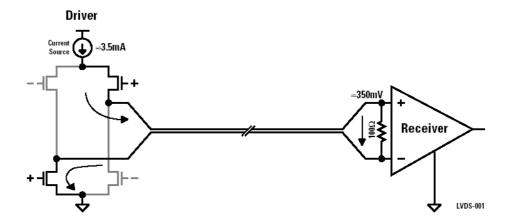

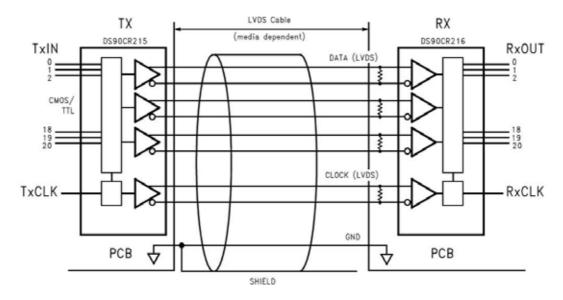

| Figure 6.    | Diagram of LVDS Driver and Receiver                                                 | 45  |

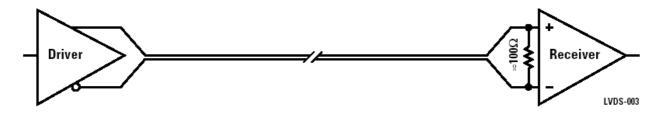

| Figure 7.    | Point to point configuration                                                        | 48  |

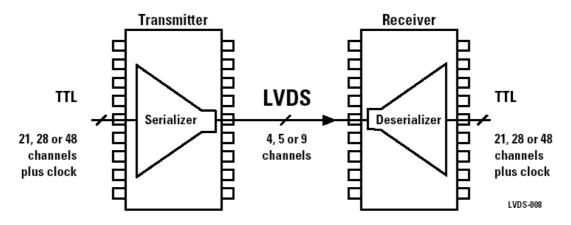

| Figure 8.    | Channel Link Chipset                                                                | 49  |

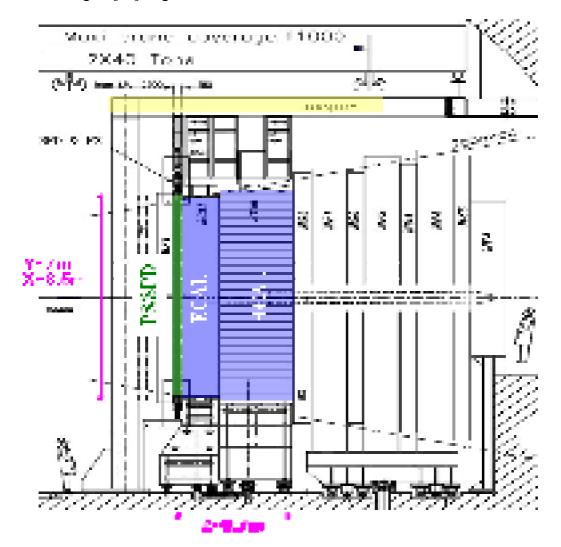

| Figure 9.    | View of the Calorimeter                                                             | 54  |

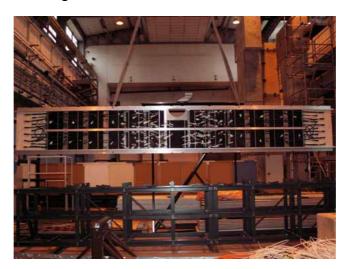

| Figure 10.   | Supermodules under construction                                                     | 56  |

| Figure 11.   | One half of the SPD/PS installed in the LHCb experimental hall (left). Individual   |     |

| scintillator | pad (right)                                                                         | 58  |

| Figure 12.   | A-side configuration                                                                | 59  |

| Figure 13.   | Left, view from the bottom of the detector. Right, view of a Box                    | 60  |

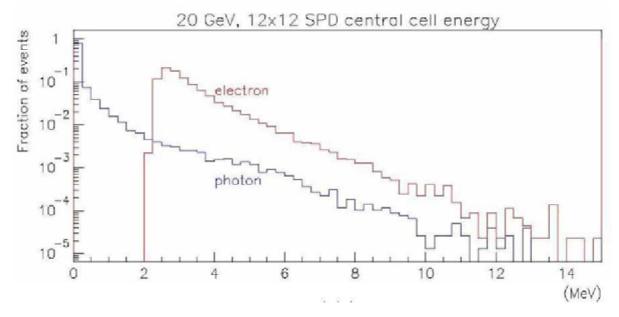

| Figure 14.   | Deposited energy at central SPD cell                                                | 62  |

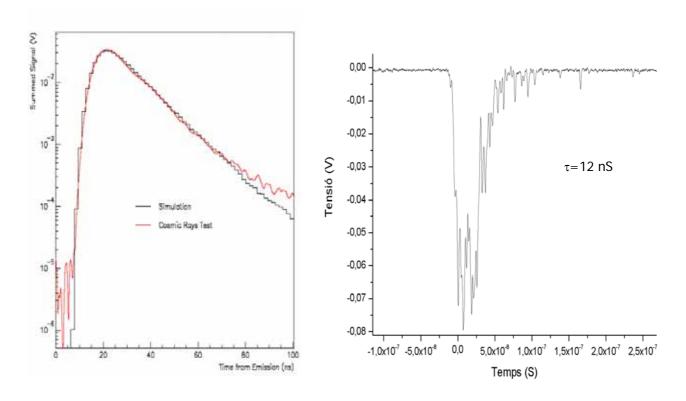

| Figure 15.   | Typical MIP signal shape: (left) average and (right) single event                   | 63  |

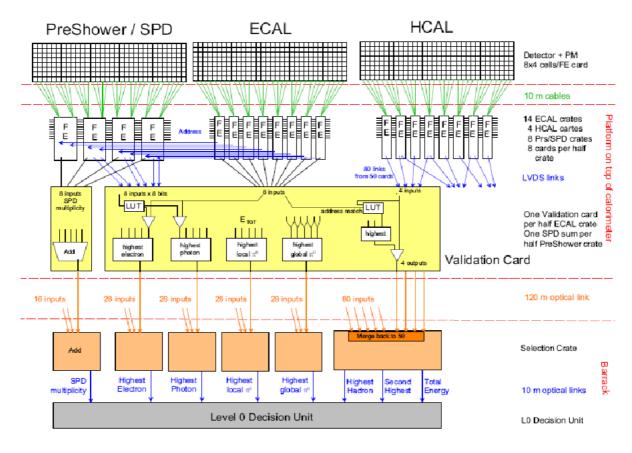

| Figure 16.   | Architecture of Calorimeter Triggers                                                | 64  |

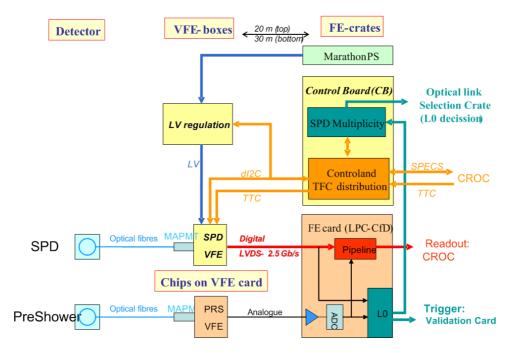

| Figure 17.   | Block diagram of the SPD front-end elements                                         | 66  |

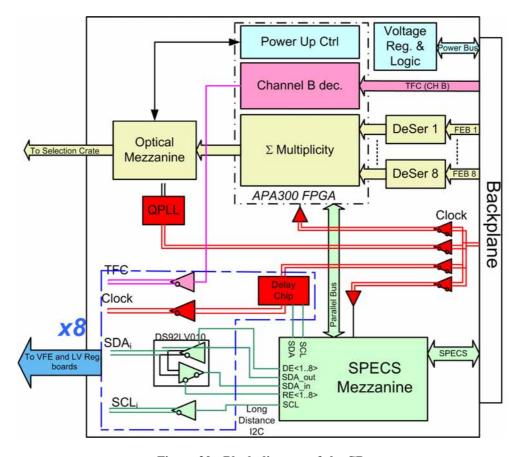

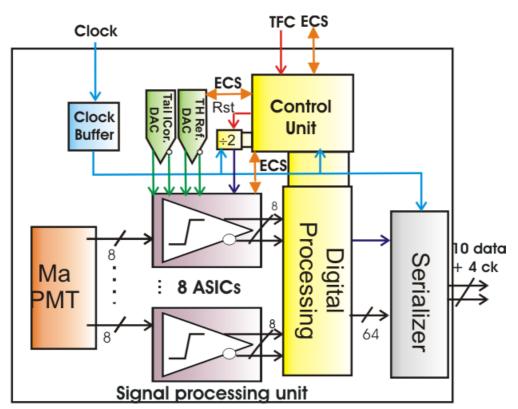

| Figure 18.   | Block diagram of the PS/SPD FE Board                                                | 67  |

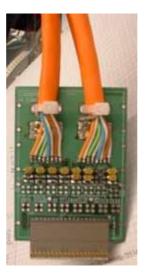

| Figure 19.   | PS VFE picture at Bottom. Diagram Block of the PS ASIC at Top                       | 69  |

| Figure 20.   | Block diagram of the CB                                                             | 71  |

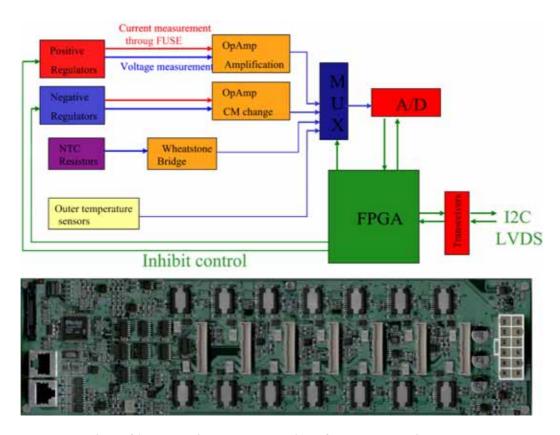

| Figure 21.   | Block diagram and top view of the LV regulation board                               | 73  |

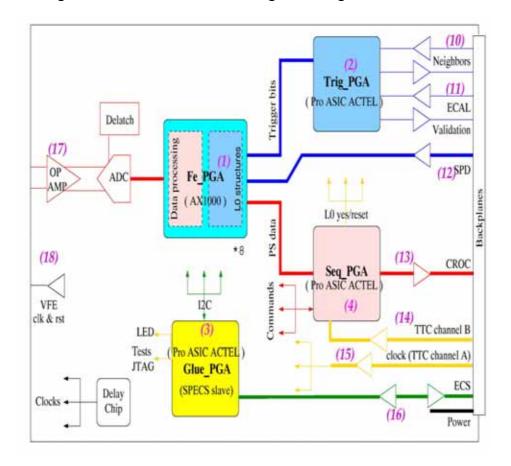

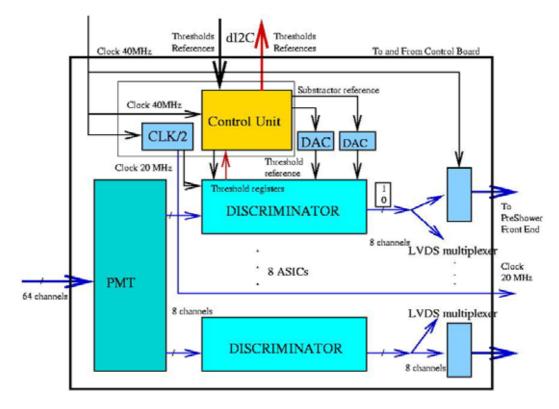

| Figure 22.   | Block diagram VFE Unit                                                              | 74  |

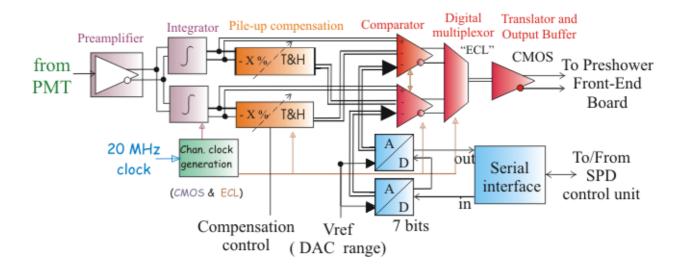

| Figure 23.   | Functional diagram of a discriminator channel                                       | 75  |

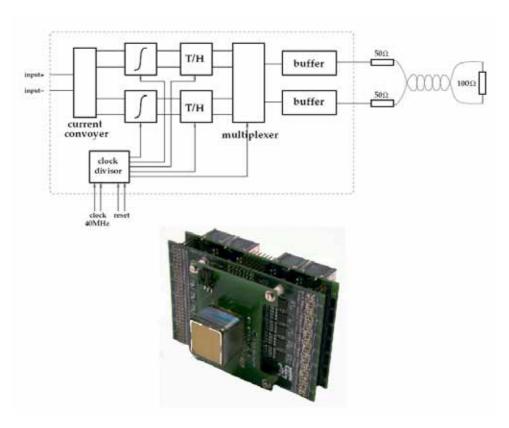

| Figure 24.   | Cable Adaptation                                                                    | 78  |

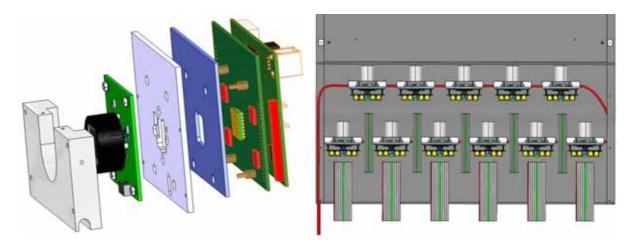

| Figure 25.   | Left, Card. Right, cooling system inside boxes                                      | 79  |

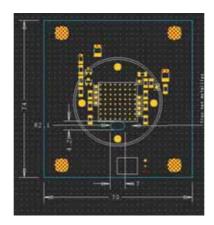

| Figure 26.   | View of the measures of Base Board                                                  | 80  |

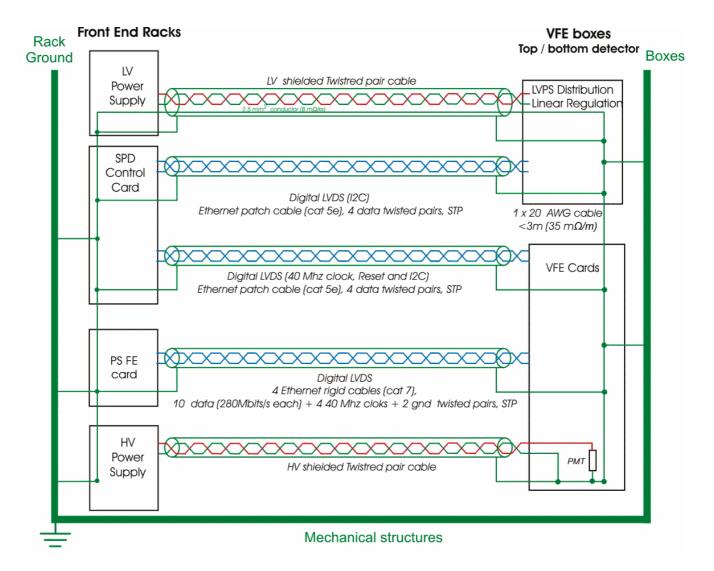

| Figure 27.   | Scheme of the grounding of the SPD                                                  | 81  |

| Figure 28.   | View of the Calorimeter                                                             | 85  |

| Figure 29.   | Left, half SPD. Right, top box detail                                               | 87  |

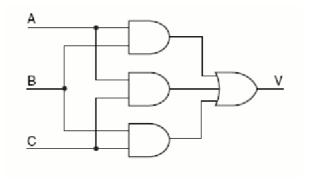

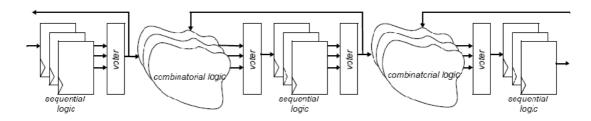

| Figure 30.   | Majority Voter                                                                      | 94  |

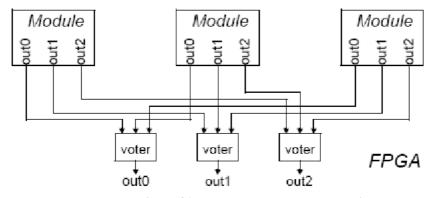

| Figure 31.   | Module Level Implementation                                                         | 94  |

| Figure 32.   | Gate Level Protection                                                               | 95  |

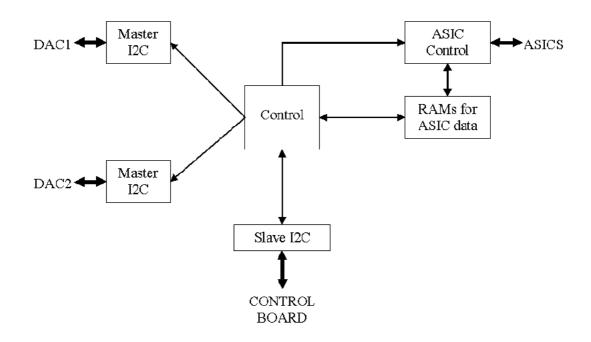

| Figure 33.   | Diagram Block of code implemented in the FPGA                                       | 96  |

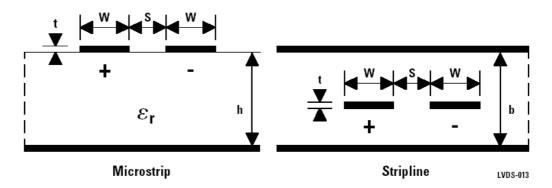

| Figure 34.   | Microstrip and Stripline differential traces                                        | 100 |

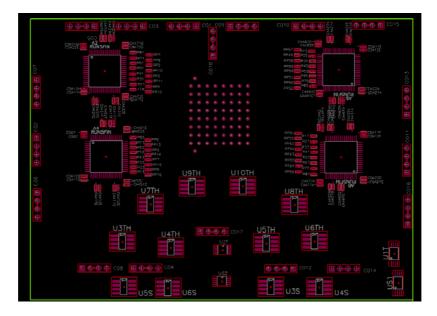

| Figure 35.   | First VFE Unit                                                                      | 102 |

| Figure 36.     | First Complete VFE. Board 1                                                           | 104    |

|----------------|---------------------------------------------------------------------------------------|--------|

| Figure 37.     | First Complete VFE. Board 2                                                           | 104    |

| Figure 38.     | Second Complete VFE. Board 1                                                          | 105    |

| Figure 39.     | Second Complete VFE. Board 2                                                          | 105    |

| Figure 40.     | VFE Diagram block                                                                     | 106    |

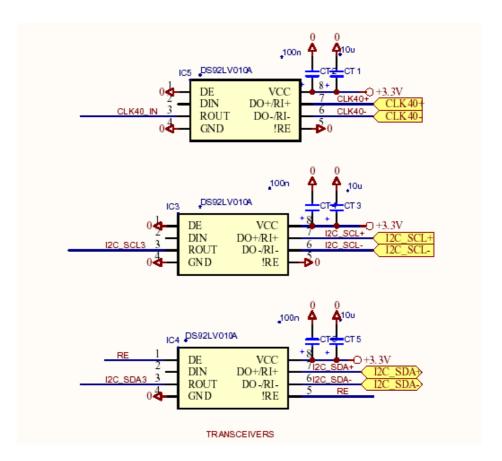

| Figure 41.     | Schematics of LVDS Transceivers                                                       | 108    |

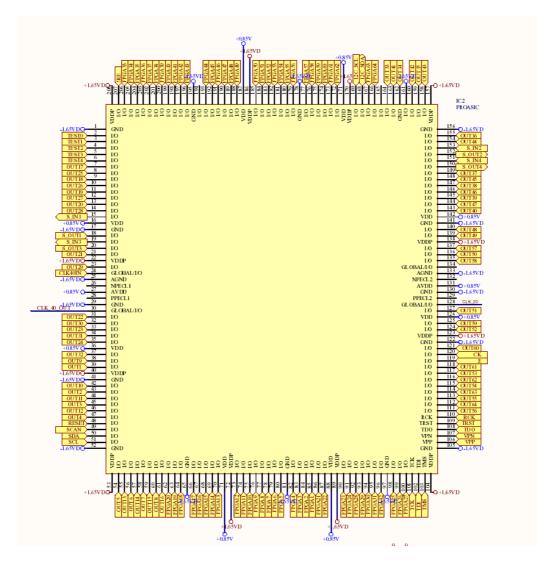

| Figure 42.     | Schematics of FPGA                                                                    | 111    |

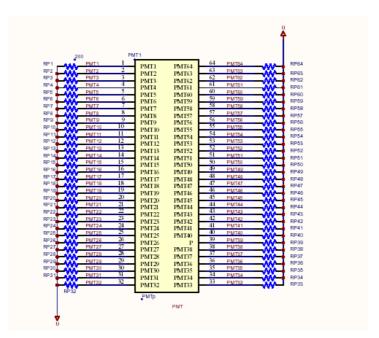

| Figure 43.     | Schematics of Photomultiplier                                                         | 112    |

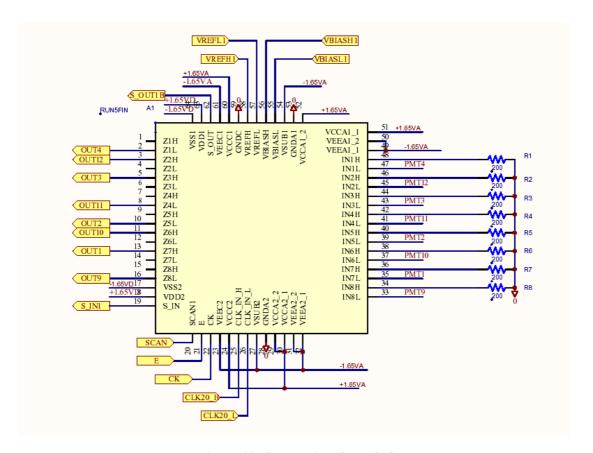

| Figure 44.     | Schematics of an ASIC                                                                 | 114    |

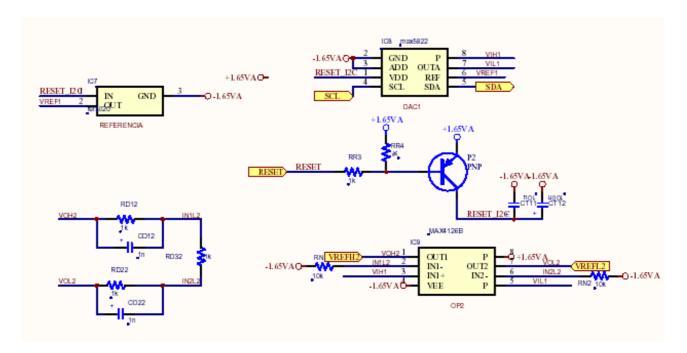

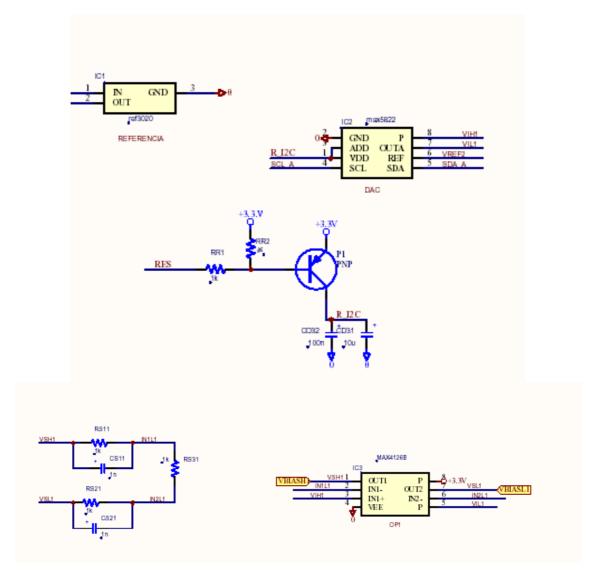

| Figure 45.     | Schematics of Threshold Reference                                                     | 116    |

| Figure 46.     | Schematics of Subtractor Reference. DAC and reference at top, OPAmp at bottom         | 118    |

| Figure 47.     | LVDS Link                                                                             | 120    |

| Figure 48.     | LVDS Chipset Link                                                                     | 120    |

| Figure 49.     | Frame                                                                                 | 121    |

| Figure 50.     | Schematics of LVDS Multiplexer                                                        | 122    |

| Figure 51.     | Schematics of Adaptation (left) and Detail of diodes (right)                          | 123    |

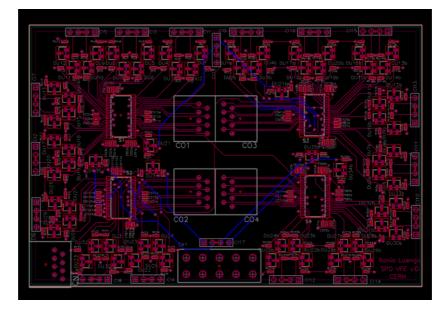

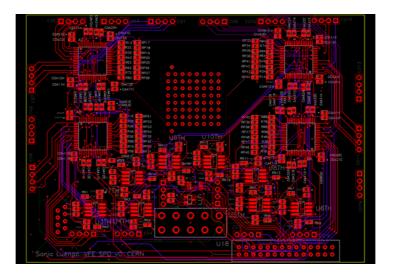

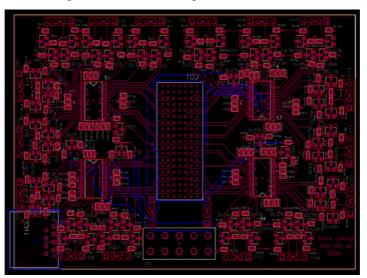

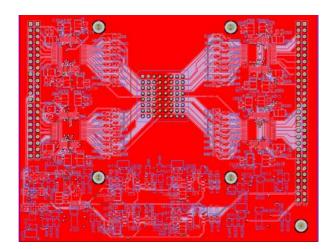

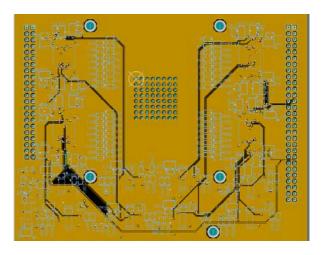

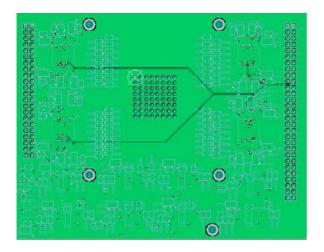

| Figure 52.     | Left, Top Layer. Right, Bottom Layer                                                  | 125    |

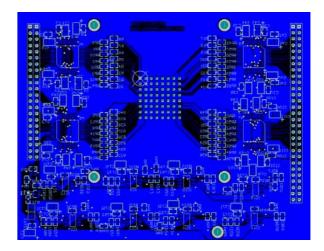

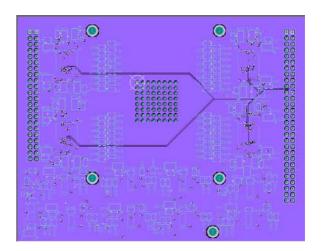

| Figure 53.     | Left, Signal 1 Layer. Right, Signal 2 Layer                                           | 125    |

| Figure 54.     | Left, Clock_H Layer. Right, Clock_L Layer                                             | 126    |

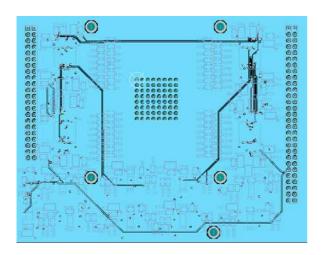

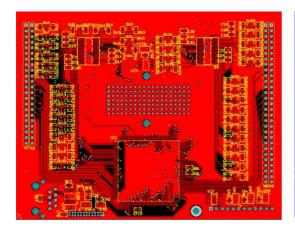

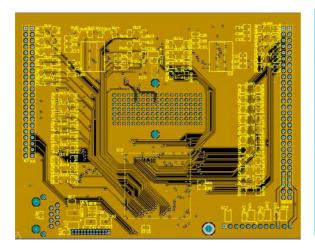

| Figure 55.     | Left, Top Layer. Right, Bottom Layer. Both containing digital signals                 | 126    |

| Figure 56.     | Left, Signal 1 Layer. Right, Signal 2 Layers. Both containing LVDS signals            | 127    |

| Figure 57.     | Left, CLK Layer. Right, GND Plane                                                     | 127    |

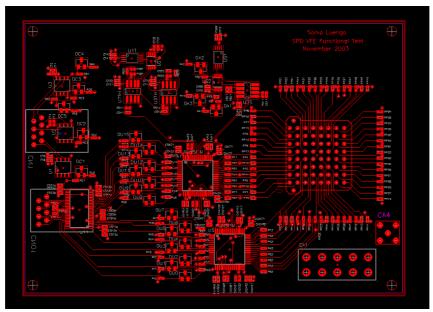

| Figure 58.     | VFE's picture                                                                         | 128    |

| Figure 59.     | Diagram block of the Data Adequisition Board for the VFE                              | 132    |

| Figure 60.     | Scan in (left) and Scan Out (Right) fist ASIC                                         | 134    |

| Figure 61.     | CK and E Signal                                                                       | 134    |

| Figure 62.     | SCL signal going to DAC Vbias. Before (Left) and After Level Shifters (Right)         | 135    |

| Figure 63.     | SDA signal going to DAC Vbias. Before (Left) and After Level Shifters (Right). Write  | te and |

| Read Access.   |                                                                                       | 135    |

| Figure 64.     | Left, SCL signal going to DAC Vref. Right, SDA signal going to DAC Vref               | 136    |

| Figure 65.     | Noise measured without PMT                                                            | 137    |

| Figure 66.     | Differential Mode (Left) and Common Mode (Right). 40MHz clock measured at the         | end    |

| of the control | cable without compensation                                                            | 138    |

| Figure 67.     | Reset by the differential pair before the power adaptation on Ch2 and after on Ch1.   | 139    |

| Figure 68.     | 20MHz Clock measured after transceiver. Clock high left, clock low right              | 139    |

| Figure 69.     | 20MHz clock measured in a differential mode                                           | 140    |

| Figure 70.     | Differential Mode. SDA differential signal at the end of the control cable. Write Acc | cess   |

| (Left) and Re  | ad Access (Right)                                                                     | 140    |

| Figure 71.     | Common Mode. SDA differential signal at the end of the control cable measured on   | the   |

|----------------|------------------------------------------------------------------------------------|-------|

| <i>RJ45</i> .  |                                                                                    | 141   |

| Figure 72.     | Differential Mode (Left) and Common Mode (Right). SCL differential signal at the e | nd of |

| the control co | able measured on the RJ45                                                          | 141   |

| Figure 73.     | Setup and Hold Time on one output of one ASIC (Input of FPGA). Clock of 40MHz      | 142   |

| Figure 74.     | Setup and Hold Time on one output of FPGA (Input of Serializer). Clock of 40MHz.   | 142   |

| Figure 75.     | Power On of FPGA measured with a differential probe                                | 143   |

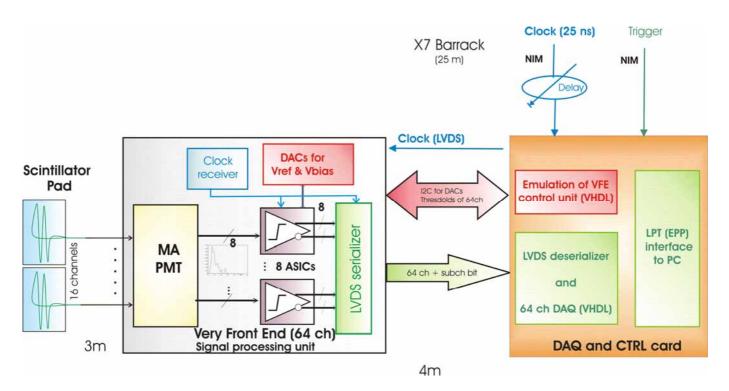

| Figure 76.     | Test Beam Diagram Block                                                            | 145   |

| Figure 77.     | Results of signal shape                                                            | 146   |

| Figure 78.     | Photostatistics Results                                                            | 147   |

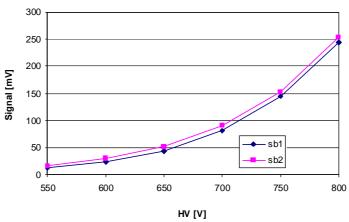

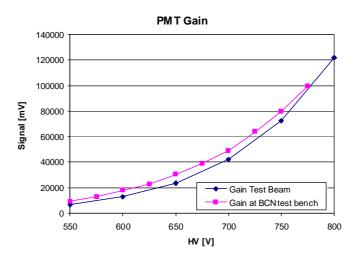

| Figure 79.     | PMT Gain                                                                           | 148   |

| Figure 80.     | Results comparison                                                                 | 148   |

| Figure 81.     | Cooling Results (X's: minutes, Y': ° Celsius)                                      | 149   |

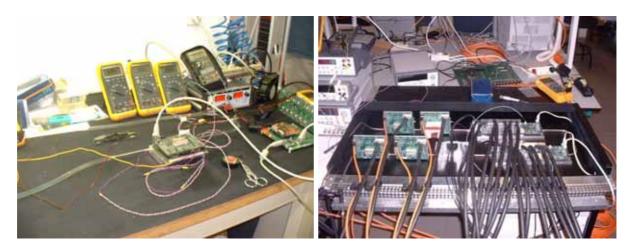

| Figure 82.     | Cooling Test at LPC on 2005, left. Cooling Test at UB on 2006, right               | 150   |

| Figure 83.     | LVDS Set up picture                                                                | 151   |

| Figure 84.     | Diagram block of LVDS Test Setup                                                   | 152   |

| Figure 85.     | Output signal al LVDS multiplexer over 100Ω                                        | 152   |

| Figure 86.     | Step Response                                                                      | 154   |

| Figure 87.     | Equivalent Circuit                                                                 | 155   |

| Figure 88.     | LanMark measurements                                                               | 156   |

| Figure 89.     | Step Response for all compensations                                                | 157   |

| Figure 90.     | Proto Measurements                                                                 | 158   |

| Figure 91.     | Laboratory Setup                                                                   | 161   |

| Figure 92.     | Program Test                                                                       | 161   |

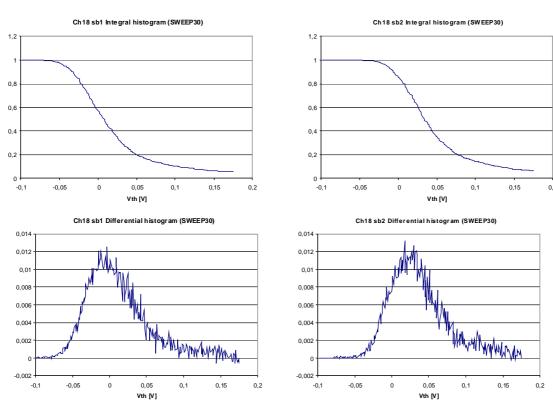

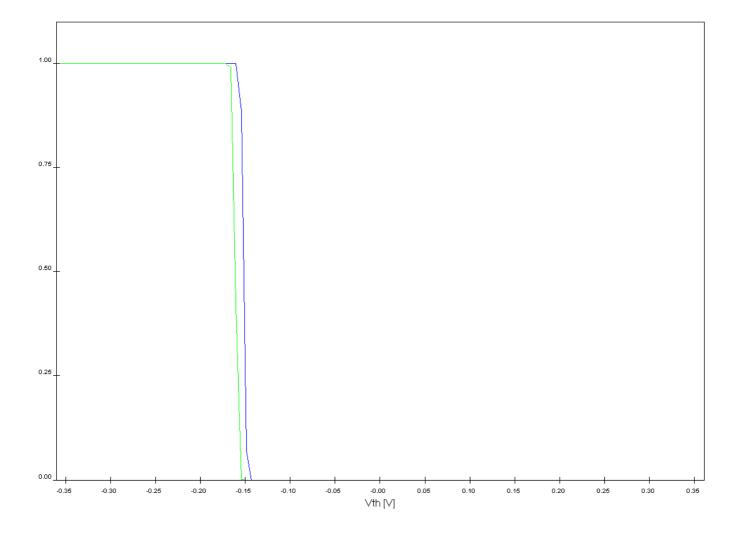

| Figure 93.     | Threshold sweep on channel 25 of S005. First subchannel in blue, second in green   | 163   |

| Figure 94.     | Average noise on S005                                                              | 164   |

| Figure 95.     | Average offset on S005                                                             | 165   |

| Figure 96.     | Internal Offset vs. External Offset                                                | 166   |

| Figure 97.     | Burn in tests                                                                      | 167   |

| Figure 98.     | Burn in results                                                                    | 168   |

| Figure 99.     | Black box setup                                                                    | 169   |

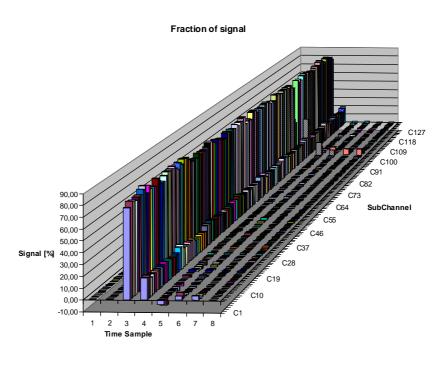

| Figure 100.    | Signal fraction with Vsub=+100mV                                                   | 170   |

| Figure 101.    | Signal fraction with Vsub= -50 mV                                                  | 170   |

| Figure 102.    | Signal fraction with Vsub= -250 mV                                                 | 171   |

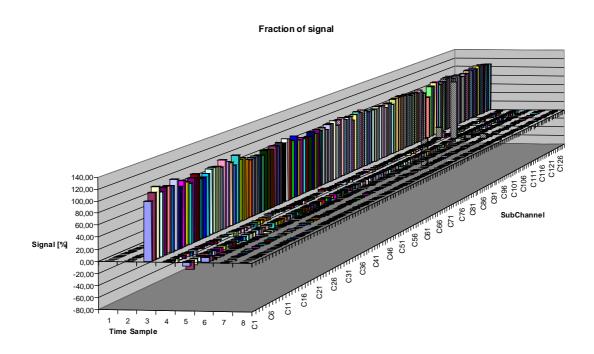

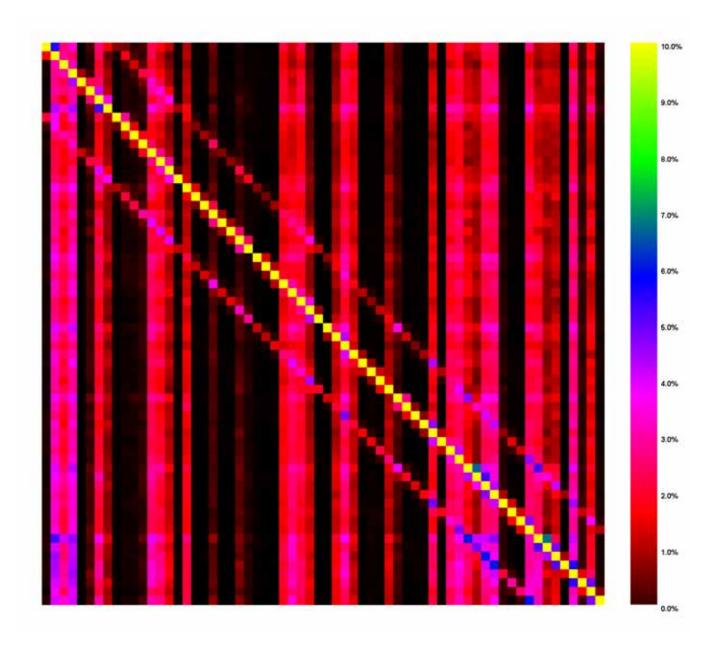

| Figure 103.    | Crosstalk for even channels in S009 VFE Unit                                       | 172   |

| Figure 104.    | View of the box used at laboratory for stability and cooling tests                 | 173   |

| Figure 105.    | Threshold sweep for channel 36. First subchannel in blue, second in green          | 174   |

| Figure 106.    | Average Noise measured on S013 VFE Unit                                            | 175   |

| Figure 107.    | Average Offset measured on S013 VFE Unit                                           | 176   |

| Figure 108. | Internal Offset vs. External Offset                                          | 177       |

|-------------|------------------------------------------------------------------------------|-----------|

| Figure 109. | Transport, left. Mounting on Bottom part, right                              | 178       |

| Figure 110. | Scaffolding, left. View from Top part, right                                 | 178       |

| Figure 111. | Box of 11 VFE Units without cabling                                          | 179       |

| Figure 112. | Test setup at Pit                                                            | 179       |

| Figure 113. | Figures of noise, noisy channels marked (HV=0V Top, HV=700V Bottom)          | 180       |

| Figure 114. | Nut added to improve ground connection                                       | 181       |

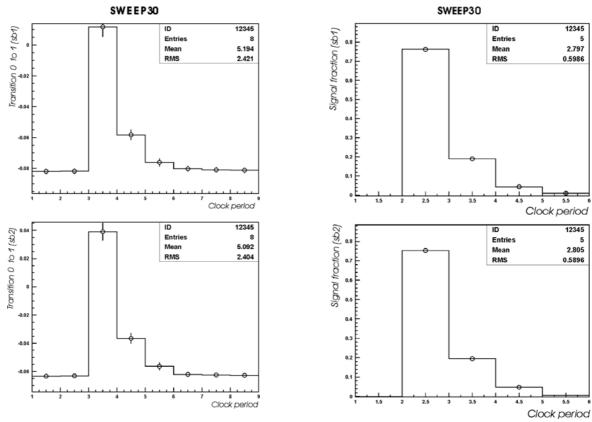

| Figure 115. | Signal fraction achieved changing the delay on trigger signal                | 182       |

| Figure 116. | Signal test on S008 with led setup                                           | 183       |

| Figure 117. | Number of photoelectrons vs. power supply of led card                        | 183       |

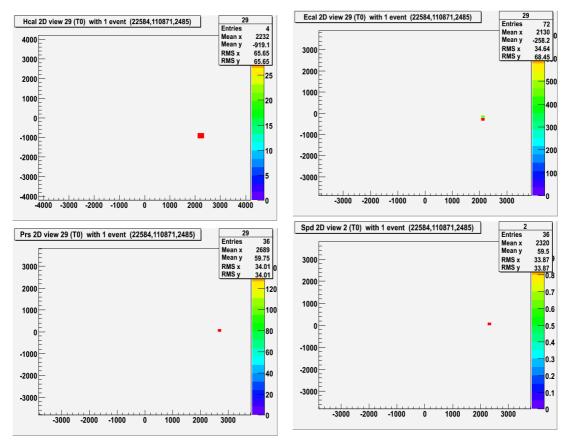

| Figure 118. | Cosmic event in the Calorimeter. HCAL at Top Left, ECAL at Top Right, PS Box | ttom Left |

| and SPD Bot | tom Right                                                                    | 184       |

# Chapter 1: Introduction

# Chapter 1. Introduction

LHCb is one of the detectors hold at CERN (Conseil Européen pour la Recherche Nucléaire). It is the world largest High Energy Physics research center. Located on the Swiss–French border, CERN houses a variety of different accelerator machines and experiments. Founded in 1954, the laboratory was one of Europe's first joint ventures and is now including 20 Member States.

CERN's accelerators and detectors require cutting edge technology, and this is the reason why CERN works in close collaboration with the industry, searching for mutual benefit.

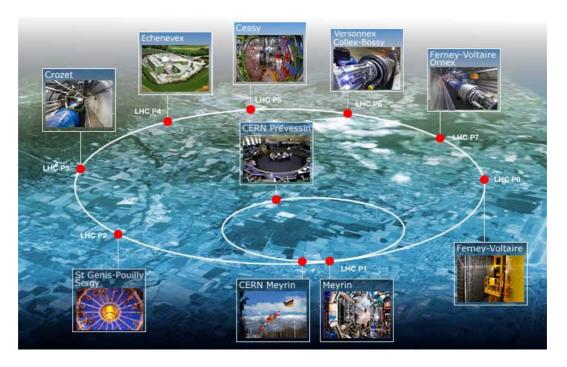

Figure 1. Aerial view of CERN accelerator complex.

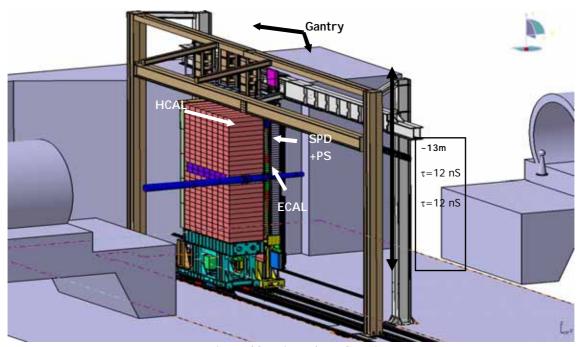

LHCb is formed by several subdetectors described in the next Chapter; one of these subdetectors is the Calorimeter where the work done is related to. The Calorimeter is divided in four subdetectors again: the Hadronic Calorimeter (HCAL), the Electromagnetic Calorimeter (ECAL), the Preshower (PS) and the Scintillator Pad Detector (SPD).

The main goal of the Calorimeter is provided charged particles for first level trigger. These charged particles could be electrons or hadrons. On one hand, the hadrons give a great volume of energy in HCAL which is enough to distinguish them, and on the other hand, the electrons give its energy in the PS and ECAL but the distinction provided by deposited energy is not enough in this case: the desposited energy by photons is such as the energy deposited by electrons, therefore

distinguishing between charged particles or not charged is needed. The SPD is in charged of this function.

This PhD is focused on the design of the Very Front End Electronics involved in the Readout Unit of the SPD. The particular environment, the mechanical constraints, the working frequency as well as the kind of signal will make the electronics solution as a unique one. In this document will be discuss the restrictions and solutions provided for its design.

The following document is divided into the chapters mentioned below, in which the work done during these years is explained. The structure of the document is as follows: In Chapter 1, the global vision of the document is given. In Chapter 2, the context where this work is involved is explained. Chapter 3 gives some keys to take into account in this kind of experiments. Chapter 4 is focused on the subdetector that the group is in charge of designing. In Chapter 5 the solution of this part of the subdetector is described. Chapter 6 shows the results achieved not only during the prototype's design but also the series ones. In Chapter 7, work's conclusions are described. And finally, papers and publications resulting from research work are detailed in Chapter 8.

# Chapter 2: Context

# Chapter 2. Context

This Chapter explains the context where the PhD has been done. First of all it is explained the group where the work is related to, later it is explained the LHC, the particle accelerator where the experiment of LHCb belongs to, and finally, the LHCb and its subdetectors (SPD is one of them).

## 2.1. LIFAELS

The Experimental High Energy Physics group from Universitat de Barcelona had applied to join the LHCb Collaboration in 1998. Prior to this occasion, they offered the Departament d'Electrònica from Enginyeria i Arquitectura La Salle (Universitat Ramon Llull), together with the Departament d'Electrònica at UB, the possibility to join the collaboration in order to design the front end electronics of the SPD in LHCb. This event led to the creation of a group working in high energy physics instrumentation related to the LHCb project in EALS, which has continued to grow according to the project needs (LIFAELS). This collaboration was officially promoted by an agreement between both universities, signed at the end of the academic year 2001-2002. The presented PhD belongs to LIFAELS, the group working in instrumentation for high energy physics mentioned above.

### 2.2. LHC

The Large Hadron Collider (LHC) is a particle accelerator which will probe deeper into matter than ever before. Due to switch on in 2008, it will ultimately collide beams of protons at energy of 14 TeV.

Four experiments, with their corresponding detectors, will study what happens when the LHC's beams collide. They will handle as much information as the entire European telecommunications network does today.

As well as having greater energy than any other accelerator in the world, the LHC will also have the most intense beams. Collisions will happen so fast (40 million times a second) that particles from one collision will still be travelling through the

detector when the next collision happens. Understanding what happens in these collisions is the key to the success of the LHC.

The detectors are:

- ALICE

- ATLAS

- CMS

- LHCb (framework of this study)

# 2.3. LHCb (Large Hadron Beauty Collider) Experiment

A proton–proton collision with a centre of mass energy of 7+7 TeV has a high  $b\bar{b}$  production cross section, about 500 µbarn<sup>1</sup> [1]. As a consequence, the LHC will be by far the most copious source of beauty particles ever built. The high luminosity of the machine will make available with large statistics Bu, Bd, Bs, Bc mesons and a variety of b–hadrons. This suggested installing on LHC a specialized b–physics detector. The name of this detector is LHCb and it is located in LHC P8 (see next figure). Its purpose is to study with high precision CP violation in the B mesons system and to look for new physics effects in rare decays of b–hadrons. The experimental data is expected to bring a deep understanding of the flavor physics inside the Standard Model and to suggest possible extensions.

<sup>&</sup>lt;sup>1</sup> A barn is the unit used in particle physics to measure cross sections that is the effective surface seen by a moving particle on the target. 1 barn =  $10^{-28}$  m<sup>2</sup>

Figure 2. Different points of detectors.

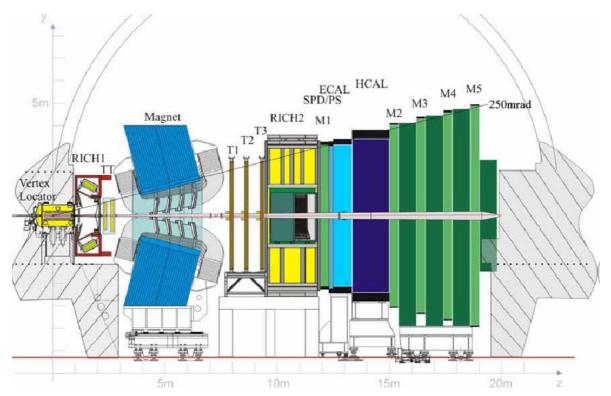

Most of the particle trajectories of interest lie inside a cone of a few hundred mrad apertures, so there is no need to surround the interaction point with detectors. The LHCb design is then very different from the one of the others LHC detectors and from collider experiments in general. The chosen geometry is that of a single–arm forward spectrometer. In this configuration the detector can obtain the same precision as a double–arm one, but the statistics collected is cut in half. Figure 3 shows the actual LHCb layout. The total length of the detector is about 20 meters and it is limited by the cavern dimension. In order to analyze the experimental data, a right handed coordinate system has been defined. Its origin has been fixed on the interaction point; z runs along the beam axis, y points upwards and x points toward the centre of the LHC ring.

Figure 3. View of LHCb Detector

Given the overall detector shape, the single sub-detectors have to be designed to adapt to the events of interest. In particular, a robust and highly performing trigger and a particle identification system are mandatory in order to study the wide range of decay modes.

The LHC bunch crossing clock is 40MHz, which is a very high rate. Taking into account the various subdetectors, we find about 94900 channels (from 1 to 12 bit of resolution, which means 87 Kbytes in total) have to be processed each 25ns. This implies that information rate is about 3.48TBytes/s. It is obvious that is not possible to record or study such amount of information, for this reason and to select "interesting events" (only at the 0.5% of events there is a useful decay to study CP violation) a trigger system is designed to discard non interesting events.

# 2.3.1. VERTEX LOCATOR (VELO)

The hadrons produced in proton-proton primary interactions in LHC and containing beauty (anti-beauty) quarks are highly Lorentz boosted in the laboratory

reference frame and they travel about one centimeter before decaying. The spatial localization of the secondary vertices originated by b-hadrons decays is important information for the event selection system. The primary interaction point is then surrounded by a vertex locator. This device is constituted by 21 silicon stations placed along the beam direction, which can measure particle trajectories in cylindrical coordinates  $(r, \theta, z)$ . The silicon stations are placed at a radial distance from the beam which is smaller than the aperture required by LHC during injection and must therefore be retractable [3].

#### 2.3.2. **MAGNET**

To measure charged particle momentum it is necessary to introduce a magnetic field. LHCb requires a dipole field with a free aperture of  $\pm 300$  mrad horizontally and  $\pm 250$  mrad vertically. In particular, the tracking detectors have to provide momentum measurement for charged particles with a precision better than 0.5% for momentum up to 200 GeV/c. This demands an integrated field of 4 Tm for tracks originating near the primary interaction point. Furthermore, good field uniformity along the transverse coordinate is required by the muon trigger.

The complicated shape of the coils and the high magnetic forces would make a superconducting magnet too expensive and mechanically unstable. LHCb has, therefore, moved to the design of a warm magnet cooled with water. To reduce electrical power requirements to about 4.2 MW, the pole faces are shaped to follow the acceptance angles of the experiment. Besides significantly lower costs, faster construction and lower risks, the warm coils offer additional advantages. A warm dipole permits rapid ramping—up of the field, synchronous to the ramping—up of LHC magnets, as well as regular field inversions to reduce systematic errors on asymmetries in CP violation [4].

This magnetic field will affect the electronics, and then it must be protected in some way as it is described in Chapter 4.

#### 2.3.3. RICH DETECTORS

Particle identification (PID) is a fundamental requirement for LHCb. It is essential for the physics to separate pions from kaons in selected B meson decays. At wide polar angles the momentum spectrum is softer; hence the particle identification system consists of two RICH detectors. The upstream detector, RICH 1, covers the low momentum charged particle range-1-60 GeV/c using aerogel and C4F10 radiators, while the downstream detector, RICH 2, covers the high momentum range from-15 GeV/c up to and beyond 100 GeV/c using a CF4 radiator. RICH 1 has a wide acceptance covering the full LHCb acceptance from ±25 mrad to ±300 mrad (horizontal) and ±250 mrad (vertical) and is located upstream of the magnet to detect the low momentum particles. RICH 2 is located downstream of the magnet and has a limited acceptance of ±25 mrad to ±120 mrad (horizontal) and ±100 mrad (vertical) where there are mainly high momentum particles.

RICH 1 has vertical optical layout symmetry whereas for RICH 2 the symmetry is horizontal. Hybrid Photon Detectors (HPDs) are used to detect the Cherenkov photons in the wavelength range 200-600 nm. The HPDs are surrounded by external iron shields and are placed in Mumetal cylinders to permit operation in magnetic fields up to 50 mT.

### 2.3.4. TRACKING SYSTEM (TT, T1, T2, T3)

The tracking system is composed by four tracking stations. Its purpose is to detect tracks in the zone between RICH1 and RICH2 and to measure particles momentum from their curvature in the magnetic field. This system also has to determinate the direction of the particles crossing the two RICH detectors and it has to connect the information from the Vertex Locator with the information from the calorimeters and the muon chambers.

The tracking stations named respectively T1, T2 and T3 are placed downstream the magnet, just before RICH2. Each of these three stations is built using two different technologies. The innermost part, where the particle flux is greater, is called

Inner Tracker (IT), while the outermost part is named Outer Tracker (OT). The IT covers a cross–shaped area around the beam pipe, approximately 120cm wide and 40cm high.

Each IT station consists of four silicon strip detection layers, with two  $\pm 5^{\circ}$  stereo views sandwitched in between two layers with vertical strips [5]. The OT, on the other hand, is constituted of straw–tube drift chambers.

The fourth tracking station is called Trigger Tracker (TT) and it is placed between RICH1 and the magnet. The TT station fulfils a two-fold purpose. Firstly, it is used to reconstruct the trajectories of low-momentum particles, which are bent out of the experiment acceptance by the magnetic field and thus do not reach stations T1–T3.

Moreover, the TT is used in the trigger to assign transverse momentum information to large impact parameter tracks. The TT is built entirely using the IT technology, but, in contrast with stations T1–T3, it will be split in two sub–stations, with a gap of 30cm in between the second and third detection layers [5].

## 2.3.5. CALORIMETERS (SPD/PS, ECAL, HCAL)

The main purpose of the LHCb calorimeter system is the identification of photons, electrons and hadrons and the measurement of their energies and positions. The collected data is immediately used in the L0 trigger to select the high pT<sup>2</sup> particles. Since this is a real–time selection, the information from the calorimeters has to be available within the 25 ns separating two bunch crossings. The selected data is also used for the complete reconstruction of electromagnetic and hadronic showers, but this analysis requires long time and so it is not part of the L0 trigger. The other essential function of the calorimeter system is the detection of photons with enough precision to allow identification of decay channels which contain in the final state a prompt photon or a neutral pion.

The calorimeter system is constituted of three different sections. The first one, the one closer to the interaction point, is constituted of two detection planes located just

-

$<sup>^{2}</sup>$  pt stands for transverse momentum, that is the fraction of the linear momentum perpendicular to the beam direction.

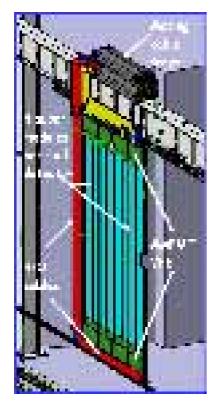

before and just after a 15mm thick lead wall. The detector elements are 15mm thick scintillator pads, which are called respectively Scintillator Pad Detector (SPD) and PreShower detector (PS). A groove in the scintillator holds the helicoidal WaveLength Shifter (WLS) fiber which collects the scintillation light. The light from both WLS fiber ends is sent by long clear fibers to multianode photomultipliers that are located above and below the detector. Since the number of interacting particles per unit surface varies of two orders of magnitude moving from centre to the outer edge, the SPD/PS has been divided in three concentric zones with different spatial granularity.

The Electromagnetic Calorimeter (ECAL) is placed just downstream the PS. It has a sampling structure of 2mm lead sheets interspersed with 4mm thick scintillator plates.

The produced light is collected by WLS filers, which are then bunched together and read by phototubes. Similarly to SPD/PS, ECAL is divided in three zones with different spatial granularity.

The Hadronic Calorimeter (HCAL) is the last calorimeter section. The sampling structure has 16 mm thick iron plates spaced with 4 mm thick scintillator plates, readout via WLS fibers. Given the dimensions of the hadronic showers and the performance requirements of the hadron trigger, the HCAL cells were chosen larger than those of ECAL. Furthermore, a lateral segmentation into only two zones has been adopted [6]. More details about the Calorimeters are explained on Chapter 4.

# 2.3.6. MUON SYSTEM (M1, M2, M3, M4, M5)

Muon triggering and offline muon identification are fundamental requirements of the LHCb experiment. The main requirement for the LHCb muon system is to provide a high–pT muon trigger at the earliest trigger level (L0). In addition, the muon trigger must unambiguously identify the bunch crossing, requiring a time resolution better than 25 ns. The heavy– flavour content of triggered events, enhanced by requiring the candidate muons to have high transverse momentum, is

utilized also offline, to accurately identify muons reconstructed in the tracking system and to provide a powerful B-meson flavour tag.

The muon system consists of five muon tracking stations, named M1, M2, M3, M4 and M5, placed along the beam axis and interspersed with shields to attenuate hadrons, electrons and photons. The first station is located just downstream RICH2 and before the calorimeters, which constitute the attenuator between M1 and M2. These two stations are the ones used to evaluate pT for the L0 trigger. The other three stations are positioned after M2 and are interspaced with iron walls 80 cm thick [7].

Stations M2–M5 are constituted of four layers of Multi–Wire Proportional Chambers (MWPC), while the outermost part of M1 has only two MWPC layers in order to reduce the material budget seen by the calorimeters [8]. In the innermost region of the first station, where the particle flux is higher, the MWPC technology is not suitable. Here the Gas Electron Multiplier (GEM) technology is used, in the form of a triple–GEM detector [9], [10].

#### 2.3.7. TRIGGER & DATA STORAGE

The LHCb sub–systems will produce a large quantity of raw data, which has to be combined and analyzed in order to extract the final results.

The online analysis is clearly not possible as a result of the large amount of data, about 3.48Tbytes/s. The adopted strategy is that of a cascade—like system, in which the lower levels operate very fast and rough decisions and pass the selected events to the upper levels. The implemented system consists of two layers.

• Level zero trigger (L0). The lowest level of trigger is completely implemented in custom electronics. The input frequency is 40 MHz, corresponding to the proton-proton bunch crossing, while the output frequency is 1 MHz. It takes data from SPD, PS, ECAL, HCAL and from the muon system and selects particles with pT. Also the VELO Pile-Up system is considered, in order to reject high-multiplicity events. This rejection assures that the selection is based on b-signatures rather than large combinatorics and that the selected events will not occupy a disproportional fraction

of the data-flow bandwidth or available processing power in the subsequent trigger level.

• *High Level Trigger (HLT)*. The HLT is a software trigger and it is based on data from all sub-detectors. The input frequency is 1 MHz and the output frequency is 2 kHz [11].

## 2.3.8. FRONT-END ELECTRONICS ARCHITECTURE

The front-end architecture chosen for LHC has to a very large extent been determined by the intrinsic problem of making a hardwired short latency trigger, with an efficient event selection, for complicated B events. A fast first level trigger has been found capable of making an event rate reduction of the order of 1 in 10. This has for the chosen LHCb luminosity enforced the use of a front-end architecture with a first level trigger rate of up to 1MHz. This was considered to be highest rate affordable for the DAQ system and required readout links. All sub-detectors store sampled detector signals at the 40 MHz bunch crossing rate in 4 µs deep pipeline buffers, while the hardwired first level trigger (L0) makes the required trigger selection.

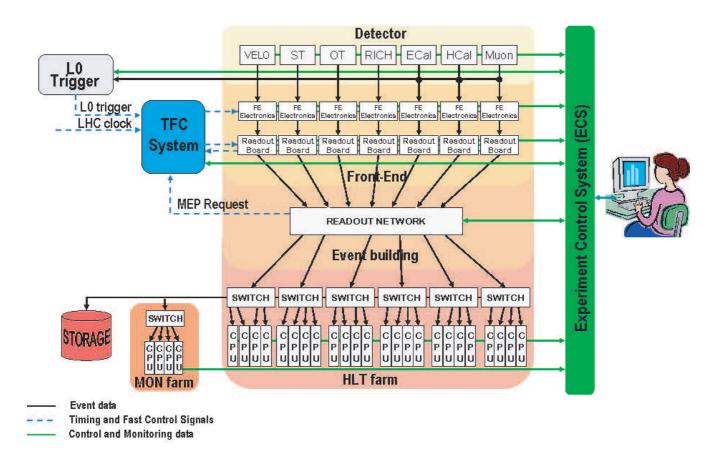

The path that information follows: it begins at Front End System level which works at the same frequency as bunch-crossing, namely 40MHz. This information arrives to the Level0 system that is in charge of making the first trigger selection. Then, the HLT recognizes proper events and finally and gets the L0 decision. Finally, the filtered information arrives to the DAQ system.

#### 2.3.9. ONLINE SYSTEM

The task of the Online system is to ensure the transfer of the data from the frontend electronics to permanent storage under known and controlled conditions. This includes the movement of the data themselves, but also the setting up of all the operational parameters of the experiment and the monitoring of these and the environmental parameters, such as temperatures or pressures. The online system also has to ensure that all detector channels are transferring their data at the same time, relative to the collisions of the particles in the accelerator.

The LHCb Online system consists of three components:

- Data Acquisition (DAQ) system: Its purpose is transporting the data belonging to a given bunch crossing, identified by the trigger, from the detector frontend electronics to permanent storage.

- *Timing and Fast Control (TFC) system*: The TFC system drives all the stages of the data readout of the LHCb detector between the Front-End electronics and the online processing farm by distributing the beam-synchronous clock, the L0 trigger, synchronous resets and fast control commands.

- Experiment Control System (ECS): It ensures the control and monitoring of the operational state of the entire LHCb detector. This encompasses the traditional Detector Control, such as high and low voltages, temperatures, gas flows, or pressures, but also the control and monitoring of the Trigger system and the TFC and DAQ systems. The hardware components of the ECS are somewhat divers, mainly as a consequence of the variety of the equipment to be controlled. This ranges from standard crates and power supplies to individual electronics boards. In LHCb a large effort was made to minimize the number of different types of interfaces and connecting busses. The field busses have been restricted to:

- SPECS, Serial Protocol for ECS, a serial bus providing high-speed,

10Mb/s, control access to front-end electronics [37]

- o CAN (Controller Area Network<sup>3</sup>)

- o (fast)Ethernet

Figure 4 shows the general architecture of the LHCb online system.

<sup>&</sup>lt;sup>3</sup> .ISO Standard 11898., see e.g. www.iso.org

Figure 4. General architecture of LHCb Online System

# Chapter 3: Electronics in particle physics

## Chapter 3. Electronics in particle physics

Electronics in instrumentation is very important to advance in any field. Focusing in the field of particle physics<sup>4</sup>, where the LHCb detector belongs to, the kind of electronics that is used must accomplish some requirements.

On first term, the environment where these electronics must hold with magnetic fields, as it is said in the last Chapter; there is a magnet which makes a magnetic field in order to measure the charged particle momentum, on second term a radiation quote produced by the collision of particles. This fact will imply that every component used in the design must be radiation tolerant; therefore the amount of components that can be used is limited. The kind of signals used in particle physics has to be taken into account as well, as a result of being small range, noisy and sometimes with a difficult processing. This fact forces in most cases a full custom design for the processing.

On last term, the mechanical form of the detector implies some constraints again: large distances from Front End Electronics to the racks where the information is processed. This fact implies the use of several techniques for avoiding interference, noise, skew, jitter...and also the power consumption has to be taken into account in order to decide which way is the best to feed the Front End Electronics.

Next pages explained with more detail these effects on the electronics.

<sup>4</sup> High energy physics (HEP) study phenomena occurring at very high energies, creating conditions under which matter behaves in non usual ways and then new Nature laws manifest. HEP experiments consist normally in colliding accelerated particles with other accelerated particles or with fixed targets. Collision produces complicated reactions which are detected, stored and studied in order to find these new Nature laws.

## 3.1. Radiation Environment

The main applications where radiation environment is a key consideration are medical equipment, high energy physics, nuclear power plants, astronomy, aerospace field and military.

Radiation effects on electronics devices can be divided into two categories: cumulative effects and Single Event Effects (SEE).

#### 3.1.1. Cumulative Effects

They are due to the creation or activation of microscopic defects in the device. Each defect is not significant in itself but the accumulation of these effects can cause the failure of the device. The cumulative effects are mainly of two kinds:

## Displacement Damage

Non-ionizing energy losses in silicon cause atoms to be displaced from their normal lattice sites, seriously degrading the electrical characteristics of semiconductor devices. In displacement damage, it is a common practice to express the radiation environment in terms of particle fluency (particles/cm2). Since the damage induced is a function of the nature and energy of the particle, the Non-Ionizing Energy Loss (NIEL) is used as a parameter for correlating the effects observed in different radiation environments. Though this correlation is not free from uncertainties and failures in some cases, it is still commonly used to translate a complex radiation environment into a simpler mono-energetic equivalent, namely 1 MeV neutrons. The macroscopic effect of displacement damage varies with technology. CMOS devices are practically unaffected up to particle fluencies much higher than those expected at LHC [12]. In bipolar technologies, displacement damage increases the bulk component of the transistor base current, leading to a decrease in gain. Other devices which are sensitive to displacement damage are some kinds of light sources, photodetectors and optocouplers.

## Total Ionizing Dose (TID)

TID effects are due to the energy deposited in electronics by radiation in the form of ionization. The unit for TID in the International System is the Gray (Gy), but the radiation effects community still widely uses the old unit, the rad. The conversion between the two units is simple: 1 Gy = 100 rad. The performance of electronics is affected by the dose deposited in the silicon dioxide used in semiconductor devices for isolation purposes. Ionization in this material leads to the generation of electronhole pairs, which can be separated by a local electric field. Holes can be trapped in the oxide or migrate to the Si-SiO<sub>2</sub> interface to participate in the complex mechanism of interface states creation. Both kinds of defects (trapped holes or interface states) accumulate to affect the behavior of the semiconductor devices.

The consequent macroscopic effect varies with technology. In CMOS technologies, threshold voltage of transistors shifts, mobility and transconductance decrease, noise and matching performance degrade, and leakage currents appear. In bipolar technologies, transistors gains decrease and leakage currents appear.

## 3.1.2. Single Event Effects

These effects are due to the direct ionization of a single particle, which is able to deposit the necessary amount of energy to disturb the correct operating of the device.

Single Event Effects (SEEs) are divided in three groups:

#### Permanent SEEs

Also known as 'Hard errors', they may be destructive.

**Single Event Latchup (SEL)** occurs in CMOS technologies. The onset of a parasitic p-n-p thyristor is triggered by the depositing of ionizing energy in a sensitive point of the circuit. This leads to an almost short-circuit current on the power lines, which can permanently damage the device. Sometimes, this condition can be local and the current can be limited (microlatch), but the effect can still be destructive.

**Single Event Burnout (SEB)** occurs in power MOSFETs, BJT and diodes when these power devices are in the 'off' state. The short-circuit current induced across the high voltage junction can permanently damage the device.

**Single Event Gate Rupture (SEGR)** also affects power MOSFETs in the 'off' state. The dielectric gate can be permanently damaged when, due to the energy deposited by an incoming particle, the electric field across the oxide is temporarily increased beyond the breakdown limit.

#### Static SEEs

Static effects are not destructive, and happen whenever one or more bits of information stored by a logic circuit are overwritten by the charge collection following the ionization event. This effect is defined **Single Event Upset (SEU)**. A special case of SEU is called Single Event Functional Interrupt (SEFI). This happens in complex circuits due to an error induced on a bit of information which controls a special function of the circuit (most often, a special test mode). A reset is necessary to bring the circuit back to the operational condition.

#### Transient SEEs

Charge collection from an ionization event creates a spurious signal that can propagate in the circuit. This can happen in most technologies, and its effect varies very significantly with the device, the amplitude of the initial current pulse, and the time of the event in relation to the circuit. Typical examples are transient pulses in combinatorial logic, which can propagate and ultimately be latched in a register, and rail-to-rail voltage pulses at the output of operational amplifiers (SET).

## 3.1.3. Safety Factors

The radiation level estimations for LHCb are generated from Monte Carlo simulations with FLUKA. Uncertainties related to the Monte Carlo simulations and their assumptions on interaction models are normally estimated to be of an order of a factor two. The radiation hardness qualification of components will also have uncertainties associated with them (e.g. dosimeter uncertainties). The components

themselves may have significant uncertainties depending on the origin of the components. ASICs from a well defined processing batch will only have a relatively small uncertainty on their measured radiation hardness. Commercial components purchased as a single lot from a well defined production batch will normally also only have limited radiation hardness variations. Commercial components purchased in different lots from independent distribution sources can be expected to have significant variations in radiation hardness.

The safety factors to apply to the qualification of components for LHCb strongly depends on the type of radiation effect, the type of component and the specific use of the component in LHCb. The final choice of safety factors used all boils down to general risk management. The total risk of failing components compromising the correct function of LHCb must be minimized within an acceptable budget. Components used in locations where they cannot easily be exchanged must be qualified with significant safety factors. Components (e.g. modules) that can be exchanged within a few hours can potentially be qualified with lower safety factors.

A clear distinction must be made between accumulated effects and single event effects. Single event effects are of statistical nature and may therefore occur at any time and at any place (obviously proportional to flux of particles and sensitivity of components). For single event effects it is important to ensure that the time between failures is sufficiently long to guarantee an effective running of the whole experiment over extended periods. Single event upsets can be recovered by a simple reinitialization of the electronics. The re-initialization of the electronics can be done at several levels. State-machines or pipeline registers can normally be recovered by a "simple" reset. Single event upsets in configuration registers will require a reloading of parameters via ECS (Experiment Control System). In both cases it will be necessary to restart active data taking with the DAQ system. It is important to ensure that this kind of soft failure does not occur so often that the system will spend a significant part of its time resolving random single event upsets. Single event upsets that prevents single detector channels to work correctly can in many cases be accepted during limited time periods, if and only if this do not significantly affect the physics and the triggers of the experiment. Bit flips in event data itself can normally be tolerated if they do not have any effect on the correct handling of following events. Single event latchup's (and single event burnout) will in many cases be a fatal failure requiring repair, unless special latchup protection circuits have been used. Single event Latchup must therefore be proven to happen sufficiently seldom that the whole LHCb experiment can work for several weeks without repair. Even hard failures can in some cases be accepted during extended periods if it can be guaranteed that the failure do not seriously affect the physics performance of the experiment. In many cases a few local "dead" detector channels will not have a significant effect on the physics of the experiment. It must though be ensured that local failures are prevented from disturbing higher levels of the system and thereby affect data collected from other parts of the detector.

Cumulative effects risk to make large parts of an electronic system unusable after a given radiation threshold has been reached. Such a situation may occur after several years of operation at a time when the components used have become obsolete and cannot be purchased commercially. For systems with large variations in radiation levels for different parts of the system (e.g. small part of front-end electronics very close to beam line) it can be envisaged to exchange limited parts of the electronics system after a certain number of years. For systems with a more uniform radiation exposure it is unrealistic to start exchanging components when they start to fail one by one. In this case it must be proven that the system can stand the radiation levels over many years of operation (10 years).

Safety factors for cumulative effects (total dose and displacement damage)

- Simulation uncertainty => Factor 2

- Radiation qualification uncertainty => Factor 2

- Component to component variation :

- o Same fabrication line, no technology changes=> Factor 2

- o Same manufacturer, unknown fabrication line=> Factor 100

- o Different manufacturer=> Re-qualification required

For cumulative effects this adds (multiplies) up to total safety factors between 8 to 400. It is clearly seen that large safety factors are required if the components used do

not come from the same fabrication line (or similar line with same process) as the components initially qualified for radiation resistance. It is in fact quite difficult in practice to guarantee that commercial components come from production lines with the same process characteristics. The safety factor related to this (100) can though be significantly lowered (2) if a new production lot, all coming from the same production line (but not necessarily the same as the qualified ones), are re-qualified by testing a new set of samples from the final lot.

The safety factor of 100 for the case of an unknown fabrication line does in fact not really make sense since certain technology changes may have very large effects on the radiation tolerance and is in principle unpredictable. The chosen safety factor has been taken as to have some confidence that in practice things will not get worse than this. In most cases such a large safety factor will enforce a re-qualification except for locations with very low radiation levels (e.g. concrete tunnel).

The minimum total safety factor of 8 can only in special justified cases be decreased. If it can be justified that the radiation qualification has been made with very precise monitoring of the radiation levels the safety factor related to this can potentially be decreased. If a thorough radiation qualification of a statistically significant part of the final production batch have been made (more than 10 units) the safety factor related to component to component variations can potentially be decreased. The acceptance of such exceptional cases can only be made after a special review organized by the electronics coordinator and a final acceptance by the LHCb technical board.

Safety factors for single event effects

- Simulation uncertainty => Factor 2

- Radiation qualification uncertainty=> Factor 2

As single event effects are a question of statistics, the number of possible failures must be estimated and the effect of the failures on the system must be evaluated. No strictly defined radiation hardness criteria can therefore be given. From a system perspective a few guidelines can though be defined. Acceptable failure rates for different failure types can be defined at the system level. To define acceptable failure rates for individual sub-systems a simple model assuming ~10 independent sub-

systems (individual sub-detectors, L0 trigger, HLT trigger, DAQ, etc.) in LHCb is used. Failure rates must be handled differently according to the following classification:

Single bit flips in event data with no effect on following events. Single bit errors in event data can in general be accepted when it is assured that it will not have any negative effect on following events

SEU requiring reset of front-end electronics and re-synchronize DAQ system. Bit flips in state-machines, pipeline registers and other synchronization logic in the front-end electronics, that only needs a front-end reset sequence (L0+HLT front-end reset) to recover correct function, can potentially be handled at rates up to several times per minute if really required.

SEU requiring instant re-initialization of front-end electronics via ECS. Bit flips in setup and configuration registers in the front-end electronics will need to be corrected by the ECS system downloading new configuration data.

SEU in configuration data that can wait for next planned re-configuration. For bit flips in configuration data that does not need immediate correction for LHCb to continue to work efficiently one can possibly wait for the next reconfiguration to be made (~once per day). Even in this case it is important to have schemes to detect that such a condition has occurred.

Hardware failures requiring instant repair. Fatal system failures requiring instant repair for the experiment to work is obviously the most serious failure mechanism. Such failures can be caused by single event latchup in integrated circuits or single event burn out in a power supply (or other possible failure mechanisms not related to radiation). The time required to repair such failures strongly depend on the location of the electronics:

Counting room: Radiation levels in the counting room is so low that electronics will not be affected and immediate access can be given while LHC is running. Electronics can be repaired with a few hours notice (assuming spare parts available).

Cavern with insignificant residual radiation: Can in principle be accessed with a few days notice. Access periods will strongly depend on the running conditions of the LHC machine itself. At startup of LHC it is planned to have short weekly shut-

downs of the LHC machine. When reliable operation of LHC is achieved, access to the cavern will depend on agreed shut-down periods between all the LHC experiments and the LHC machine.

Cavern with residual radiation: Residual radiation will in some cases limit access to long shutdown periods (~once per year) where things have time to cool down. The regions around the interaction point (vertex tank) and the beam pipe will in this respect pose potential problems. Electronics where a single point failure can prevent LHCb to collect worthy physics data should never be placed in zones with significant residual radiation.

*Inside detectors:* Electronics located inside detectors can only be repaired when detectors are open which can only be done during long shut-down periods (once per year). Electronics modules vital for the global LHCb experiment must never be placed inside detectors in most cases, but for example, for the SDP VFE there is no other way to manage it.

Hardware failures not requiring instant repair: Electronics dealing with limited number of isolated detector channels can normally be accepted to have hardware failures for limited time periods without affecting seriously the physics of LHCb. For electronics located in the cavern, without residual radiation these failures will be repaired at the first possible occasion (~once per month). For electronics located in zones with significant residual radiation, or within the detector itself, repairs can only be performed once per year and it must be ensured that only an insignificant number of detector channels will be lost over a period of one year of running.

## 3.1.4. Material Activation

Materials can become activated when hadronic interactions occur within them; that is the case of the LHCb experiment where, as in any accelerator environment, a multitude of radionuclides can be produced due to spallation reactions. On the other hand not all interactions yield radioactive isotopes; the resulting nuclide can in fact also be stable. Many radioactive isotopes have short half-lives and disappear rather quickly, while other have longer decay constants and remain active in the material

for an extended period of time. In the latter case, the materials have to be considered as radioactive and an appropriate handling and disposal schemes have to be devised [39]. Some studies have been performed with FLUKA simulation code [40, 41], to determine the induced radioactivity of the materials in the LHCb experimental setup with the aim of defining a Radioactive Waste Reference Zoning for LHCb equipment.

One of the main concerns in the design of the experiment was to keep the material budget to a minimum within the acceptance from the interaction point (IP) to the Calorimeters. Although the impact on the physics measurements was the main reason to do so, this also results in a reduced amount of hadronic interactions, and thus activation, in the region from the IP to  $z \sim 1200 cm$ . A significant amount of activation is expected in the Calorimeters and Muon Filters, particularly in the very forward region, and very closes the IP.

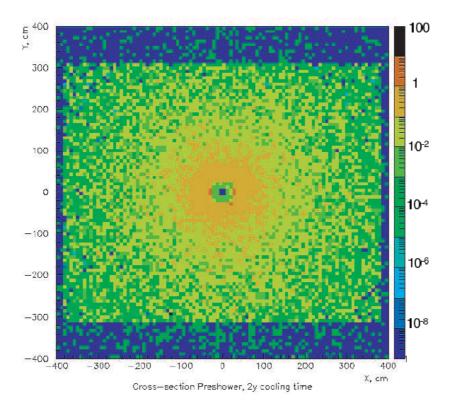

Figure 5 shows the simulations in SPD/PS after 10 years of operation and 2 years of cooling [39].

Figure 5. Relative activity in the SPD-PS lead, averaged over the lead thickness. 10 years of operation and 2 years cooling time.

## 3.1.5. Figures

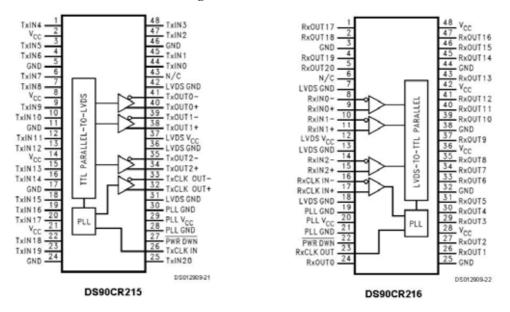

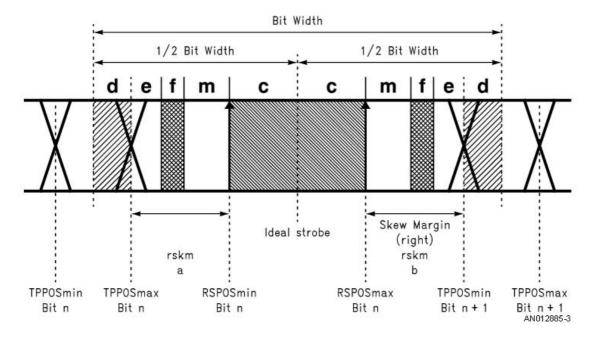

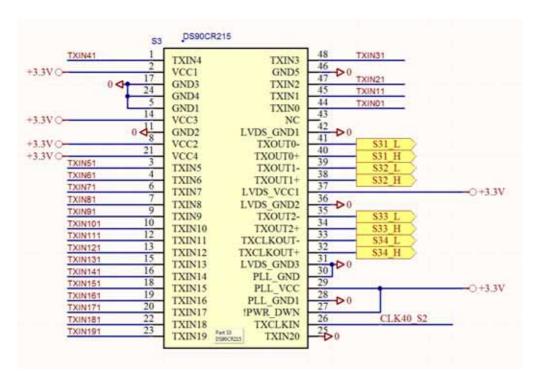

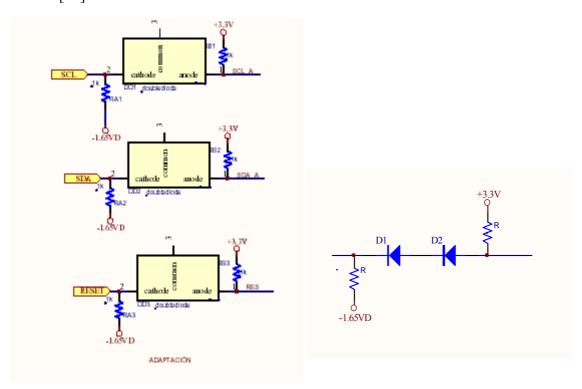

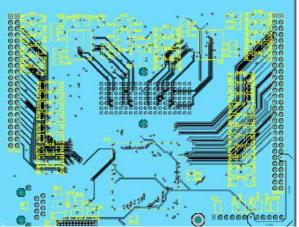

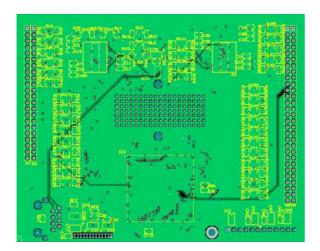

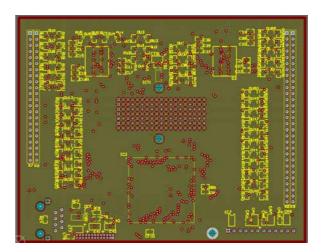

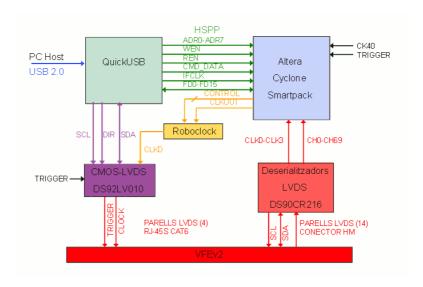

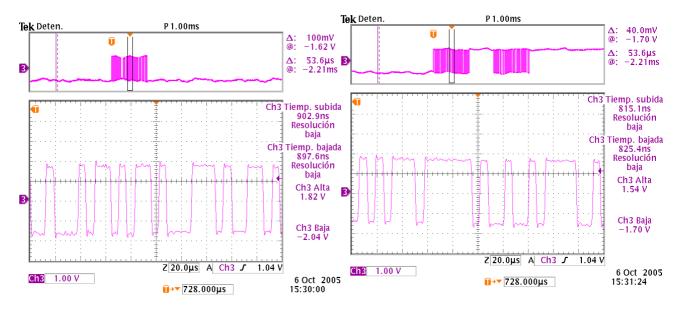

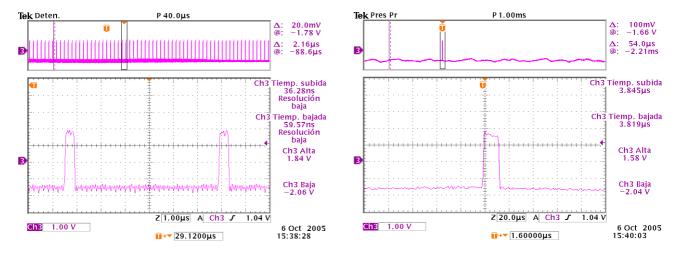

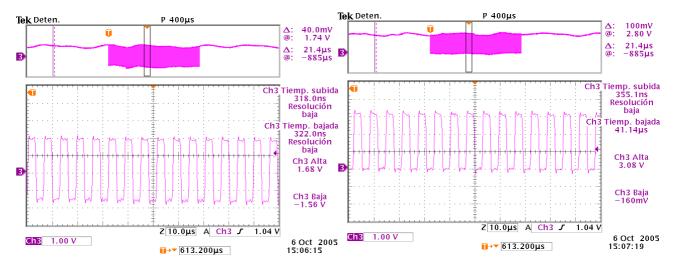

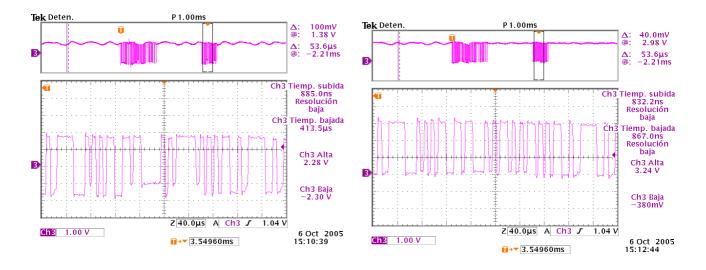

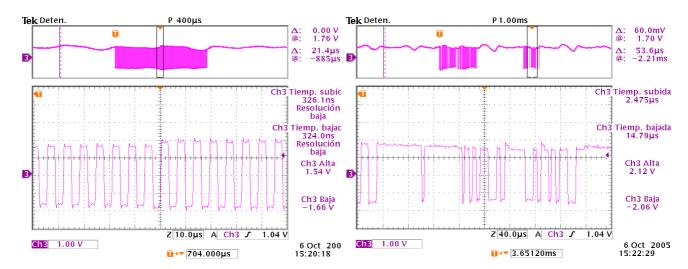

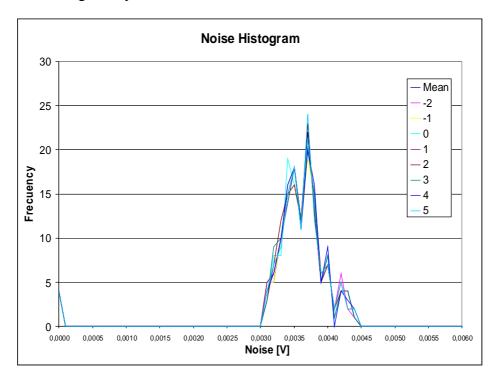

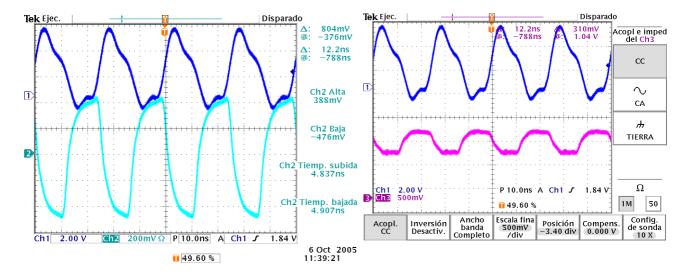

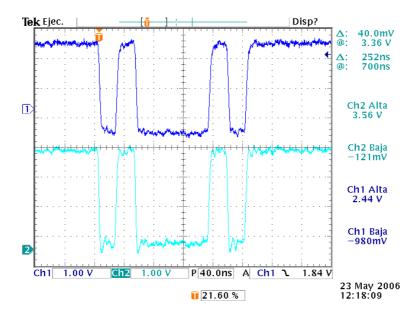

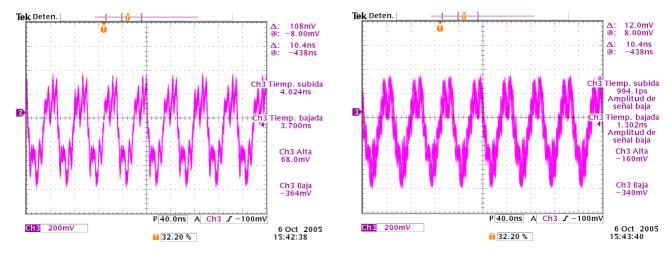

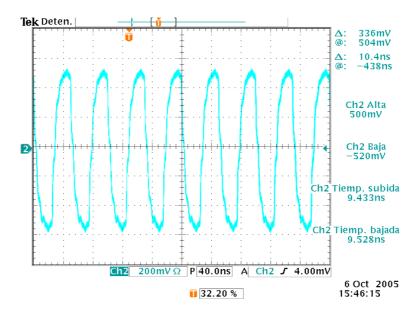

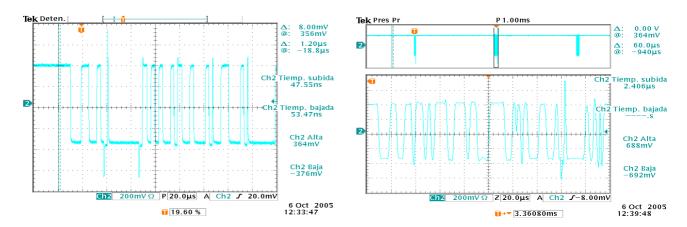

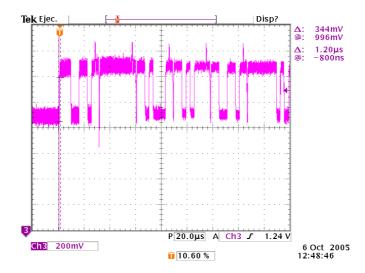

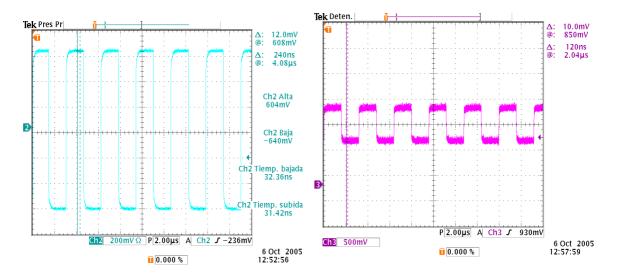

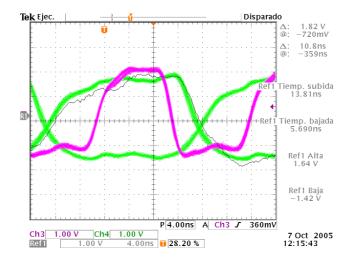

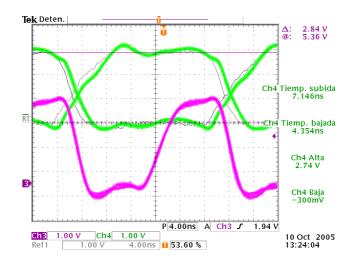

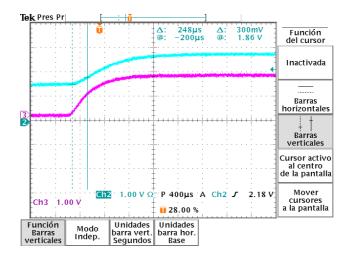

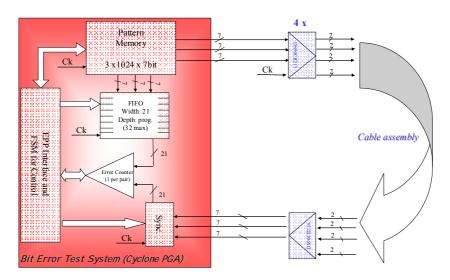

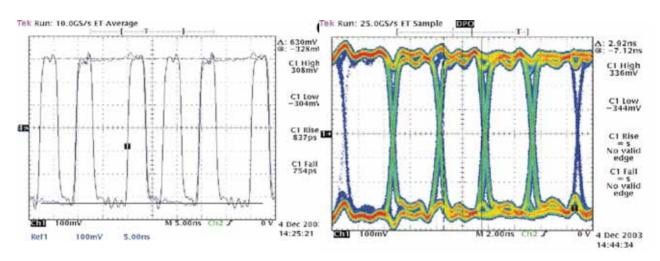

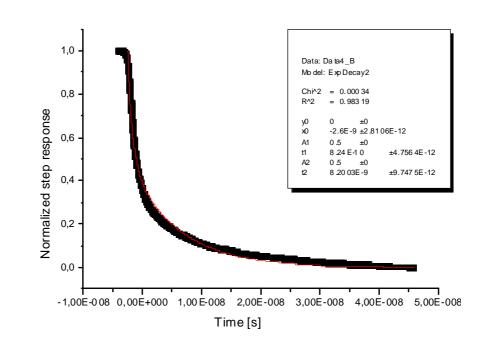

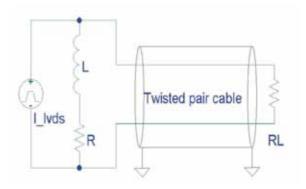

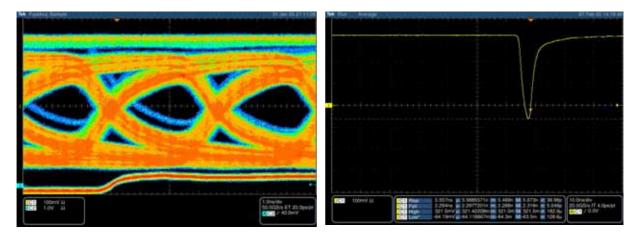

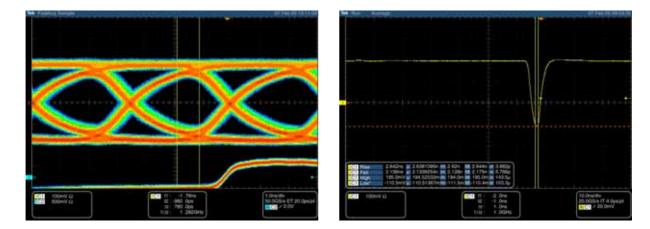

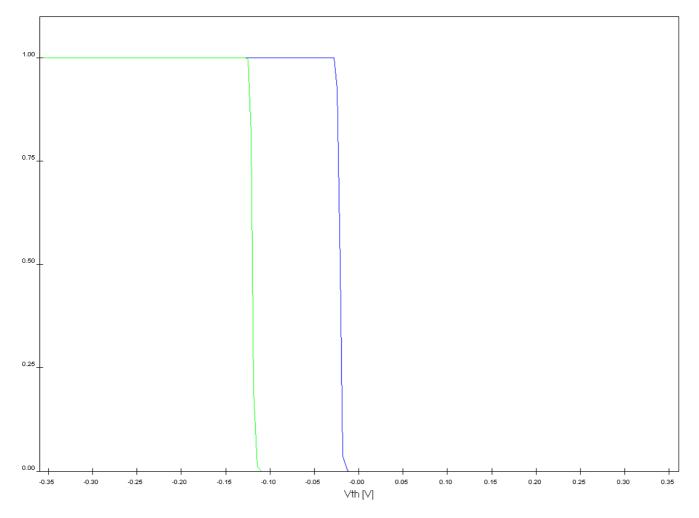

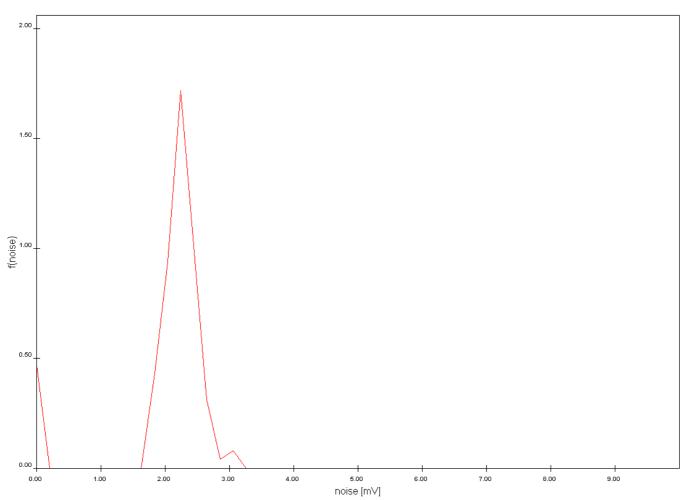

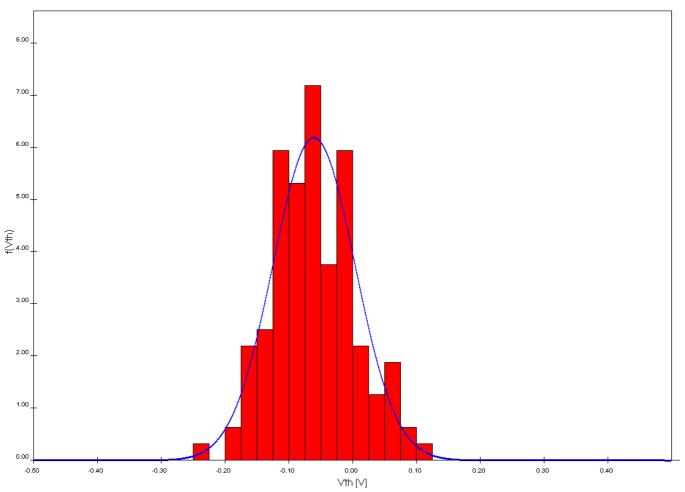

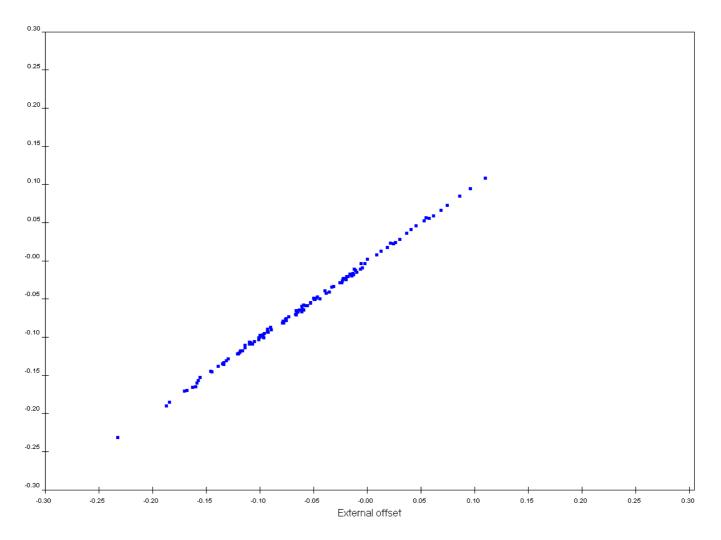

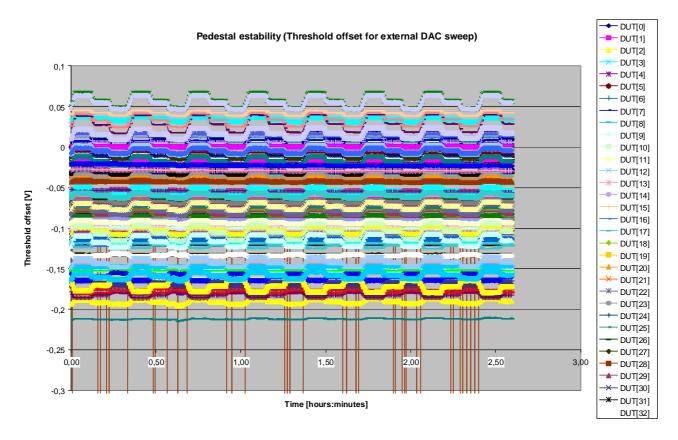

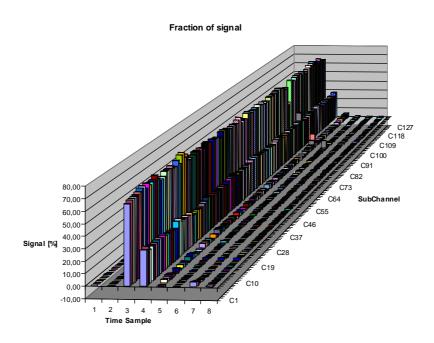

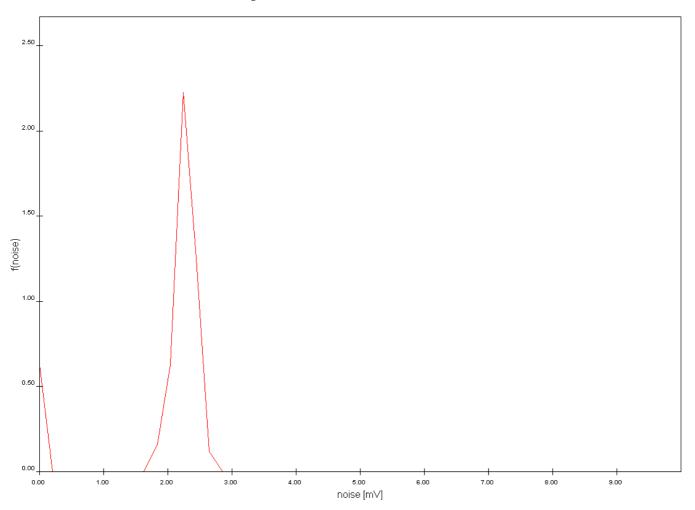

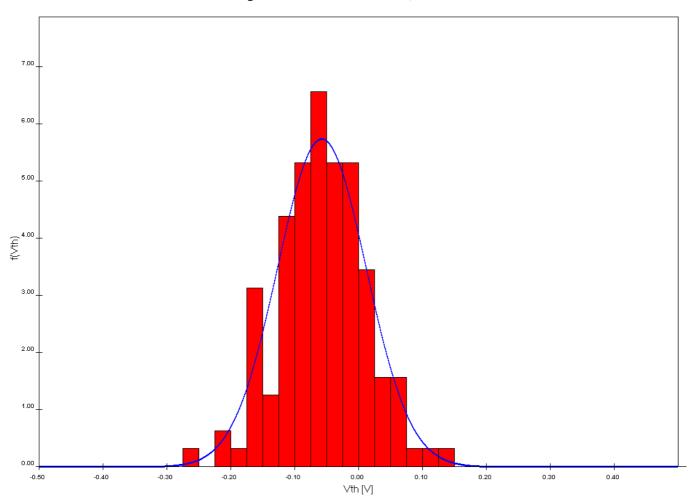

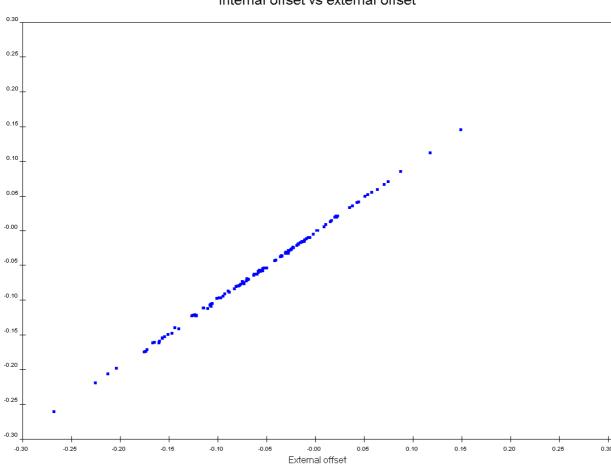

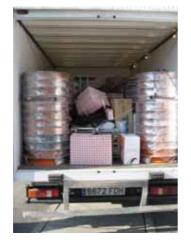

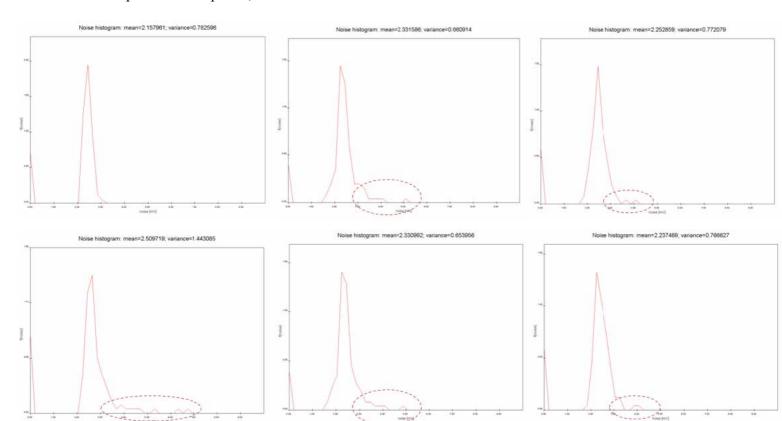

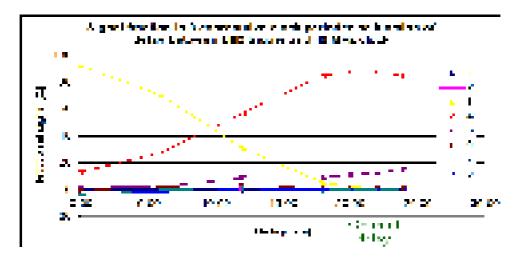

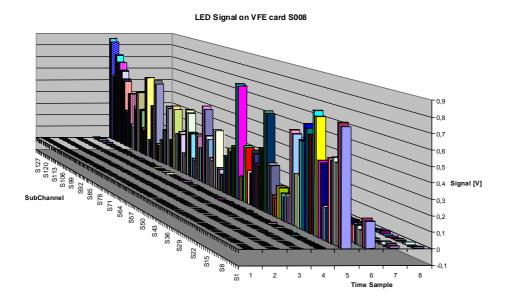

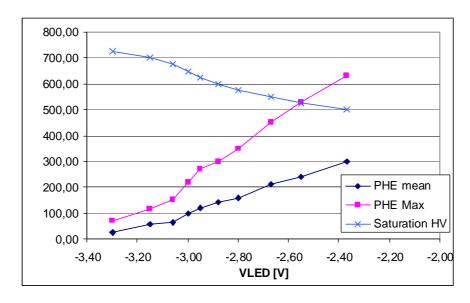

Some figures about radiation in Calorimeter found by simulation, is shown in the Table 1.