2012

Study and Modeling of Multi-Gate Transistors in the Context of CMOS Technology Scaling

Ferney A. Chaves

Departament d'Enginyeria Electrònica Escola d'Enginyeria Universitat Autònoma de Barcelona

#### PH. D. THESIS

# Study and Modeling of Multi-Gate Transistors in the Context of CMOS Technology Scaling

# FERNEY ALVEIRO CHAVES ROMERO 2012

In Partial Fulfillment of the Requirements of the PhD Program in Electronics Engineering for the Degree of Doctor

Universitat Autònoma de Barcelona

Advisors

Dr. David Jiménez Jiménez Dr. Jordi Suñé Tarruella

El Dr. David Jiménez Jiménez, profesor Agregado, y el Dr. Jordi Suñé

Tarruella, Catedrático de Universidad, del Departament d'Enginyeria

Electrònica de la Universitat Autònoma de Barcelona,

**CERTIFICAN**

Que la memoria "Study and Modeling of Multi-Gate Transistors in the

Context of CMOS Technology Scaling" que presenta Ferney Alveiro

Chaves Romero para optar al grado de Doctor en Ingeniería Electrónica,

ha sido realizado bajo su dirección.

Bellaterra, marzo de 2012

Dr. David Jiménez Jiménez

Dr. Jordi Suñé Tarruella

Cuando bordeamos un abismo y la noche es tenebrosa, el jinete sabio suelta las riendas y se entrega al instinto del caballo.

> Armando Palacio Valdés (1853-1938) Literato español

#### Agradecimientos

Después de los muchos esfuerzos que he tenido que realizar para llegar a este punto y así ver culminada una etapa más en mi camino por la académica y la investigación, quiero ante todo agradecer a Dios por sostenerme, darme la sabiduría y el aliento necesario cuando más lo he necesitado. Gracias Señor por no permitirme desfallecer.

Agradezco a mis padres Mary y Alberio y a mis hermanos, quienes siempre han creído en mí y de quienes siempre he recibido apoyo incondicional. A mi hijo Sebastian, quien ha sido testigo viviendo conmigo pacientemente este proceso y quien siempre me ha llenado de fuerza para seguir. A mi Jimena hermosa por su apoyo diario, por la fe que ha tenido en mí y por su compañía durante la culminación de este doctorado. Los amo.

Gracias también a mis amigos, los de Barcelona y los de Colombia, por animarme cuando me sentía cansado y por hacer de mi vida fuera de mi casa algo más placentero.

También un agradecimiento especial a David por sus valiosos aportes, enseñanzas, discusiones, paciencia y sobre todo por su amistad. Así mismo a Jordi por su dirección, apoyo y por la amabilidad que siempre me demostró. Gracias a Andrés y a Fran de la Universidad de Granada por los aportes y la colaboración que siempre estuvieron dispuestos a brindarme.

Finalmente debo agradecer el apoyo del Ministerio Español de Ciencia y Tecnología bajo contrato No. TEC2009-09350 (parcialmente financiado por el programa FEDER de la Unión Europea) y a la financiación por parte de la Generalitat de Catalunya con el programa Distinción de la Generalitat de Catalunya para la promoción de la investigación universitaria, bajo el proyecto S08811001G Nanoelectrónica.

#### **SUMMARY**

The scaling of the conventional MOSFETs has led these devices to the nanoscale to increase both the performance and the number of components per chip. In this process, the so-called "Short Channel Effects" have arisen as a limiting factor. To extend the use of the bulk MOSFETs, the most effective ways of suppressing such effects are the reduction of the gate oxide thickness and increasing of the channel doping concentration. When the gate oxide thickness is reduced to a few atomic layers, quantum mechanical tunneling is responsible of a huge increase in the gate leakage current impairing the normal operation of MOSFETs. This has made mandatory the use of high permittivity materials or high-κ as gate dielectrics.

Despite the proposed solutions, reduction of the physical dimensions of the conventional MOSFETs cannot be maintained. To keep the technological trend, new MOSFET structures have been suggested such as ultra-thin body Multi-Gate MOSFETs. In particular, the Double-Gate MOSFETs is considered as a promising MG structure for its several qualities and advantages in scaling.

This thesis focuses on the modeling of Double-Gate MOSFET and, in particular, on the modeling of the gate leakage current critically affecting the power consumption. First we develop a compact quantum model for both the electrostatic potential and the electric charge in symmetric double-gate MOSFET with undoped thin body. Then, this quantum model is used to propose an analytical compact model for the direct tunnelling current with  ${\rm SiO}_2$  as gate dielectric, firstly, and later assuming a dual layer consisting of a  ${\rm SiO}_2$  interfacial layer and a high- $\kappa$  material.

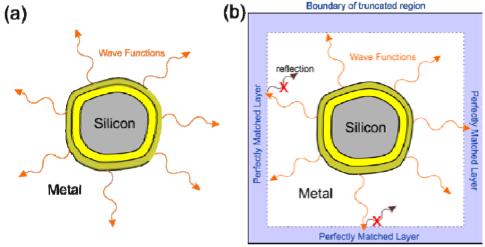

Finally, an accurate method for the calculation of the gate tunnelling current is developed. It is based on Absorbing Boundary Conditions techniques and, more specifically, on the Perfectly Mached Layer (PML) method.

This thesis is motivated by the recommendations given by the "International Technology Roadmap of Semiconductors" (ITRS) about the need for the modeling and simulation of multi-gate semiconductor structures.

#### **RESUM**

L'escalat dels transistors MOSFET convencionals ha portat a aquests dispositius a la nanoescala per incrementar tant les seves prestacions com el nombre de components per xip. En aquest process d'escalat, els coneguts "Short Channel Effects" representen una forta limitació. La forma més efectiva de suprimir aquests efectes i així estendre l'ús del MOSFET convencional, és la reducció del gruix de l'òxid de porta i l'augment de la concentració de dopants al canal. Quan el gruix d'òxid de porta es redueix a unes quantes capes atòmiques, apareix l'efecte túnel mecano-quàntic d'electrons, produint un gran augment en el corrent de fuita, perjudicant la normal operació dels MOSFETs. Això ha fet obligatori l'ús de materials d'alta permitivitat o materials high-κ en els dielèctrics de porta.

Tot i les solucions proposades, la reducció de les dimensiones físiques del MOSFET convencional no pot ser mantinguda de forma indefinida i per mantenir la tendència tecnològica s'han suggerit noves estructures com ara MOSFETs multi-porta de cos ultra-prim. En particular, el MOSFET de doble porta és considerat com una estructura multi-porta prometedora per les seves diverses qualitats i avantatges en l'escalat.

Aquesta tesi s'enfoca en la modelització de dispositius MOSFET de doble porta i, en particular, en la modelització del corrent túnel de porta que afecta críticamente al consum de potència del transistor. Primerament desenvolupem un model quàntic compacte tant per al potencial electrostàtic com per a la càrrega elèctrica en el transistor de doble-porta simètric amb cos no dopat. Després, aquest model quàntic s'utilitza per proposar un model analític compacte per al corrent túnel directe amb SiO<sub>2</sub> com dielèctric de porta, primerament, i després amb una doble capa composta de SiO<sub>2</sub> com a capa interfacial i un material "high-κ". Finalment es desenvolupa un mètode precís per calcular el corrent túnel de porta. El mètode es basa en l'aplicació de condicions de frontera absorbents i, més especificament, en el mètode PML.

Aquesta tesi està motivada per les recomanacions fetes pel "International Technology Roadmap of Semiconductors" (ITRS) sobre la necessitat existent de modelatge i simulació d'estructures semiconductores multi-porta.

### CONTENT

| CHAPTER 1.                                                         | Pa |

|--------------------------------------------------------------------|----|

| Introduction and Background                                        |    |

| 1.1 CMOS Technology Scaling                                        |    |

| 1.2 Double-Gate MOSFET                                             |    |

| 1.3 Thesis Organization.                                           |    |

| CHAPTER 2.                                                         |    |

| Explicit Quantum Potential and Charge Model for Double-gate        |    |

| MOSFETs                                                            |    |

| 2.1 Outline                                                        |    |

| 2.2 Classical Potential Model.                                     |    |

| 2.3 Quantum Potential Model.                                       |    |

| 2.3.1 Maximum Central Potential.                                   |    |

| 2.3.2 The Central Potential                                        |    |

| 2.3.3 The γ parameter                                              |    |

| 2.3.4 The ξ parameter                                              |    |

| 2.4 Quantum Charge Model                                           |    |

| 2.5 Results                                                        |    |

| 2.6 Summary                                                        |    |

| CHAPTER 3.                                                         |    |

| Explicit Model for the Gate Tunneling Current in                   |    |

| Double-Gate MOSFETs                                                |    |

| 3.1 Outline                                                        |    |

| 3.2 Model Development                                              |    |

| 3.3 Results                                                        |    |

| 3.4 Summary                                                        |    |

| CHAPTER 4.                                                         |    |

| Explicit Model for Direct Tunneling Current in Double-Gate MOSFETs |    |

| Through a Dielectric Stack                                         |    |

| 4.1 Outline                                                        |    |

| 4.2 Model Development.                                             |    |

| 4.3 Results.                                                      | 69  |

|-------------------------------------------------------------------|-----|

| 4.4 Summary                                                       | 75  |

| CHAPTER 5.                                                        |     |

| Accurate Calculation of Gate Tunneling Current in Double-Gate and |     |

| Single-Gate SOI MOSFETs Through Gate Dielectric Stacks            |     |

| 5.1 Outline                                                       | 77  |

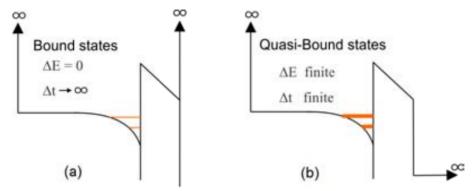

| 5.2 Models for Gate Tunneling Calculation                         | 78  |

| 5.2.1 Closed boundary based method.                               | 80  |

| 5.2.2 Transverse resonant method                                  | 82  |

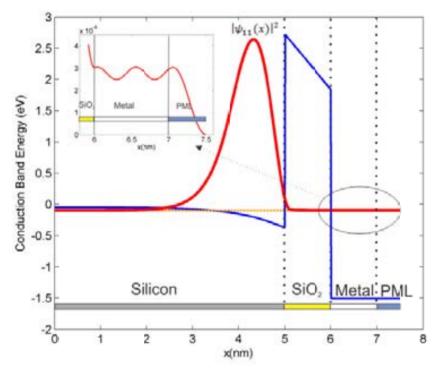

| 5.2.3 Perfectly Matched Layer Method.                             | 83  |

| 5.3 Gate Tunneling Current Using the PML Method                   | 86  |

| 5.4 Summary                                                       | 94  |

| APPENDIX A.                                                       |     |

| Analytical Solution for $\xi$ Parameter                           |     |

| 1. Compose a continuous starting function                         |     |

| as the initial approximation.                                     | 97  |

| 2. Modify the starting function with a high-order correction      | 98  |

| 3. Make another correction to improve accuracy                    | 99  |

| APPENDIX B.                                                       |     |

| Predictor-Corrector Algorithm to Solve SP Equations with PML      | 101 |

| 1. Physical Model                                                 | 102 |

| 2. Approximation of the Quantum Electron Density                  | 103 |

| 3. Schrödinger-Poisson Solution Using a                           |     |

| Predictor-Corrector Approach                                      | 106 |

| CONCLUSIONS                                                       | 109 |

| PUBLICATIONS                                                      | 111 |

| REFERENCES                                                        | 113 |

## **CHAPTER 1.**

# **Introduction and Background**

#### 1.1 CMOS Technology Scaling

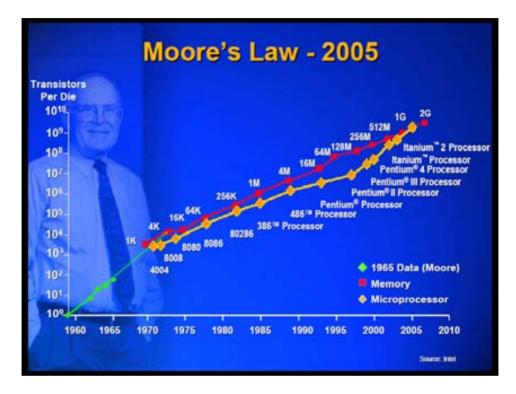

Throughout recent history, silicon-based microelectronics has experienced tremendous growth and performance improvements since the innovative concept of integrated circuit (IC) was invented by J. Kilby in late 1950's [1]. The computational power is enhanced at a tremendous rate with cost reduction, resulting in incredible reduction of cost-per-computation with higher computational performance in data processing and memory functions. In 1965, Gordon Moore made a very famous and important observation: the complexity of ICs approximately doubles every year (Moore later refined the period to two years) [2]. This estimation is the well known "Moore's Law" [3]. Over the past four decades, the scaling of the conventional metal-oxide-semiconductor field-effect transistor (MOSFET) has been accomplished with technology innovations and led the device dimensions well into the nanometer era, allowing a great integration as shown in Figure1-1.

"Scaling" refers to reduction of the lateral geometric dimensions of devices and interconnect. This evolution of process technologies has brought new benefits. However, the performance improvement by scaling the dimension of conventional bulk MOSFET is approaching a limit.

A MOSFET device is considered to be short when the channel length is the same order of magnitude as the depletion-layer widths of the source and drain junction. As the channel length is reduced (scaling) to increase both the operation speed and the number of component per chip, "Short Channel Effects" (SCEs) arise as hurdles. In particular some different SCEs can be distinguished:

threshold voltage roll-off, subthreshold swing degradation, drain-induced barrier lowering (DIBL), surface scattering, velocity saturation, impact ionization and hot electrons.

**Figure 1-1**Moore's Law has delivered exponential increases in the number of transistors integrated into microprocessors and other leading platform ingredients. [Source: Intel Corporation]

In conventional bulk MOSFET technologies, the most effective ways of suppressing SCE are the reduction of the gate oxide thickness ( $T_{ox}$ ) and the increase of the channel doping concentration ( $N_A$ ) [4, 5]. The former is aimed to increase the gate capacitance, thus enhancing the electrostatic control of the gate over the channel. The latter is desired to minimize depletion depths of the source-to-channel and drain-to-channel junctions, preventing the junction electric fields from penetrating too much into the channel and forming an undesired leakage path relatively distant from the gate.

Researchers in [6, 7] have shown that the gate oxide scaling to thicknesses close to a few atomic layers gives rise to quantum mechanical tunneling producing a sharp increase in gate leakage currents. The gate leakage current is the current flowing into the gate of the transistor also called the tunneling current. Other major causes of concern in further reduction of the SiO<sub>2</sub> thickness include increased polysilicon gate depletion and gate dopant penetration into the channel region, which leads to questions regarding dielectric integrity, reliability, and stand-by power consumption. With scaling, gate leakage has increased to undesirable values and will continue to increase at a much higher rate mandating the use of dielectric materials with high electric permittivity or high-κ dielectrics [8]. This allows the actual thickness of the gate dielectric to be increased while still maintaining the same electric field in the channel.

Specifically, the International Technology Roadmap for Semiconductors (ITRS) [9] identifies that for 32nm technology node, gate oxide thickness is nearly to 1nm. The direct tunneling current through the gate oxide of such small thickness may become more of a problem especially in terms of the stand-by power consumption [10]. In addition, abnormal degradation of the drive current has been experimentally observed when the gate oxide thickness is less than 1.3nm [11]. Meanwhile, the channel doping concentration required for SCE control in sub-32 nm bulk MOSFETs is expected to be a few times 10<sup>18</sup> cm<sup>-3</sup> and above [12, 13]. These extremely high doping levels will lead to i) severe degradation of the carrier mobility as the impurity scattering becomes dominant, ii) severe threshold voltage variations because of random microscopic fluctuations of dopant atoms both in numbers and in placement [14, 15], and iii) increased junction band-to-band tunneling current [16]. In view of the fundamental nature of both the gate direct tunneling current and random dopant fluctuations, it becomes problematic to scale bulk MOSFETs much deeper into the sub-32 nm technology regime while preserving good immunity to SCEs.

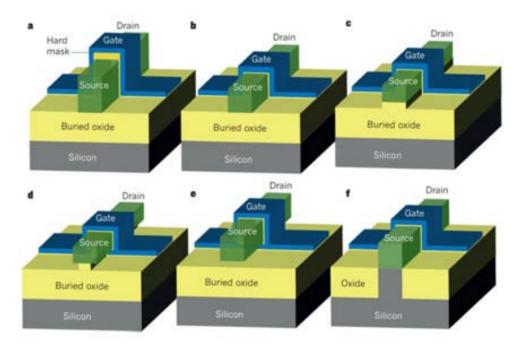

On the other hand, a major portion of semiconductor device production, nowadays, is devoted to digital logic and one key theme is continued scaling of the MOSFETs for leading-edge logic technology in order to maintain historical trends of improved device performance. This scaling is driving the industry toward a number of major technological innovations, including material and process changes such as high- $\kappa$  gate dielectric, metal gate electrodes, strained silicon channels, etc., and in the near future, new structures such as ultra-thin body fully depleted SOI, multi-gate (MG) MOSFETs (Fig. 1-2), such as FinFETs and alternate high-mobility channel materials [17] are expected to be

incorporated. In particular, the Double-Gate MOSFETs is a promising MG structure for its several qualities and advantages in scaling which will be described in the next section. Besides, Double-Gate (DG) MOSFET actually is the central device studied in this thesis.

Figure 1-2

The different ways in which the gate electrode can be wrapped around the channel region of a transistor are shown.  $\bf a$ , A silicon-on-insulator (SOI) fin field-effect transistor (FinFET). The 'hard mask' is a thick dielectric that prevents the formation of an inversion channel at the top of the silicon 'fin'. Gate control is exerted on the channel from the lateral sides of the device.  $\bf b$ , SOI triple-gate (or tri-gate) MOSFET. Gate control is exerted on the channel from three sides of the device (the top, as well as the left and right sides).  $\bf c$ , SOI  $\Pi$ -gate MOSFET. Gate control is improved over the tri-gate MOSFET shown in  $\bf b$  because the electric field from the lateral sides of the gate exerts some control on the bottom side of the channel.  $\bf d$ , SOI  $\Omega$ -gate MOSFET. Gate control of the bottom of the channel region is better than in the SOI  $\Pi$ -gate MOSFET. The names  $\Pi$  gate and  $\Omega$  gate reflect the shape of the gates.  $\bf e$ , SOI gate-all-around MOSFET. Gate control is exerted on the channel from all four sides of the device.  $\bf f$ , A bulk tri-gate MOSFET. Gate control is exerted on the channel from three sides of the device (the top, the left and the right). In this case, there is no buried oxide underneath the device. Ref. [17].

Implementation of fully depleted SOI and multi-gate will be challenging. Since such devices will typically have lightly doped channels, the threshold voltage will not be controlled by the channel doping. The problems associated

with high channel doping and stochastic dopant variation in planar bulk MOSFETs will be alleviated, but numerous new challenges are expected. These innovations are expected to be introduced at a rapid pace, and hence understanding, modeling, and implementing them into manufacturing in a timely manner is expected to be a major issue for the industry [9].

For the long-term, when the transistor gate length is projected to scale below 10 nm and body (fin) thicknesses below 5 nm, the impact of quantum confinement effects on such thin devices should be well understood.

The numerical modeling and simulation of semiconductor structures by computer is a useful resource for the study and understanding of several electronic phenomena, of which would otherwise have an incomplete knowledge. In fact, in most cases, the simulated devices are ahead of the current technology. Computer simulation allows, in a fast way, to explore new geometries and sizes that could be manufactured in the future.

Modeling and simulation in semiconductor technology is one of the few enabling methodologies that can reduce development cycle times and cost. One of the topical areas of Modeling and Simulation of the ITRS is the Device Modeling which presents as a difficult challenge the nanoscale devices simulation capability: methods, models and algorithms. In particular it is necessary modeling for gate stacks with ultra-thin/high-κ dielectrics for several channel materials with respect to electrical permittivity, built-in charge, influence on workfunction by interface interaction with metals, reliability, carrier transport and tunneling currents. As mentioned before, gate dielectrics have become so thin that tunneling gate current is today an important design factor. Therefore, a comprehensive quantum modeling of the entire gate stack (channel, dielectric and electrode) is needed to represent the behavior of oxides that are only a few atomic layers thick. Since the adoption of high-k dielectrics and metals, details of tunneling and charge transport in the dielectric, effective dielectric constant of complex dielectric stacks, interfaces states and dipoles, and charge and trap distribution in high-k materials must be included urgently. Simulations must also be applicable beyond standard planar CMOS.

#### 1.2 Double-Gate MOSFET

DG CMOS offers distinct advantages for scaling to very short gate lengths. Furthermore, adoption of gate dielectrics with permittivity substantially greater than that of SiO<sub>2</sub> (high-κ materials) may be deferred if a DG architecture is employed. Recently, through use of delta devices, now commonly referred to as the FinFET [18], significant advantages in DG device technology and performance have been demonstrated. Fabrication of FinFET is very close to that conventional CMOS process, with only minor disruptions, offering the potential for a rapid deployment to manufacturing. Planar products designs have been converted to FinFET without disruption to the physical area, thereby demonstrating its compatibility with today's planar CMOS design methodology and automation techniques [19].

CMOS technology scaling has traversed many anticipate barriers over the past two decades to rapidly progress from 2µm to sub 100nm rules, as discussed in the article by Chuang et.al. [20]. Two obstacles, namely subthreshold and gate dielectric leakage become the dominant barrier for further CMOS scaling, even for highly leakage-tolerant applications such as microprocessors.

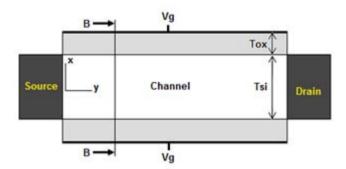

DG MOSFET is composed of a thin silicon body sandwiched between the gate dielectrics and contacts as Figure 1-3 shows. We will consider that the two gates of the DG device are shorted giving rise to numerous advantages, such as greater control of the gate over the channel thereby reducing SCEs [21, 22]. Such SCE limit the minimum channel length at which a FET is electrically well behaved. Unlike bulk MOSFETs which require very high channel doping (~10<sup>18</sup>/cm³ for sub-100nm devices), thin body DG MOSFETs show good short-channel behavior even with undoped silicon as a channel.

As the channel length of a bulk MOSFET is reduced, the drain potential begins to strongly influence the channel potential, leading to an inability to shut off the channel current with the gate. This SCE is mitigated by use of thin gate oxide (to increase the influence of the gate on the channel) and thin depletion depth below the channel to the substrate, to shield the channel from the drain. Gate oxide thickness has been reduced to the point where, at sub-100 nm CMOS, the power drain from gate leakage is comparable to the power used for switching of circuits. Thus, further reduction of the thickness would lead to unreasonable power increases. Alternatively, further decrease of the depletion

region degrades gate influence on the channel and leads to a slower turn on of the channel region.

Figure 1-3

Cross section scheme of the symmetrical DG MOSFET considered in this work.

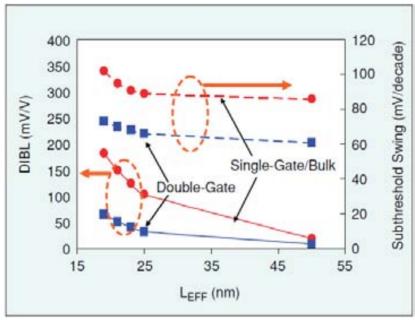

In DGs, the longitudinal electric field generated by the drain is better screened from the source end of the channel due to proximity to the channel of the second gate, resulting in reduced SCE such as the DIBL and improved subthreshold swing (S). Therefore, as CMOS scaling becomes limited by leakage currents, DG offers the opportunity to proceed beyond the performance of single-gate (SG) bulk-silicon. Figure 1-4 shows MEDICI-predicted DIBL and subthreshold swing for bulk silicon and (symmetrical) DG devices as a function of the effective channel length  $L_{eff}$ . Both the DIBL and subthreshold swing for the DG device are dramatically improved relative to those of the bulk-silicon counterpart [19].

From a bulk-silicon device design perspective, increased body doping concentration could be employed to reduce DIBL; however, at some point it would also increase the subthreshold swing, thereby requiring higher threshold voltage to keep the subthreshold current adequately low. Similarly, decreasing the body doping concentration could improve the subthreshold swing but degrade DIBL. Hence a compromise is necessary for the bulk-silicon device design. Note that, for a scaled bulk-silicon device, a highly doped channel must be used to control severe SCEs, and lower S for extremely short  $L_{eff}$  could not be achieved by use of low channel doping.

**Figure 1-4** MEDICI-predicted DIBL and subthreshold swing versus effective channel length for DG and bulk-silicon nFETs. The DG device is designed with an undoped body and a near-mid-gap gate material [19].

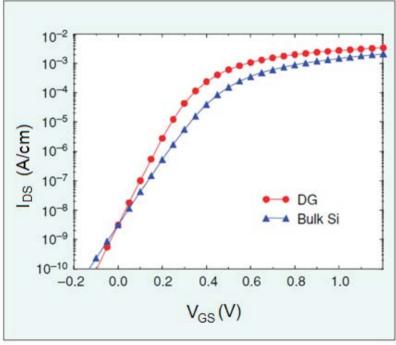

In Figure1-5 simulations of the drain current  $I_{DS}$  of DG and SG MOSFETs shows the steeper turn on of the DG, which results from the gate coupling advantage previously discussed. This property enables the use of lower threshold voltage for the DG for a given off-current. As a direct result, higher drive currents at lower power-supply voltages  $V_{DD}$  are attainable.

#### 1.3 Thesis Organization

This thesis is organized in the following way: in Chapter 2 a compact quantum model for both the electrostatic potential and electric charge in thin-film symmetric double-gate MOSFET is presented. This is done from a classical model proposed by Taur [23]. That quantum model is used in Chapter 3 to propose an analytical compact model for the gate tunnelling current with silicon dioxide as a gate dielectric, relying on a quadratic approximation to the

conduction band profile and the well-known WKB approximation to the transmission probability. The Chapter 4 is devoted to extend the compact model presented in Chapter 3 to take account a dielectric stack consisting of a  $SiO_2$  interfacial layer and a high permittivity dielectric material (high- $\kappa$ ). Up to this point the electronic states are considered fully bounded, namely, wave function penetration is not allowed into the gate dielectrics. Finally and thinking in future research for applied to other MG transistors such as cylindrical gate or quadruple gate, an accurate method for the calculation of the gate tunnelling in DG MOSFETs is studied and developed in Chapter 5, which is based on Absorbing Boundary Conditions techniques and, more specifically, on the Perfectly Mached Layer (PML) method.

Figure 1-5 Simulation of DG and single-gate FETs, designed for equal subthreshold current density at  $V_{GS} = 0 \text{ V}$ , illustrates the gain in drive current from improved channel control of the DG FET. Both gates contribute to control of the channel potential in subthreshold, while in the bulk case the gate must compete with the influence of the substrate [19].

#### CHAPTER 2.

# Explicit Quantum Potential and Charge Model for Double-gate MOSFETs

#### 2.1 Outline

In this chapter, a compact quantum model for both the electrostatic potential and electric charge in thin-film symmetric double-gate MOSFET with undoped body is presented. As a novelty, both the resulting potential and charge have explicit expressions on bias and geometrical parameters. A comparison has been made between self-consistent numerical solutions of Schrödinger-Poisson equations and our model results with close agreement. Finally, the range of validity of the presented model is discussed.

MULTI-GATE metal-oxide-semiconductor field-effect transistors (MOSFETs), and in particular, DG MOSFETs, are a topic of intense interest in order to improve the performance of complementary metal-oxide-semiconductor (CMOS) devices [24]. Theoretically, DG MOSFETs can be scaled to significantly shorter channel length than bulk MOSFETs for a given oxide thickness [25] keeping a better control of short channel effects (SCE). Because of such advantage, these devices are potential candidates as building blocks for nanoscale circuits in the midterm, thus making the development of computer-aided-design (CAD) compatible models an important issue. When the gate

length is scaled below deep submicron dimensions very large normal electric fields at the Si/SiO<sub>2</sub> interface may appear. Therefore a significant bending of the energy bands at the Si/SiO<sub>2</sub> interface is produced and the potential well becomes narrow enough to quantize the motion of inversion layer carriers in the direction perpendicular to the interface [26]. Due to the quantization, the energy levels are splitted into subbands and the lowest of the allowed energy levels for electrons in the well does not coincide with the bottom of the conduction band. On the other hand, the electron density does not reach its maximum at the Si/SiO<sub>2</sub> interface as semiclassical theory predicts [27, 28], but at some distance inside the semiconductor. Thus, a reliable compact model for DG MOSFETs must take into account quantum effects. Several works have been devoted to model the electrostatic features of DG-MOSFETs, which can be categorized as: i) models relying on a purely classical description [23] and [29-31], which do not treat QM effects, ii) 1D and 2D self-consistent models which numerically solve the coupled Schrödinger and Poisson equations [32-34], ideal for quantitative understanding of the physics behind, but not suitable for compact modeling; iii) models using a perturbation theory -even in strong inversion region-, for which the structural confinement is taken into account, but which are not suitable to deal with the strong field dependence [35, 36]; and iv) models based on a quantum-mechanical variational approach [37], where the potential depends on the inversion charge density, and thus requires the solution of an implicit equation.

In this chapter, we extend the state-of-the-art by proposing a simple model for the electrostatics of undoped DG-MOSFETs, which reproduces the results obtained from accurate self-consistent quantum-mechanical (QM) solutions, showing an explicit dependence with the gate voltage and geometrical parameters, thus making it suitable for compact modeling.

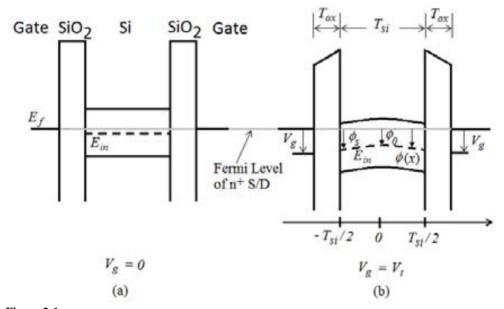

#### 2.2 Classical Potential Model

This section shows the main features of a classical model for the potential and charge of the DG-MOSFET developed by Taur [6]. Figure 2-1 illustrates the geometric parameters such as the silicon thickness  $T_{si}$  and SiO<sub>2</sub> dielectric thickness  $T_{ox}$  and the schematic band diagrams of the device. Same voltage is applied to the two gates having the same work function. At zero gate voltage  $V_g$ , the position of the silicon bands is largely determined by the gate work function.

This is because as long as the thin silicon is lightly-doped and the depletion charge is negligible, the bands remain essentially flat throughout the thickness of the film. Since there is no contact to the silicon body, the energy levels are referenced to the electron quasi-Fermi level or the conduction band of the n+source—drain (not shown), represented by the long dotted line in Figure 2-1. As the gate voltage increases toward the threshold voltage in Figure 2-1b, mobile charge or electron density becomes appreciable and the conduction band of the silicon body moves toward the conduction band of the source-drain. The silicon bands will just float to the position dictated by the gate work function.

Figure 2-1

Schematic band diagrams of a symmetric, undoped double-gate nMOSFET. At zero gate voltage (a), the silicon bands are flat for the gate work function (slightly toward n than the midgap work function) shown in the example. Near the threshold voltage (b), the conduction band of the silicon body at the surface is bent to near the conduction band of the n source-drain (long dotted line).

By defining the coordinates and potential as in Figure 2-1, one can write Poisson's equation for the silicon region with only the mobile charge (electron) density as

$$\frac{d^2\phi}{dx^2} = \frac{q}{\epsilon_{Si}} n_i e^{\phi/V_T} \tag{2.1}$$

where q is the electronic charge,  $\epsilon_{si}$  is the permittivity of the silicon,  $n_i$  is the intrinsic carrier density,  $V_T = k_B T/q$  is the thermal voltage with the Boltzmann's constant  $k_B$  and the absolute temperature T. Here, we consider an nMOSFET with  $\phi/V_T \gg 1$  so that the hole density is negligible.

Using the symmetry boundary condition  $d\phi/dx|_{x=0} = 0$  and integrating (2.1) twice, the electrostatic potential can be expressed as

$$\phi(x) = \phi_0 - 2V_T ln \left[ cos \left( \sqrt{\frac{qn_i}{2\epsilon_{si}V_T}} e^{\phi_0/2V_T} x \right) \right]$$

(2.2)

valid for the entire range  $-T_{si}/2 \le x \le T_{si}/2$  and where all the potentials are referenced to the source Fermi level. Here,  $\phi_0 \equiv \phi(x=0)$  is the potential at the center of the silicon film, to be solved later as a function of  $V_g$ .

The surface potential  $\phi_s \equiv \phi(x = T_{si}/2)$  is then given by

$$\phi_s = \phi_0 - 2V_T ln \left[ cos \left( \sqrt{\frac{qn_i}{2\epsilon_{si}V_T}} e^{\phi_0/2V_T} \frac{T_{si}}{2} \right) \right]$$

(2.3)

and it is also related to  $V_g$  and  $T_{ox}$  through the boundary condition at the Si/SiO<sub>2</sub> interface:

$$V_{g} - \Delta \varphi - \phi_{s} = \frac{\epsilon_{si}}{\epsilon_{ox}} T_{ox} \frac{d\phi}{dx} \Big|_{x = \frac{T_{si}}{2}} = \frac{T_{ox}}{\epsilon_{ox}} \sqrt{2\epsilon_{si}kTn_{i}(e^{\phi_{s}/V_{T}} - e^{\phi_{0}/V_{T}})}$$

(2.4)

Here  $\Delta \varphi$  is the work function difference between the gate electrode and intrinsic silicon. Given  $V_g$ , Eqs. (2.3) and (2.4) are coupled equations that can be solved for  $\phi_s$  and  $\phi_0$ .

The sheet density of mobile charge can be obtained from the Gauss's law and  $Q_{ch} = 2\epsilon_{si}(d\phi/dx)_{x=t_{si}/2}$  (the factor of two arises from the two surfaces).

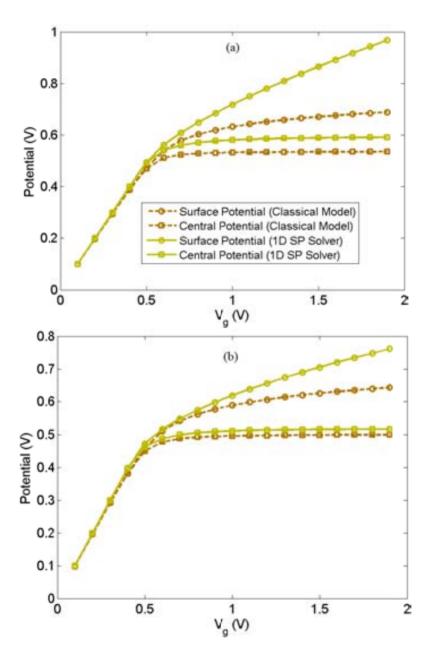

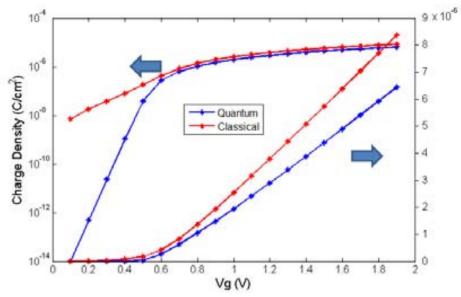

Although this is a simple physics-based model for DG, it requires numerical calculations, Newton-Raphson type, to solve the highly nonlinear Eq. (2.4). On the other hand, quantum corrections should arise when very thin Si-film is considered. For instance, Figure 2-2 shows, for two different geometries, the

Figure 2-2 Comparison between classical [6] and quantum [38] models of the potentials in DG MOSFETs for (a)  $T_{si} = 5$ nm,  $T_{ox} = 1$ nm; (b)  $T_{si} = 1$ 0nm,  $T_{ox} = 3$ nm.

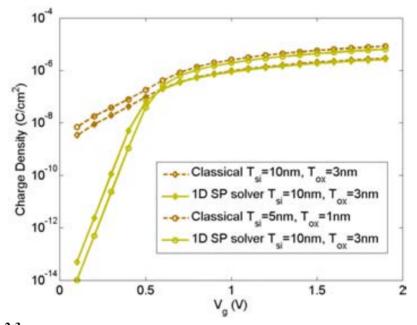

differences between the potentials (surface and central) when these are calculated using the classical model described in this section and when those are calculate by means of a self-consistent 1D Schrödinger-Poisson (SP) solver [38]. Also, Figure 2-3 shows those differences to the mobile charge density  $Q_{ch}$  as a function of  $V_g$ . Clearly, the differences correspond to the quantization or discretization of electronic states and to the decreasing of the density of states (DOS). In next section we propose a simple compact model for the potentials and charge which takes into account the quantum effects present in DG MOSFETs.

**Figure 2-3**Comparison between classical [6] and quantum [38] models of mobile charge density in DG MOSFETs.

#### 2.3 Quantum Potential Model

Our model takes the classical potential described in previous section as a starting point. The potential given by Eq. (2.2) is obtained by solving the Poisson equation (Eq. (2.1)) in the silicon region with only the classical mobile charge (electrons) density.

Since the angle of the cosine function in Eq. (2.2) cannot exceed  $\pi/2$ , the central potential  $\phi_0$  is pinned to an upper bound of  $\phi_{0max} = V_T ln \left(\frac{2\pi^2 V_T \varepsilon_{si}}{T_{si}^2 q n_i}\right)$  which gives the saturation values of  $\phi_0$  in Figure 2-2 and it is the maximum value that the central potential reaches by increasing the gate voltage. Using this saturation value for  $\phi_0$ , the classical potential  $\phi$  of the Eq. (2.2) can be rewritten as follow without loss of generality [23]:

$$\phi(x) = \phi_0 - 2V_T \ln \left[ \cos \left( \frac{\pi}{T_{ci}} e^{(\phi_0 - \phi_{0max})/2V_T} x \right) \right]$$

(2.5)

Now, in order to correct the classical potential we must add QM effects, relevant at the nanoscale. We will do it introducing two additional parameters  $\xi$  and  $\gamma$  together with a  $\phi_{0max}$  modified parameter in Eq. (2.6) to allow the fitting of the self-consistent QM numerical solution:

$$\phi(x) = \phi_0 - \frac{2V_T}{\gamma} ln \left[ cos \left( \frac{\pi \xi}{T_{si}} e^{(\phi_0 - \phi_{0max})/2V_T} x \right) \right]$$

(2.6)

We can justify the introduction of two parameters because quantum effects modify both the charge density and its spatial distribution. The main idea and the simplicity of our model are based on finding compact expressions for the parameters  $\phi_{0max}$ ,  $\phi_0$ ,  $\gamma$  and  $\xi$ , as we will show.

#### 2.3.1 Maximum central potential $\phi_{0max}$ :

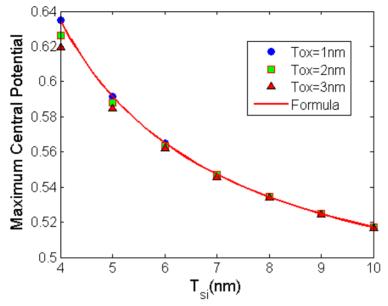

For the QM case, the maximum central potential is larger than in the classical case due to the decrease of the charge density. Figure 2-4 shows the dependence of the maximum central potential with the silicon thickness  $T_{si}$  for  $T_{ox} = 1, 2$  and 3 nm, which were obtained from simulations using a 1D self-consistent simulator [38]. Based on these simulations, a semi-empirical formula can be obtained with a goodness of fit statistics given by R = 1, using a square of correlation (R-square) metrics:

$$\phi_{0max} = (aT_{si} + b)/(T_{si} + c), \tag{2.7}$$

with the values a = 0.4555 (0.4535, 0.4574) V, b = 0.1755 (0.1156, 0.2358)nm-V and c = -0.8525 (-0.9366, -0.7683) nm, where the numbers inside the parenthesis correspond to the confidence bounds. Note that  $T_{ox}$  does

not explicitly appear in Eq. (2.7) because  $\phi_{0max}$  exhibits a very weak dependence on  $T_{ox}$  for  $T_{si} \ge 4$ nm.

**Figure 2-4** Maximum central potentials for  $T_{ox} = 1,2$  and 3 nm versus the silicon thickness  $T_{si}$ . Data are taken from 1D self-consistent simulator. Solid line corresponds to Eq. (2.7).

The sensitivity of final results respect to small variations on  $\phi_{0max}$  is shown in the Figure 2-12.

#### 2.3.2 The central potential $\phi_0$

The Central potential is calculated using the approach of Ortiz [39], which to portray the behavior of  $\phi_0$  as a function of gate voltage uses the following smoothing function, similar to one previously used to model drain saturation voltage [40]:

$$\phi_0 = U - \sqrt{U^2 - (V_g - V_{fb})\phi_{0max}}$$

(2.8)

$$U = \frac{1}{2} \left[ \left( V_g - V_{fb} \right) + (1 + r) \phi_{0max} \right]$$

(2.9)

Here  $V_g$  is the voltage applied to both gates,  $V_{fb}$  is the flat band voltage and r is a smoothing parameter weakly dependent on  $T_{ox}$  and  $T_{si}$ , which may be also determined from [39]

$$r = (AT_{ox} + B)(C/T_{si} + D)$$

(2.10)

where the constants  $A = 0.0267 \text{ nm}^{-1}$ , B = 0.0270, C = 0.4526 nm and D = 0.0650 are appropriate values for oxide thicknesses below 5nm and film channel thicker than 4nm.

#### 2.3.3 The $\gamma$ parameter

We have mentioned that the charge density and potential profile are modified by the QM effects. We can model the change on the potential profile by means of the  $\gamma$  parameter, which is also obtained from the analysis of 1D self-consistent simulation, and is nicely modeled by the expression:

$$\gamma = \left[\frac{k}{(T_{si} + a_o)^2} + l\right] * G(T_{si}, T_{ox})$$

(2.11)

$$G(T_{si}, T_{ox}) = \left(1 + exp\left(\frac{f(T_{ox}) - T_{si}}{a_1}\right)\right)^{-1} + G_0,$$

(2.12)

with

$$f(T_{ox}) = (f_1 + f_2)/2 + |f_1 - f_2|/2,$$

(2.13)

$$f_2 = 2T_{ox} + f_2^0 (2.14)$$

where the combination  $k=-5.9\,\mathrm{nm}^2$ ,  $a_0=0.078\,\mathrm{nm}$ , l=0.23,  $a_1=0.1\,\mathrm{nm}$ ,  $G_0=10^{-4}$ ,  $f_1=5.5\,\mathrm{nm}$ ,  $f_2^0=1.5\,\mathrm{nm}$  yields pretty nice results. Factor G depends strongly on the ratio  $2T_{ox}/T_{si}$  which is closed related to the structural parameter m defined as  $m=2\epsilon_{si}T_{ox}/\epsilon_{ox}T_{si}$ . For values of  $T_{si}$  where the two inverted channels of the DG do not overlap, the  $\gamma$  parameter has two different regimes closely related to m. If  $T_{si}/2T_{ox} \gtrsim 1$  then  $\gamma \cong k/(T_{si}+a_o)^2+l$ , otherwise  $\gamma \cong G_0$ . When the two inverted channels overlap, i.e for values of  $T_{si} \lesssim 5\,\mathrm{nm}$  and  $\forall T_{ox}$ ,  $\gamma \cong G_0$ , reflecting a greater effect of structural parameter on the electrostatics of the DG.

#### 2.3.4 The $\xi$ parameter

The  $\xi$  parameter must be obtained after applying the boundary condition at the Si/SiO<sub>2</sub> interface:

$$V_g = V_{fb} + \phi_s + \frac{\epsilon_{si}}{\epsilon_{ox}} T_{ox} \frac{d\phi}{dx} \Big|_{x = T_{si}/2},$$

(2.15)

where  $\phi_s = \phi(x = T_{si}/2)$  corresponds to the surface potential. By using Eq. (2.6), introducing the change of variable  $\beta = \xi \frac{\pi}{2} e^{(\phi_0 - \phi_{0max})/2V_T}$ , and after a simple algebraic manipulation, Eq. (2.15) can be written as:

$$f(\beta) = \ln(\cos(\beta)) - m\beta \tan(\beta) + F = 0. \tag{2.16}$$

Here m is the structural parameter, and  $F = \gamma/2V_T * (V_g - V_{fb} - \phi_0)$ . Given a gate voltage  $V_g$ , Eq. (2.16) cannot be analytically solved for  $\beta$ , and numerical or table look-up methods are required. To overcome this limitation, we can adopt a three step-method to find out  $\beta$  in a closed and accurate manner (see Appendix A for details) [41]. Finally, substitution of the explicit expressions for  $\phi_0$ ,  $\phi_{omax}$ ,  $\gamma$  and  $\xi$  into Eq. (2.6) provide a compact model for the electrostatic potential and charge including QM effects.

# 2.4 Quantum Charge Model

An analytic and continuous expression of the quantum electric charge associated with the gate is desirable in circuit simulation to know, for example, the gate tunneling current or capacitance to compute the AC and transient behavior.

Due to the confinement of electron motion normal to the  $Si/SiO_2$  interface, the conduction band within the transistor channel is split in several subbands, each of which is associated with the corresponding energy eigenvalue. The channel charge per unit area may be expressed as

$$Q_{ch} = q \sum_{i=1,2} \sum_{j} N_{i} log \left[ 1 + e^{(E_{f} - E_{ij})/kT} \right]$$

(2.17)

where i and j are subscripts for valleys and subbands respectively,  $N_i$  is the density of states in the subband at energy  $E_{ij}$ . For silicon <100> cristal orientation, two groups of conduction subbands, with degeneracy factor  $g_1 = 2$  and  $g_2 = 4$ , corresponding to the six distinct ellipsoidal constant energy surfaces, are considered for the computation of the density of states:

$$N_i = \frac{g_i m_{di}^* kT}{\pi \hbar^2} \tag{2.18}$$

where  $m_{d1}^* = m_t, m_{d2}^* = \sqrt{m_l m_t}$  are the density-of-states effective masses for the low and high energy valleys respectively with  $m_l = 0.92 m_0$  and  $m_t = 0.19 m_0$  corresponding to the longitudinal and transversal masses.

It is difficult to find an analytic expression for the subband energies  $E_{ij}$  for all possible gate voltages. To circumvent this problem we can take advantage of the asymptotic behavior of  $Q(V_g)$ . Specifically, for  $V_g \lesssim V_{th}$  (where  $V_{th}$  refers to the threshold voltage), the electronic states in a box-like potential well with an infinite barrier height are a very good approximation. On the other hand, for  $V_g \gtrsim V_{th}$ , Eq. (2.15) provides a simple relation, through the oxide voltage, between the channel charge and surface potential. Hence, we can write the following expressions accounting for the asymptotic behavior at low and high gate voltages, respectively:

$$Q^{<} = q \sum_{i=1,2} \sum_{j} N_{i} log \left[ 1 + e^{(E_{f} - E_{ij}^{0})/kT} \right] \quad \text{for} \quad V_{a} \lesssim V_{th} \quad (2.19)$$

and

$$Q^{>} = \frac{2\epsilon_{ox}}{T_{ox}} \left( V_g - V_{fb} - \phi_s \right) \text{ for } V_g \gtrsim V_{th}$$

(2.20)

where

$$E_{ij}^0 = \frac{\hbar^2}{2m_{zi}} \left(\frac{j\pi}{T_{si}}\right)^2 + \frac{E_g}{2} - q\phi_s$$

.

The factor two in Eq. (2.20) takes into account the contribution to the charge from the two gates, and  $m_{zi}$  refers to the confinement mass for valley  $i^{th}$ , so  $m_{z1} = m_l$ ,  $m_{z2} = m_t$ .

Similarly to one previous model used to calculate the drain saturation voltage [40], based on a hyperbolic smoothing function with asymptotic

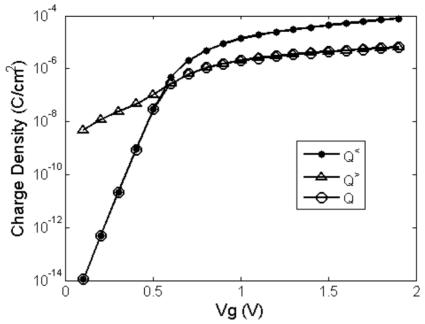

Figure 2-5 Charge density for  $T_{si} = 5$ nm and  $T_{ox} = 1$ nm. Solid lines are data from 1D simulator and symbols corresponds to our model data.

behavior to  $Q^{<}$  and  $Q^{>}$ , the charge density can be composed using the expression

$$Q = Q_m - \sqrt{{Q_m}^2 - Q^{<}Q^{>}}, (2.21)$$

with  $Q_m = 0.5(Q^> + \mu Q^<)$ , and  $\mu = 1.01$  being a smoothing parameter that controls the distance of the hyperbola from its asymptotes. Figure 2-5 shows the behavior of Q,  $Q^<$  and  $Q^>$  as a function of the gate voltage and the Figure 2-6 shows the difference between the classical and quantum solutions of the charge density for comparison purposes.

Using the mentioned procedure, the charge per unit area can be expressed in a compact and explicit form in terms of known variables.

Figure 2-6 Quantum and classical charge density for  $T_{si}=5 \text{nm}$  and  $T_{ox}=1 \text{nm}$ .

#### 2.5 Results

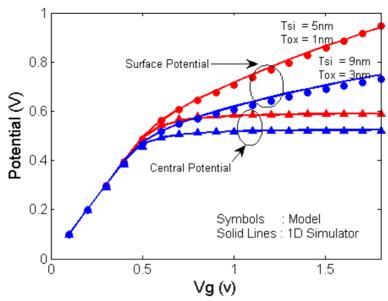

The model was validated by an extensive comparison with quantum numerical simulations from a 1D Poisson-Schrödinger solver [38]. Specifically, we have simulated the surface potentials, central potentials and charge density in the silicon channel as a function of  $V_g$ . Additionally, the silicon conduction band profiles along the perpendicular direction to the interface  $Si/SiO_2$  have been computed for comparison.

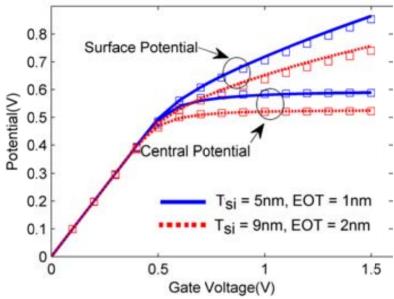

Figure 2-7 shows an example of the surface and central potential as a function of  $V_g$  with different geometries. The results show that the output of our model is in close agreement with the self-consistent solution with a relative error less than 5 % in any case.

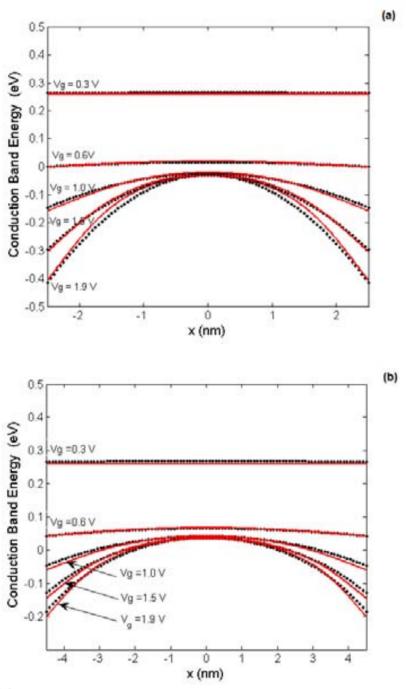

Typical silicon conduction band profiles are shown in Figure 2-8a and Figure 2-8b, respectively, for several gate voltages. Note that bands are essentially flat in the subthreshold region, just up to  $V_g \sim 0.4$  V identified as the threshold voltage. For  $V_g \gtrsim 0.4$  V, the surface potential increases linearly, and the central potential slightly downshifts until saturation is reached at  $V_g \sim 1$ V, identified as the onset of screening effects. Limitations of our model arise when

Figure 2-7 Electrostatic potentials at the center of the channel and the surface versus the gate voltage  $V_g$ . Geometrical parameters used here are  $T_{si} = 5$ nm,  $T_{ox} = 1$ nm and  $T_{si} = 9$ nm,  $T_{ox} = 3$ nm. The flat band voltage is assumed to be  $V_{fb} = 0$  V. Solid lines correspond to 1D simulations and symbols to our model data.

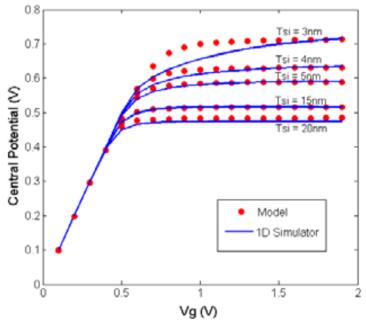

very thin films are considered. To illustrate this point, Figure 2-9 shows the behavior of the central potential as a function of  $V_g$  for DG-MOSFETs with different silicon films. For  $T_{si} \gtrsim 4$ nm, the central potential shows a saturated like behavior above the threshold voltage, indicative of the gate field shielding due to the formation of inverted channels on both surfaces. However, for  $T_{si} \lesssim 4$ nm and super-threshold operation, the central potential is no longer constant but grows almost linearly  $(d\phi_0/dV_g>0)$ , as can be observed from QM self-consistent results, suggesting the suppression of the two separated inverted channels in favor of volume inversion operation, where the gate field is now allowed to penetrate into the silicon film thus taking the control of the central potential.

Figure 2-8 Silicon conduction band profiles for (a)  $T_{si} = 5$ nm,  $T_{ox} = 1$ nm and (b)  $T_{si} = 9$ nm,  $T_{ox} = 3$ nm. Solid lines are data from 1D simulator and symbols corresponds to our model data.

Although we have found that for  $T_{si} \lesssim 4$ nm the  $T_{ox}$  dependence of  $\phi_{0max}$  start to be important and our model fails in this range (see Figure 2-4 and Figure 2-9), it works very well in scales where the effective mass approximation for nanoscale system is reasonable and the simulated results are correct. This is, the parabolic approximation may be not sufficient for nanoscale systems with atomic scale variations and tight-binding band-structure calculation or empirical pseudo potentials may be necessary [42, 43]. To highlight the importance of introducing a quantum model for the electrostatics on thin DG-MOSFETs, the reader should remember Figure 2-2 where the surface and central potentials are calculated from our model and compared with the classical model from Taur [23]. Note that the difference  $\phi_s - \phi_0$ , above the threshold voltage, as given by the quantum model is significantly larger than the classical result, which should be taken into account, for instance, when tunneling gate current needs to be calculated.

Figure 2-9 Electrostatic potentials at the center of the channel versus the gate voltage  $V_g$  for  $T_{si} = 2,3,4$  and 5 nm. Solid lines correspond to the simulations and symbols to our model data.

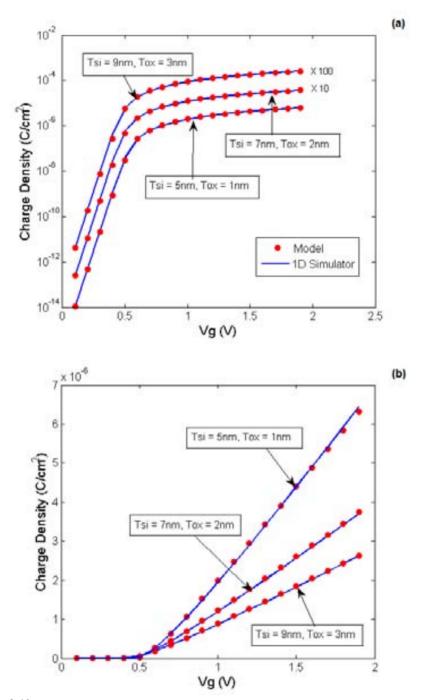

Figure 2-10 shows a comparison between our charge model presented in Section 2.4 and 1D simulation data for different geometries as a function of the gate voltage. It continuously covers all the operation regions with unique

Figure 2-10 Charge density versus gate voltage for several geometries and flat band voltage  $V_{fb}=0$  V. (a) Logarithmic scale and (b) linear scale. Solid lines correspond to 1D simulations and symbols to our model data. Some curves in (a) have been shifted upwards for the sake of clarity.

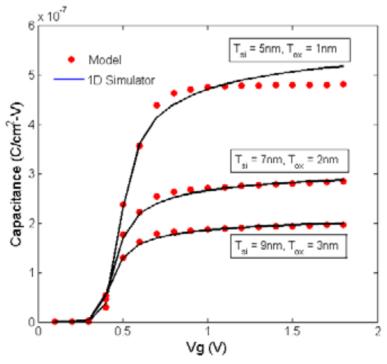

analytic expressions. A close agreement, in both subthreshold and superthreshold regions, proves the correct behavior of our model. Importantly, the gate capacitance, defined as  $C_g = dQ/dV_g$  is well captured by our model (Figure 2-11). That is a key parameter when AC and transient simulations are required.

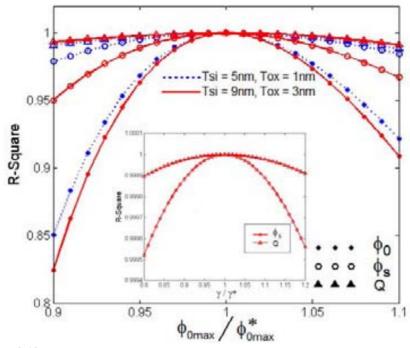

Finally, Figure 2-12 shows, for different geometries, the sensitivity of physical variables  $\phi_0$ ,  $\phi_s$  and Q to small variations of  $\phi_{0max}$  and  $\gamma$  parameters included in Eq. (2.6), around the values of  $\phi_{0max}^*$  and  $\gamma^*$  calculated from Eqs. (2.7) and (2.11), respectively. The sensitivity is quantified using the R-Square factor. The inset shows similar results but, in this case, the sensitivity analysis refers to the  $\gamma$  parameter. Note the  $\xi$  parameter in Eq. (2.6) has not been analyzed because is a function of  $\gamma$  and  $\phi_{0max}$  through Eq. (2.16). The R-Square factor appears to be not very sensitive to small variation of  $\phi_{0max}$  and  $\gamma$  parameters included in Eq. (2.6).

Figure 2-11 Gate capacitance versus gate voltage for several geometries and flat band voltage  $V_{fb} = 0$  V. Solid lines correspond to 1D simulations and symbols to our model data.

Figure 2-12 R-Square factor analysis of  $\phi_0$ ,  $\phi_s$  and Q as a function of  $\phi_{0max}$  relative to  $\phi_{0max}^*$ . The inset shows the R-Square factor of  $\phi_s$  and Q as a function of  $\gamma$  relative to  $\gamma^*$ .

# 2.6 Summary

A simple model for the quantum electrostatic potential and charge of the undoped long channel DG-MOSFET for thin silicon films has been developed and assessed. Additionally our model accurately reproduces the gate capacitance. The model presented here, based on the previously developed classical model [23], accounts for the Si-film thickness, oxide thickness and gate voltage dependences. Our model gives a closed form for the potential and charge (it does not need any iteration) and the results are in close agreement with self-consistent solutions.

We must emphasize that this model works very well within the range of validity of the used approximations. That is, for  $T_{si} \gtrsim 4$ nm,  $T_{ox} \leq 5$ nm, suband superthreshold regions. Although Ge's model [37] describes the quantum potential profile in a wider range of silicon thickness, their approach is not

useful to obtain the distribution of voltage through the MOS structure because the potential is referenced to the surface potential; i.e.  $\phi_s = 0$  for all  $V_g$ . That is, our model is able to calculate, completely, the dependence on  $\phi_s$ ,  $\phi_0$  and Q as a function of the gate voltage. The presented compact model can be interpreted as the core of more advanced models including, for instance, short-channel effects, non-equilibrium effects and tunneling effects.

Next chapter will address the development of an explicit model for the direct tunneling current in DG structures, using  $SiO_2$  as gate dielectric material. Such a model makes extensive use of the electrostatic model presented in this chapter.

# CHAPTER 3.

# Explicit Model for the Gate Tunneling Current in DoubleGate MOSFETs

#### 3.1 Outline

In this chapter, an explicit compact quantum model for the gate tunneling current in double-gate (DG) MOSFET is presented. Specifically, an explicit closed-form expression is proposed, useful for the fast evaluation of the gate leakage in the context of electrical circuit simulators. A benchmarking test against 1D self-consistent numerical solution of Schrödinger-Poisson (SP) equations has been performed to demonstrate the accuracy of the model.

Like conventional transistors, the scaling rule of DG-MOSFETs for controlling SCE dictates a reduction of the equivalent oxide thickness together with the channel length. The increasing gate leakage has to be taken into account due to its importance in determining the standby power.

Researchers have proposed some models for calculating the gate current in DG-MOSFETs however, due to the difficulty of solving the coupled SP equations, certain models have being proposed based on semi-empirical

dependent electric field expressions [44, 45], or purely numerical [46, 32], or considering only the ground state derived from a triangular approximation for the electronic confinement [47]. It is therefore valuable to have a compact model of the gate leakage current for DG-MOSFETs simply calling an explicit closed-form expression embedding the dependence on bias and both geometrical and electrical parameters.

In this work, we further extend the state-of-the-art by proposing a simple model for the electron conduction band (ECB) direct tunneling current of undoped DG-MOSFET, which is the dominant mechanism contributing to the gate leakage [48]. Our results are compared with those obtained from accurate self-consistent quantum-mechanical (QM) solutions resulting in excellent agreement for both moderate and strong inversion regimes, thus making it suitable for compact modeling.

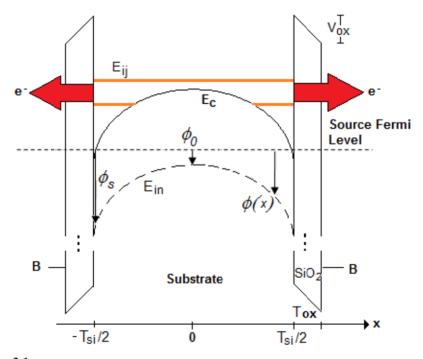

**Figure 3-1** Energy-band diagram along a perpendicular cut to the channel, where the direct gate tunneling flow is marked with thick arrows.

# 3.2 Model Development

In this section, modeling of quantum mechanical effects in an undoped silicon layer, considered as the active layer of the transistor, and subsequent direct tunneling current for a symmetric DG geometry are presented. Figure 3-1 shows a representative energy-band diagram along a vertical cut, where  $E_c$  represents the silicon conduction band edge,  $E_{in}$  is the intrinsic Fermi energy, and  $V_{ox}$  is the potential drop at the gate oxide. Also represented are the surface potential  $\phi_s$  and the central potential  $\phi_0$ , both referred to the Fermi level at the source. Also shown in Figure 3-1 are some of the quantized electron energy subbands and the direct gate tunneling flow of electrons from the Si substrate towards the metal gate.

Because of structural and/or electrostatic confinement in nanoscale DG-MOSFETs, quantization of the carrier energy in the Si layer is a relevant effect to be considered, generally, for any operation regime. Quantum effects result in a spatially wider carrier density as compared to the classical prediction. A common approach to tackle quantum effects consists of solving the coupled SP equations in a fully self-consistent manner. This method is accurate, but time consuming.

What we propose here is an efficient method in terms of computational time. Simplification of the complexity is possible using a quadratic approximation for the electron conduction band in the active layer as a perturbation to the box-like potential well created by the SiO<sub>2</sub>/Si/SiO<sub>2</sub> structure. Our model starts from the 1D classical modified potential to include quantum effects described in Chapter 2 and published in Ref. [49]. As demonstrated in Figure 2-7, both the surface and central potentials are well reproduced as compared with self-consistent SP simulations, where, to remember, the surface potential takes the form

$$\phi_s = \phi_0 - \frac{2kT}{q\gamma} ln \left[ cos \left( \frac{\pi \xi}{2} e^{q(\phi_0 - \phi_{0max})/2kT} \right) \right]$$

(3.1)

where the meaning of parameters  $\phi_{0max}$ ,  $\phi_0$ ,  $\xi$  and  $\gamma$  were previously discussed. It is worth noting that these quantities can be explicitly computed and numerical calculations are not required.

**Figure 3-2** Scheme of the transit time for electrons moving through the perpendicular direction to the channel. Also shown are the quantities defined in Eq. (3.7).

Next, for simplicity, we assume a parabolic shape for the 1D electrostatic potential across the channel nicely fitting both  $\phi_s$  and  $\phi_0$

$$\phi(x) = \phi_0 + 4(\phi_s - \phi_0)x^2/T_{si}^2 \tag{3.2}$$

Using the 2D density of states (DOS) and Fermi-Dirac statistic, the channel charge per unit area contributed per subband can be expressed as

$$N_{ij} = q \left( \frac{kT}{\pi \hbar^2} \right) g_i m_{di}^* \ln[1 + e^{(E_f - E_{ij})/kT}]$$

(3.3)

Based on perturbation methods [50], the energy level  $E_{ij}$  (referred to the minimum of the conduction band at the surface  $E_{cs}$ ) could be split into:

$$E_{ij} = E_{ij}^0 + E_{ij}^1 (3.4)$$

where

$$E_{ij}^{0} = \frac{\hbar^{2}}{2m_{zi}} \left(\frac{j\pi}{T_{si}}\right)^{2} \tag{3.5}$$

corresponds to the eigenvalues of the non-perturbed Hamiltonian (box-like potential well with infinite barriers) and

$$E_{ij}^{1} = \int_{-T_{si}/2}^{T_{si}/2} \psi_{j}^{0}(x) \tilde{E}_{c}(x) \psi_{j}^{0*}(x) dx = 2\Delta E_{os} \left( \frac{1}{(j\pi)^{2}} + \frac{1}{3} \right)$$

(3.6)

is the correction of the eigenvalues due to the perturbed Hamiltonian (quadratic potential approximation given by Eq. (3.2)). The eigenfunction  $\psi_j^0(x)$  corresponds to the wave function coming from the non-perturbed Hamiltonian and is equal to  $\sqrt{2/T_{si}}\sin(j\pi/T_{si}(x+T_{si}/2))$ . Note that  $\psi_j^{0*}$  refers to the complex conjugate and is equal to  $\psi_j^0$ . For expressing Eq. (3.6), we have used the following conventions (see Figure 3-2):

$$E_c(x) = E_g/2 - q\phi(x)$$

Conduction band relative to the Fermi level at the source electrode.

$$E_{cs} = E_c \left( \frac{\pm T_{si}}{2} \right)$$

Conduction band at the Si/SiO<sub>2</sub> interface.

$$E_{co} = E_c(0)$$

Conduction band at the center of Si layer.

$$\Delta E_{\rm os} = E_{co} - E_{cs}$$

Difference between the center and surface potential.

$$\tilde{E}_c(x) = E_c(x) - E_{cs}$$

Conduction band relative to  $E_{cs}$

$$= \Delta E_{os} (1 - 4x^2/T_{si}^2)$$

(3.7)

As we are interested in a simple expression for direct tunneling current at both low and high supply voltage regimes, we chose a modified WKB method to calculate the electron transmission probability [51]. Within the mass effective approximation, transmission probability of electrons with energy  $E_{ij}$  can be written in the form:

$$P_{ij} = P_{WKB} \cdot P_R, \tag{3.8}$$

where  $P_{WKB} = \exp\left(-2\int_0^{T_{ox}} k_{ox,ij}(x')dx'\right)$  is the usual WKB tunneling probability [52], valid for smoothly varying potentials. Here a change of coordinate has been made such that  $x' = x - T_{si}/2$ . The term  $P_R$  is a correction accounting for reflections due to potential discontinuities [51]. The momentum

entering in the integral can be calculated by using a Franz-type dispersion relation for the gate oxide [53], namely

$$\frac{\hbar^2 k_{ox,ij}^2}{2m_{ox}} = \eta_{ij} = E_{ox,ij} \left( 1 - \frac{E_{ox,ij}}{E_{g,ox}} \right)$$

(3.9)

$$v_{ox,ij} = \frac{1}{\eta'_{ij}} \sqrt{\frac{2\eta_{ij}}{m_{ox}}},$$

(3.10)

where  $m_{ox}$  is the electron effective mass within the SiO<sub>2</sub> oxide,  $E_{g,ox}$  is the oxide band gap  $\approx 9$  eV for SiO<sub>2</sub>,  $v_{ox,ij}$  refers to the group velocity of electrons in the oxide, and  $\eta_{ij}^{'}$  is defined as  $\frac{d\eta_{ij}}{dE_{ox,ij}}$ . On the other hand  $E_{ox,ij}(x')$  is the magnitude of the electron energy relative to the oxide conduction band edge given by  $\Phi_{\rm B} - E_{ij} - qV_{ox}x'/T_{ox}$ , where  $\Phi_{\rm B}$  is the discontinuity between the Si and SiO<sub>2</sub> conduction bands ( $\sim 3.15$  eV), and  $V_{ox}$  is the oxide voltage drop equal to  $Q\frac{T_{ox}}{2\epsilon_{ox}}$ , where the factor 2 in the denominator comes from the half of the total charge (Q) that is controlled by each gate.

To go ahead both  $P_{WKB}$  and  $P_R$  for electrons with energy  $E_{ij}$  can be expressed, respectively, as

$$P_{WKB} = exp \left[ \frac{E_g T_{ox} \sqrt{2m_{ox}}}{4\hbar q V_{ox}} \left( 2\eta'_{ij} \sqrt{\eta_{ij}} + \sqrt{E_g} \sin^{-1} \eta'_{ij} \right) \Big|_{E_{ox,ij}(x'=T_{ox})}^{E_{ox,ij}(x'=0)} \right]$$

(3.11)

$$P_{R} = \frac{4v_{Si,ij}(E)v_{ox,ij}(E_{ox,ij}|_{x'=0})}{v_{Si,ij}^{2}(E)+v_{ox,ij}^{2}(E_{ox,ij}|_{x'=0})} \frac{4v_{Si,ij}(E+qV_{ox})v_{ox,ij}(E_{ox,ij}|_{x'=T_{ox}})}{v_{Si,ij}^{2}(E+qV_{ox})+v_{ox,ij}^{2}(E_{ox,ij}|_{x'=T_{ox}})}$$

(3.12)

where  $v_{Si,ij}$  is the perpendicular (normal to the interface) component of electron group velocity. Both  $P_R$  and  $P_{WKB}$  are quantities depending on the transversal  $m_t$  and longitudinal  $m_l$  electron effective masses. The group velocity for electrons in the substrate is computed as

$$v_{Si,ij} = \sqrt{\frac{2E_{ij}}{m_{zi}}} \tag{3.13}$$

In addition to the eigenvalues and transmission probabilities, the "lifetime"  $T_{ij}$  of the electrons in the  $i,j^{th}$  electronic state flowing toward the gates from the silicon layer is needed to calculate the leakage current. A useful model for this parameter comes from [32]:

$$\frac{1}{T_{ij}} = \frac{P_{ij}}{\tau_{ij}} \left[ (1 - P_b) + \frac{1}{2} P_b^2 \right]$$

(3.14)

where  $\tau_{ij}$  is the classical transit time of an electron between Si/SiO<sub>2</sub> interface and the classical turning point  $x_{t,ij}$ ,  $P_{ij}$  is the transmission probability of Eq. (3.8) and  $P_b$  is the tunneling probability through the conduction band. Note that the time elapsed for tunneling through the barrier in the silicon region has been neglected in Eq. (3.14).

The transit time is defined as the integral of the inverse of the group velocity  $\tau_{ij} = 2 \int_{x_{t,ij}}^{T_{si}/2} v^{-1}(x) dx$ , which could be analytically calculated yielding

$$\tau_{ij} = 2 \int_{x_{t,ij}}^{T_{si}/2} \sqrt{\frac{m_{zi}}{2(E_{ij} - \tilde{E}_c(x))}} dx = T_{si} \sqrt{\frac{m_{zi}}{2\Delta E_{os}}} \ln \left( \frac{\sqrt{\Delta E_{os}} + \sqrt{E_{ij}}}{\sqrt{|E_{ij} - \Delta E_{os}|}} \right) (3.15)$$

This expression is valid for both  $E_{ij} \leq \Delta E_{os}$  and  $E_{ij} > \Delta E_{os}$  cases. A physical interpretation of the transit time is sketched in Figure 3-2.

The tunneling probability  $P_b$  for electrons with energies between  $E_{co}$  and  $E_{cs}$  to cross the conduction band can be calculated with the help of a simplified WKB approximation in the form

$$P_{b} = exp\left\{-2\int_{-x_{t,ij}}^{x_{t,ij}} \sqrt{\frac{2m_{zi}}{\hbar^{2}} \left[E_{ij} - \tilde{E}_{c}(x)\right]} dx\right\}$$

(3.16)

Inserting Eqs. (3.4) to (3.7) into Eq. (3.16) and, after some manipulations,  $P_b$  could be written as a simple closed-form expression

$$P_b = exp\left(-\sqrt{\frac{m_{zi}\pi^2 T_{si}^2}{2\hbar^2 \Delta E_{os}}} (\Delta E_{os} - E_{ij})\right) \text{ for } E_{cs} < E < E_{c0}$$

(3.17)

It is worth noting that  $\frac{1}{T_{ij}} \sim P_{ij}/(2\tau_{ij})$  for energy levels such as  $E_{ij} > \Delta E_{os}$ , for which  $P_b = 1$ . Conversely, for energies deep in the potential well formed by the electrostatic confinement, then  $P_b \sim 0$  and  $\frac{1}{T_{ij}} \sim P_{ij}/\tau_{ij}$  similar to the case of a very thick semiconductor, which is equivalent to bulk diodes connected by the common substrate.

The proposed semi-classical model for the electron lifetime given by Eq. (3.14) yields similar results as compared with the half-with of the resonant state method [54, 55] as well as the method of quasi-bounded states with absorbing boundary conditions [56, 57]. However is computationally more efficient.

Finally, combining the results from Eqs. (3.3), (3.8), (3.14) and (3.17), we can readily obtain the total gate direct tunneling current density by adding the contribution of every subband:

$$J = \sum_{ij} N_{ij} / T_{ij} = \sum_{ij} J_{ij}$$

(3.18)

#### 3.3 Results

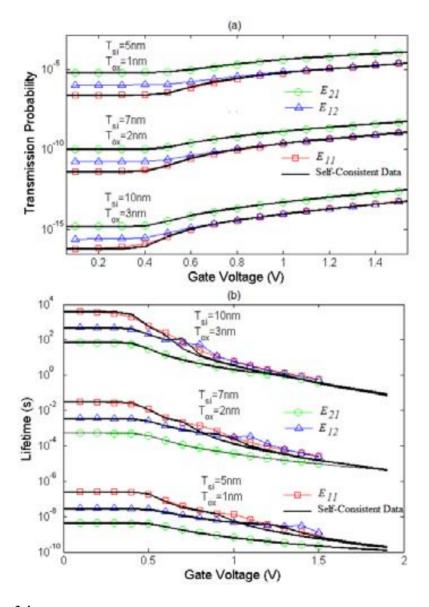

The model described in this chapter considers as fundamental quantities  $E_{ij}$ ,  $N_{ij}$ , and  $T_{ij}$ . In this section we check the accuracy of these quantities and therefore of the proposed compact model. To illustrate the model outcome we only consider the first three states, which contribute the most to the gate direct tunneling current. We also have assumed a flat band voltage  $V_{fb}$  equal to zero, corresponding to a midgap gate. The results below show that the model output is in close agreement with the self-consistent solution in all operation regions and for wide range of silicon layer and gate oxide thicknesses, representative of the design window for nanoscale DG-MOSFETs.

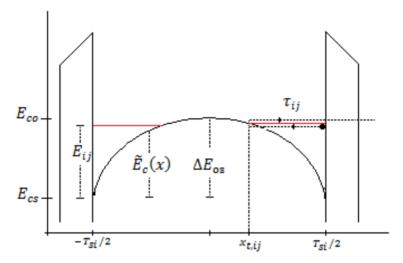

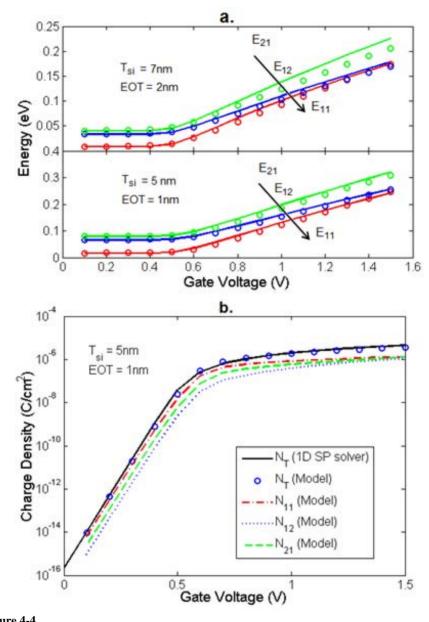

The behavior of the ground state energy  $E_{11}$ ,  $E_{12}$  and  $E_{21}$  as a function of the gate voltage is shown in Figure 3-3a. As expected, the energy states increase as  $T_{si}$  is reduced due to the structural confinement. Below the threshold voltage,

Figure 3-3 (a) Subband energies versus gate voltage for different geometries; (b) Charge densities of the three first states and total charge density  $(N_T)$ ;

the band bending is negligible, and the band diagram looks like a square potential well. Beyond the threshold voltage, the electric field strength induces an electrostatic confinement of carriers, resulting in a semi-quadratic potential

well. Figure 3-3b represents the total charge density and the charge densities  $N_{11}$ ,  $N_{12}$  and  $N_{21}$  as a function of the gate voltage. Here, we see that the  $E_{21}$  level contributes significantly to the charge density because its degeneracy and density of states effective mass, despite having a higher energy than the other two levels (see Figure 3-3a).

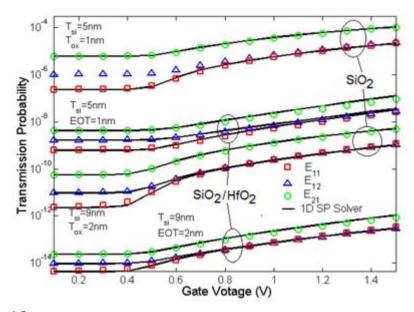

**Figure 3-4** (a) Transmission probability of the  $E_{ij}$  state through the oxide barrier; (b) Electron lifetime of the  $E_{ij}$  state.

**Figure 3-5**Gate current density where the inset shows the gate current density as a function of the oxide thickness. Symbols: model; Solid lines: SP simulations.

Figure 3-4a and Figure 3-4b show the transmission probability  $P_{ij}$  and lifetime  $T_{ij}$ , respectively. Here, we can appreciate the strong dependence of the tunneling with the oxide thickness (see also the inset of Figure 3-5). In general, the transmission probability increases and the lifetime is reduced with the gate voltage as a result of the electric confinement in the inversion layer. However this effect is smaller when the body is thinner because the confining electric field is reduced [58].

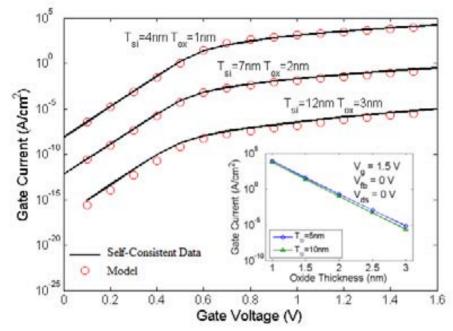

Combining the fundamental quantities, following Eq. (3.18), we have finally calculated the gate current density for several geometries. The result is shown in Figure 3-5 and the inset shows the expected exponential character of the tunneling current with the thickness of the barrier oxide.

In absence of experimental data in the literature (to our knowledge), our results are comparable with those reported in works where the self-consistent simulations take into account the electronic wave function penetration in the metal gate [46, 58].

# 3.4 Summary

An explicit compact model of the gate direct tunneling current for the symmetric undoped DG-MOSFET has been developed and assessed. Specifically the model was checked via comparison with self-consistent SP simulations. Our model is accurate within the range of validity of the used approximations. That is, for  $T_{si} \gtrsim 4nm$  and  $T_{ox} \leq 5nm$ . All the quantities taking part in the model are explicit closed-form expressions that permit to calculate the dependence of the gate direct tunneling current as a function of the gate voltage.

This model makes possible the fast evaluation of the gate leakage in aggressive scaled DG-MOSFETs and could be incorporated into a general compact model as a building block of electrical circuit simulators.

Although the present model for the direct tunneling works for silicon dioxide as gate dielectric material, when the  $SiO_2$  thickness is scaled roughly to 1nm very large gate current density is observed. Figure 3-5 shows that the gate current density exceeds  $1A/cm^2$  for gate voltage values larger than 0.5 V, which are too high for low power applications [9]. The introduction of high- $\kappa$  dielectric materials as gate insulators is a key solution to solve the gate tunneling leakage current issue because for a given equivalent oxide thickness (EOT) the leakage is much smaller for high- $\kappa$  than for oxi-nitride gate dielectric. Next chapter proposes an extension of the model presented in this chapter, where dual layer stacks including high- $\kappa$  insulators are considered in the calculation of the direct tunneling current.

# **CHAPTER 4.**

# Explicit Model for Direct Tunneling Current in DoubleGate MOSFETs Through a Dielectric Stack

#### 4.1 Outline

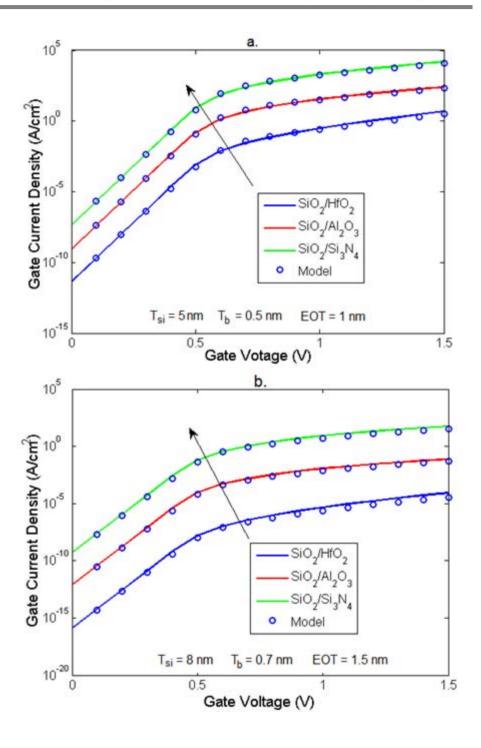

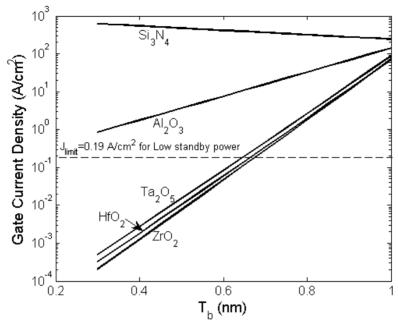

In this chapter an extension to the model presented in the previously chapter is presented. In this case, an explicit compact quantum model for the direct tunneling current through dual layer  $SiO_2$ /high- $\kappa$  dielectrics in Double Gate structures is proposed. Specifically, an explicit closed-form expression is proposed, useful to study the impact of dielectric constants and band offsets in determining the gate leakage, allowing to identify materials to construct these devices, and useful for the fast evaluation of the gate leakage in the context of electrical circuit simulators. A comparison with self-consistent numerical solution of Schrödinger-Poisson (SP) equations has been performed to demonstrate the accuracy of the model. Finally, a benchmarking test for different gate stacks have been proposed searching to fulfill the gate tunneling limits as projected by the ITRS.

Similar to the conventional transistors, the scaling rule of DG-MOSFETs dictates a reduction of the oxide thickness together with the channel length, causing a large increase of the gate leakage current [9]. This is critical in determining power dissipation of circuits, especially those used in low-power electronic systems such as cell phones, lap-tops etc. Similarly to the bulk MOSFET, a way to overcome this limitation is to use high- $\kappa$  materials deposited over a thin SiO<sub>2</sub> layer to form the gate insulator.

To calculate the gate leakage current in DG-MOSFETs it would strictly be necessary to solve the coupled Schrödinger-Poisson (SP) equations in a fully self-consistent manner considering a quasi-bound system. This method is accurate, but time consuming. Researchers have proposed some analytical models for calculating the gate current in DG-MOSFETs including high-κ dielectrics. However those models have being proposed based on semi-empirical dependent electric field expressions [44, 59] and do not consider the quantization of the energy levels. On the other hand there are some purely numerical models solving the SP equations self-consistently [32, 46] not useful for a fast evaluation of device performances in circuits simulators. It is therefore valuable to have a compact model of the gate tunneling current for DG-MOSFETs with dielectrics including high-κ materials, simply calling an explicit closed-form expression that takes into account relevant quantum effects. Such models are essential to understand the scaling limits of DG-MOSFETs.

We introduce a compact model of the direct tunneling current mechanism of symmetric undoped DG-MOSFETs considering a  $SiO_2$ /high- $\kappa$  hetero-structure as gate oxide based on the previous model of the Chapter 3 where only  $SiO_2$  dielectric was used and reported in Ref. [60].

Direct tunneling is known to be the dominant contribution to the gate leakage current [61]. Our results are compared with those obtained from accurate self-consistent quantum-mechanical (QM) solutions, resulting in excellent agreement for both moderate and strong inversion regimes. Both accuracy and simplicity of the model makes it suitable for circuit simulators.

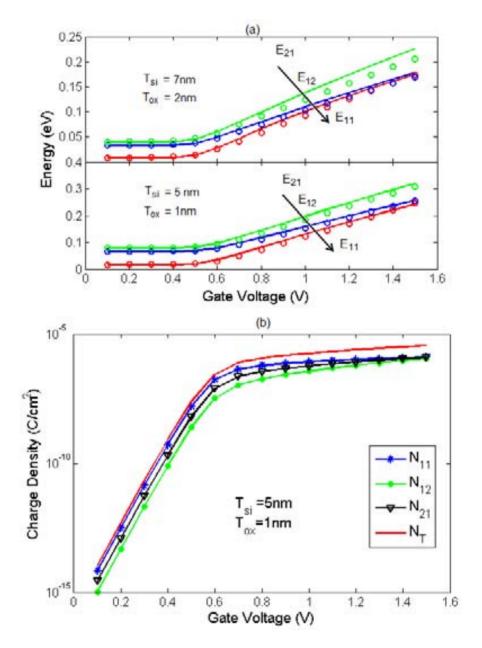

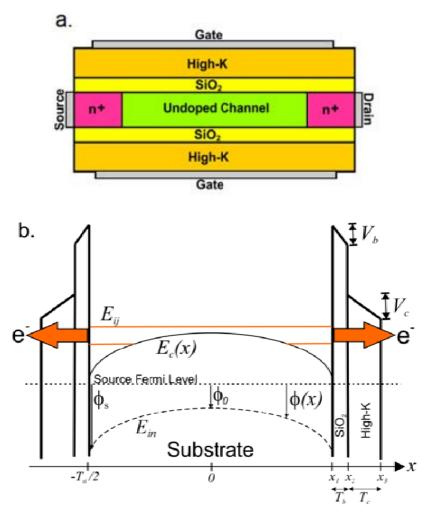

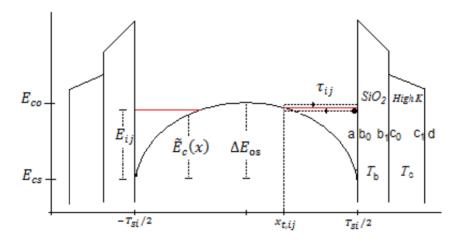

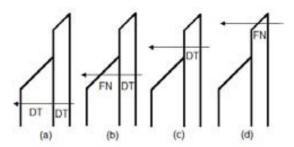

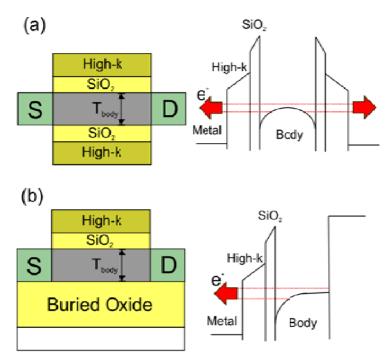

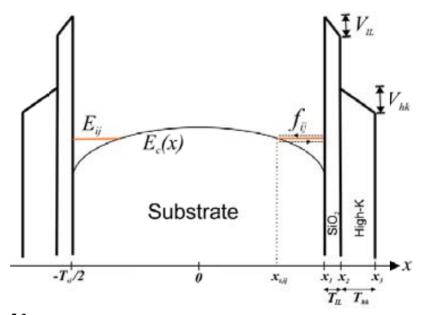

**Figure 4-1** Schemes of (a) DG-MOSFET structure and (b) the energy-band diagram across the channel.

# 4.2 Model Development

To model the direct tunneling current of a symmetric DG-MOS capacitor (Figure4-1a) we have assumed fully bound states, meaning that the electron wave function does not penetrate through the gate oxide. Fig. 1b shows an energy-band diagram considering volume inversion, where  $E_c$  represents the silicon conduction band edge,  $E_{in}$  is the intrinsic Fermi energy, and  $V_b$  and  $V_c$  are the potential drops at the SiO<sub>2</sub> and high- $\kappa$  dielectrics, respectively. Again, the surface and central potentials  $\phi_s$  and  $\phi_0$  are both referred to the Fermi level at

the source. The electron direct gate tunneling current goes from the Si substrate to the metal gate passing through the dielectric stacks.

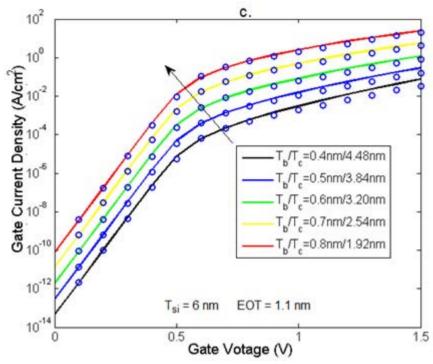

In this chapter we propose a suitable method in terms of computational time. Again, it relies on a quadratic approximation for the electron conduction band in the silicon layer acting as a perturbation to the box-like potential well created by the high- $\kappa$ /SiO<sub>2</sub>/Si/SiO<sub>2</sub>/high- $\kappa$  structure (see Figure 4-1b). Our model starts from a 1D classical potential expression, modified to include QM effects [49], which was proposed for a DG structure using SiO<sub>2</sub> as gate dielectric with thickness  $T_{ox}$  and potential drop  $V_{ox}$ . It can be easily adapted to our purposes, only replacing  $T_{ox}$  by the Equivalent Oxide Thickness  $EOT = T_b + \frac{3.9}{\kappa} * T_c$ , and  $V_{ox}$  would be now the sum of the potential drops in each layer  $V_b$  and  $V_c$ , so  $V_{ox} = V_b + V_c$ . The  $\kappa$  term is the high- $\kappa$  material dielectric constant. By making those changes the full model described in Chapter 2 and published under Ref. [49] can be used to calculate the band profile. As shown in Figure 4-2, where the DG with SiO<sub>2</sub>/HfO<sub>2</sub> as dielectric stack is considered, both the surface and central potentials are well replicated as compared with self-consistent SP simulations, where the surface potential takes the form

$$\phi_s = \phi_0 - \frac{2kT}{q\gamma} ln \left[ cos \left( \frac{\pi \xi}{2} e^{q(\phi_0 - \phi_{0max})/2kT} \right) \right]$$

(4.1)

It is worth remembering that  $\phi_{0max}$ ,  $\phi_0$ ,  $\xi$  and  $\gamma$  can be explicitly computed and iterative numerical calculations are not required.

Next, we assume a parabolic shape for the 1D electrostatic potential across the channel nicely fitting both  $\phi_s$  and  $\phi_0$

$$\phi(x) = \phi_0 + 4(\phi_s - \phi_0)x^2/T_{si}^2 \tag{4.2}$$

Using the 2D density of states (DOS) and Fermi-Dirac statistic, the channel charge per unit area contributed per sub-band can be expressed as

$$N_{ij} = \frac{qkT}{\pi \hbar^2} g_i m_{di}^* \ln \left[ 1 + e^{(E_f - E_{ij})/kT} \right]$$

(4.3)

where  $g_i$  and  $m_{di}^*$  are the degeneracy and the DOS effective mass of the *i*th valley respectively, and  $E_{ij}$  is the energy level of the *j*th sub-band in the *i*th valley, referred to the minimum of the conduction band at the surface  $E_{cs}$ .

Figure 4-2 Surface and central potentials of a DG-MOS capacitor considering a  $SiO_2/HfO_2$  gate stack, where  $SiO_2$  has a physical thickness  $T_b = 0.7$ nm. Lines correspond to 1D SP self-consistent simulation and symbols correspond to the model.

Based on perturbation methods [50], the energy level  $E_{ij}$  could be split into:

$$E_{ij} = E_{ij}^0 + E_{ij}^1 (4.4)$$

where

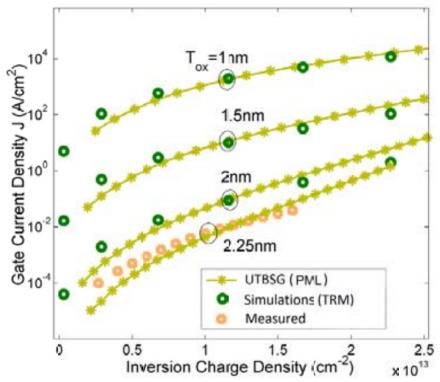

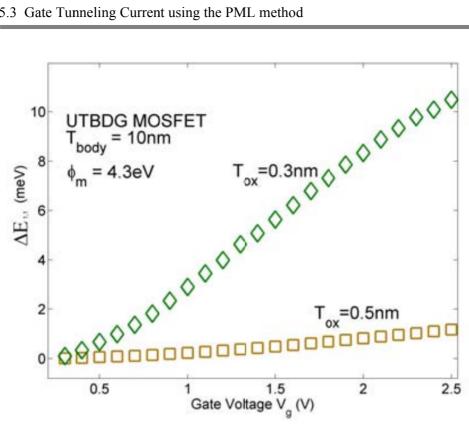

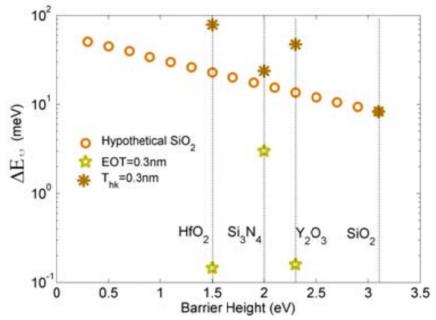

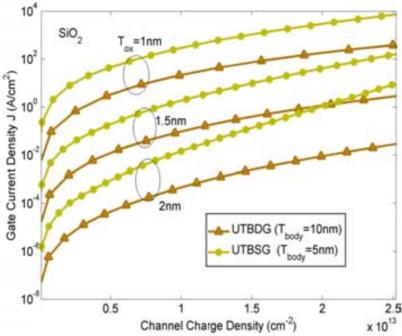

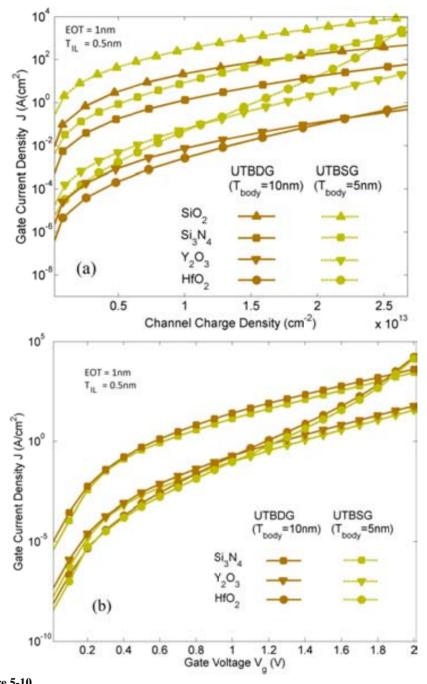

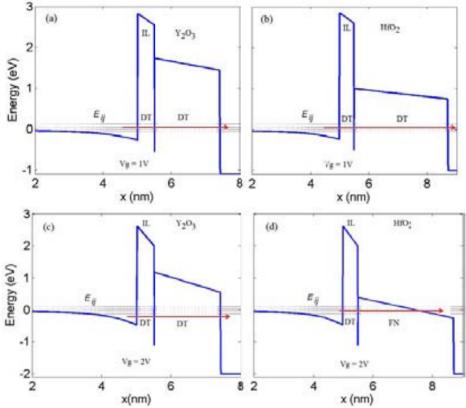

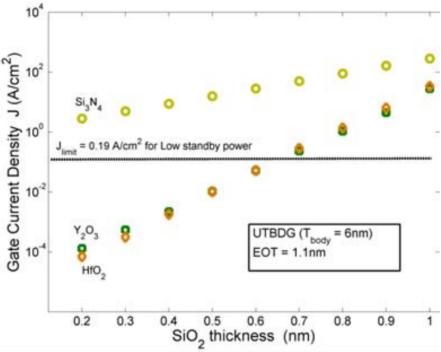

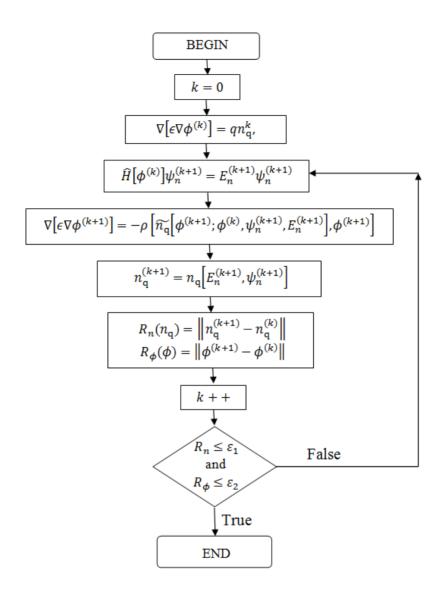

$$E_{ij}^{0} = \frac{\hbar^{2}}{2m_{zi}} \left(\frac{j\pi}{T_{si}}\right)^{2} \tag{4.5}$$